#### Intelligent Double Low-Side Switch 2 × 2 A

#### TLE 4211

#### **Bipolar IC**

#### Features

- Double low-side switch, 2 x 2 A

- Power limitation

- Overtemperature shutdown

- Status monitoring

- Shorted-load protection

- Reverse polarity protection

- Integrated clamp Z-Diodes

- Voltage proof up to 70 V

- Temperature range 40 to 125 °C

| Туре     | Ordering Code | Package     |

|----------|---------------|-------------|

| TLE 4211 | Q67000-A8118  | P-TO220-7-1 |

#### Application

Applications in automotive electronics require intelligent power switches activated by logic signals, which are shorted-load protected and provide error feedback.

The IC contains two of these power switches (low-side switch). In case of inductive loads the integrated power Z-diodes clamp the discharging voltage.

With TTL signals at the control inputs (active low) both switches can be activated independently of one another. If one of the inputs is not in use, it must be applied to high potential.

The status output (open collector) signals the following malfunctions through low potential:

- Overload,

- Open load,

- Output shorted to ground,

- Overvoltage.

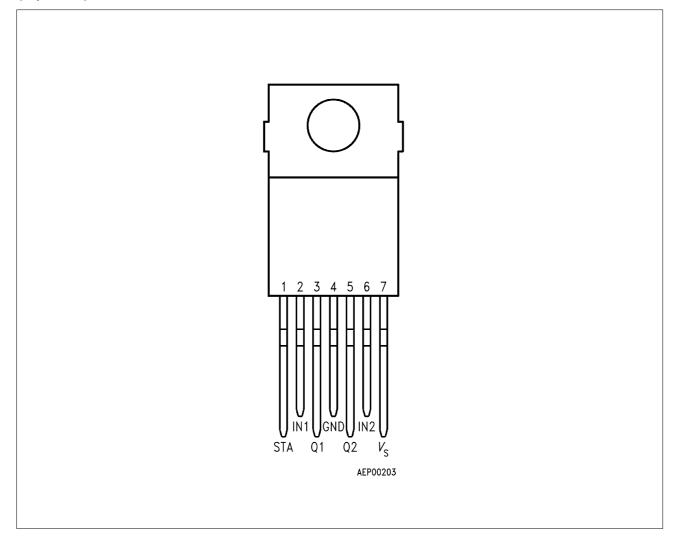

## Pin Configuration

(top view)

#### **Pin Definitions and Functions**

| Pin No. | Symbol | Function                                                                                                                                                                                                                                                           |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | STA    | <b>Status output (open collector)</b><br>for both outputs; indicates overload, open load and shorted load to<br>ground as well as overvoltage at pin 7. In case of malfunction the<br>status output is switched to low after a delay time (except<br>overvoltage). |

| 2       | IN1    | Control input 1 (TTL-compatible)<br>activates output transistor 1 in case of low-potential.                                                                                                                                                                        |

| 3       | Q1     | <b>Output 1</b><br>Shorted-load protected, open collector output with 36 V clamp Z-diode to ground.                                                                                                                                                                |

| 4       | GND    | <b>Ground</b><br>Wiring must be designed for a max. short-circuit current (2 x 3.5 A).                                                                                                                                                                             |

| 5       | Q2     | Output 2<br>Shorted-load protected, open collector output with 36 V clamp<br>Z-diode to ground.                                                                                                                                                                    |

| 6       | IN2    | <b>Control input 2 (TTL-compatible)</b><br>activates output transistor 2 in case of low-potential.                                                                                                                                                                 |

| 7       | Vs     | <b>Supply voltage</b><br>In case of overvoltage at this pin large sections of the circuit are<br>deactivated. The status output indicates the malfunction without<br>delay time.                                                                                   |

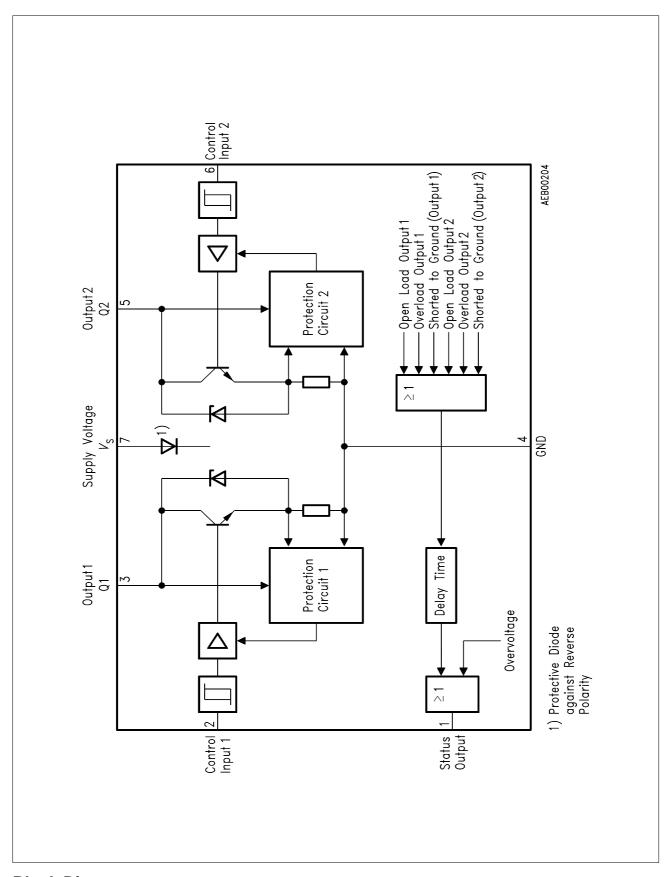

## **Block Diagram**

#### **Circuit Description**

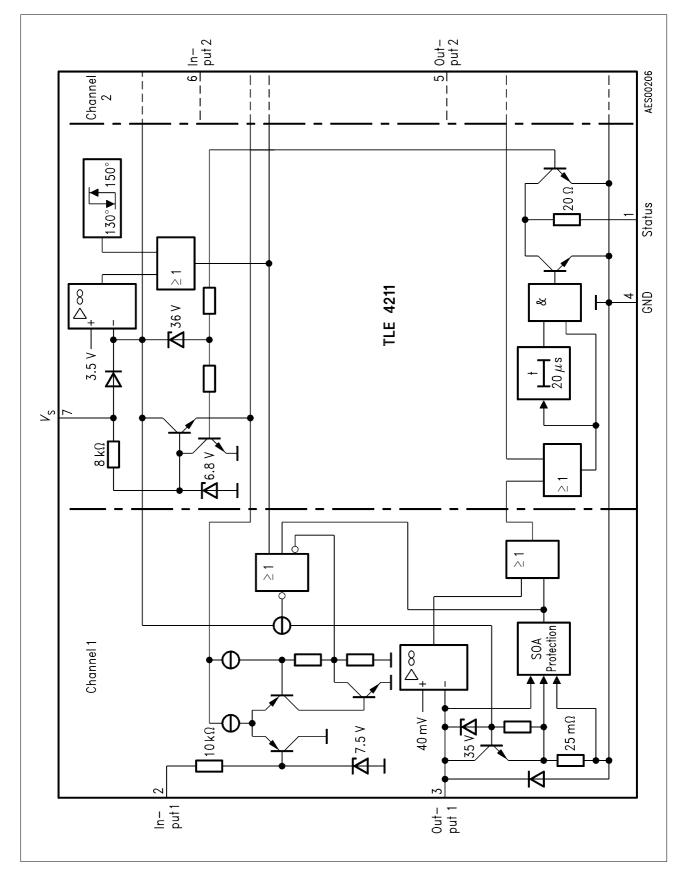

#### Input Circuits

The control inputs comprise TTL-compatible Schmitt triggers with hysteresis. Driven by these stages the inverting buffer amplifiers convert the logic signal for driving the NPN power transistors.

#### **Switching Stages**

The output stages comprise NPN power transistors with open collectors. Since the protective circuit allocated to each stage limits the power dissipation, the outputs are shorted-load protected to the supply voltage throughout the entire operating range. Positive voltage peaks, which occur during the switching of inductive loads, are limited by the integrated clamp Z-diodes.

#### Monitoring and Protective Functions

The outputs are monitored for open load, overload, and shorted output to ground (**see table below**). In addition, large sections of the circuit are de-activated in case of excessive supply voltages  $V_{\rm S}$ . Linked via OR gate the information regarding these malfunctions effects the status output (open collector, active low). An internally determined delay time applied to all malfunctions but overvoltage prevents the output of messages in case of short-term malfunctions. Furthermore, a temperature protection circuit prevents thermal overload. An integrated reverse diode protects the supply voltage  $V_{\rm S}$  against reverse polarities. Similarly the load circuit is protected against reverse polarities within the limits established by the maximum ratings (no shorted load at the same time!). At supply voltages below the operating range an undervoltage detector ensures that neither the status nor the outputs are activated.

| Status Output (L = Error) |              |                                |                                 |   |  |  |  |  |

|---------------------------|--------------|--------------------------------|---------------------------------|---|--|--|--|--|

|                           | Undervoltage | Operat                         | Overvoltage                     |   |  |  |  |  |

|                           |              | V <sub>I</sub> = L<br>(active) | V <sub>I</sub> = H<br>(passive) |   |  |  |  |  |

| Normal function           | Н            | Н                              | Н                               | L |  |  |  |  |

| Overload                  | Н            | L                              | Н                               | L |  |  |  |  |

| Open load                 | Н            | L                              | Н                               | L |  |  |  |  |

| Shorted output to ground  | Н            | L                              | L                               | L |  |  |  |  |

Semiconductor Group

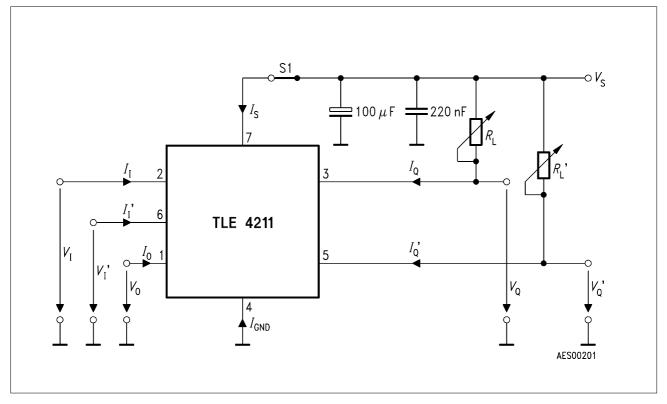

## Circuit Diagram

Semiconductor Group

#### **Absolute Maximum Ratings**

$T_{\rm j}$  = - 40 to 150 °C

| Parameter | Symbol | Limit | Unit |  |

|-----------|--------|-------|------|--|

|           |        | min.  | max. |  |

### Voltages

| Supply voltage (pin 7) <sup>1)</sup>          | Vs          | - 45  | 45 | V |

|-----------------------------------------------|-------------|-------|----|---|

| Supply voltage (pin 7) $t \le 500 \text{ ms}$ | Vs          | -     | 70 | V |

| Input voltage (pin 2; pin 6)                  | $V_{\rm I}$ | - 5   | 45 | V |

| Output voltage (pin 1)                        | Vo          | - 0.3 | 45 | V |

#### **Currents**

| Switching current (pin 3; pin 5)                                                | IQ                      | limited   | internally  |         |

|---------------------------------------------------------------------------------|-------------------------|-----------|-------------|---------|

| Current with reverse polarity (pin 3; pin 5) $T_{\rm C} \le 85 ^{\circ}{\rm C}$ | $I_{Q}$                 | - 2.2     | _           | А       |

| Output current (pin 1)                                                          | I <sub>Q</sub>          | _         | 10          | mA      |

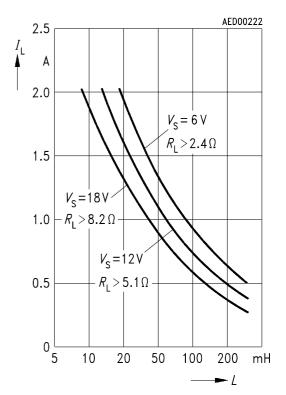

| Max. current at inductive load                                                  | I <sub>Q</sub>          | _         | see Diagram |         |

| Junction temperature<br>Storage temperature                                     | $T_{ m j} \ T_{ m stg}$ | -<br>- 50 | 150<br>150  | °C<br>℃ |

#### **Operating Range**

| Supply voltage                                                | Vs                            | 5.6 <sup>2)</sup> | 20      | V          |

|---------------------------------------------------------------|-------------------------------|-------------------|---------|------------|

| Supply voltage slew rate                                      | $dV_{\rm S}/dV$               | - 1               | 1       | V/µs       |

| Case temperature                                              | T <sub>C</sub>                | - 40              | 125     | °C         |

| Thermal resistance<br>junction to case<br>junction to ambient | $R_{ m th~JC} \ R_{ m th~JA}$ |                   | 4<br>65 | K/W<br>K/W |

<sup>1)</sup> Refer to monitoring and protective functions <sup>2)</sup> Lower limit = 4.6 V, if previously  $V_{\rm S}$  greater than 5.6 V (turn-on hysteresis)

#### **Characteristics**

$V_{\rm S}$  = 6 to 18 V and  $T_{\rm j}$  = – 40 to 125 °C

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### **General Characteristics**

| Quiescent current<br>Supply voltage                              | I <sub>S</sub><br>I <sub>S</sub> | _  | 3.5<br>100 | 10<br>180 | mA<br>mA | $V_{\rm I} = V_{\rm I} > V_{\rm IH}$ $V_{\rm I} = V_{\rm I} < V_{\rm IL}$ |

|------------------------------------------------------------------|----------------------------------|----|------------|-----------|----------|---------------------------------------------------------------------------|

| Supply overvoltage shutdown threshold                            | $V_{\rm SO}$                     | 34 | 36         | 42        | V        | $I_{\rm O}$ = 5 mA; $V_{\rm O}$ < 0.4 V                                   |

| Open load error<br>threshold voltage                             | $V_{QU}$                         | _  | 40         | _         | mV       | $I_{\rm O}$ = 5 mA; $V_{\rm O}$ < 0.4 V                                   |

| Open load error<br>threshold current                             | I <sub>QU</sub>                  | _  | 50         | 120       | mA       | $V_{\rm Q} = V_{\rm QU}$                                                  |

| Open load error<br>threshold current for<br>both channels active | I <sub>QU</sub>                  | _  | -          | 250       | mA       | $V_{\rm Q1} = V_{\rm Q2} = V_{\rm QU}$                                    |

#### Logic

| Control input<br>H-input voltage<br>L-input voltage   | $V_{IH} \ V_{IL}$              | -<br>0.7 | 1.7<br>1.1 | 2.4<br>_ | V<br>V   |                                       |

|-------------------------------------------------------|--------------------------------|----------|------------|----------|----------|---------------------------------------|

| Hysteresis of<br>input voltage                        | $\Delta V_{\rm I}$             | _        | 0.6        | _        | V        | _                                     |

| H-input current<br>L-input current                    | $I_{\rm IH}$<br>- $I_{\rm IL}$ | _        |            | 10<br>10 | μΑ<br>μΑ | $V_{\rm I} = 5 V$ $V_{\rm I} = 0.5 V$ |

| Status output<br>(open coll.)<br>L-saturation voltage | V <sub>OSat</sub>              | _        | _          | 0.4      | V        | <i>I</i> <sub>0</sub> = 5 mA          |

| Status delay time                                     | t <sub>dS</sub>                | 12       | 20         | 30       | μs       | 1)                                    |

<sup>1)</sup> Period from the beginning of the disturbance at one channel (exception: overvoltage) until the 50 % value of the status switching edge is reached.

### Characteristics (cont'd)

$V_{\rm S}$  = 6 to 18 V and  $T_{\rm j}$  = – 40 to 125 °C

| Parameter | Symbol | Limit Values |      | Unit | Test Condition |  |

|-----------|--------|--------------|------|------|----------------|--|

|           |        | min.         | typ. | max. |                |  |

#### **Power Output**

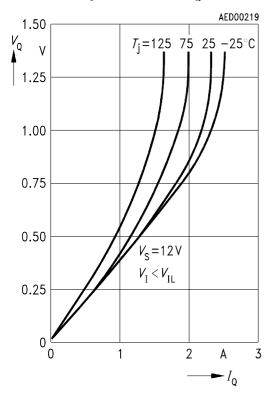

| Saturation voltage                | $V_{QSat}$                              | _ | 0.6        | 0.8     | V        | $I_{Q} = 1.6 \text{ A}; V_{I} < V_{IL};$<br>$T_{j} = 25 \text{ °C}$ |

|-----------------------------------|-----------------------------------------|---|------------|---------|----------|---------------------------------------------------------------------|

| Leakage current                   | IQ                                      | _ | _          | 300     | μA       | $V_{\rm Q}$ = 6 V; $V_{\rm I}$ > $V_{\rm IH}$                       |

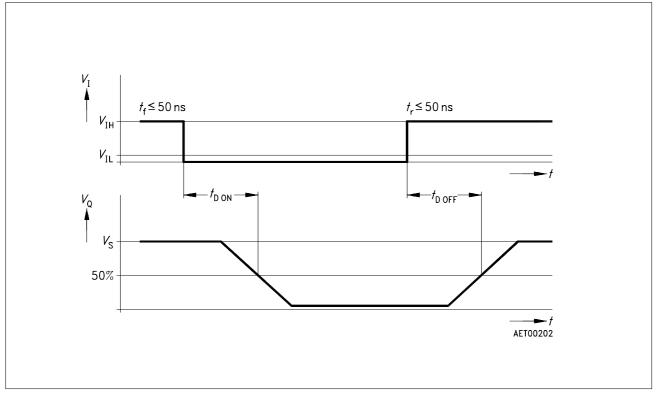

| Switch-ON time<br>Switch-OFF time | t <sub>D ON</sub><br>t <sub>D OFF</sub> |   | 0.5<br>2.5 | 5<br>10 | μs<br>μs | see Timing Diagram;<br>$I_{\rm Q} = 1  {\rm A}$                     |

| Output voltage<br>Negative clamp  | $-V_{\rm QF}$                           | _ | 1.4        | 1.8     | V        | $I_{\rm Q} = -2.0 \ {\rm A}$                                        |

## **Power Clamp Diode** ( $V_{\rm S}$ = 42 V; $S_{\rm 1}$ open)

| Output voltage positive clamp | V <sub>QZ</sub> | 34 | 36 | 40 | V | $I_{\rm Q} = 0.1  {\rm A}$ |

|-------------------------------|-----------------|----|----|----|---|----------------------------|

| Serial resistance             | r <sub>z</sub>  | _  | 2  | —  | Ω | $0 A < I_Q < 2 A$          |

#### **Test Circuit**

### **Timing Diagram**

Semiconductor Group

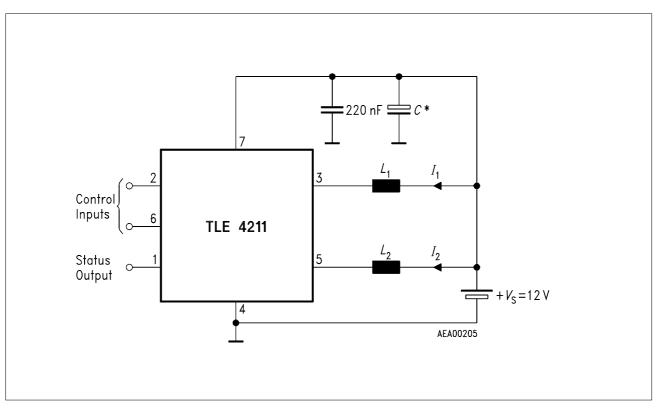

#### **Application Circuit**

$C^*$  is to be dimensioned such that e.g. in case of a battery voltage failure the maximum ratings of the IC are not exceeded by the recirculation energy  $L_1$ ,  $L_2$ .

Output Voltage  $V_{q}$ versus Output Current  $I_{q}$

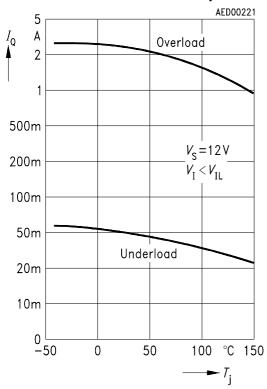

# Status Signal Threshold versus Chip Temperature $T_i$

# Maximum Load Current $I_{L}$ versus Load Inductance L

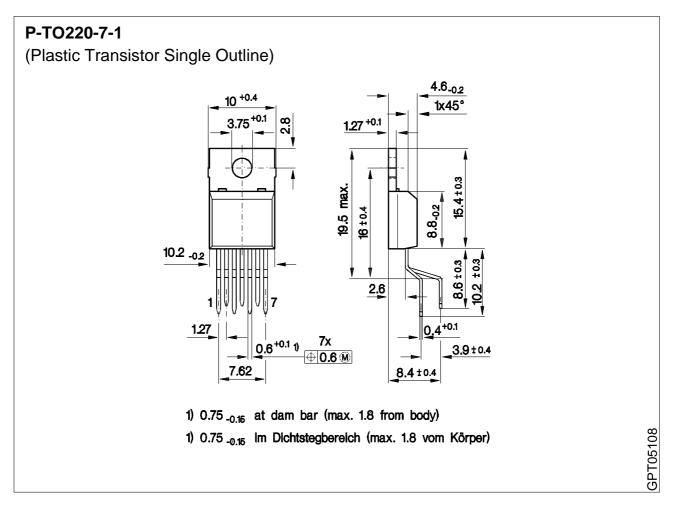

#### **Package Outlines**

#### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Dimensions in mm