## **General Description**

The MAX4886 high-speed analog switch is ideal for HDMI/DVI switching applications, permitting 2:1 or 1:2 switching. The MAX4886 contains four differential pairs of 1:2 or 2:1 switches for RGB and clocking signals. The MAX4886 connects either one monitor to one of two digital video signals, or one HDMI/DVI source to one of two loads (sink).

The MAX4886 set of differential switches is based on an nFET architecture with internal charge pump for gate overdrive. This advanced architecture results in an extremely low capacitance and on-resistance needed for the excellent return loss requirements for digital switching. An efficient internal charge-pump design offers very low quiescent current for power-sensitive notebook designs.

The MAX4886 features  $8\Omega$  (typ) on-resistance and 2.5pF on-capacitance switches for routing RGB and CLK video signals. The MAX4886 is a high-frequency companion device to the MAX4929. These two devices combined perform the full 2:1 HDMI/DVI switching function.

The MAX4886 is available in a space-saving, 42-pin, 3.5mm x 9.0mm TQFN package and operates over the extended -40°C to +85°C temperature range.

## **Applications**

**HDTV Monitors/Receivers** Video Projectors **Notebook Computers** Digital HDTV Switch Boxes/Tuners Multimedia Audio/Video Switchers Servers/Routers with DVI Interfaces Digital Video Recorders LVDS Switching 1000 Base-BX, Switching

**Features**

♦ Single +3.0V to +3.6V Power Supply

♦ Low On-Resistance (Ro<sub>N</sub>): 8Ω (typ)

♦ Low On-Capacitance (CoN): 2.5pF (typ)

♦ Low Skew: 20ps (typ)

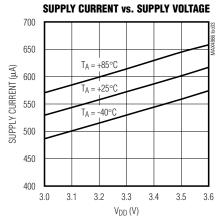

♦ 700µA Low Supply Current

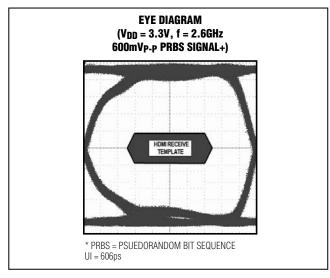

◆ 2.6GHz (typ) Ultra-High Bandwidth

♦ 0.6dB (typ) Ultra-Low Insertion Loss

♦ High-Frequency Companion Device to MAX4929

♦ Use MAX4886 and MAX4929 to Form a Complete HDMI/DVI 2:1 Switch

♦ 42-Pin, 3.5mm x 9.0mm, Space-Saving TQFN

### **Ordering Information**

| PART        | TEMP RANGE     | EMP RANGE PIN-<br>PACKAGE |            |

|-------------|----------------|---------------------------|------------|

| MAX4886ETO+ | -40°C to +85°C | 42 TQFN-EP*               | T42359OM-1 |

<sup>+</sup>Denotes a lead-free package.

## **Eye Diagram**

Pin Configuration appears at end of data sheet.

<sup>\*</sup>EP = Exposed paddle.

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                                                             | Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>42-Pin Thin QFN-EP (derate 35.7mW/°C above |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| VDD0.3V to +4V                                                                                |                                                                                                     |  |  |

| SEL (Note 1)0.3V to (V <sub>DD</sub> + 0.3V)<br>COM , NC , NO0.3V to (V <sub>DD</sub> + 0.3V) | +70°C)2857.1mW<br>Operating Temperature Range40°C to +85°C                                          |  |  |

| Continuous Current Through Any Switch±120mA                                                   | Storage Temperature Range65°C to +150°C                                                             |  |  |

| Peak Current Through Any Switches                                                             | Junction Temperature+150°C                                                                          |  |  |

| (Pulsed at 1ms, 10% duty cycle)±240mA                                                         | Lead Temperature (soldering, 10s)+300°C                                                             |  |  |

|                                                                                               |                                                                                                     |  |  |

Note 1: Signal exceeding Vpp or GND are clamped by internal diodes. Limit forward-diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VDD = +3.0V to +3.6V, TA = TMIN to TMAX. Typical values are at VDD = +3.3V, TA = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                | SYMBOL                 | CONDITIONS                                                                                       |                              | MIN | TYP  | MAX  | UNITS |  |

|--------------------------|------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-----|------|------|-------|--|

| Supply Voltage Range     | V <sub>DD</sub>        |                                                                                                  |                              | 3.0 |      | 3.6  | V     |  |

| Quiescent Supply Current | I <sub>DD</sub>        | $+3V \le V_{DD} \le +3.6V$ ; SEL = 0V or $V_{DD}$                                                |                              |     | 600  | 1100 | μΑ    |  |

| ANALOG SWITCH            |                        |                                                                                                  |                              |     |      |      |       |  |

|                          |                        | V <sub>DD</sub> = +3V, 0V ≤ V <sub>COM</sub> _<br>≤ V <sub>DD</sub> , I <sub>COM</sub> _ = -40mA | $T_A = +25^{\circ}C$         |     | 8    | 11   | Ω     |  |

| On Decistance (Nets 2)   | Davi                   |                                                                                                  | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 15   |       |  |

| On-Resistance (Note 3)   | Ron                    | $V_{DD} = +3V$ ,                                                                                 | $T_A = +25^{\circ}C$         |     | 8    | 11   |       |  |

|                          |                        | $I_{COM} = -40$ mA,<br>$0 \le V_{COM} \le 1.5$ V                                                 | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 15   |       |  |

|                          |                        | $V_{DD} = +3V, 1.5V$                                                                             | $T_A = +25^{\circ}C$         |     | 0.28 | 0.40 | Ω     |  |

| On-Resistance Matching   |                        | ≤ V <sub>COM</sub> ≤ V <sub>DD</sub> ,<br>I <sub>COM</sub> = -40mA                               | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 0.8  |       |  |

| (Notes 3, 4)             | ΔRon                   | V <sub>DD</sub> = +3V, 0 ≤ V <sub>COM</sub> _<br>≤ 1.5V, I <sub>COM</sub> _= -40mA               | T <sub>A</sub> = +25°C       |     | 0.28 | 0.40 |       |  |

|                          |                        |                                                                                                  | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 0.8  |       |  |

|                          |                        | $V_{DD} = +3V$ ,                                                                                 | $T_A = +25^{\circ}C$         |     | 0.02 | 0.60 | Ω     |  |

| On-Resistance Flatness   | D                      | I <sub>COM</sub> _ = -40mA,<br>1.5V < V <sub>COM</sub> _ < V <sub>DD</sub>                       | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 1    |       |  |

| (Note 3)                 | R <sub>FLAT</sub> (ON) | V <sub>DD</sub> = +3V,                                                                           | $T_A = +25^{\circ}C$         |     | 0.02 | 0.60 |       |  |

|                          |                        | $I_{COM} = -40 \text{mA},$<br>$0 \le V_{COM} \le 1.5 \text{V}$                                   | $T_A = T_{MIN}$ to $T_{MAX}$ |     |      | 1    |       |  |

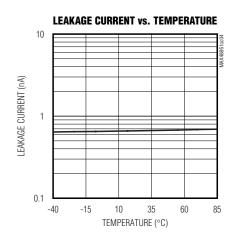

| Leakage Current          | IL                     | $V_{DD} = +3.6V, V_{COM} = +0.3V, +3.3V, V_{NC} \text{ or } V_{NO} = +3.3V, 0.3V$                |                              | -1  |      | +1   | μΑ    |  |

| SWITCH DYNAMIC           |                        |                                                                                                  |                              |     |      |      |       |  |

| Off-Capacitance          | C <sub>OFF</sub>       | $f = 1MHz$ , $V_{COM} = V_{NC}$ or $V_{NO}$ 1.5                                                  |                              |     | 1.5  |      | рF    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.0 \text{V to } +3.6 \text{V}, T_A = T_{MIN} \text{ to } T_{MAX}. \text{ Typical values are at } V_{DD} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                 | SYMBOL             | CONDITIONS                                                                          | MIN   | TYP | MAX | UNITS |  |  |

|---------------------------|--------------------|-------------------------------------------------------------------------------------|-------|-----|-----|-------|--|--|

| On-Capacitance            | Con                | f = 1MHz, V <sub>COM</sub> = V <sub>NC</sub> or V <sub>NO</sub>                     | 2.5   |     | рF  |       |  |  |

| Propagation Delay         | tPD1, tPD2         | $R_S = R_L = 50\Omega$ (Figure 2)                                                   | 100   |     | ps  |       |  |  |

| Output Skew Between Ports | tskew1             | Skew between any two ports, $R_S = R_L = 50\Omega$ (Figure 3)                       | 20    |     | ps  |       |  |  |

| Skew Between Same Ports   | tskew2             | $R_S = R_L = 50\Omega$ , skew between any two ports (Figure 3)                      | 20    |     | ps  |       |  |  |

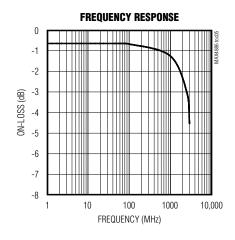

| SWITCH AC PERFORMANCE     |                    |                                                                                     |       |     |     |       |  |  |

| On-Channel -3dB Bandwidth | BW                 | $R_S = R_L = 50\Omega$ (Figure 4)                                                   | 2.6   |     |     | GHz   |  |  |

| Insertion Loss            | ILOS               | $R_S = R_L = 50\Omega$ , $f = 50MHz$ (Figure 4)                                     | 0.6   |     | dB  |       |  |  |

| Off-Isolation             | VISO               | $R_S = R_L = 50\Omega$ , single-ended, f = 50MHz (Figure 4)                         | -58   |     | dB  |       |  |  |

| Crosstalk                 | V <sub>CT1</sub>   | Crosstalk between any two switches, $R_S = R_L = 50\Omega$ , $f = 50MHz$ (Figure 4) | -49   |     | dB  |       |  |  |

| LOGIC INPUTS (SEL)        | LOGIC INPUTS (SEL) |                                                                                     |       |     |     |       |  |  |

| Input-Low Voltage         | VIL                | $V_{DD} = +3.0V$                                                                    | OV    |     | 0.8 | V     |  |  |

| Input-High Voltage        | VIH                | V <sub>DD</sub> = +3.6V                                                             | 2.0   |     | V   |       |  |  |

| Input-Voltage Hysteresis  | V <sub>HYST</sub>  |                                                                                     | 100   |     | mV  |       |  |  |

| Input Leakage Current     | ILEAK              | $V_{DD} = +3.6V$ , $V_{COM}$ or $V_{NC}$ or $V_{NO} = 0V$                           | -1 +1 |     | μΑ  |       |  |  |

Note 2: Maximum and minimum limits over temperature are guaranteed by design and characterization. Device is production tested at  $T_A = +25$ °C.

Note 3: Negative current is going into COM\_ and out of NO\_ or NC\_.

Note 4: Guaranteed by design.

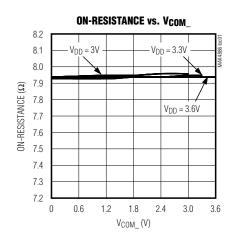

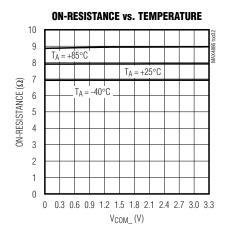

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Pin Description**

| PIN                                    | NAME            | FUNCTION                                                                                            |  |  |  |  |  |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1, 4, 10, 14,<br>17, 19, 21,<br>39, 41 | GND             | Ground                                                                                              |  |  |  |  |  |

| 5, 8, 13, 18,<br>20, 30, 40,<br>42     | V <sub>DD</sub> | Power-Supply Voltage Input. Bypass V <sub>DD</sub> to GND with a 0.1µF or larger ceramic capacitor. |  |  |  |  |  |

| 2                                      | COM1+           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 3                                      | COM1-           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 6                                      | COM2+           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 7                                      | COM2-           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 9                                      | SEL             | Select Input. Logic input for switch connection (see Table 1).                                      |  |  |  |  |  |

| 11                                     | COM3+           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 12                                     | COM3-           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 15                                     | COM4+           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 16                                     | COM4-           | Data Signal Inputs/Outputs                                                                          |  |  |  |  |  |

| 22                                     | NO4-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 23 NO4+ Diffe                          |                 | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 24 NO3-                                |                 | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 25                                     | NO3+            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 26                                     | NC4-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 27                                     | NC4+            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 28                                     | NC3-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 29                                     | NC3+            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 31                                     | NO2-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 32                                     | NO2+            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 33                                     | NO1-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 34 NO1+ Differential Pa                |                 | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 35 NC2- Differe                        |                 | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 36 NC2+ Differential Pair.             |                 | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 37                                     | NC1-            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| 38                                     | NC1+            | Differential Pair. Data Signal Inputs/Outputs.                                                      |  |  |  |  |  |

| EP                                     | EP              | Exposed Paddle. Connect EP to GND.                                                                  |  |  |  |  |  |

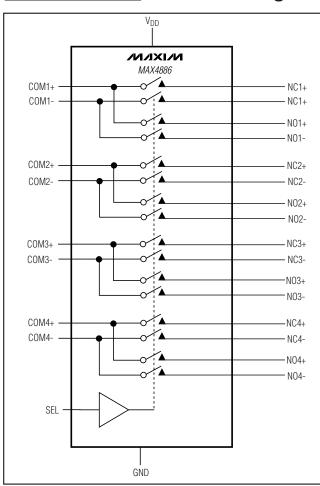

### Functional Diagram

## **Detailed Description**

The MAX4886 high-speed analog switch is ideal for HDMI/DVI switching applications, permitting 2:1 or 1:2 switching. The MAX4886 contains four differential pairs for HDMI or DVI switching. The MAX4886 connects either one monitor to one of two digital video signals or one HDMI/DVI output to one of two connectors or loads.

The MAX4886 differential switches are based on an nFET architecture with an internal charge pump for gate overdrive. This advanced architecture results in an extremely low capacitance and on-resistance needed for an excellent returns loss.

The MAX4886 features an  $8\Omega$  (typ) on-resistance and 2.5pF on-capacitance switches for routing RGB and CLK video signals.

Table 1. Switch Truth Table

| SEL |   | FUNCTION    |

|-----|---|-------------|

|     | 0 | COM_ to NC_ |

|     | 1 | COM_ to NO_ |

The MAX4886 switches are identical, and any of the switches can be used to route RGB and CLK video signals.

The device will also be useful in other high-speed switching applications such as LVDS and LVPECL.

### **Analog-Signal Levels**

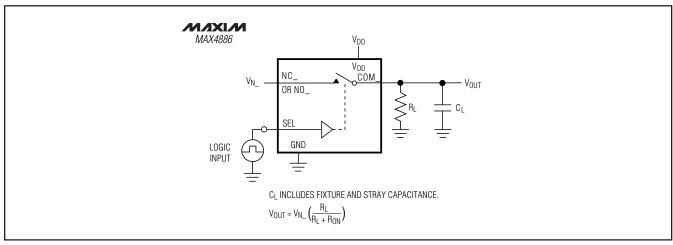

Signal inputs over the full voltage range (0V to V<sub>DD</sub>) are passed through the switch with minimal change in on-resistance (see the *Typical Operating Characteristics* section). The switches are bidirectional. Therefore, COM\_, NC\_, and NO\_ can be either inputs or outputs.

### **Logic Inputs (SEL)**

The MAX4886 has a logic input that controls the switch on/off function. Use SEL to switch COM\_ to NO\_ or COM\_ to NC\_. Table 1 and the *Functional Diagram* illustrate the MAX4886 Truth Table.

## **Applications Information**

### **Power-Supply Bypassing and Sequencing**

Proper power-supply sequencing is recommended for all CMOS devices. Do not exceed the absolute maximum ratings, because stresses beyond the listed ratings can cause permanent damage to the device. Always sequence  $V_{DD}$  on first, followed by the switch inputs and the logic inputs. Bypass at least one  $V_{DD}$  input to ground with a  $0.1\mu F$  capacitor as close to the device as possible. Use the smallest physical size possible for optimal performance.

It is also recommended to bypass more than one  $V_{DD}$  input. A good strategy is to bypass one  $V_{DD}$  input with a  $0.1\mu F$  capacitor and at least a second  $V_{DD}$  input with a 1nF to 10nF capacitor. (Use 0603 or smaller physical size ceramic capacitor).

### PC Board (PCB) Layout

High-speed switches such as the MAX4886 require proper PCB layout for optimum performance. Ensure that impedance-controlled PCB traces for high-speed signals are matched in length, and as short as possible. Connect the MAX4886 exposed paddle to a solid ground plane.

## **Timing Circuits/Timing Diagrams**

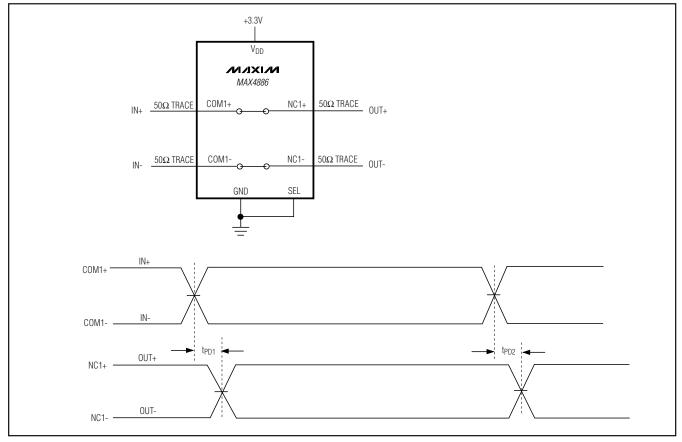

Figure 1. Switching Time

Figure 2. Propagation Delay

## Timing Circuits/Timing Diagrams (continued)

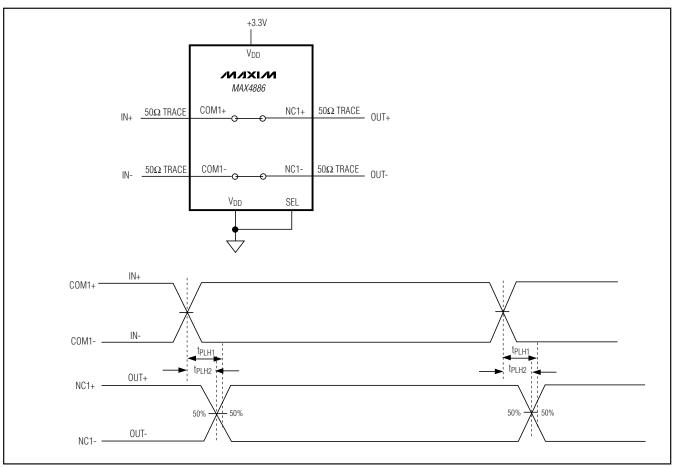

Figure 3. Skew Measurements

## Additional Applications Information

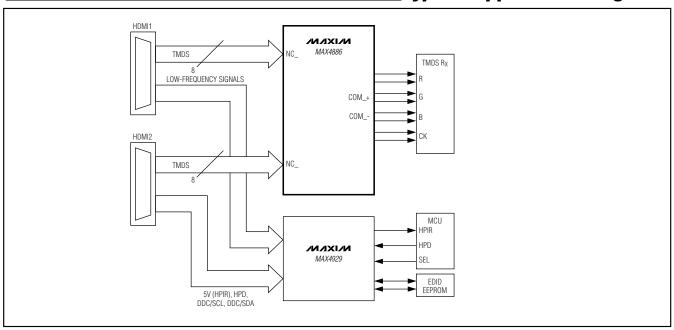

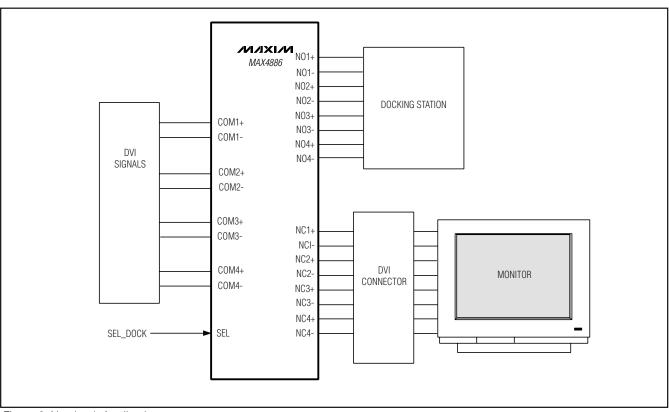

In a typical application (see Figure 5), the MAX4886 and MAX4929 are used to route the TMDS signals and low-frequency signals between two HDMI inputs.

In another application (see Figure 6), the MAX4886 is used in a notebook to route high-frequency DVI port on the computer or to the connector on the docking station. The MAX4886 routes four differential signals (RGB and CLK) either to the DVI connector or to the docking station port. The switch is inherently bilateral and may be used as a 2:1 or 1:2 mux without penalties.

**Chip Information**

PROCESS: BiCMOS

Connect exposed paddle to GND.

## Timing Circuits/Timing Diagrams (continued)

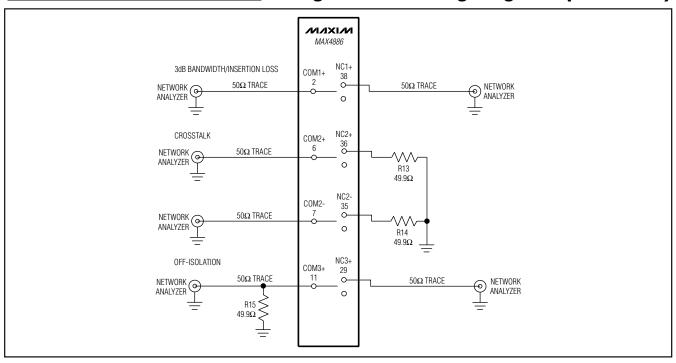

Figure 4. On-Loss, Off-Isolation, and Crosstalk

## **Typical Application Diagrams**

Figure 5. TV/Monitor Application

## **Typical Application Diagrams (continued)**

Figure 6. Notebook Application

## **Pin Configuration**

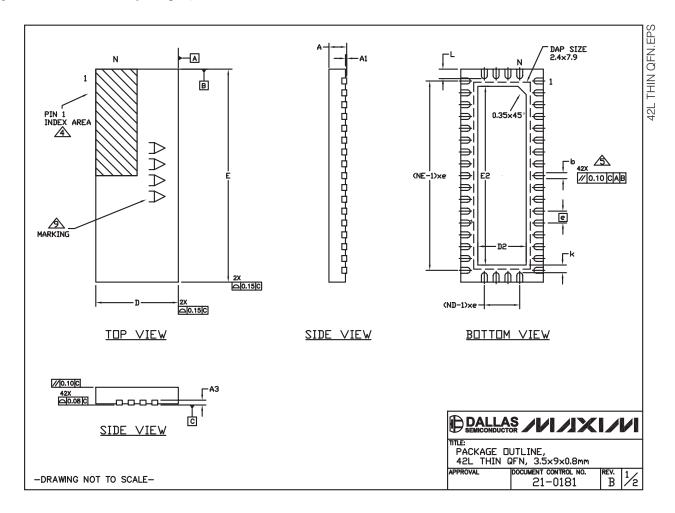

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

|      | COMMO | N DIMEN | ZNDIZN |             |

|------|-------|---------|--------|-------------|

| REF. | MIN.  | N□M.    | MAX.   | NOTE        |

| Α    | 0.70  | 0.75    | 0.80   |             |

| A1   | 0     | -       | 0.05   |             |

| A3   | C     |         |        |             |

| b    | 0.20  | 0.25    | 0.30   |             |

| D    | 3,40  | 3,50    | 3.60   |             |

| Ε    | 8.90  | 9.00    | 9.10   |             |

| е    | C     | .50 BSC | ,      |             |

| k    | 0.25  | -       | _      |             |

| L    | 0.35  | 0.40    | 0.45   | ALL<br>PINS |

| N    |       |         |        |             |

| ND   | 4     |         |        |             |

| NE   |       |         |        |             |

|            | EXPOSED PAD VARIATIONS |      |      |      |      |      |

|------------|------------------------|------|------|------|------|------|

|            |                        | 1)2  |      | E2   |      |      |

| PKG. CODE  | MIN.                   | N□M. | MAX. | MIN. | N□M. | MAX. |

| T423590-1  | 1.95                   | 2.05 | 2.15 | 7.45 | 7.55 | 7.65 |

| T423590M-1 | 1.95                   | 2.05 | 2.15 | 7.45 | 7.55 | 7.65 |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

1. THE TERMINAL \*1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL \*1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL \*1 IDENTIFIER ARE OPTIONAL \*1 THE TERMINAL \*1 IDENTIFIER AND TH IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- ⚠ DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

- $\triangle$  ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS, COPLANARITY SHALL NOT EXCEED 0.08mm.

- WARPAGE SHALL NOT EXCEED 0.10mm.

- MARKING IS FOR PACKAGE ORIENTATION PURPOSE ONLY.

- LEAD CENTERLINES TO BE AT DEFINED BY DIMESION e ±0.05.

-DRAWING NOT TO SCALE-

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.