# **RapidIO MegaCore Function**

# **User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-MC\_RIOPHY-2.16

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

# **Contents**

| Chapter 1. About This MegaCore Function                                     |      |

|-----------------------------------------------------------------------------|------|

| Features                                                                    | 1-1  |

| RapidIO IP Core Features                                                    | 1-2  |

| Supported Transactions                                                      | 1–3  |

| Device Family Support                                                       | 1-4  |

| IP Core Verification                                                        | 1-5  |

| Simulation Testing                                                          | 1-5  |

| Hardware Testing                                                            | 1-5  |

| Interoperability Testing                                                    | 1-6  |

| Performance and Resource Utilization                                        | 1-6  |

| Release Information                                                         | 1–11 |

| Installation and Licensing                                                  | 1–12 |

| OpenCore Plus Evaluation                                                    | 1–12 |

| OpenCore Plus Time-Out Behavior                                             | 1–13 |

| Chapter 2. Getting Started                                                  |      |

| Design Flows                                                                | 2–1  |

| MegaWizard Plug-In Manager Design Flow                                      | 2–2  |

| SOPC Builder Design Flow                                                    |      |

| Qsys Design Flow                                                            |      |

| MegaWizard Plug-In Manager Design Flow                                      | 2–3  |

| Specifying Parameters                                                       |      |

| Simulating the Design                                                       |      |

| SOPC Builder Design Flow                                                    | 2-5  |

| Specifying Parameters                                                       | 2–6  |

| Completing the SOPC Builder System                                          | 2–7  |

| Simulating the System                                                       | 2-8  |

| Qsys Design Flow                                                            | 2-9  |

| Specifying Parameters                                                       |      |

| Completing the Qsys System                                                  | 2–10 |

| Simulating the System                                                       |      |

| Specifying Constraints                                                      |      |

| Compiling the Full Design and Programming the FPGA                          |      |

| Instantiating Multiple RapidIO IP Cores                                     |      |

| Clock and Signal Requirements for Arria V, Cyclone V, and Stratix V Devices |      |

| Clock and Signal Requirements for Other Devices with Transceivers           |      |

| Sourcing Multiple Tcl Scripts                                               | 2–16 |

| Chapter 3. Parameter Settings                                               |      |

| Physical Layer Settings                                                     | 3–1  |

| Device Options                                                              | 3–1  |

| Mode Selection                                                              | 3–2  |

| Transceiver Selection                                                       | 3-2  |

| Transceiver Configuration                                                   | 3–3  |

| Synchronizing Transmitted ackID                                             | 3-5  |

| Sending Link-Request Reset-Device on Fatal Errors                           |      |

| Number of Link-Request Attempts Before Declaring Fatal Error                |      |

| Data Settings                                                               | 3-6  |

iv Contents

| Baud Rate                                     | 3–6  |

|-----------------------------------------------|------|

| Reference Clock Frequency                     |      |

| Receive Buffer                                |      |

| Transmit Buffer                               | 3–6  |

| Receive Priority Retry Thresholds             | 3–6  |

| Transport and Maintenance Settings            |      |

| Transport Layer                               |      |

| Enable Transport Layer                        | 3–7  |

| Device ID Width                               | 3–7  |

| Avalon-ST Pass-Through Interface              | 3–7  |

| Destination ID Checking                       | 3–8  |

| Input/Output Maintenance Logical Layer Module | 3–8  |

| Maintenance Logical Layer                     |      |

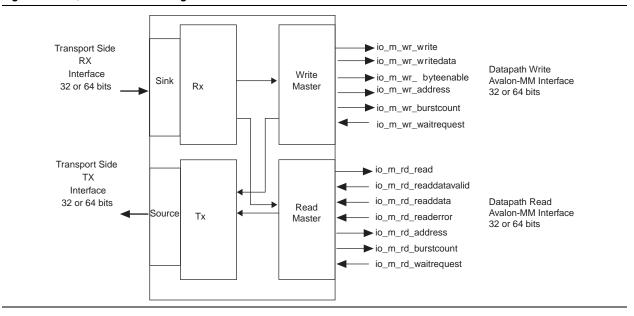

| Transmit Address Translation Windows          |      |

| Port Write                                    | 3–9  |

| Port Write Tx Enable                          | 3–9  |

| Port Write Rx Enable                          | 3–9  |

| I/O and Doorbell Settings                     | 3–9  |

| I/O Logical Layer Interfaces                  | 3–9  |

| I/O Slave Address Width                       |      |

| I/O Read and Write Order Preservation         | 3–9  |

| Avalon-MM Master                              | 3–10 |

| Avalon-MM Slave                               | 3–10 |

| Doorbell Slave                                | 3–10 |

| Capability Registers Settings                 | 3–10 |

| Device Registers                              |      |

| Device ID                                     |      |

| Vendor ID                                     | 3–11 |

| Revision ID                                   | 3–11 |

| Assembly Registers                            | 3–11 |

| Assembly ID                                   | 3–11 |

| Vendor ÍD                                     | 3–11 |

| Revision ID                                   | 3–11 |

| Extended Features Pointer                     | 3–12 |

| Processing Element Features                   | 3–12 |

| Bridge Support                                | 3–12 |

| Memory Access                                 | 3–12 |

| Processor Present                             | 3–12 |

| Switch Support                                |      |

| Enable Switch Support                         | 3–12 |

| Number of Ports                               | 3–12 |

| Port Number                                   |      |

| Data Messages                                 |      |

| Source Operation                              |      |

| Destination Operation                         |      |

| EDA Settings                                  |      |

| Simulation Libraries                          |      |

| File                                          |      |

| Description                                   |      |

| Generate Simulation Model                     |      |

| Timing and Resource Estimation                |      |

| Summary                                       | 3–14 |

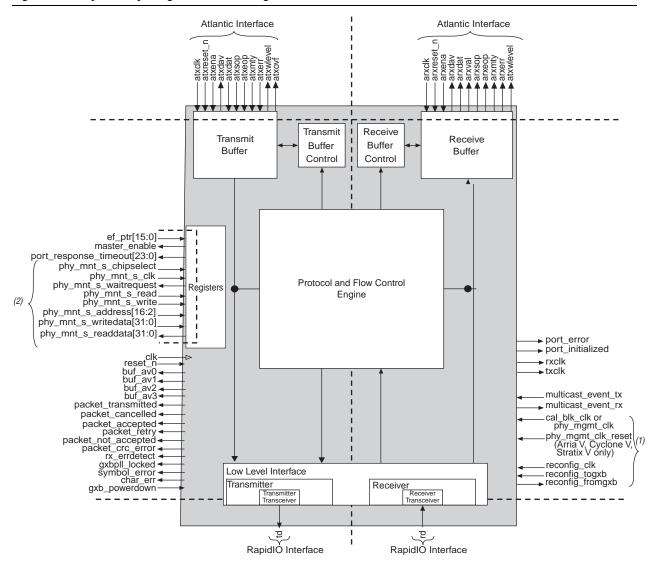

| Chapter 4. Functional Description                                          |      |

|----------------------------------------------------------------------------|------|

| Interfaces                                                                 |      |

| RapidIO Interface                                                          |      |

| Atlantic Interface                                                         |      |

| Avalon Memory Mapped (Avalon-MM) Master and Slave Interfaces               |      |

| Avalon-MM Interface Byte Ordering                                          |      |

| Avalon Streaming (Avalon-ST) Interface                                     |      |

| XGMII External Transceiver Interface                                       | 4-3  |

| Clocking and Reset Structure                                               |      |

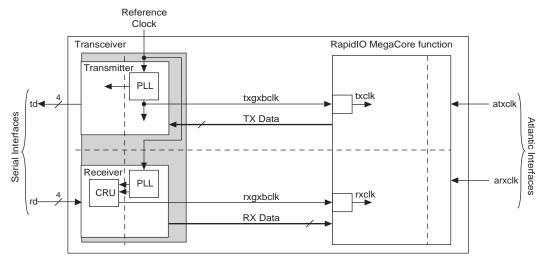

| Clocking for RapidIO IP Cores with Only a Physical Layer                   |      |

| Reference Clock                                                            |      |

| Baud Rates                                                                 |      |

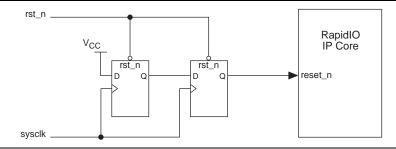

| Reset for RapidIO IP Cores with Only a Physical Layer                      |      |

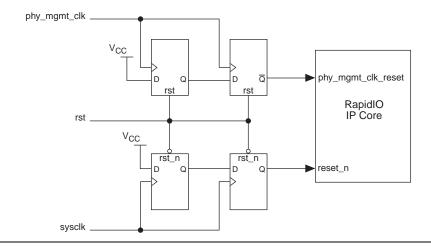

| Clocking for RapidIO IP Cores with Physical, Transport, and Logical Layers |      |

| Reset for RapidIO IP Cores with Physical, Transport, and Logical Layers    |      |

| Physical Layer                                                             |      |

| Features                                                                   |      |

| Physical Layer Architecture                                                |      |

| Low-level Interface Receiver                                               |      |

| Receiver Transceiver                                                       |      |

| CRC Checking and Removal                                                   |      |

| Low-Level Interface Transmitter                                            |      |

| Transmitter Transceiver in Variations With an Internal Transceiver         |      |

| Protocol and Flow Control Engine                                           |      |

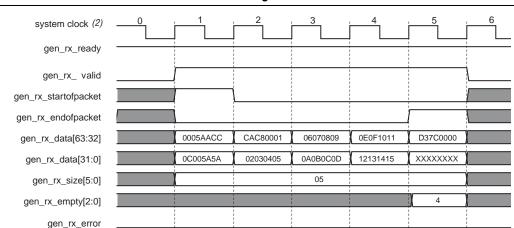

| Atlantic Interface                                                         |      |

| Atlantic Interface Receive Buffer and Control Block                        |      |

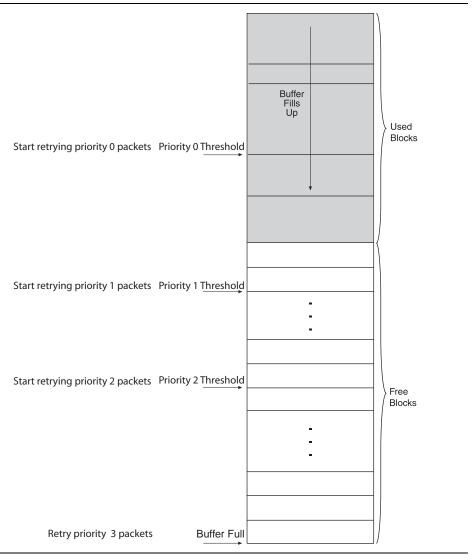

| Priority Threshold Values                                                  |      |

| Atlantic Interface Transmit Buffer and Control Block                       |      |

| Transmit and Retransmit Queues                                             |      |

| Transmit Buffer                                                            |      |

| Forced Compensation Sequence Insertion                                     |      |

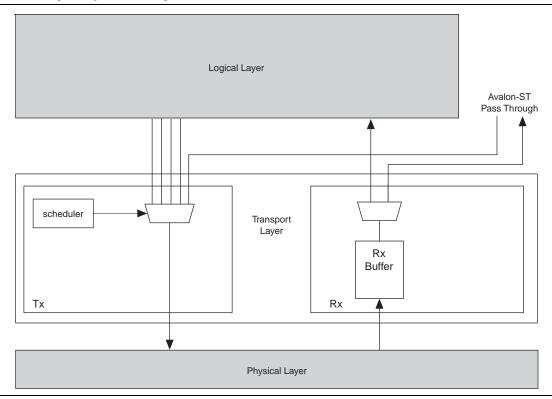

| Transport Layer                                                            |      |

| Receiver                                                                   |      |

| Transaction ID Ranges                                                      |      |

| Transmitter                                                                |      |

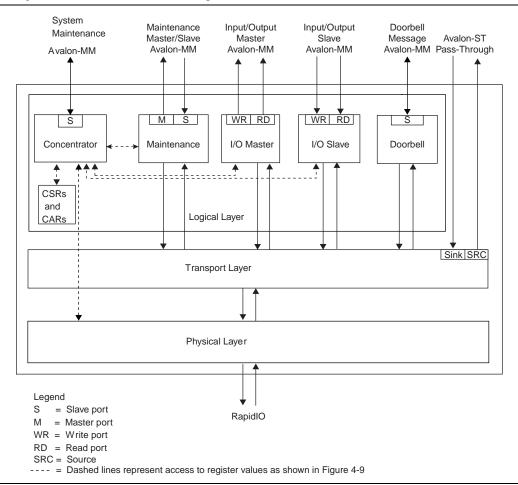

| Logical Layer Modules                                                      |      |

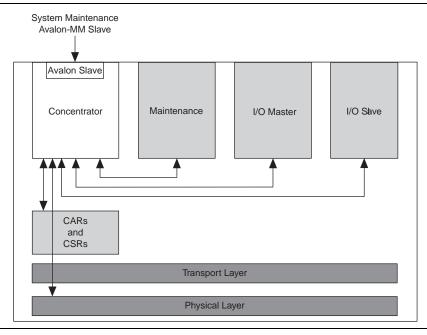

| Concentrator Register Module                                               |      |

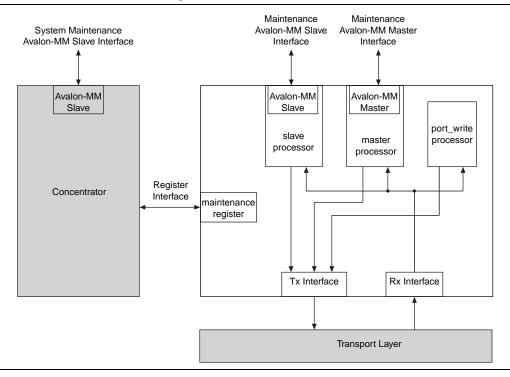

| Maintenance Module                                                         |      |

| Maintenance Register                                                       |      |

| Maintenance Slave Processor                                                |      |

| Maintenance Master Processor                                               |      |

| Port-Write Processor                                                       |      |

| Maintenance Module Error Handling                                          |      |

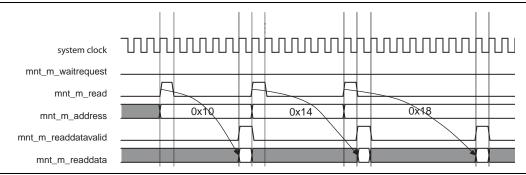

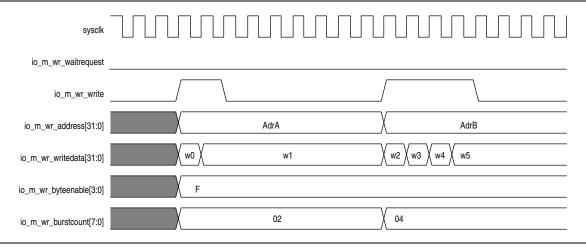

| Input/Output Logical Layer Modules                                         |      |

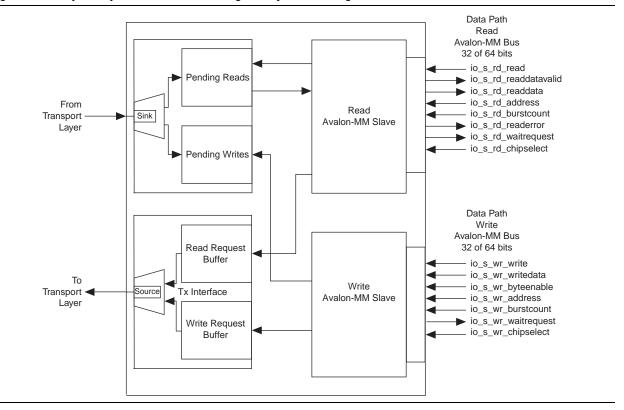

| Input/Output Avalon-MM Master Module                                       |      |

| RapidIO Packet Data wdptr and Data Size Encoding in Avalon-MM Transactions |      |

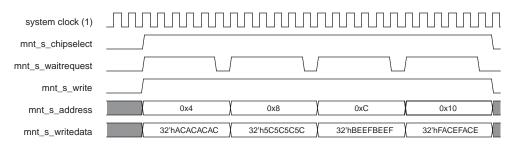

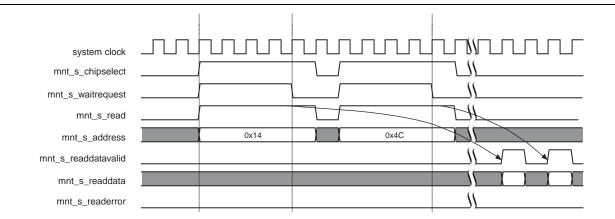

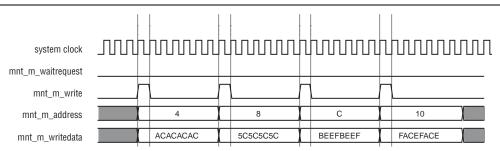

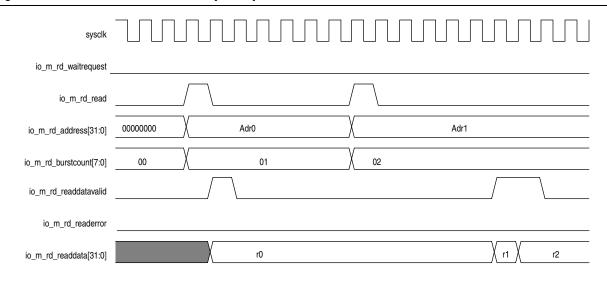

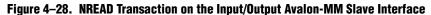

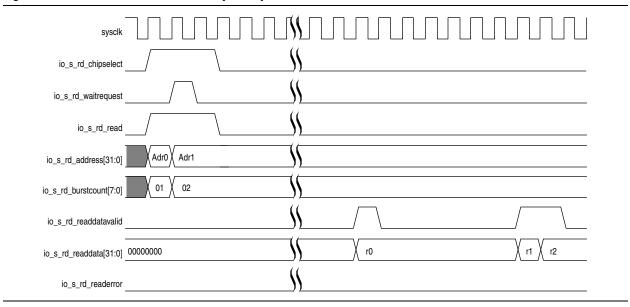

| Input/Output Avalon-MM Master Module Timing Diagrams                       | 4-43 |

| Input/Output Avalon-MM Slave Module                                        | 4–44 |

| Avalon-MM Burstcount and Byteenable Encoding in RapidIO Packets            |      |

| Input/Output Avalon-MM Slave Module Timing Diagrams                        |      |

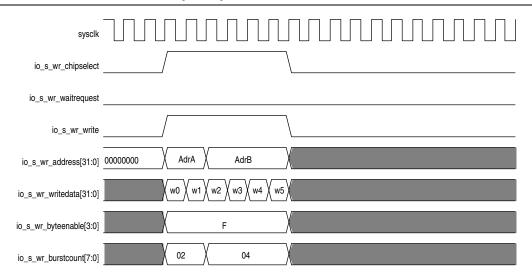

| Doorbell Module                                                            | 4-56 |

| Doorbell Module Block Diagram                                              |      |

| Preserving Transaction Order                                               | 4–57 |

vi Contents

|                                                                        | 4 ==  |

|------------------------------------------------------------------------|-------|

| Doorbell Message Generation                                            |       |

| Doorbell Message Reception                                             |       |

| Avalon-ST Pass-Through Interface                                       |       |

| Pass-Through Interface Examples                                        |       |

| Error Detection and Management                                         |       |

| Physical Layer Error Management                                        | 4–64  |

| Protocol Violations                                                    |       |

| Fatal Errors                                                           |       |

| Logical Layer Error Management                                         |       |

| Maintenance Avalon-MM Slave                                            |       |

| Maintenance Avalon-MM Master                                           |       |

| Port-Write Reception Module                                            |       |

| Port-Write Transmission Module                                         |       |

| Input/Output Avalon-MM Slave                                           |       |

| Input/Output Avalon-MM Master                                          |       |

| Avalon-ST Pass-Through Interface                                       | 4–70  |

| Ohantor E. Cianala                                                     |       |

| Chapter 5. Signals                                                     |       |

| Physical Layer Signals                                                 |       |

| Atlantic Interface Signals                                             | . 5–4 |

| Status Packet and Error Monitoring Signals                             | . 5–6 |

| Multicast Event Signals                                                | . 5–7 |

| Receive Priority Retry Threshold-Related Signals                       |       |

| Transceiver Signals                                                    |       |

| Register-Related Signals                                               | 5–11  |

| Transport and Logical Layer Signals                                    |       |

| Clock and Reset Signals                                                |       |

| Avalon-MM Interface Signals                                            |       |

| Avalon-ST Pass-Through Interface Signals                               | 5–14  |

| Error Management Extension Signals                                     |       |

| Packet and Error Monitoring Signal for the Transport Layer             | 5–18  |

| Chapter 6. Software Interface                                          |       |

| Physical Layer Registers                                               | 6_4   |

| Transport and Logical Layer Registers                                  |       |

| Capability Registers (CARs)                                            |       |

| Command and Status Registers (CSRs)                                    |       |

| Maintenance Interrupt Control Registers                                |       |

| Receive Maintenance Registers                                          |       |

| Transmit Maintenance Registers                                         |       |

| Transmit Port-Write Registers                                          |       |

| Receive Port-Write Registers                                           |       |

| Input/Output Master Address Mapping Registers                          |       |

| Input/Output Master Address Mapping Registers                          |       |

| Input/Output Slave Interrupts                                          |       |

|                                                                        |       |

| Transport Layer Feature Register                                       |       |

| Error Management Registers                                             |       |

| Doorbell Message Registers                                             | υ–2b  |

| Chapter 7. Testbenches                                                 |       |

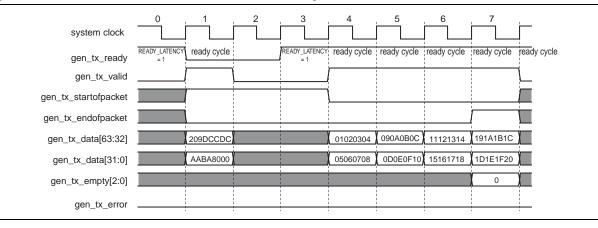

| Testbench for Variations with Only a Physical Layer                    | . 7–1 |

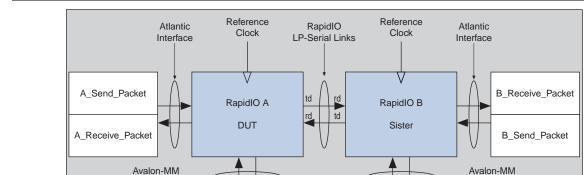

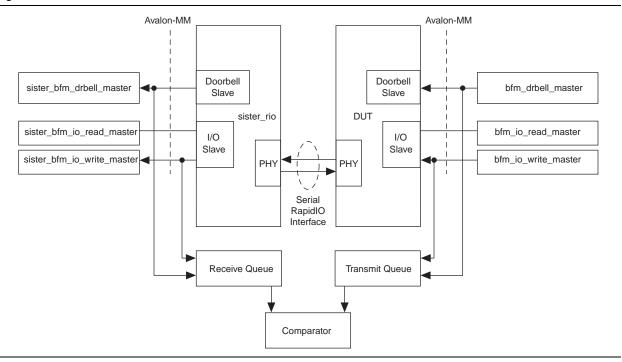

| Testbench for a Variation with Physical, Transport, and Logical Layers |       |

| Reset, Initialization, and Configuration                               | . 7–6 |

| Maintenance Write and Read Transactions                                      |            |

|------------------------------------------------------------------------------|------------|

| SWRITE Transactions                                                          | 7–8        |

| NWRITE_R Transactions                                                        | 7–9        |

| NWRITE Transactions                                                          | 7–10       |

| NREAD Transactions                                                           | 7–10       |

| Doorbell Transactions                                                        |            |

| Doorbell and Write Transactions With Transaction Order Preservation          | 7–12       |

| Port-Write Transactions                                                      |            |

| Transactions Across the Avalon-ST Pass-Through Interface                     | 7–14       |

| Chapter 8. SOPC Builder Design Example                                       |            |

| Creating a New Quartus II Project                                            | 8–3        |

| Running SOPC Builder                                                         |            |

| Adding and Parameterizing the RapidIO Component                              |            |

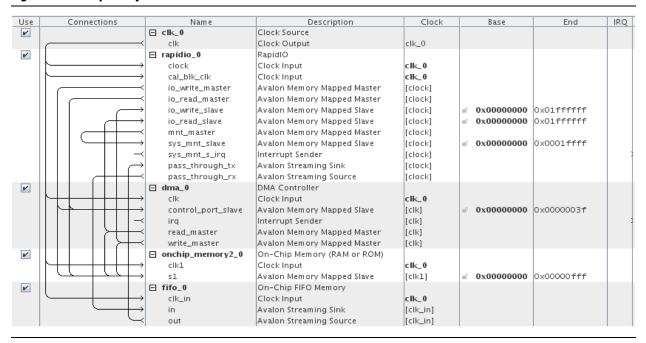

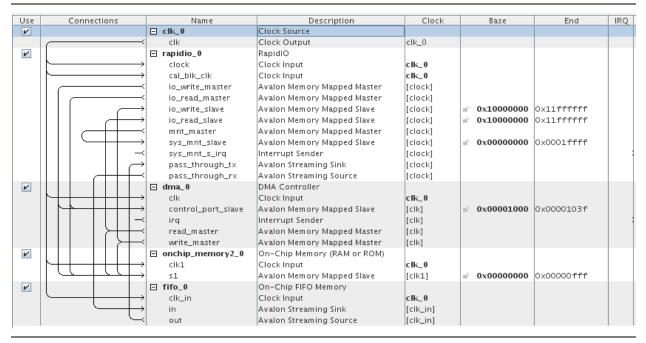

| Adding and Connecting Other System Components                                |            |

| Adding the DMA Controller                                                    |            |

| Adding the On-Chip Memory                                                    |            |

| Adding the On-Chip FIFO Memory                                               |            |

| Connecting the Clocks and the System Components                              |            |

| Displaying Clock Information and Connecting Unconnected Clocks               |            |

| Connecting System Components                                                 |            |

| Assigning Addresses and Setting the Clock Frequency                          |            |

| Generating the System                                                        |            |

| Simulating the System                                                        |            |

| Compiling and Programming the Device                                         |            |

|                                                                              |            |

| Chapter 9. Qsys Design Example                                               |            |

| Creating a New Quartus II Project                                            | 9–2        |

| Running Qsys                                                                 |            |

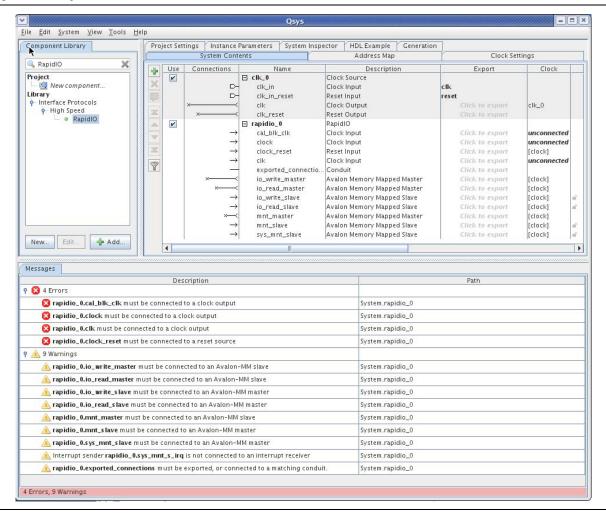

| Adding and Parameterizing the RapidIO Component                              |            |

| Adding and Connecting Other System Components                                |            |

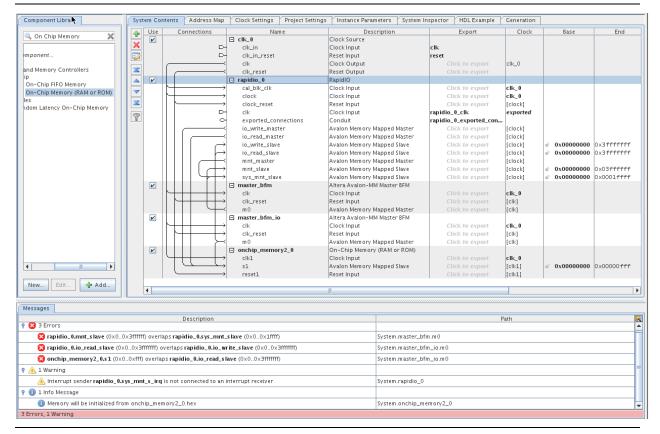

| Adding the Master Maintenance BFM                                            |            |

| Adding the Master I/O BFM                                                    |            |

| Adding the On-Chip Memory                                                    |            |

| Connecting Clocks and the System Components                                  |            |

| Connecting Unconnected Clocks                                                |            |

| Connecting System Components                                                 |            |

| Assigning Addresses and Setting the Clock Frequency                          |            |

| Generating the System                                                        |            |

| Simulating the System                                                        |            |

| Appendix A. Initialization Sequence                                          |            |

|                                                                              |            |

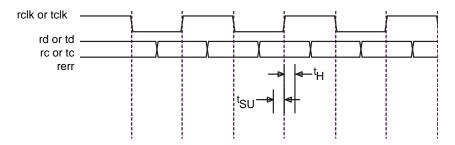

| Appendix B. XGMII Interface Timing                                           |            |

| RapidIO XGMII Interface                                                      | B–1        |

| Timing Constraints                                                           |            |

| Setting Quartus II t <sub>SU</sub> and t <sub>H</sub> Checks                 |            |

| Example                                                                      |            |

|                                                                              | <b>.</b> D |

| Appendix C. Porting a RapidIO Design from the Previous Version of the Softwa | are        |

| Upgrading a RapidIO Design Without Changing Tools                            |            |

| Upgrading an SOPC Builder Design with a RapidIO Component to a Qsys Sy       | rstem C–2  |

|                                                                              |            |

viii Contents

| Appendix D. Calculating Resource Utilization for Modular Configurations |        |

|-------------------------------------------------------------------------|--------|

| Modular Configurations                                                  | D–1    |

| Calculate Estimated ALUTs for Specific Modules                          | D–2    |

| Additional Information                                                  |        |

| Document Revision History                                               | Info–1 |

| How to Contact Altera                                                   | Info–2 |

| Typographic Conventions                                                 | Info-3 |

# 1. About This MegaCore Function

The RapidIO interconnect—an open standard developed by the RapidIO Trade Association—is a high-performance packet-switched interconnect technology designed to pass data and control information between microprocessors, digital signal processors (DSPs), communications and network processors, system memories, and peripheral devices.

The Altera® RapidIO MegaCore® function targets high-performance, multicomputing, high-bandwidth, and coprocessing I/O applications. Figure 1–1 shows an example system implementation.

FPGA Controller Interface Memory Bridge DSP Proprietary, CPRI, OBSAI, Ethernet, etc. System Interconnect RapidIO Memory MegaCore DSP Function ASSP Memory Serial DSP RapidIO **ASSP** Switch Memory DSP ASSP CPU

Figure 1-1. Typical RapidIO Application

## **Features**

This section outlines the features and supported transactions of the RapidIO IP core.

## **RapidIO IP Core Features**

The RapidIO IP core has the following features:

- Compliant with RapidIO Trade Association, RapidIO Interconnect Specification, Revision 2.1, August 2009, available from the RapidIO Trade Association website at www.rapidio.org

- Successfully passed RIOLAB's Device Interoperability Level-3 (DIL-3) testing

- Supports 8-bit or 16-bit device IDs

- Supports incoming and outgoing multi-cast events

#### Physical layer features

- 1x/4x serial with integrated transceivers in selected device families and support for external transceivers in older device families

- All four standard serial data rates supported: 1.25, 2.5, 3.125, and 5.0 gigabaud (Gbaud)

- Receive/transmit packet buffering, flow control, error detection, packet assembly, and packet delineation

- Automatic freeing of resources used by acknowledged packets

- Automatic retransmission of retried packets

- Scheduling of transmission, based on priority

- Reset controller—fatal error does not require manual resetting

- Optional automatic resetting of link partner after detection of fatal errors

- Support for synchronizing with link partner's expected ackID after reset

- Full control over integrated transceiver parameters

- Configurable number of recovery attempts after link response time-out before declaring fatal error

#### Transport layer features

- Supports multiple Logical layer modules

- A round-robin outgoing scheduler chooses packets to transmit from various Logical layer modules

#### Logical layer features

- Generation and management of transaction IDs

- Automatic response generation and processing

- Request to response time-out checking

- Capability registers (CARs) and command and status registers (CSRs)

- Direct register access, either remotely or locally

- Maintenance master and slave Logical layer modules

- Input/Output Avalon® Memory-Mapped (Avalon-MM) master and slave Logical layer modules with burst support

- Avalon streaming (Avalon-ST) interface for custom implementation of message passing

- Doorbell module supporting 16 outstanding DOORBELL packets with time-out mechanism

- Support for preservation of transaction order between outgoing DOORBELL messages and I/O write requests

- New registers and interrupt indicate NWRITE\_R transaction completion

- Support for preservation of transaction order between outgoing I/O read requests and I/O write requests from Avalon-MM interfaces

- SOPC Builder support

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

- Support for OpenCore Plus evaluation

## **Supported Transactions**

The RapidIO IP core supports the following RapidIO transactions:

- NREAD request and response

- NWRITE request

- NWRITE\_R request and response

- SWRITE request

- MAINTENANCE read request and response

- MAINTENANCE write request and response

- MAINTENANCE port-write request

- DOORBELL request and response

# **Device Family Support**

Table 1–1 defines the device support levels for Altera IP cores.

Table 1-1. Altera IP Core Device Support Levels

| FPGA Device Families                                                                                                                                                                                                                                                      | HardCopy Device Families                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary support—The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution. | HardCopy Companion—The IP core is verified with preliminary timing models for the HardCopy companion device. The IP core meets all functional requirements, but might still be undergoing timing analysis for the HardCopy device family. It can be used in production designs with caution. |

| Final support—The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                              | HardCopy Compilation—The IP core is verified with final timing models for the HardCopy device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                                  |

Table 1–2 shows the level of support offered by the Rapid IO IP core for each Altera device family.

Table 1-2. Device Family Support

| Device Family         | Support                                                          |

|-----------------------|------------------------------------------------------------------|

| Arria® GX             | Final                                                            |

| Arria II GX           | Final                                                            |

| Arria II GZ           | Final                                                            |

| Arria V               | Refer to the What's New in Altera IP page of the Altera website. |

| Cyclone® II           | Final                                                            |

| Cyclone III           | Final                                                            |

| Cyclone III LS        | Final                                                            |

| Cyclone IV GX (1)     | Final                                                            |

| Cyclone V             | Refer to the What's New in Altera IP page of the Altera website. |

| HardCopy® II          | HardCopy Compilation                                             |

| HardCopy III          | HardCopy Compilation                                             |

| HardCopy IV E         | HardCopy Compilation                                             |

| HardCopy IV GX        | HardCopy Compilation                                             |

| Stratix® II           | Final                                                            |

| Stratix II GX         | Final                                                            |

| Stratix III           | Final                                                            |

| Stratix IV            | Final                                                            |

| Stratix IV GT         | Final                                                            |

| Stratix V             | Refer to the What's New in Altera IP page of the Altera website. |

| Other device families | No support                                                       |

#### Note to Table 1-2:

(1) The RapidlO IP core supports only the EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Cyclone IV GX devices.

#### **IP Core Verification**

Before releasing a version of the RapidIO IP core, Altera runs comprehensive regression tests in the current version of the Quartus<sup>®</sup> II software. These tests use the MegaWizard<sup>™</sup> Plug-In Manager, SOPC Builder, and the Qsys system integration tool to create the instance files. These files are tested in simulation and hardware to confirm functionality.

Altera also performs interoperability testing to verify the performance of the IP core and to ensure compatibility with ASSP devices.

The RapidIO IP core v9.0 successfully passed RIOLAB's Device Interoperability Level-3 (DIL-3) testing in 2009.

## **Simulation Testing**

Altera verifies the RapidIO IP core using the following industry-standard simulators:

- ModelSim® simulator

- VCS in combination with the Synopsys Native Testbench (NTB)

The test suite contains testbenches that use the RapidIO bus functional model (BFM) from the RapidIO Trade Association to verify the functionality of the IP core.

The regression suite tests various functions, including the following functionality:

- Link initialization

- Packet format

- Packet priority

- Error handling

- Throughput

- Flow control

Constrained random techniques generate appropriate stimulus for the functional verification of the IP core. Functional coverage metrics measure the quality of the random stimulus, and ensure that all important features are verified.

# **Hardware Testing**

Altera tests and verifies the RapidIO IP core in hardware for different platforms and environments.

The hardware tests cover serial 1x and 4x variations running at 1.25, 2.5, 3.125, and 5.0 Gbaud, and processing the following traffic types:

- NREADs of various size payloads—4 bytes to 256 bytes

- NWRITES of various size payloads—4 bytes to 256 bytes

- NWRITE\_Rs of a few different size packets

- SWRITES

- Port-writes

- DOORBELL messages

MAINTENANCE reads and writes

The hardware tests also cover the following control symbol types:

- Status

- Packet-accepted

- Packet-retry

- Packet-not-accepted

- Start-of-packet

- End-of-packet

- Link-request, Link-response

- Stomp

- Restart-from-retry

- Multicast-event

#### **Interoperability Testing**

Altera performs interoperability tests on the RapidIO IP core, which certify that the RapidIO IP core is compatible with third-party RapidIO devices.

Altera performs interoperability testing with processors and switches from various manufacturers including:

- Texas Instruments Incorporated

- Integrated Device Technology, Inc. (IDT)

Testing of additional devices is an on-going process.

In addition, the RapidIO IP core v9.0 successfully passed RIOLAB's Device Interoperability Level-3 (DIL-3) testing in 2009.

## **Performance and Resource Utilization**

This section contains tables showing IP core variation size and performance examples. Appendix D, Calculating Resource Utilization for Modular Configurations outlines ways you can reduce resource utilization to create smaller IP core variations.

Table 1–3 to Table 1–6 list the resources and expected performance for selected variations that use these modules:

- Physical layer with 8 KByte transmit buffers and 4 KByte receive buffers

- Transport layer

- Input/Output Avalon-MM master and slave

The numbers of LEs, combinational ALUTs, and logic registers in Table 1–3 to Table 1–6 are rounded up to the nearest 100.

Table 1–3 shows results obtained using the Quartus II software v11.1 for the following devices:

Cyclone II (EP2C50F484C6)

- Cyclone III (EP3C55F780C6)

- Cyclone IV GX (EP4CGX50CF23C6)

Table 1-3. Serial RapidIO FPGA Resource Utilization I

| Davisa      | Parameters                                       |    |                            | 15.    | Memory:<br>M4K or<br>M9K <sup>(1)</sup> |  |

|-------------|--------------------------------------------------|----|----------------------------|--------|-----------------------------------------|--|

| Device      | Layers Lane Baud Rate (Gbaud)                    |    | LEs                        |        |                                         |  |

|             | Physical layer only                              | 1× | 3.125 with external SERDES | 6,800  | 48                                      |  |

| Ovelene II  | Filysical layer offiy                            | 4× | 1.250 with external SERDES | 10,000 | 55                                      |  |

| Cyclone II  | Physical and<br>Transport layers,                | 1× | 3.125 with external SERDES | 11,800 | 91                                      |  |

|             | and<br>I/O master and slave                      | 4× | 1.250 with external SERDES | 15,100 | 97                                      |  |

|             | Physical layer only                              | 1× | 3.125 with external SERDES | 6,600  | 35                                      |  |

| Ovelene III | Physical layer only                              | 4× | 1.250 with external SERDES | 9,700  | 41                                      |  |

| Cyclone III | Physical and Transport layers,                   | 1× | 3.125 with external SERDES | 11,300 | 70                                      |  |

|             | and<br>I/O master and slave                      | 4× | 1.250 with external SERDES | 14,600 | 77                                      |  |

|             | Dhysical layer only                              | 1× | 3.125                      | 7,600  | 33                                      |  |

|             | Physical layer only                              | 4× | 2.500                      | 10,200 | 32                                      |  |

| Cyclone IV  | Physical and                                     | 1× | 3.125                      | 13,300 | 63                                      |  |

| GX          | Transport layers,<br>and<br>I/O master and slave | 4× | 2.500                      | 16,500 | 63                                      |  |

#### Note to Table 1-3:

Table 1–4 shows results obtained using the Quartus II software v11.1 for a Cyclone V device (5CGXFC7C6F23C6).

Table 1-4. Serial RapidIO FPGA Resource Utilization II (Cyclone V Device)

| Device    | Parameters                                 |      |                   | Combinational                       | Logio | Memory          |   |

|-----------|--------------------------------------------|------|-------------------|-------------------------------------|-------|-----------------|---|

|           | Layers                                     | Mode | Baud Rate (Gbaud) | Combinational Logic ALUTS Registers | M10K  | Memory<br>ALUTs |   |

|           | Physical                                   | 1x   | 3.125             | 3,700                               | 3,900 | 30              | 0 |

|           | layer<br>only                              | 4x   | 2.5               | 5,000                               | 5,600 | 31              | 8 |

| Cyclone V | Cyclone V Physical and                     | 1x   | 3.125             | 7,000                               | 7,400 | 60              | 0 |

| Cyclone V | Transport layers, and I/O master and slave | 4x   | 2.5               | 8,300                               | 9,600 | 61              | 0 |

<sup>(1)</sup> M4K for Cyclone II devices and M9K for Cyclone III and Cyclone IV devices.

Table 1–5 shows results obtained using the Quartus II software v11.1 for the following devices:

- Arria GX (EP1AGX60DF780C6)

- Arria II GX (EP2AGX65DF25C4)

- Arria II GZ (EP2AGZ225FF35C3)

- Arria V (5AGXBB1D4F31C4)

Table 1-5. Serial RapidIO FPGA Resource Utilization III

| Device      |                                                                      | Param | eters             |                        | Logic<br>Registers | Memory                                 |                                          |

|-------------|----------------------------------------------------------------------|-------|-------------------|------------------------|--------------------|----------------------------------------|------------------------------------------|

|             | Layers                                                               | Mode  | Baud Rate (Gbaud) | Combinational<br>ALUTs |                    | M4K,<br>M9K, or<br>M10K <sup>(1)</sup> | M512 or<br>Memory<br>ALUT <sup>(2)</sup> |

|             | Physical                                                             | 1x    | 3.125             | 3,700                  | 4,000              | 37                                     | 9                                        |

|             | layer<br>only                                                        | 4x    | 2.5               | 5,100                  | 5,600              | 36                                     | 9                                        |

| Arria GX    | Physical and                                                         | 1x    | 3.125             | 6,300                  | 7,100              | 78                                     | 11                                       |

|             | Transport<br>layers, and<br>I/O master and<br>slave                  | 4x    | 2.5               | 7,600                  | 9,200              | 74                                     | 13                                       |

|             | Physical                                                             | 1x    | 3.125             | 3,700                  | 3,900              | 33                                     | 0                                        |

|             | layer<br>only                                                        | 4x    | 3.125             | 5,400                  | 5,800              | 32                                     | 0                                        |

| Arria II GX | Physical and                                                         | 1x    | 3.125             | 7,100                  | 7,400              | 63                                     | 0                                        |

|             | Transport<br>layers, and<br>I/O master and<br>slave                  | 4x    | 3.125             | 8,200                  | 9,600              | 63                                     | 0                                        |

|             | Physical                                                             | 1x    | 5.00              | 3,700                  | 4,000              | 29                                     | 20                                       |

|             | layer<br>only                                                        | 4x    | 3.125             | 5,500                  | 6,000              | 29                                     | 38                                       |

| Arria II GZ | Arria II GZ  Physical and Transport layers, and I/O master and slave | 1x    | 5.00              | 7,100                  | 7,600              | 54                                     | 74                                       |

|             |                                                                      | 4x    | 3.125             | 8,600                  | 9,800              | 56                                     | 50                                       |

|             | Physical                                                             | 1x    | 5.00              | 3,600                  | 4,000              | 29                                     | 0                                        |

|             | layer<br>only                                                        | 4x    | 3.125             | 5,000                  | 6,300              | 31                                     | 0                                        |

| Arria V     | Physical and                                                         | 1x    | 5.00              | 7,100                  | 7,800              | 59                                     | 0                                        |

| Ama v       | Transport<br>layers, and<br>I/O master and<br>slave                  | 4x    | 3.125             | 8,100                  | 10,400             | 61                                     | 0                                        |

#### Note to Table 1-5:

<sup>(1)</sup> M4K for Arria GX devices; M9K for Arria II GX and Arria II GZ devices; and M10K for Arria V devices.

<sup>(2)</sup> M512 for Arria GX devices; Memory ALUT for Arria II GX, Arria II GZ, and Arria V devices.

Table 1–6 shows results obtained using the Quartus II software v11.1 for the following devices:

- Stratix II (EP2S30F672C3)

- Stratix II GX (EP2SGX30DF780C3)

- Stratix III (EP3SE260F1517C2)

- Stratix IV GX (EP4SGX230DF29C2)

- Stratix V (5SGXMA7H2F35C2)

Table 1-6. Serial RapidIO FPGA Resource Utilization IV (Part 1 of 2)

| Device        |                                                     | Paran | neters                        | Combinational ALUTs | Logic<br>Registers | Memory                                 |                                          |

|---------------|-----------------------------------------------------|-------|-------------------------------|---------------------|--------------------|----------------------------------------|------------------------------------------|

|               | Layers                                              | Mode  | Baud Rate (Gbaud)             |                     |                    | M4K,<br>M9K, or<br>M20K <sup>(1)</sup> | M512 or<br>Memory<br>ALUT <sup>(2)</sup> |

|               | Physical<br>layer                                   | 1x    | 3.125 with external<br>SERDES | 3,700               | 3,900              | 38                                     | 10                                       |

|               | only                                                | 4x    | 3.125 with external<br>SERDES | 5,600               | 6,200              | 44                                     | 10                                       |

| Stratix II    | Physical and<br>Transport                           | 1x    | 3.125 with external<br>SERDES | 6,200               | 7,000              | 80                                     | 11                                       |

|               | layers, and<br>I/O master and<br>slave              | 4x    | 3.125 with external<br>SERDES | 8,100               | 9,600              | 82                                     | 14                                       |

|               | Physical                                            | 1x    | 3.125                         | 3,700               | 4,000              | 37                                     | 9                                        |

|               | layer<br>only                                       | 4x    | 3.125                         | 5,300               | 5,700              | 35                                     | 10                                       |

| Stratix II GX | Physical and                                        | 1x    | 3.125                         | 6,200               | 7,100              | 79                                     | 10                                       |

| Stratix ii ux | Transport<br>layers, and<br>I/O master and<br>slave | 4x    | 3.125                         | 7,500               | 9,200              | 73                                     | 14                                       |

|               | Physical<br>layer<br>only                           | 1x    | 3.125 with external SERDES    | 3,800               | 4,000              | 32                                     | 42                                       |

|               |                                                     | 4x    | 3.125 with external<br>SERDES | 6,200               | 7,100              | 35                                     | 112                                      |

| Stratix III   | Physical and<br>Transport                           | 1x    | 3.125 with external<br>SERDES | 6,200               | 7,200              | 63                                     | 144                                      |

|               | layers, and<br>I/O master and<br>slave              | 4x    | 3.125 with external SERDES    | 8,800               | 11,200             | 62                                     | 403                                      |

|               | Physical                                            | 1x    | 3.125                         | 3,700               | 4,000              | 27                                     | 24                                       |

| Stratix IV GX | layer<br>only                                       | 4x    | 3.125                         | 5,200               | 5,900              | 25                                     | 38                                       |

|               | Physical and                                        | 1x    | 3.125                         | 7,100               | 7,600              | 51                                     | 87                                       |

|               | Transport<br>layers, and<br>I/O master and<br>slave | 4x    | 3.125                         | 9,000               | 10,300             | 51                                     | 83                                       |

|              | Parameters                           |      |                   |                        |                    | Memory                                 |                                          |

|--------------|--------------------------------------|------|-------------------|------------------------|--------------------|----------------------------------------|------------------------------------------|

| Device       | Layers                               | Mode | Baud Rate (Gbaud) | Combinational<br>ALUTs | Logic<br>Registers | M4K,<br>M9K, or<br>M20K <sup>(1)</sup> | M512 or<br>Memory<br>ALUT <sup>(2)</sup> |

|              | Physical                             | 1x   | 5.00              | 3,800                  | 4,200              | 20                                     | 22                                       |

|              | layer<br>only                        | 4x   | 5.00              | 5,300                  | 6,600              | 20                                     | 36                                       |

| Stratix V GX | Physical and                         | 1x   | 5.00              | 7,000                  | 7,800              | 41                                     | 96                                       |

| Stratix V GX | Transport layers, and I/O master and | 4x   | 5.00              | 8,600                  | 10,700             | 45                                     | 90                                       |

Table 1-6. Serial RapidIO FPGA Resource Utilization IV (Part 2 of 2)

#### Note to Table 1-5:

- (1) M4K for Stratix II and Stratix II GX devices; M9K for Stratix III and Stratix IV devices; and M20K for Stratix V devices.

- (2) M512 for Stratix II and Stratix II GX devices; Memory ALUT for Stratix III, Stratix IV GX, and Stratix V devices.

Table 1–7 shows the recommended device family speed grades for the supported link widths and internal clock frequencies. In all cases, Altera recommends that you set **Quartus II Analysis & Synthesis Optimization Technique** to **Speed**.

For information about how to apply the **Speed** setting, refer to volume 1 of the *Quartus II Handbook*.

Table 1–7. Recommended Device Family and Speed Grades (1) (Part 1 of 2)

|                              | Mode 1x          |                   |                   |                   |                   | 4x                |                   |                   |                                      |

|------------------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------------------|

| Device<br>Family             | Rate             | 1.25<br>Gbaud     | 2.5<br>Gbaud      | 3.125<br>Gbaud    | 5.0<br>Gbaud      | 1.25<br>Gbaud     | 2.5<br>Gbaud      | 3.125<br>Gbaud    | 5.0<br>Gbaud                         |

| ,                            | f <sub>MAX</sub> | 31.25<br>MHz      | 62.50<br>MHz      | 78.125<br>MHz     | 125<br>MHz        | 62.5<br>MHz       | 125<br>MHz        | 156.25<br>MHz     | 250<br>MHz                           |

| Arria GX (2)                 |                  | -6                | -6                | -6                | (3)               | -6                | -6 <sup>(4)</sup> | (3)               | (3)                                  |

| Arria II GX                  |                  | -4, -5, -6        | -4, -5, -6        | -4, -5, -6        | (3)               | -4, -5, -6        | -4, -5            | -4, -5            | (3)                                  |

| Arria II GZ                  |                  | -3, -4            | -3, -4            | -3, -4            | -3                | -3, -4            | -3, -4            | -3, -4            | (3)                                  |

| Arria V                      |                  | C4, -5, C6        | C4, -5, C6        | C4, -5, C6        | C4 (5)            | C4, -5, C6        | C4, -5            | C4 (5)            | (3)                                  |

| Stratix II,<br>Stratix II GX |                  | -3, -4, -5        | -3, -4, -5        | -3, -4, -5        | (3)               | -3, -4, -5        | -3, -4            | -3 (6)            | (3)                                  |

| Stratix III                  |                  | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | (3)               | -2, -3, -4        | -2, -3, -4        | -2, -3            | (3)                                  |

| Stratix IV                   |                  | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | -2, -3, -4        | <b>-2</b> , <b>-3</b> <sup>(7)</sup> |

| Stratix V                    |                  | C1, -2, -3,<br>-4 | C1, -2,<br>-3 <sup>(7)</sup>         |

| Cyclone II,<br>Cyclone III   |                  | -6, -7, -8        | -6, -7, -8        | -6, -7            | (3)               | -6, -7, -8        | (3)               | (3)               | (3)                                  |

| Cyclone IV GX                |                  | -6, -7, -8        | -6, -7, -8        | -6, -7            | (3)               | -6, -7, -8        | -6 <sup>(9)</sup> | (3)               | (3)                                  |

| Table 1-7 | Recommended | <b>Device Family</b> | and Speed Gra | ades <sup>(1)</sup> | (Part 2 of 2) |

|-----------|-------------|----------------------|---------------|---------------------|---------------|

|-----------|-------------|----------------------|---------------|---------------------|---------------|

|                  | Mode             |               | 1x           |                |              |               | 4x           |                |              |  |

|------------------|------------------|---------------|--------------|----------------|--------------|---------------|--------------|----------------|--------------|--|

| Device<br>Family | Rate             | 1.25<br>Gbaud | 2.5<br>Gbaud | 3.125<br>Gbaud | 5.0<br>Gbaud | 1.25<br>Gbaud | 2.5<br>Gbaud | 3.125<br>Gbaud | 5.0<br>Gbaud |  |

| ,                | f <sub>MAX</sub> | 31.25<br>MHz  | 62.50<br>MHz | 78.125<br>MHz  | 125<br>MHz   | 62.5<br>MHz   | 125<br>MHz   | 156.25<br>MHz  | 250<br>MHz   |  |

| Cyclone V (10)   |                  | C6, -7, C8    | C6, -7, C8   | C6, -7, C8     | C6 (11)      | C6, -7, C8    | -6           | (3)            | (3)          |  |

#### Notes to Table 1-7:

- (1) In this table, the entry -n indicates that both the industrial speed grade In and the commercial speed grade Cn are supported for this device family, RapidIO mode, and baud rate.

- (2) Only the -6 speed grade is available for the Arria GX device family.

- (3) Not supported for this device family.

- (4) Altera does not recommend implementation of 4x RapidIO IP core variations with lane speeds of 2.5 Gbaud in the smallest member of the Arria GX device family (EP1AGX20). For other devices in the Arria GX family, you can use the Design Space Explorer in the Quartus II software to find the optimal Fitter settings for your design to meet the timing constraints. Following the Timing Advisor's recommendations, including optimizing for speed and using LogicLock regions may be necessary to meet timing, especially for more complex variations.

- (5) Some simple Arria V 1x variations with lane speed of 5.0 Gbaud, and some simple Arria V 4x variations with lane speeds of 3.125 Gbaud, such as physical-layer-only variations, may meet timing in -5 speed grade devices, after following the Timing Advisor's recommendations.

- (6) 4x 3.125 Gbaud is possible in a -4 speed grade Stratix II and Stratix II GX device only with the smallest Rx and Tx buffer sizes.

- (7) Altera recommends that for designs that include a 4x 5.0 Gbaud RapidIO IP core variation and that target a -3 speed grade Stratix IV GX or Stratix V device, you use multiple seeds in the Quartus II Design Space Explorer to find the optimal Fitter settings to meet the timing constraints. Following the Timing Advisor's recommendations, including optimizing for speed and using LogicLock regions may be necessary to meet timing, especially for more complex variations implemented in the largest devices.

- (8) The RapidIO IP core supports only the EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150 Cyclone IV GX devices.

- (9) Some simple Cyclone IV GX 4× variations, such as physical-layer-only variations, may meet timing at 2.5 Gbaud in -7 speed grade devices, after following the Timing Advisor's recommendations.

- (10) Only the -6 and -7 speed grades are available for Cyclone V GT devices.

- (11) The RapidIO IP core supports 1× 5.0 Gbaud variations that target the Cyclone V device family in Cyclone V GT devices only. The RapidIO parameter editor does not warn you of this fact. You can generate a 1× 5.0 Gbaud variation that targets a Cyclone V GX variation, for example, but when you attempt to add the extra constraints required for the RapidIO IP core, as discussed in "Specifying Constraints" on page 2–12, the Quartus II software Analysis and Synthesis tool fails.

## **Release Information**

Table 1–8 provides information about this release of the RapidIO IP core.

Table 1–8. RapidIO Release Information

| Item          | Description |

|---------------|-------------|

| Version       | 12.0        |

| Release Date  | June 2012   |

| Ordering Code | IP-RIOPHY   |

| Product ID    | 0095        |

| Vendor ID     | 6AF7        |

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP core. Any exceptions to this verification are reported in the *MegaCore IP Library Release Notes and Errata*. Altera does not verify compilation with IP core versions older than the previous release.

# **Installation and Licensing**

The RapidIO IP core is part of the Altera MegaCore IP Library, which is distributed with the Quartus II software and downloadable from the Altera website, www.altera.com.

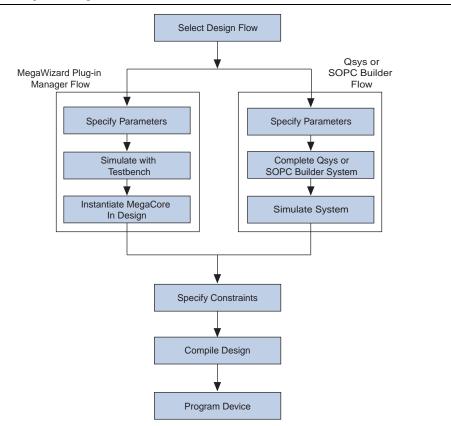

Figure 1–2 shows the directory structure after you install the RapidIO IP core, where *<path>* is the installation directory. The default installation directory on Windows is **C:\altera\**<*version number>*; on Linux it is */opt/altera\*<*version number>*.

Figure 1–2. Directory Structure

You can use Altera's free OpenCore Plus evaluation feature to evaluate the IP core in simulation and in hardware before you purchase a license. You must purchase a license for the IP core only when you are satisfied with its functionality and performance, and you want to take your design to production.

After you purchase a license for the RapidIO IP core, you can request a license file from the Altera website at www.altera.com/licensing and install it on your computer. When you request a license file, Altera emails you a license.dat file. If you do not have internet access, contact your local Altera representative.

# **OpenCore Plus Evaluation**

With the Altera free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a megafunction (Altera IP core or AMPP<sup>SM</sup> megafunction) in your system using the Quartus II software and Altera-supported VHDL and Verilog HDL simulators.

- Verify the functionality of your design and evaluate its size and speed quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device and verify your design in hardware.

#### **OpenCore Plus Time-Out Behavior**

OpenCore Plus hardware evaluation supports the following two operation modes:

- *Untethered*—the design runs for a limited time.

- Tethered—requires a connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely.

All megafunctions in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one megafunction in a design, a specific megafunction's time-out behavior may be masked by the time-out behavior of the other megafunctions.

For Altera IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite.

Your design stops working after the hardware evaluation time expires.

The RapidIO IP core then behaves as if its Atlantic™ interface signals atxena and arxena are tied low. All packet transfers through the Physical layer are suppressed. As a result, the RapidIO IP core cannot transmit new packets (it only transmits the idle sequence and status control symbols), and cannot read packets from the Physical layer. If the remote link partner continues to transmit packets, the RapidIO IP core refuses new packets by sending packet\_retry control symbols after its receiver buffer fills up beyond the corresponding threshold.

| For Information About      | Refer To                                          |

|----------------------------|---------------------------------------------------|

| Installation and licensing | Altera Software Installation and Licensing        |

| Open Core Plus             | AN 320: OpenCore Plus Evaluation of Megafunctions |

# 2. Getting Started

## **Design Flows**

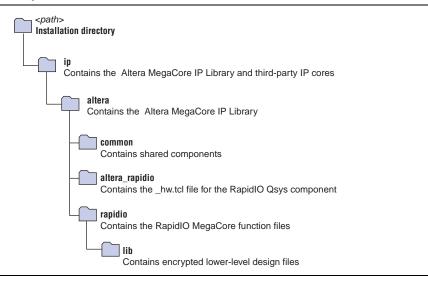

You can customize the RapidIO IP core to support a wide variety of applications. You can instantiate this IP core in the MegaWizard Plug-In Manager, in the Qsys system integration tool, or in SOPC Builder.

The MegaWizard Plug-In Manager flow offers the following advantages:

Allows you to parameterize the IP core to create a variation that you can instantiate manually in your design.

The SOPC Builder flow offers the following advantages:

- Allows you to integrate other Altera-provided custom components such as DMA controllers, on-chip memories, and FIFOs in your design.

- Uses Avalon-MM interfaces.

The Qsys flow offers the following additional advantages over SOPC Builder:

- Provides visualization of hierarchical designs.

- Allows greater customization of interconnect elements and pipelining.

- Provides closer integration with the Quartus II software.

RapidIO variations that target an Arria II GZ, Arria V, Cyclone V, or Stratix V device are supported in the MegaWizard Plug-In Manager and the Qsys flows only.

2-2 Chapter 2: Getting Started

Design Flows

Figure 2–1 shows the stages for creating a system with the RapidIO IP core and the Quartus II software. Each stage is described in detail in subsequent sections.

Figure 2-1. RapidIO Design Flow

# MegaWizard Plug-In Manager Design Flow

You can use the MegaWizard Plug-In Manager in the Quartus II software to parameterize a custom IP core variation. When you select the RapidIO IP core in the MegaWizard Plug-In Manager, the RapidIO parameter editor appears. The RapidIO parameter editor lets you interactively set parameter values and select optional ports. This flow is best for manual instantiation of an IP core in your design.

# **SOPC Builder Design Flow**

The SOPC Builder design flow enables you to integrate a RapidIO endpoint in an SOPC Builder system. The SOPC Builder design flow automatically connects selected components with the system interconnect, eliminating the requirement to design low-level interfaces and significantly reducing design time. When you add a RapidIO IP core instance to your design, a RapidIO parameter editor guides you in selecting the properties of the RapidIO IP core instance.

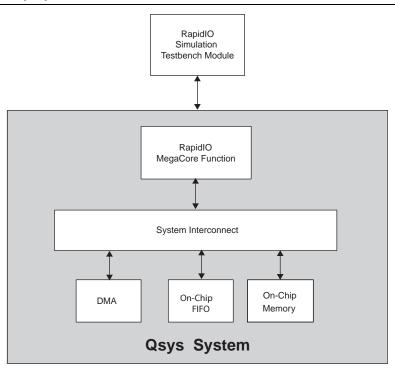

## **Qsys Design Flow**

The Qsys design flow enables you to integrate a RapidIO endpoint in a Qsys system. The Qsys design flow allows you to connect component interfaces with the system interconnect, eliminating the requirement to design low-level interfaces and significantly reducing design time. When you add a RapidIO IP core instance to your design, a RapidIO parameter editor guides you in selecting the properties of the RapidIO IP core instance.

# **MegaWizard Plug-In Manager Design Flow**

The MegaWizard Plug-In Manager flow allows you to customize the RapidIO IP core, and manually integrate the function in your design.

## **Specifying Parameters**

To specify RapidIO IP core parameters using the MegaWizard Plug-In Manager, follow these steps:

- Create a Quartus II project using the New Project Wizard available from the File menu.

- 2. Launch the **MegaWizard Plug-In Manager** from the Tools menu, and follow the prompts in the MegaWizard Plug-In Manager interface to create a custom megafunction variation.

To select the RapidIO IP core, click Installed Plug-Ins > Interfaces > RapidIO.

- 3. Specify the parameters on all pages in the **Parameter Settings** tab. For details about these parameters, refer to Chapter 3, Parameter Settings.

- 4. If you want to generate an IP functional simulation model for the IP core in the selected language, on the **EDA** tab, turn on **Generate simulation model**.

- The IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software.

Use the simulation models only for simulation and not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

- Some third-party synthesis tools can use a netlist that contains the structure of this IP core but no detailed logic to optimize timing and performance of the design containing it.

- To use this feature if your synthesis tool supports it, turn on **Generate netlist**.

- 6. On the **Summary** tab, select the files you want to generate. A gray checkmark indicates a file that is automatically generated. All other files are optional.

- For more information about the files generated in your project directory, refer to the project files list in the HTML report file in your project directory.

- 7. Click Finish to generate the IP core and supporting files.

- You may have to wait several minutes for file generation to complete, especially if you are generating an IP functional simulation model.

- 8. If you generate the RapidIO IP core instance in a Quartus II project, you are prompted to add the Quartus II IP File (.qip) to the current Quartus II project. You can also turn on Automatically add Quartus II IP Files to all projects.

- The .qip is generated by the parameter editor, and contains information about the generated IP core. In most cases, the .qip contains all of the necessary assignments and information required to process the IP core or system in the Quartus II compiler. The MegaWizard Plug-In Manager generates a single .qip for each IP core.

- 9. After you review the generation report (*<variation name>.html*) in your project directory, click **Exit** to close the MegaWizard Plug-In Manager.

You can now integrate your custom IP core variation in your design, simulate, and compile.

When you integrate your RapidIO IP core variation in your design, note the connection and I/O assignment requirements described in "Completing the Qsys System" on page 2–10.

## **Simulating the Design**

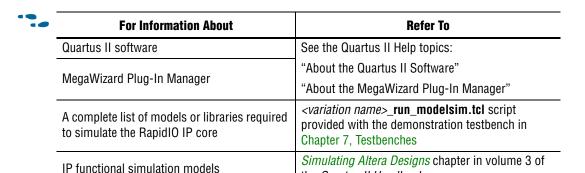

You can simulate your RapidIO IP core variation using the IP functional simulation model and the Verilog HDL demonstration testbench. The IP functional simulation model and testbench files are generated in your project directory. The directory also includes scripts to compile and run the demonstration testbench. The testbench demonstrates how to instantiate a model in a design and includes some simple stimulus to control the user interfaces of the RapidIO interface.

For information about the demonstration testbench, refer to Chapter 7, Testbenches.

If you specify VHDL for your RapidIO IP core, the IP functional simulation model is in VHDL, but the testbench is in Verilog HDL. Therefore, you must have a license to run mixed language simulations to run the testbench with the VHDL model. Alternatively, you can run simulation in a VHDL-only environment. In a VHDL-only environment, you must create your own test environment.

To simulate your MegaWizard Plug-In Manager flow generated RapidIO IP core variation with the IP functional simulation model and the Verilog HDL demonstration testbench, using the Mentor Graphics ModelSim simulator, perform the following steps:

- 1. Start the ModelSim simulator.

- 2. In ModelSim, change directory to your project directory.

- 3. Type the following command to set up the required libraries, compile the generated IP Functional simulation model, and exercise the simulation model with the provided testbench:

do <variation>\_run\_modelsim.tcl ←

# **SOPC Builder Design Flow**

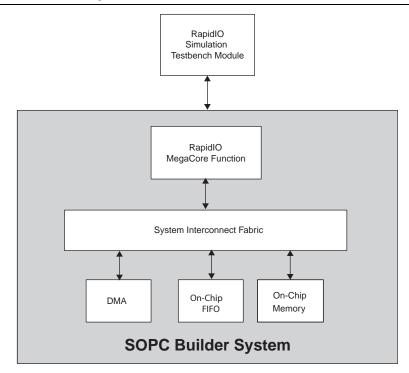

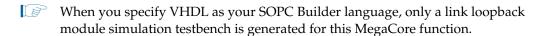

You can use SOPC Builder to build a system that contains your customized RapidIO IP core. You can easily add other components and quickly create an SOPC Builder system. SOPC Builder automatically generates HDL files that include all of the specified components and interconnections. The HDL files are ready to be compiled by the Quartus II software to produce output files for programming an Altera device. SOPC Builder also generates a simulation testbench module that includes basic

the Quartus II Handbook

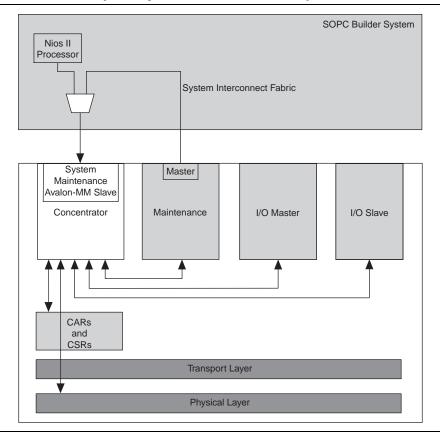

transactions to validate the HDL files. Figure 2–2 shows a block diagram of an example SOPC Builder system.

Figure 2-2. SOPC Builder System

| For Information About      | Refer To                                                                                                                                                                                        |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System interconnect fabric | System Interconnect Fabric for Memory-Mapped Interfaces and System Interconnect Fabric for Streaming Interfaces chapters in the SOPC Builder User Guide and the Avalon Interface Specifications |  |  |

| SOPC Builder               | SOPC Builder User Guide                                                                                                                                                                         |  |  |

| Quartus II software        | Quartus II Help                                                                                                                                                                                 |  |  |

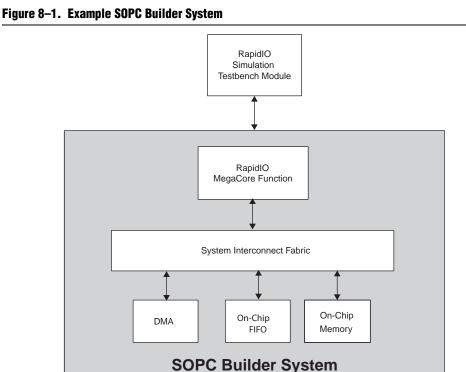

## **Specifying Parameters**

To specify RapidIO parameters using the SOPC Builder flow, follow these steps:

- 1. Create a new Quartus II project using the **New Project Wizard** available from the File menu.

- 2. On the Tools menu, click SOPC Builder.

- 3. For a new system, specify the system name and language.

- 4. On the **System Contents** tab, double-click **RapidIO** to add it to your system. The RapidIO parameter editor appears.

- 5. Specify the required parameters on all pages in the **Parameter Settings** tab of the RapidIO parameter editor in SOPC Builder. For detailed explanations of these parameters, refer to Chapter 3, Parameter Settings.

- 6. Click **Finish** to complete the RapidIO IP core and add it to the system.

## **Completing the SOPC Builder System**

To complete the SOPC Builder system, follow these steps:

- 1. Add and parameterize any additional components. For a complete SOPC Builder system design example containing the RapidIO IP core, refer to Chapter 8, SOPC Builder Design Example.

- 2. Connect the components using the Connection panel on the **System Contents** tab.

- For Arria GX, Arria II GX, Cyclone IV GX, Stratix II GX, and Stratix IV GX designs, ensure that you connect the calibration clock (cal\_blk\_clk) to a clock signal with the appropriate frequency range of 10 to 125 MHz. The cal\_blk\_clk ports on other components that use transceivers must be connected to the same clock signal.

- By default, SOPC Builder does not display clock names. To display clock names in the Module Name column and the clocks in the Clock column in the System Contents tab, click Filters to display the Filters dialog box. In the Filter list, click All Interfaces.

- For Arria II GX, Cyclone IV GX, and Stratix IV GX designs with high-speed transceivers, you must add a dynamic reconfiguration block (altgx\_reconfig) and connect it as specified in the *Arria II Device Handbook*, *Cyclone IV Device Handbook*, or *Stratix IV Device Handbook*. This block supports offset cancellation. The design compiles without the altgx\_reconfig block, but it cannot function correctly in hardware.

- 4. If you intend to simulate your SOPC builder system, on the **System Generation** tab, turn on **Simulation** to generate a functional simulation model for your system.

- 5. Click **Generate** to generate the system.

- Among the files generated by SOPC Builder is the .qip file. This file contains information about a generated IP core or system. In most cases, the .qip file contains all of the necessary assignments and information required to process the IP core or system in the Quartus II compiler. Generally, a single .qip file is generated for each SOPC Builder system. However, some more complex SOPC Builder components generate a separate .qip file. In that case, the system .qip file references the component .qip file.

- 6. For Arria II GX and Stratix IV GX designs, after you generate the system, you must create assignments for the high-speed transceiver VCCH settings by following these steps:

- a. In the Quartus II window, on the Assignments menu, click Assignment Editor.

- b. In the <<new>> cell in the To column, type the top-level signal name for your RapidIO IP core instance td signal. The default signal name that SOPC Builder generates is td\_rapidio.

- c. Double-click in the **Assignment Name** column and click **I/O Standard**.

- d. Double-click in the Value column and click your standard (for example, 1.5-V PCML).

- e. In the new <<new>> row, repeat steps b to d for your RapidIO IP core instance rd signal.

## Simulating the System

During system generation, SOPC Builder optionally generates an IP functional simulation model and testbench for the entire system which you can use to simulate your system easily in any Altera-supported simulation tool. SOPC Builder also generates a set of ModelSim Tcl scripts and macros that you can use to simulate the testbench, IP functional simulation models, and clear text RTL design files that describe your system in the ModelSim simulation software.

In the SOPC Builder design flow, if you specify Verilog HDL as the target HDL, a complete testbench is generated, but if you specify VHDL, only a link loopback module is generated.

By default, the testbench provided for Verilog HDL SOPC Builder systems initializes the link and reads some registers in the RapidIO IP core. The testbench provides tasks that you can use to create a test sequence specific to your SOPC Builder system. For an example SOPC Builder system with a more complete testbench, refer to Chapter 8, SOPC Builder Design Example.

To run the testbench SOPC Builder provides by default for a system in which the RapidIO IP core is generated in Verilog HDL, perform the following steps:

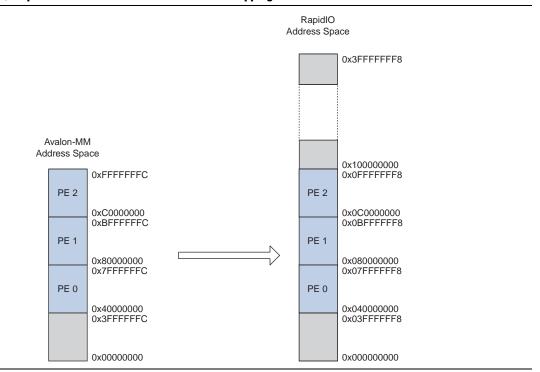

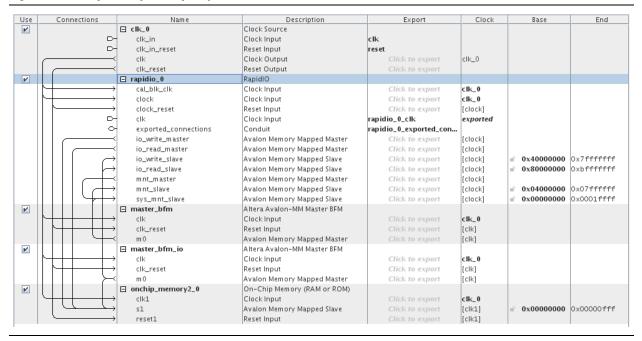

- 1. Start the ModelSim software.