# **POS-PHY Level 2 and 3 Compiler User Guide**

The IP described in this document is scheduled for product obsolescence and discontinued support as described in PDN0906. Therefore, Altera<sup>®</sup> does not recommend use of this IP in new designs. For more information about Altera's current IP offering, refer to Altera's Intellectual Property website.

101 Innovation Drive San Jose, CA 95134 www.altera.com

MegaCore Version: Document Date:

9.1 November 2009

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

### Chapter 1. About This Compiler

| Release Information                  | 1–1 |

|--------------------------------------|-----|

| Device Family Support                | 1–1 |

| Features                             | 1–2 |

| General Description                  | 1–3 |

| Atlantic Interface                   |     |

| OpenCore Plus Evaluation             | 1–4 |

| Performance and Resource Utilization | 1–5 |

### **Chapter 2. Getting Started**

| Design Flow                           |  |

|---------------------------------------|--|

| POS-PHY Level 2 & 3 Walkthrough       |  |

| Create a New Quartus II Project       |  |

| Launch IP Toolbench                   |  |

| Step 1: Parameterize                  |  |

| Step 2: Set Up Simulation             |  |

| Step 3: Generate                      |  |

| Simulate the Design                   |  |

| IP Functional Simulation Model        |  |

| Testbench with the ModelSim Simulator |  |

| Testbench with NativeLink             |  |

| Compile the Design                    |  |

| Program a Device                      |  |

| Set Up Licensing                      |  |

### **Chapter 3. Functional Description**

| Example Configurations          | -2 |

|---------------------------------|----|

| Example Implementations         |    |

| Internal Architecture           | -4 |

| POS-PHY Interface               | -5 |

| Packet Data Width Conversion    | -6 |

| Packet FIFO Buffer              | -6 |

| 'B' Interface                   | -6 |

| OpenCore Plus Time-Out Behavior | -6 |

| Parameters                              |  |

|-----------------------------------------|--|

| Interface Settings                      |  |

| FIFO Buffer & Clock Selector Options    |  |

| Common B Clock                          |  |

| Parity Settings                         |  |

| Pass Through Mode                       |  |

| ParErr On Error Pin                     |  |

| FIFO Buffer Settings                    |  |

| Atlantic Interface FIFO Buffer Settings |  |

| FIFO Buffer Size                        |  |

| Address & Packet Available Settings     |  |

| POS-PHY Level 3 Interfaces              |  |

| POS-PHY Level 2 Interfaces              |  |

| Base Address                            |  |

| SX Always                               |  |

| Interface Signals                       |  |

| Global Interface                        |  |

| POS-PHY Level 3 Interface               |  |

| POS-PHY Level 2 Interface               |  |

| Atlantic Interface                      |  |

| Timing                                  |  |

| Signal Naming Convention                |  |

| Compatibility                           |  |

| Example Packet Types                    |  |

| MegaCore Verification                   |  |

|                                         |  |

### **Additional Information**

| Revision History        | 1–1 |

|-------------------------|-----|

| How to Contact Altera   | 1–1 |

| Typographic Conventions | 1–1 |

## **Release Information**

Table 1–1 provides information about this release of the Altera® POS-PHY Level 2 and 3 Compiler.

| Item Description     |               |  |  |

|----------------------|---------------|--|--|

| Version              | 9.1           |  |  |

| Release Date         | November 2009 |  |  |

| Ordering Codes:      |               |  |  |

| POS-PHY level 2 PHY  | IP-POSPHY/P2  |  |  |

| POS-PHY level 2 link | IP-POSPHY/L2  |  |  |

| POS-PHY level 3 PHY  | IP-POSPHY/P3  |  |  |

| POS-PHY level 3 link | IP-POSPHY/L3  |  |  |

| Product IDs:         |               |  |  |

| POS-PHY level 2 PHY  | 0058 0071     |  |  |

| POS-PHY level 2 link | 0070 0071     |  |  |

| POS-PHY level 2 PHY  | 0051 0071     |  |  |

| POS-PHY level 2 link | 0050 0071     |  |  |

| Vendor ID            | 6AF7          |  |  |

Table 1–1.

POS-PHY Level 2 and 3 Compiler Release Information

For more information about this release, refer to the MegaCore IP Library Release Notes and Errata.

Altera verifies that the current version of the Quartus® II software compiles the previous version of each MegaCore® function. The MegaCore IP Library Release Notes and Errata report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release."

## **Device Family Support**

MegaCore functions provide either full or preliminary support for target Altera device families:

- Full support means the MegaCore function meets all functional and timing requirements for the device family and may be used in production designs

- Preliminary support means the MegaCore function meets all functional requirements, but may still be undergoing timing analysis for the device family; it may be used in production designs with caution.

Table 1–2 shows the level of support offered by the POS-PHY Level 2 and 3 Compiler to each Altera device family.

| Device Family            | Support     |

|--------------------------|-------------|

| Arria™ GX                | Full        |

| Arria II GX              | Preliminary |

| Cyclone®                 | Full        |

| Cyclone II               | Full        |

| Cyclone III              | Full        |

| HardCopy <sup>®</sup> II | Full        |

| HardCopy III             | Preliminary |

| HardCopy IV E            | Preliminary |

| Stratix®                 | Full        |

| Stratix II               | Full        |

| Stratix II GX            | Full        |

| Stratix III              | Full        |

| Stratix IV               | Preliminary |

| Stratix GX               | Full        |

| Other device families    | No support  |

Table 1–2. Device Family Support

## **Features**

- Conforms to POS-PHY level 2 and level 3 specifications

- Link-layer or PHY-layer POS-PHY interfaces

- Creates bridges between different POS-PHY interfaces

- Support for traffic up to a rate of 3.2 gigabits per second (Gbps) (POS-PHY level 3) or 832 megabits per second (Mbps) (POS-PHY level 2), such as SONET OC-48

- Single-PHY (SPHY) or up to 8-channel multi-PHY (MPHY) operation with polled and direct packet available options

- Atlantic<sup>™</sup> interface that allows a consistent interface between all Altera cell and packet MegaCore functions

- Selectable POS-PHY interface bus widths (8/16/32 bit) and Atlantic interface bus widths (8/16/32/64 bit)—allowing translation between different bus types

- Parity generation/detection

- Configurable first-in first-out (FIFO) options: selectable FIFO width, depth, and fill thresholds.

- Easy-to-use IP Toolbench interface

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

- Support for OpenCore Plus evaluation

## **General Description**

The POS-PHY Level 2 and 3 Compiler generates MegaCore functions for use in linklayer or physical layer (PHY) devices that transfer data to and from packet over SONET/SDH (POS) devices using the standard POS-PHY bus.

The POS-PHY Level 2 and 3 Compiler comprises separately configurable modules, which can be easily combined via the IP Toolbench to generate a highly parameterized module, allowing POS-PHY compliant interfaces (and non-standard interfaces) to be included in custom designs.

The compiler supports POS-PHY level 3 operating at up to 3.2 Gbps, and level 2 operating at up to 832 Mbps.

The POS-PHY Level 2 and 3 Compiler is compliant with all applicable standards, including:

- POS-PHY Level 3 Specification, Issue 4, June 2000

- POS-PHY Level 2 Specification, Issue 5, December 1998

- Optical Internet working Forum (OIF), System Packet Interface Level 3 (SPI-3)

- Altera Corporation, Atlantic Interface Specification

This allows efficient translation between the different formats, including mapping between different bus speeds and bus widths, as well as customizable FIFO buffer parameters.

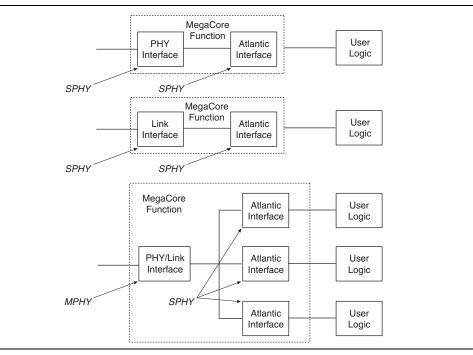

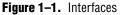

The compiler allows configurations such as PHY-PHY, link-link bridges, or packet multiplexing MegaCore functions, and SPHY and MPHY applications. Figure 1–1 on page 1–3 shows the possible interfaces. Figure 1–2 on page 1–4 shows the possible bridges.

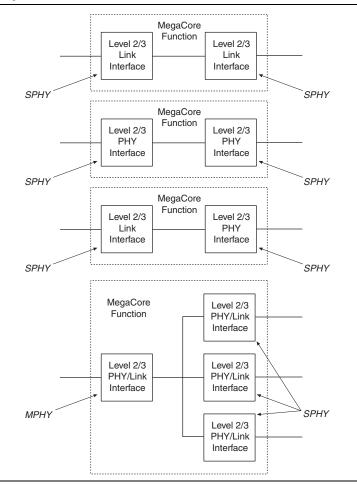

#### Figure 1-2. Bridges

#### **Atlantic Interface**

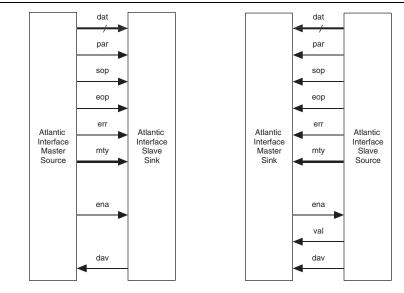

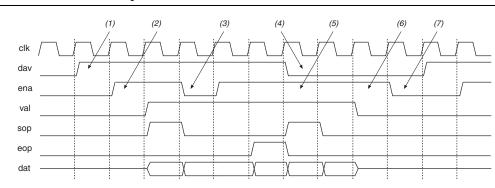

The Atlantic interface allows a consistent interface between all Altera cell and packet MegaCore functions. The Atlantic interface supports a point-to-point connection.

• For more information on the Atlantic interface, refer to *FS* 13: *Atlantic Interface*.

### **OpenCore Plus Evaluation**

With Altera's free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a megafunction (Altera MegaCore function or AMPP<sup>SM</sup> megafunction) within your system

- Verify the functionality of your design, as well as evaluate its size and speed quickly and easily

- Generate time-limited device programming files for designs that include megafunctions

- Program a device and verify your design in hardware

You only need to purchase a license for the megafunction when you are completely satisfied with its functionality and performance, and want to take your design to production.

For more information on OpenCore Plus hardware evaluation using the POS-PHY Level 2 and 3 Compiler, see "OpenCore Plus Time-Out Behavior" on page 3–6 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

## **Performance and Resource Utilization**

Table 1–3 through 1–7 show typical expected performance for SPHY and 4-port POS-PHY MegaCore functions. All results are push-button performance and use a FIFO buffer size of 512 bytes. These results were obtained using the Quartus® II software version for the following devices:

- Cyclone II (see tables for device details)

- Cyclone III (EP3C5F256C6 for POS-PHY level 3)

- Stratix III (EP3SL70F484C2 for POS-PHY level 2; EP3SL50F484C2 for POS-PHY level 3)

- Stratix IV (EP4SGX70DF29C2X )

| Table 1-3. Performance—POS-PHY Level 2 Link Laye | r—Cyclone II Device |

|--------------------------------------------------|---------------------|

|--------------------------------------------------|---------------------|

|                       |       | Memory Blocks |                        |

|-----------------------|-------|---------------|------------------------|

| MegaCore Function     | LEs   | M4K           | f <sub>max</sub> (MHz) |

| Device: EP2C5F256C6   |       |               |                        |

| SPHY receive          | 416   | 2             | 176                    |

| SPHY transmit         | 407   | 2             | 149                    |

| Device: EP2C15AF484C6 |       |               |                        |

| MPHY 4-port receive   | 1,267 | 8             | 167                    |

| MPHY 4-port transmit  | 1,272 | 8             | 128                    |

Table 1-4. Performance—POS-PHY Level 2 Link Layer—Stratix III Device

|                      |       | Logic     | Memory Blocks |                        |

|----------------------|-------|-----------|---------------|------------------------|

| MegaCore Function    | ALUTS | Registers | M9K           | f <sub>max</sub> (MHz) |

| SPHY receive         | 177   | 348       | 2             | 344                    |

| SPHY transmit        | 210   | 326       | 2             | 310                    |

| MPHY 4-port receive  | 558   | 1,051     | 8             | 320                    |

| MPHY 4-port transmit | 624   | 1,024     | 8             | 221                    |

Table 1–5.

Performance—POS-PHY Level 2 PHY Layer—Cyclone II Device (Part 1 of 2)

|                     |     | Memory Blocks |                        |

|---------------------|-----|---------------|------------------------|

| MegaCore Function   | LEs | M4K           | f <sub>max</sub> (MHz) |

| Device: EP2C5F256C6 |     |               |                        |

| SPHY receive        | 354 | 2             | 174                    |

|                       |       | Memory Blocks |                        |

|-----------------------|-------|---------------|------------------------|

| MegaCore Function     | LEs   | M4K           | f <sub>max</sub> (MHz) |

| SPHY transmit         | 285   | 2             | 159                    |

| Device: EP2C15AF484C6 |       |               | ·                      |

| MPHY 4-port receive   | 1,175 | 8             | 161                    |

| MPHY 4-port transmit  | 1,126 | 8             | 139                    |

Table 1–5.

Performance—POS-PHY Level 2 PHY Layer—Cyclone II Device (Part 2 of 2)

Table 1–6.

Performance—POS-PHY Level 2 PHY Layer—Stratix III Device

|                      |       | Logio              | Memory Blocks |                        |

|----------------------|-------|--------------------|---------------|------------------------|

| MegaCore Function    | ALUTS | Logic<br>Registers | M9K           | f <sub>max</sub> (MHz) |

| SPHY receive         | 122   | 309                | 2             | 340                    |

| SPHY transmit        | 123   | 234                | 2             | 346                    |

| MPHY 4-port receive  | 487   | 995                | 8             | 318                    |

| MPHY 4-port transmit | 529   | 918                | 8             | 293                    |

Table 1–7.

Performance—POS-PHY Level 3 Link Layer—Cyclone III Device

|                      |       | Memory Blocks |                        |

|----------------------|-------|---------------|------------------------|

| MegaCore Function    | LEs   | М9К           | f <sub>MAX</sub> (MHz) |

| SPHY receive         | 379   | 2             | 165                    |

| SPHY transmit        | 377   | 2             | 139                    |

| MPHY 4-port receive  | 1,202 | 8             | 171                    |

| MPHY 4-port transmit | 1,242 | 8             | 164                    |

Table 1–8.

Performance—POS-PHY Level 3 Link Layer—Stratix III Device

|                      |       | Logic     | Memory Blocks |                        |

|----------------------|-------|-----------|---------------|------------------------|

| MegaCore Function    | ALUTS | Registers | M9K           | f <sub>max</sub> (MHz) |

| SPHY receive         | 149   | 330       | 2             | 234                    |

| SPHY transmit        | 164   | 313       | 2             | 205                    |

| MPHY 4-port receive  | 522   | 1,019     | 8             | 217                    |

| MPHY 4-port transmit | 613   | 1,009     | 8             | 178                    |

|                      |       | Logic     | Memory Blocks |                        |

|----------------------|-------|-----------|---------------|------------------------|

| MegaCore Function    | ALUTs | Registers | М9К           | f <sub>max</sub> (MHz) |

| SPHY receive         | 149   | 330       | 2             | 231                    |

| SPHY transmit        | 164   | 313       | 2             | 180                    |

| MPHY 4-port receive  | 522   | 1,019     | 8             | 254                    |

| MPHY 4-port transmit | 613   | 1,009     | 8             | 174                    |

|                      |       | Memory Blocks |                        |

|----------------------|-------|---------------|------------------------|

| MegaCore Function    | LEs   | M4K           | f <sub>max</sub> (MHz) |

| SPHY receive         | 350   | 2             | 174                    |

| SPHY transmit        | 365   | 2             | 173                    |

| MPHY 4-port receive  | 1,175 | 8             | 169                    |

| MPHY 4-port transmit | 1,218 | 8             | 143                    |

Table 1–10.

Performance—POS-PHY Level 3 PHY Layer—Cyclone III Device

Table 1–11.

Performance—POS-PHY Level 3 PHY Layer—Stratix III

Device

|                      |       | Logic     | Memory Blocks |                        |

|----------------------|-------|-----------|---------------|------------------------|

| MegaCore Function    | ALUTS | Registers | М9К           | f <sub>max</sub> (MHz) |

| SPHY receive         | 121   | 307       | 2             | 270                    |

| SPHY transmit        | 160   | 294       | 2             | 287                    |

| MPHY 4-port receive  | 489   | 999       | 8             | 245                    |

| MPHY 4-port transmit | 587   | 984       | 8             | 231                    |

| Table 1–12. Performance—POS-PHY Level 3 PHY Layer—Stratix |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

|                      |       | Logio              | Memory Blocks |                        |

|----------------------|-------|--------------------|---------------|------------------------|

| MegaCore Function    | ALUTS | Logic<br>Registers | М9К           | f <sub>max</sub> (MHz) |

| SPHY receive         | 121   | 307                | 2             | 243                    |

| SPHY transmit        | 160   | 294                | 2             | 286                    |

| MPHY 4-port receive  | 489   | 999                | 8             | 222                    |

| MPHY 4-port transmit | 587   | 984                | 8             | 260                    |

## 2. Getting Started

## **Design Flow**

To evaluate the POS-PHY Level 2 and 3 Compiler using the OpenCore Plus feature include these steps in your design flow:

1. Obtain and install the POS-PHY Level 2 and 3 Compiler.

The POS-PHY Level 2 and 3 MegaCore function is part of the MegaCore IP Library, which is distributed with the Quartus<sup>®</sup> II software and downloadable from the Altera<sup>®</sup> website, www.altera.com.

**For system requirements and installation instructions, refer to** *Quartus II Installation & Licensing for Windows and Linux Workstations.*

Figure 2–1 on page 2–1 shows the directory structure after you install the POS-PHY Level 2 and 3 Compiler, where *<path>* is the installation directory. The default installation directory on Windows is **c:altera90**; on Linux it is **/opt/altera90**.

Figure 2–1. Directory Structure

2. Create a custom variation of a POS-PHY Level 2 or 3 MegaCore function using IP Toolbench.

IP Toolbench is a toolbar from which you can quickly and easily view documentation, specify parameters, and generate all of the files necessary for integrating the parameterized MegaCore function into your design.

- 3. Implement the rest of your design using the design entry method of your choice.

- 4. Use the IP Toolbench-generated IP functional simulation model to verify the operation of your design.

For more information on IP functional simulation models, refer to the Simulating Altera IP in Third-Party Simulation Tools chapter in volume 3 of the Quartus II Handbook.

- 5. Use the Quartus II software to compile your design.

- You can also generate an OpenCore Plus time-limited programming file, which you can use to verify the operation of your design in hardware.

- 6. Purchase a license for the POS-PHY Level 2 and 3 Compiler.

After you have purchased a license for the POS-PHY Level 2 and 3 compiler, the design flow requires these additional steps:

- 1. Set up licensing.

- 2. Generate a programming file for the Altera<sup>®</sup> device(s) on your board.

- 3. Program the Altera device(s) with the completed design.

- 4. Perform design verification.

## **POS-PHY Level 2 & 3 Walkthrough**

This walkthrough explains how to create a POS-PHY Level 2 or 3 MegaCore function using the Altera POS-PHY Level 2 and 3 Compiler IP Toolbench and the Quartus II software. When you finish generating a POS-PHY Level 2 or 3 MegaCore function, you can incorporate it into your overall project.

IP Toolbench only allows you to select legal combinations of parameters, and warns you of any invalid configurations.

This walkthrough involves the following steps:

- Create a New Quartus II Project

- Launch IP Toolbench

- Step 1: Parameterize

- Step 2: Set Up Simulation

- Step 3: Generate

### **Create a New Quartus II Project**

You need to create a new Quartus II project with the **New Project Wizard**, which specifies the working directory for the project, assigns the project name, and designates the name of the top-level design entity.

To create a new project follow these steps:

- Choose Programs > Altera > Quartus II < version> (Windows Start menu) to run the Quartus II software. Alternatively, you can also use the Quartus II Web Edition software.

- 2. Choose New Project Wizard (File menu).

- 3. Click **Next** in the **New Project Wizard Introduction** page (the introduction does not display if you turned it off previously).

- 4. In the **New Project Wizard: Directory, Name, Top-Level Entity** page, enter the following information:

- a. Specify the working directory for your project. For example, this walkthrough uses the **c:\altera\projects\pl2pl3\_project** directory.

- The Quartus II software automatically specifies a top-level design entity that has the same name as the project. This walkthrough assumes that the names are the same.

- b. Specify the name of the project. This walkthrough uses **example** for the project name.

- 5. Click Next to close this page and display the New Project Wizard: Add Files page.

- When you specify a directory that does not already exist, a message asks if the specified directory should be created. Click **Yes** to create the directory.

- 6. Click **Next** to close this page and display the **New Project Wizard: Family & Device Settings** page.

- 7. On the **New Project Wizard: Family & Device Settings** page, choose the target device family in the Family list.

- 8. The remaining pages in the **New Project Wizard** are optional. Click **Finish** to complete the Quartus II project.

You have finished creating your new Quartus II project.

#### Launch IP Toolbench

To launch IP Toolbench in the Quartus II software, follow these steps:

- 1. Start the MegaWizard<sup>®</sup> Plug-In Manager by choosing **MegaWizard Plug-In Manager** (Tools menu). The MegaWizard Plug-In Manager dialog box displays.

- Refer to the Quartus II Help for more information on how to use the MegaWizard Plug-In Manager.

| The MegaWizard Plug-In Manager helps you create or modify<br>design files that contain custom variations of megafunctions.<br>Which action do you want to perform?<br>© <u>Create a new custom megafunction variation</u><br>© Edit an existing custom megafunction variation<br>© Copy an existing custom megafunction variation<br>Copyright (C) 1991-2009 Altera Corporation |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

- 2. Specify that you want to create a new custom megafunction variation and click Next.

- Expand the Communications > POS-PHY directory then click POS-PHY Level 2 & 3 Compiler.

- 4. Select the output file type for your design; the wizard supports VHDL, and Verilog HDL.

- 5. The MegaWizard Plug-In Manager shows the project path that you specified in the **New Project Wizard**. Append a variation name for the MegaCore function output files *<project path>*\*<variation name>*. Figure 2–3 shows the wizard after you have made these settings.

Figure 2–3. Select the Megafunction

| Which megafunction would you like to customize?<br>Select a megafunction from the list below | Which device family will you be Stratix II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                              | Which type of output file do you want to create?  AHDL  YHDL  Verilog HDL  What name do you want for the gutput file? Browse  C:\altera\projects\pl2_project\example  Return to this page for another create operation Note: To compile a project successfully in the Quartus II software, your design files must be in the project directory, in the global user libraries specified in the Options dialog box (Tools menu), or a user libraries specified in the Options dialog box (Tools menu), or a user library specified in the User Libraries page of the Settings dialog box (Assignments menu). Your current user library directories are: |

6. Click Next to launch IP Toolbench.

### **Step 1: Parameterize**

To parameterize your MegaCore function, follow these steps:

1. Click Parameterize in the IP Toolbench (see Figure 2–4 on page 2–5).

#### Figure 2-4. IP Toolbench—Parameterize

- 2. Select your architecture options where the POS-PHY 'A' interface is a data source or sink (see Figure 2–5).

- Source indicates that interface 'A' is an output from the MegaCore function. Sink indicates that interface 'A' is an input to the MegaCore function.

Figure 2–5. Select the 'A' Interface Direction

| Parame         | eterize - POS-PHY Level 🔳 🗖 🗙                                           |  |

|----------------|-------------------------------------------------------------------------|--|

|                | Architecture Options<br>Interface A Bus Direction<br>③ Source<br>〇 Sink |  |

|                | Number of channels 1                                                    |  |

| <u>C</u> ancel | Press F1 for help.                                                      |  |

- 3. In a MPHY architecture there is a 'B' interface for each supported channel (maximum eight). Select the number of supported channels that you require.

- To create a design that supports source and sink data directions, you must run IP Toolbench twice, to create the source and sink designs separately.

- 4. Click Next.

- 5. Select your interface types (see Figure 2–6).

- a. Select interface 'A' using the radio buttons.

- b. Choose 'B' interfaces using the drop-down menus.

#### Figure 2–6. Select the Interface Types

|             |                    | BInt     | erfaces        |   |  |

|-------------|--------------------|----------|----------------|---|--|

| A Interface |                    |          | Interface Type |   |  |

|             |                    | B1       | Atlantic Slave | ~ |  |

| POS-PHY     | Level 3 Link Layer | B2       |                |   |  |

| O POS-PHY   | Level 3 PHY Layer  | B3       |                |   |  |

| O POS-PHY   | Level 2 Link Layer | B4       |                |   |  |

| Ŭ           |                    | B5       |                |   |  |

| O POS-PHY   | Level 2 PHY Layer  | B6       |                |   |  |

|             |                    | B7<br>B8 |                |   |  |

|             |                    |          |                |   |  |

- 6. Click Next.

- 7. Choose the interface settings (see Figure 2–7 on page 2–6).

- *POS-PHY Level 3 Specification, Issue 4, June 2000* supports an 8- or 32-bit interface. Additionally this MegaCore function supports a 16-bit interface for POS-PHY level 3.

- *POS-PHY Level 2 Specification, Issue 5, December 1998* supports a 16 bit interface. Additionally, this MegaCore function supports 8- and 32-bit interfaces for POS-PHY level 2.

The Atlantic interface can be 8-, 16-, 32-, or 64-bits wide.

#### Figure 2–7. Choose the Interface Settings

| Interface Settings |          |               |                 |           |

|--------------------|----------|---------------|-----------------|-----------|

|                    | B In     | terfaces      |                 |           |

|                    |          | Bus Width     | Clock Selection |           |

| A Interface        | B1       | 32 💌          | B Clock         | ×         |

|                    | B2       |               |                 |           |

| Bus Width 32 💙     | B3<br>B4 |               |                 |           |

|                    | B5       |               |                 |           |

|                    | B6       |               |                 |           |

|                    | B7       |               |                 |           |

|                    | B8       |               |                 |           |

|                    | Co       | ommon B Clock |                 |           |

|                    |          |               | Press E1        | for help. |

2–6

- 8. Click Next.

- 9. Select the parity settings of the interfaces (see Figure 2–8).

If parity is used the polarity setting must be the same for all interfaces.

Figure 2–8. Select the Parity Settings

|                     | B Interfaces |            |                |

|---------------------|--------------|------------|----------------|

| A Interface         | Parity Con   | trol ParEr | r on Error Pin |

| 💿 None              | B1 None      | ~          |                |

| Pass Through        | B2           |            |                |

| O Generate Odd      | B3           |            |                |

| Ŭ                   | B4           |            |                |

| 🚫 Generate Even     | B5           |            |                |

| DevEware Ewen Die   | B6<br>B7     |            |                |

| ParErr on Error Pin | B8           |            |                |

|                     | DO           |            |                |

For more information on the parity settings, see "Parity Settings" on page 3–8.

- 10. Click Next.

- 11. Choose the first-in first-out (FIFO) buffer settings (see Figure 2–9).

Figure 2–9. Choose the FIFO Buffer Settings

| A Interface          | B Interfaces |             |       |              |

|----------------------|--------------|-------------|-------|--------------|

| Empty Threshold 64   | Size         | Full Thresh | Burst | Remote Burst |

| Empty Threshold 64   | B1 512       | 64          | 32    |              |

| Burst 0              | B2           |             |       |              |

| Remote Burst 32 🔽    | B3           |             |       |              |

|                      | B4<br>B5     |             |       |              |

|                      | B6           |             |       |              |

| Detect FIFO Overflow | B7           |             |       |              |

| Fixed Burst          | B8           |             |       |              |

|                      |              |             |       |              |

| IFO Diagrams         |              |             |       |              |

| A B1                 |              |             |       |              |

|                      | urst         |             |       |              |

|                      | 512          |             |       |              |

| empty full           |              |             |       |              |

|                      |              |             |       |              |

If you select the **Fixed Burst** option, you must also set the burst size by entering a value in the Burst field. Data is then sent in bursts of the specified burst size only, or in bursts containing an end of packet.

The wizard indicates the minimum **Burst** value supported.

You must also adjust the FIFO thresholds so that the data sent to the FIFO for a burst is greater than the burst (an end of packet of packet flushes the FIFO). The minimum and maximum values are set as follows:

- The minimum value must be set at the size of the remote burst. If you set any value below this, it is automatically adjusted to the size of the remote burst.

- The maximum value is derived from the empty threshold. It must take into account the latency in the pipeline and the time that the core takes to decide to stop sending data. Therefore, the maximum burst size is calculated as follows:

('A' interface empty threshold in bytes) – (5 × fifo\_byte\_width)

Where fifo\_byte\_width is the width in bytes of the FIFO (4 for a 32-bit data width).

For more information on the FIFO buffer settings, see "FIFO Buffer Settings" on page 3–9.

12. Click Next.

13. Choose the address and packet available settings (see Figure 2–10).

Figure 2–10. Choose the Address and Packet Available Settings

| A Interface                                       | B Interfaces                                 |           | 1         |

|---------------------------------------------------|----------------------------------------------|-----------|-----------|

| Packet Available Mode<br>Direct (No Addressing) 💙 | Packet Available Mode Direct (No Addressing) | Base Addr | SX Always |

| Base Address 0 💌                                  |                                              |           |           |

| SX Always                                         |                                              |           |           |

For more information on the address and packet available settings, see "Address & Packet Available Settings" on page 3–15.

14. Click Next.

15. IP Toolbench shows the product order codes (see Figure 2–11). Click Finish.

| arameterize - POS-PHY Level 2 and 3 📮 🗖 🗙        |

|--------------------------------------------------|

|                                                  |

|                                                  |

| Order Code(s)                                    |

| The order code(s) for the selected core is(are): |

| IP-POSPHY/L3                                     |

|                                                  |

|                                                  |

|                                                  |

| Press F1 for help.                               |

|                                                  |

Figure 2–11. Product Order Code

### **Step 2: Set Up Simulation**

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software. It allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

You may only use these simulation model output files for simulation purposes and expressly not for synthesis or any other purposes. Using these models for synthesis will create a nonfunctional design.

To generate an IP functional simulation model for your MegaCore function, follow these steps:

1. Click Set Up Simulation in IP Toolbench (see Figure 2–12 on page 2–9).

Figure 2–12. IP Toolbench—Set Up Simulation

2. Turn on Generate Simulation Model (see Figure 2–13).

| Figure 2–13. | Generate Simu | lation Model |

|--------------|---------------|--------------|

|--------------|---------------|--------------|

| Set Up Simulati                                                                                                                                                            | סח<br>סח                                                                                                                 |                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Generate Sir                                                                                                                                                               | nulation Model                                                                                                           |                                                                                                           |

| Language                                                                                                                                                                   | Verilog HDL 💌                                                                                                            |                                                                                                           |

| HDL model prod<br>allow fast functio<br>and Verilog HDL<br>You may only us;<br>purposes and ex<br>Using these mod<br>Cenerate net<br>fyou are synthes<br>tool, you can gen | e these simulation model output fil<br>pressly not for synthesis or any oth<br>lels for synthesis will create a non-<br> | hese models<br>⊬standard VHDL<br>es for simulation<br>er purposes.<br>functional design.<br>EDA synthesis |

- 3. Choose the language in the Language list.

- 4. Some third-party synthesis tools can use a netlist that contains only the structure of the MegaCore function, but not detailed logic, to optimize performance of the design that contains the MegaCore function. If your synthesis tool supports this feature, turn on **Generate netlist**.

- 5. Click OK.

### **Step 3: Generate**

To generate your MegaCore function, follow these steps:

1. Click Step 3: Generate in IP Toolbench (see Figure 2–14).

| 0                     | POS-PHY Lev 🔳 🗆 🔀            |

|-----------------------|------------------------------|

|                       | MegaCore"                    |

|                       | About this Core              |

| piler                 | Documentation                |

| 13 Com                | Display Symbol               |

| evel 2 and 3 Compiler | Step 1:<br>Parameterize      |

| 7                     | Step 2:<br>Set Up Simulation |

| H4-SO4                | Step 3:<br>Generate          |

Figure 2–14. IP Toolbench—Generate

Figure 2–15 on page 2–11 shows the generation report.

#### Figure 2–15. Generation Report

| MegaCore <sup>®</sup> COI                                    | mpiler                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Entity Name                                                  | auk_pac_mtx_mw                                                                                                                                                                                                                                                                                                                                       |

| Variation Name                                               | example                                                                                                                                                                                                                                                                                                                                              |

| Variation HDL                                                | Verilog HDL                                                                                                                                                                                                                                                                                                                                          |

| Output Directory                                             | C:\attera\projects\posphy_project                                                                                                                                                                                                                                                                                                                    |

| ' <b>ile Summary</b><br>he MegaWizard interfa<br><b>File</b> | ace is creating the following files in the output directory:           Description                                                                                                                                                                                                                                                                   |

| ∙<br>ne MegaWizard interf∉                                   |                                                                                                                                                                                                                                                                                                                                                      |

| ∙<br>ne MegaWizard interf∉                                   | Description           This XML file is a Pin Planner support file that Pin Planner automatically uses.<br>This file must remain in the same directory as the example ppf file.           This XML file describes the MegaCore pin attributes to the Quartus II Pin<br>Planner. MegaCore pin attributes include pin direction, location, I/O standard |

| ne MegaWizard interfa<br>File<br>example.ppx                 | Description           This XML file is a Pin Planner support file that Pin Planner automatically uses.<br>This file must remain in the same directory as the example ppf file.           This XML file describes the MegaCore pin attributes to the Quartus II Pin                                                                                   |

Table 2–1 describes the generated files and other files that may be in your project directory. The names and types of files specified in the IP Toolbench report vary based on whether you created your design with VHDL or Verilog HDL.

| Extension                                                                                   | Description                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre><variation name="">syn.v or <variation name="">syn.vhd</variation></variation></pre>   | A timing and resource netlist for use in some third-party synthesis tools.                                                                                                                                                                                                                                                                     |

| <variation name="">.bsf</variation>                                                         | Quartus II symbol file for the MegaCore function variation. You can use this file in the Quartus II block diagram editor.                                                                                                                                                                                                                      |

| <variation name="">.cmp</variation>                                                         | A VHDL component declaration file for the MegaCore function variation. Add the contents of this file to any VHDL architecture that instantiates the MegaCore function.                                                                                                                                                                         |

| <variation name="">.ppf</variation>                                                         | This XML file describes the MegaCore function pin attributes to the Quartus II Pin Planner.<br>MegaCore function pin attributes include pin direction, location, I/O standard assignments, and<br>drive strength. If you launch IP Toolbench outside of the Pin Planner application, you must<br>explicitly load this file to use Pin Planner. |

| <variation name="">.ppx</variation>                                                         | This XML file is a Pin Planner support file that Pin Planner automatically uses. This file must remain in the same directory as the <i><variation name="">.ppf</variation></i> file.                                                                                                                                                           |

| <variation name=""><b>.vhd</b> or<br/><variation name=""><b>.v</b></variation></variation>  | A MegaCore function variation file, which defines a VHDL or Verilog HDL top-level description of the custom MegaCore function. Instantiate the entity defined by this file inside your design. Include this file when compiling your design in the Quartus II software.                                                                        |

| <variation name=""><b>.vo</b> or<br/><variation name=""><b>.vho</b></variation></variation> | VHDL or Verilog HDL IP functional simulation model.                                                                                                                                                                                                                                                                                            |

#### Table 2–1. Generated Files

- 2. After you review the generation report, click **Exit** to close IP Toolbench and click **Yes** on the **Quartus II IP Files** message.

- The Quartus II IP File (.qip) is a file generated by the MegaWizard interface or SOPC Builder that contains information about a generated IP core. You are prompted to add this .qip file to the current Quartus II project at the time of file generation. In most cases, the .qip file contains all of the necessary assignments and information required to process the core or system in the Quartus II compiler. Generally, a single .qip file is generated for each MegaCore function and for each SOPC Builder system. However, some more complex SOPC Builder components generate a separate .qip file, so the system .qip file references the component .qip file.

You can now integrate your custom MegaCore function variation into your design, simulate, and compile.

## **Simulate the Design**

You can simulate your design using the IP Toolbench-generated VHDL and Verilog HDL IP functional simulation models.

For more information on IP functional simulation models, refer to "IP Functional Simulation Model" on page 2–13 and the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Handbook*.

Altera also provides fixed example VHDL and Verilog HDL testbenches that you can use to simulate example sink or source POS-PHY systems. You can use a testbench as a basis for your own design. The testbenches can be used with the IP functional simulation models. The testbenches and associated files are located in the sim\_lib\testbench directory.

### **IP Functional Simulation Model**

This section tells you how to use the demonstration testbench with the ModelSim simulator or with other simulators using NativeLink.

For more information on NativeLink, refer to the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Handbook*.

#### **Testbench with the ModelSim Simulator**

To use an example testbench with IP functional simulation models in the ModelSim simulator, follow these steps:

IP The testbench includes pregenerated Verilog HDL IP functional simulation models.

- 1. Start the ModelSim simulator.

- 2. Change the directory to the **sim\_lib\modelsim** directory.

- 3. For VHDL type the following command:

```

do compile_pl3_link_source_fixed_example_vlog_ipfs.tcl+

```

or for Verilog HDL type the following command:

do compile\_pl3\_link\_source\_fixed\_example\_vhdl\_ipfs.tcl+

For the sink example, replace source with sink.

#### **Testbench with NativeLink**

You can run receive and transmit tests with third-party IP functional simulators using NativeLink, for VHDL or Verilog HDL. The following procedure describes a receive test for the Verilog HDL model.

To use the testbench with NativeLink, follow these steps:

Using the New Project Wizard in the Quartus II software, create a new project in the \posphy\_l2\_l3\sim\_lib\testbench\verilog directory with the project name and top-level entity name of auk\_pac\_mrx\_pl3\_link.

For the VHDL model, replace the **verilog** directory with the **vhdl** directory.

For the transmit test, replace **mrx** with **mtx**.

- 2. Add the POS-PHY level 2 and 3 library:

- a. On the Assignments menu click Settings.

- b. Under Category click Libraries

- c. In Project library name click ...

- d. Browse to \pos\_phy\_l2l3\lib and click Open.

- e. Click Add.

- f. Click OK.

- 3. Add the following files to the project from the **\posphy\_l2\_l3\lib** directory:

- auk\_pac\_gen\_if.vhd

- auk\_pac\_functions.vhd

- auk\_pac\_components.vhd

The files must be in the order shown, from top to bottom, which is the order of compilation. Use the **Up** and **Down** buttons in the **New Project Wizard: Add Files** window to order the files.

- 4. Check that the absolute path to your third-party simulation tool is set. Set the path from **EDA Tool Options** in the **Options** dialog box (Tools menu).

- 5. On the Processing menu, point to Start and click Start Analysis & Elaboration.

If the analysis and elaboration is not successful, fix the error before moving to the next step.

- 6. On the Assignments menu, click **Settings**. The Settings window appears. Expand **EDA Tool Settings** and select **Simulation**.

- 7. In Tool name, select a simulator tool from the list.

In EDA Netlist Writer options, select **Verilog** from the list for **Format for output netlist** (Select VHDL if you are preparing a VHDL simulation).

In NativeLink settings, select the **Compile test bench** option and then click **Test Benches** . The Test Benches window appears.

- 8. In the Test Benches window, click **New**. The New Test Bench Settings window appears.

- 9. In the New Test Bench Settings window, enter the information described in Table 2–2 (see also Figure 2–16 on page 2–15). To enter the files described in the table, browse to the files in your project.

| Parameter                          | Setting/File Name        |

|------------------------------------|--------------------------|

| Test bench name                    | <any name=""></any>      |

| Top-level module in test bench     | auk_pac_mrx_ref (1)      |

| Design instance name in test bench | mrx (1)                  |

| Run for                            | 100 ns                   |

| Test bench files                   | auk_pac_mrx_ref_tb.v (2) |

Table 2–2.

NativeLink Test Bench Settings

Notes to table:

(2) If you are preparing a VHDL simulation, use **auk\_pac\_mrx\_ref\_tb.vhd** in the **vhdl** directory.

Figure 2–16 shows the testbench settings for a receive simulation.

<sup>(1)</sup> Use **mtx** for Tx simulations.

| Create new test bench settings.                                                                                                                                                          |                            |                        |                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|--------------------------------------------------------------------|

| I est bench name: pl3_simulato<br>Top level module in test bench:<br>Design instance name in test ben<br>Simulation period<br>C Run simulation until all yect<br>C End simulation at 100 | auk_pac_mrx_ref<br>ch: mrx |                        |                                                                    |

| Test bench files<br><u>File name</u><br>auk_pac_mrx_ref_tb.v                                                                                                                             | Library                    | HDL Version<br>Default | <u>Add</u> <u>H</u> emove <u>Up</u> <u>D</u> own <u>P</u> ropertie |

| ]                                                                                                                                                                                        |                            |                        |                                                                    |

Figure 2–16. Example of New Test Bench Settings for NativeLink

- 10. When you have entered the required information for your new testbench, click **OK** in the New Test Bench Settings window.

- 11. Click **OK** in the Test Benches window and then click **OK** in the Settings window.

- 12. On the Tools menu, point to **Run EDA Simulation Tool** and click **EDA RTL Simulation**. The simulation now begins with your chosen simulation tool.

### **Compile the Design**

You can use the Quartus II software to compile your design. Refer to Quartus II Help for instructions on compiling your design.

## **Program a Device**

After you have compiled your design, program your targeted Altera device, and verify your design in hardware.

With Altera's free OpenCore Plus evaluation feature, you can evaluate the POS-PHY Level 2 and 3 Compiler before you purchase a license. OpenCore Plus evaluation allows you to generate an IP functional simulation model, and produce a time-limited programming file.

....

For more information on IP functional simulation models, refer to the *Simulating Altera IP in Third-Party Simulation Tools* chapter in volume 3 of the *Quartus II Handbook*.

You can simulate the POS-PHY Level 2 and 3 Compiler in your design, and perform a time-limited evaluation of your design in hardware.

For more information on OpenCore Plus hardware evaluation using the POS-PHY Level 2 and 3 Compiler, see "OpenCore Plus Evaluation" on page 1–4, "OpenCore Plus Time-Out Behavior" on page 3–6, and AN 320: OpenCore Plus Evaluation of Megafunctions.

## **Set Up Licensing**

You need to purchase a license for the MegaCore function only when you are completely satisfied with its functionality and performance and want to take your design to production.

After you purchase a license for the POS-PHY Level 2 and 3 MegaCore function, you can request a license file from the Altera website at www.altera.com/licensing and install it on your computer. When you request a license file, Altera emails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

## 3. Functional Description

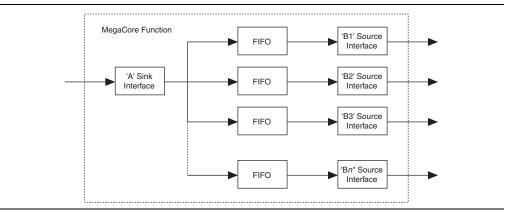

The POS-PHY Level 2 and 3 Compiler has two interfaces—an 'A' interface and one or many 'B' interfaces. Table 3–1 shows the possible interfaces.

Table 3–1. Possible Interfaces

| 'A' Interface               | 'B' Interface               |

|-----------------------------|-----------------------------|

| PHY level 3 (SPHY or MPHY)  | PHY level 3 (SPHY only)     |

| PHY level 2 (SPHY or MPHY)  | PHY level 2 (SPHY only)     |

| Link level 3 (SPHY or MPHY) | Link level 3 (SPHY only)    |

| Link level 2 (SPHY or MPHY) | Link level 2 (SPHY only)    |

|                             | Atlantic master (SPHY only) |

|                             | Atlantic slave (SPHY only)  |

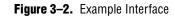

Figure 3–1 and 3–2 show example interfaces.

MegaCore<sup>®</sup> function data flow direction is from source to sink, that is, data flows from a physical layer (PHY) receive source to a link receive sink. A MegaCore function must have a minimum of one source and one sink interface.

Figure 3–1. Example MegaCore Function Interfaces

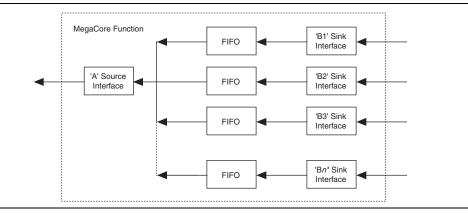

POS-PHY level 3 is a point-to-point system—transmit joins to transmit; channel 0 joins to channel 0, and so on (see Figure 3–3). POS-PHY level 2 is a unidirectional bus system.

## **Example Configurations**

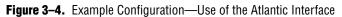

Figure 3–4 on page 3–2 shows a packet-processing function, which receives packets at one end from a POS-PHY PHY interface, processes them, and passes them on to a POS-PHY link interface.

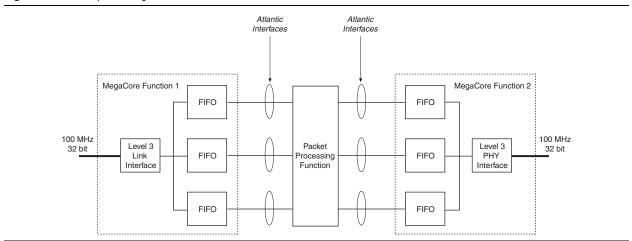

Figure 3–5 shows a bridging function with multiple lower-rate ports, which can be 8-bit POS-PHY level 3 or 16-bit POS-PHY level 2.

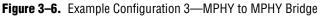

Figure 3–6 on page 3–3 shows an MPHY to MPHY POS-PHY bridge, which includes an MPHY POS-PHY level 2 interface and one first-in first-out (FIFO) buffer per supported address (MPHY).

## **Example Implementations**

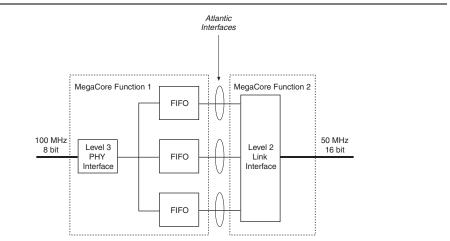

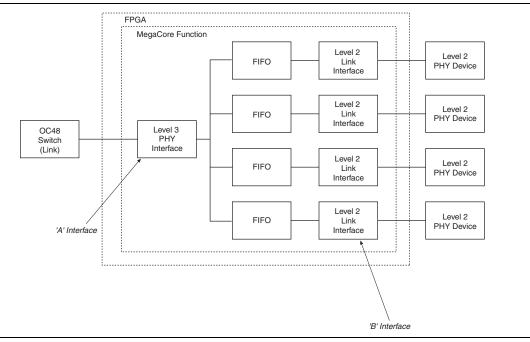

Figure 3–7 shows the FPGA interfacing to an OC-48 framer.

Figure 3–8 on page 3–4 shows the FPGA interfacing multiple POS-PHY level 2 devices to an OC-48 switch.

Figure 3–8. Example Implementation 2

## **Internal Architecture**

The POS-PHY Level 2 and 3 Compiler comprises the following four MegaCore functions:

- POS-PHY level 2 link-layer

- POS-PHY level 2 PHY-layer

- POS-PHY level 3 link-layer

- POS-PHY level 3 PHY-layer

Each MegaCore function includes a separate receiver and transmitter, which can be instantiated in a single device or separate devices.

There are many similarities in the internal architecture of these blocks. The main difference is in the non-symmetrical handshaking on the physical interface between receive and transmit directions.

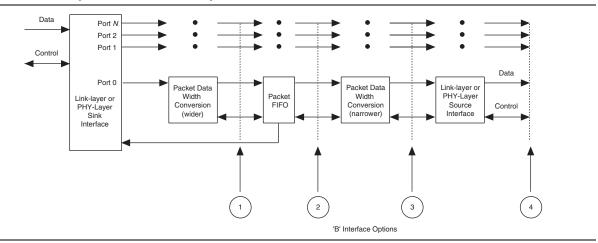

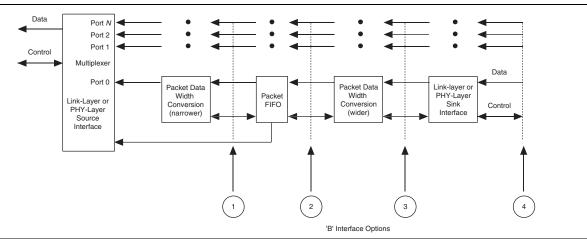

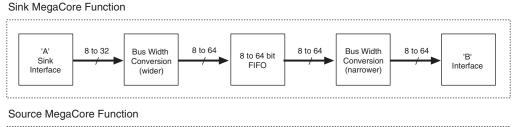

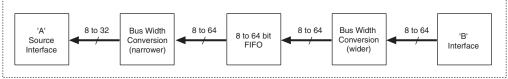

Figure 3–9 on page 3–5 shows the sink MegaCore function block diagram. Figure 3–10 on page 3–5 shows the source MegaCore function block diagram.

Figure 3–9. Sink MegaCore Function Block Diagram

Figure 3–10. Source MegaCore Function Block Diagram

#### **POS-PHY Interface**

Each POS-PHY supports single and multi-PHY implementations. The POS-PHY interface interfaces to an internal multiplexer, which allows access to multiple/single internal packet FIFO buffers. Status information from the FIFO buffers is used to control the POS-PHY interface. The source interface provides polled or direct packet available modes.

#### **Packet Data Width Conversion**

Packet data width conversion provides conversion from a narrower to a wider data stream, and from a wider to a narrower data stream, if required (such as, 8-bit to 32- or 16-bit, or 32-bit to 8- or 16-bit, and so on).

### **Packet FIFO Buffer**

The packet FIFO buffer has configurable width, depth, and fill level options. The FIFO buffer stores packet data in line with its associated packet flags (start of packet (SOP), end of packet (EOP), modulo (mod), and so on.

#### **'B' Interface**

The 'B' interface can be positioned at four different places, as follows:

- 1. After the first data width conversion—you provide a FIFO-like interface. The data width must be greater than or equal to the required POS-PHY bus width. Atlantic<sup>™</sup> interfaces here can only be masters.

- 2. After the packet FIFO buffer—you must interface to the internal packet FIFO buffer at the data width of the FIFO buffer, which is greater than or equal to that of the required POS-PHY bus. Atlantic interfaces here can be master or a slave interfaces.

- 3. After the second data width conversion—this position provides an interface where the data width can be narrower than that supported by the FIFO buffer. For example, a 32-bit POS-PHY to or from an 8-bit POS-PHY. Atlantic interfaces here can be a master or a slave interfaces.

- 4. After a POS-PHY interface—where you can create a POS-PHY bridge. From a single compiler you can build a MPHY to multiple SPHY bridge, or an SPHY to SPHY bridge. You can create more complex solutions by instantiating more than one MegaCore function.

## **OpenCore Plus Time-Out Behavior**

OpenCore Plus hardware evaluation supports the following two operation modes:

- Untethered—the design runs for a limited time.

- Tethered—requires a connection between your board and the host computer. If tethered mode is supported by all megafunctions in a design, the device can operate for a longer time or indefinitely.

All megafunctions in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one megafunction in a design, a specific megafunction's time-out behavior may be masked by the time-out behavior of the other megafunctions.

For MegaCore functions, the untethered timeout is 1 hour; the tethered timeout value is indefinite.

Your design stops working after the hardware evaluation time expires and the following events occur:

- The sop ina input goes low

- The addr\_outa output goes low

- The dpav\_outa output goes low

- The ppav\_outa output goes low

- The spav\_outa output goes low

- The rd\_outa output goes low

- For the POS-PHY transmit interface:

- The wr\_outA output goes low

- The val\_outA output goes low

- 'The sx\_outA output goes low

- The sop\_outA output goes low

- 'The eop\_outA output goes low

- The err\_outA output goes high

- The data\_outA output goes low

For more information on OpenCore Plus hardware evaluation, see "OpenCore Plus Evaluation" on page 1–4 and AN 320: OpenCore Plus Evaluation of Megafunctions.

## **Parameters**

The function's parameters, which can only be set in IP Toolbench (see "Step 1: Parameterize" on page 2–5), include the following settings:

- Interface Settings

- Parity Settings

- FIFO Buffer Settings

- Address & Packet Available Settings

#### **Interface Settings**

#### FIFO Buffer & Clock Selector Options

The following interface 'B' FIFO buffer and clock selector options are available:

- A Clock (No FIFO buffer)—only available if the 'B' interface is an Atlantic master, and the 'B' interface bus width ≥ the 'A' interface bus width. The relevant 'B' interface does not use an internal FIFO buffer, and is clocked by the 'A' interface clock pin. This is recommended only if you connect 'B' interfaces directly to another MegaCore function with an Atlantic slave interface

- A Clock—the corresponding 'B' interface uses an internal single clock FIFO buffer, and is clocked by the A interface clock pin

B Clock—the corresponding 'B' interface uses an internal dual clock FIFO buffer, and is clocked by the corresponding 'B' interface clock pin

The FIFO buffer width is the greater of the A bus width and the associated B bus width.

#### **Common B Clock**

With MPHY configurations there is more than one 'B' interface in the MegaCore function. Select this option to use a common clock and reset pins for all the 'B' interfaces that use the B clock option.

If you select this option, the 'B' interface clock and reset pins are labeled b\_clk and b\_reset\_n.

### **Parity Settings**

This section describes pass through mode and the parerr on error pin.

#### **Pass Through Mode**

In pass through mode any detected data parity errors on a sink interface are regenerated on the source interface, even when there is a bus width change.

P

If a parity error is detected on a sink interface port that has a wider data width than its corresponding source interface port, the parity error is generated on all output words that correspond to the input word with an error.

Table 3–2 shows the number of errors generated per input error.

| Data Width In | Data Width Out | Number of Errors Generated per Input Error |

|---------------|----------------|--------------------------------------------|

| 64            | 8              | 8                                          |

| 64            | 16             | 4                                          |

| 64            | 32             | 2                                          |

| 64            | 64             | 1                                          |

| 32            | 8              | 4                                          |

| 32            | 16             | 2                                          |

| 32            | 32             | 1                                          |

| 16            | 8              | 2                                          |

| 16            | 16             | 1                                          |

| 8             | 8              | 1                                          |

Table 3–2.

Number of Errors Generated

If you are using the parity bit and the parity does not match the data, the MegaCore function always detects the parity error.

For a source Atlantic interface, the par pin is an output that indicates the sink interface has received parity errors.

For a sink Atlantic interface, the par pin is an input that sees either a one or a zero depending on the incoming data's parity value.

If a parity error is detected on a sink interface port, which has a wider data width than its corresponding source interface port, the parity output is high on all output words that correspond to the input word with an error (see Table 3–2).

When a parity error is detected (as the data comes in), but the data width changes (increases), there are two options—pass through or error.

*Pass through*—the word that goes out, which contains the erroneous word and a good word, is flagged with an incorrect parity.

*Error*—the par signal functionality changes. It does not show parity, but goes high only when there is an error with the word, that is, it goes high to show where the error is.

## **ParErr On Error Pin**

When you check this option, the err signal is created, which looks for parity errors in the entire packet. The err signal can go high at anytime, but is valid only at the end of the packet (in accordance with the POS-PHY specifications). A high indicates a parity error somewhere in the packet. A parity error detected on a sink interface is signalled by setting the err pin at the end of the affected packet on the source interface.

# **FIFO Buffer Settings**

Table 3–3 shows the effect of the FIFO buffer settings for POS-PHY level 3 interfaces.

All FIFO buffer parameters are shown in bytes.

| Interface<br>(Direction)     | FIFO Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FIFO Burst                                                                                                                                                                                                                                                                                                                                    | FIFO Remote Burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link<br>Transmit<br>(Source) | When each FIFO buffer overflows<br>the FIFO buffer threshold level, or<br>contains a packet or packet<br>fragment with an EOP, it triggers<br>its not empty flag. The interface<br>then tries to empty each of the FIFO<br>buffers containing data, as soon as<br>it detects the PHY transmit<br>interface has indicated it has space.<br>When operating in polled mode,<br>this is indicated using the PTPA<br>and STPA inputs. When operating<br>in direct status mode, this is<br>indicated using the DTPA inputs. | Indicates the maximum<br>number of bytes the interface<br>transfers in each FIFO buffer<br>burst.<br>In MPHY mode, at the end of<br>each FIFO buffer burst the<br>MegaCore function re-<br>arbitrates for a new channel<br>in a round-robin fashion.<br>Set FIFO buffer burst <= FIFO<br>buffer threshold.<br>Not applicable in SPHY<br>mode. | Prevents the PHY transmit interface<br>from overflowing. Must be compatible<br>with the PHY transmit interface FIFO<br>buffer burst setting. When the interface<br>is in the process of transferring data<br>and the PHY transmit interface indicates<br>it is almost full, link transmit interface<br>transfers up to FIFO buffer remote burst<br>more bytes before stopping.<br>When operating in polled mode, this is<br>indicated using the PTPA and STPA<br>inputs.<br>When operating in direct status mode,<br>this is indicated using the DTPA inputs. |

| Link<br>Receive<br>(Sink)    | The interface indicates, by<br>asserting low the RENB output,<br>that it is not full when it has more<br>than or equal to FIFO buffer<br>threshold spaces for bytes in all of<br>its FIFO buffers (1 FIFO buffer per<br>channel). The interface indicates,<br>by deasserting high the RENB<br>output, that it is full when it has no<br>more spaces for bytes in any of its<br>FIFO buffers (1 FIFO buffer per<br>channel).                                                                                           | This should be set to the minimum value allowed.                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 3-3. POS-PHY Level 3 FIFO Buffer Settings (Part 1 of 2)

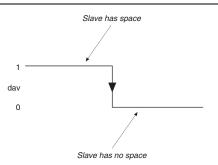

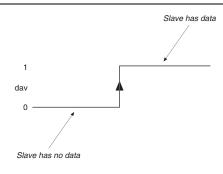

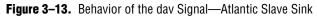

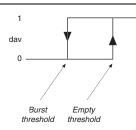

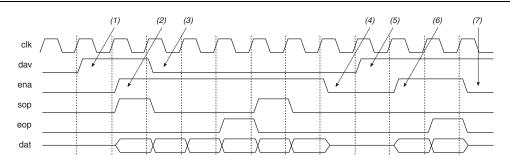

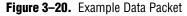

| Interface<br>(Direction)   | FIFO Threshold                                                                                                                                                                                                                           | FIFO Burst                                                                                                                                                                                                               | FIFO Remote Burst |