# Phase-Locked Loop (ALTPLL) Megafunction User Guide

© November 2009 UG-ALTPLL-8.0

# Introduction

The Phase-Locked Loop (PLL) is a closed-loop frequency-control system that compares the phase difference between the input signal and the output signal of a voltage-controlled oscillator (VCO). The negative feedback loop of the system forces the PLL to be phase-locked.

PLLs are widely used in telecommunications, computers, and other electronic applications. The PLL can be used to generate stable frequencies, recover signals from a noisy communication channel, or distribute clock signals throughout your design.

# **Building Blocks of a PLL**

This section describes the basic building blocks of a PLL and common terms to describe PLL behaviors.

For details about device-specific PLL structure and PLL implementation, refer to the relevant device handbook.

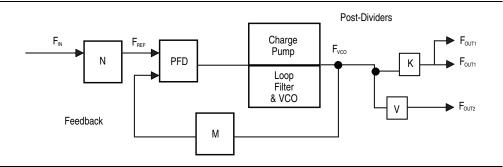

Figure 1 shows a typical PLL block diagram of a PLL.

Figure 1. PLL Block Diagram

The PLL consists of a pre-divider counter (N counter), a phase-frequency detector (PFD) circuit, a charge pump, loop filter, a VCO, a feedback multiplier counter (M counter), and post-divider counters (K and V counters).

The PFD detects the differences in phase and frequency between its reference signal ( $f_{REF}$ ) and feedback signal (Feedback), controls the charge pump, and controls a loop filter that converts the phase difference to a control voltage. This voltage controls the VCO.

Based on the control voltage, the VCO oscillates at a higher or lower frequency, which affects the phase and frequency of the Feedback signal. After the  $f_{REF}$  signal and the Feedback signal have the same phase and frequency, the PLL is said to be phase-locked.

Page 2 Introduction

Inserting the M counter in the feedback path causes the VCO to oscillate at a frequency that is M times the frequency of the  $f_{REF}$  signal. The  $f_{REF}$  signal is equal to the input clock ( $f_{IN}$ ) divided by the pre-scale counter (N).

The reference frequency is described by the equation  $f_{REF} = f_{IN}/N$ . The VCO output frequency is  $f_{VCO} = f_{IN} \times M/N$ , and the output frequency of the PLL is described by the equation  $f_{OUT} = (f_{IN} \times M)/(N \times K)$  for the signals shown in Figure 1 on page 1.

The following terms are commonly used to describe the behavior of a PLL:

■ PLL lock time—Also known as the PLL acquisition time, PLL lock tme is the amount of time required by the PLL to attain the target frequency and phase relationship after power-up, after a programmed output frequency change, or after a reset of the PLL.

Simulation software does not model a realistic PLL lock time. Simulation shows an unrealistically fast lock time. For the actual lock time specification, refer to the device datasheet.

- **PLL resolution**—The minimum frequency increment value of a PLL VCO. The value is based on the number of bits in the *M* and *N* counter.

- **PLL sample rate**—The  $f_{REF}$  sampling frequency required to perform the phase and frequency correction in the PLL. The PLL sample rate is  $f_{REF}/N$ .

# **ALTPLL Megafunction Overview**

The Quartus  $^{\odot}$  II software provides the ALTPLL MegaWizard  $^{\text{TM}}$  interface to specify the PLL circuitry in the supported devices. You can use the MegaWizard Plug-In Manager to configure the ALTPLL MegaWizard interface and build ALTPLL megafunctions efficiently. The ALTPLL MegaWizard interface appears in the I/O category in the MegaWizard Plug-In Manager.

This user guide describes the major features of the ALTPLL megafunction that you can configure in the MegaWizard interface. This user guide also includes design examples.

This user guide assumes that you are familiar with megafunctions and how to create them. If you are unfamiliar with Altera megafunctions or the MegaWizard Plug-In Manager, refer to the *Megafunction Overview User Guide*.

# **Device Family Support**

The ALTPLL megafunction supports the following series of devices:

- Stratix<sup>®</sup> series

- Cyclone<sup>®</sup> series

- Arria<sup>®</sup> series

- Hardcopy<sup>®</sup> series (except the HardCopy device family)

ALTPLL Megafunction Features Page 3

# **ALTPLL Megafunction Features**

This section describes the PLL types, operation modes, and advanced features available for configuration in the ALTPLL megafunction. Each PLL feature includes a table that compares the PLL feature in the supported devices, and describes the relevant parameter settings.

For information about PLL timing specifications, refer to the *DC & Switching Characteristics* chapter in the relevant device handbook.

The ALTPLL megafunction provides the following features:

- "Types of PLLs"

- "Operation Modes" on page 4

- "Output Clocks" on page 10

- "Advanced Features" on page 15

- "Advanced Control Signals (pllena, areset, pfdena)" on page 15

- "Clock Switchover" on page 17

- "Spread-Spectrum Clocking" on page 20

- "Gated Lock and Self-Reset" on page 21

- "Programmable Bandwidth" on page 24

- "Advanced PLL Parameters" on page 26

- "PLL Dynamic Reconfiguration" on page 26

- "Dynamic Phase Configuration" on page 29

# **Types of PLLs**

The following section describes the types of PLL that are available in the ALTPLL megafunction. The types of PLL supported by the megafunction depend on the device family. Device families typically support one or two PLL types. For example, the Stratix series supports two types of PLLs, and the Cyclone series supports only one type. The two PLL types supported within a device family are identical in their analog portions and differing slightly in the digital portion. For example, more counters on one type than another.

In Arria GX, Stratix II, Stratix II GX, Stratix and Stratix GX device families, and their corresponding HardCopy device families, the PLLs belong to the fast or enhanced PLL type. In Arria II GX, Stratix III device families onwards, and their corresponding HardCopy device families, the fast and enhanced PLLs are named Left\_Right and Top\_Bottom respectively. In the Cyclone series of devices, each device family supports only one PLL type. However, the features available vary among device families. For example, the Cyclone III PLL supports dynamic reconfiguration but the Cyclone II PLL does not support this feature. Only the fast or Left\_Right PLL type supports LVDS functionality.

For information about the arrangement of PLLs in a specific device, refer to the relevant device handbook.

# **Parameter Setting**

You select the PLL type on the **General/Modes** page of the ALTPLL MegaWizard interface. The list of available PLL types to choose from depends on the device family you selected. If you select **Select the PLL type automatically**, the ALTPLL MegaWizard interface selects the best possible PLL type, based on other options you set in the ALTPLL MegaWizard interface.

#### Total Number of PLL Available in Each Supported Device Family

Table 1 shows the total number of PLLs available for configuration and the PLL types supported by the ALTPLL megafunction for each device family.

|               | •                    |                           |

|---------------|----------------------|---------------------------|

| Device Family | Total Number of PLLs | PLL Types                 |

| Arria GX      | 8                    | Enhanced and Fast         |

| Arria II GX   | 6                    | Left_Right                |

| Stratix IV    | 12                   | Top_Bottom and Left_Right |

| Stratix III   | 12                   | Top_Bottom and Left_Right |

| Stratix II    | 12                   | Enhanced and Fast         |

| Stratix II GX | 8                    | Enhanced and Fast         |

| Stratix       | 12                   | Enhanced and Fast         |

| Stratix GX    | 8                    | Enhanced and Fast         |

| Cyclone IV    | 4                    | Cyclone IV PLL            |

| Cyclone III   | 4                    | Cyclone III PLL           |

| Cyclone II    | 4                    | Cyclone II PLL            |

| Cyclone       | 2                    | Cyclone PLL               |

Table 1. Total Number of PLLs per Device Family

# **Operation Modes**

The ALTPLL megafunction supports up to five different clock feedback modes, depending on the selected device family. Each mode allows clock multiplication and division, phase shifting, and duty-cycle programming.

The following list describes the operation modes for the ALTPLL megafunction:

- Normal mode—The PLL feedback path source is a global or regional clock network, minimizing clock delay to registers for that clock type and specific PLL output. You can specify PLL output that is compensated.

- Source-Synchronous mode—The data and clock signals arrive at the same time at the input pins. In this mode, the signals are guaranteed to have the same phase relationship at the clock and data ports of any Input Output Enable (IOE) register.

- Zero-Delay Buffer mode—The PLL feedback path is confined to the dedicated PLL external output pin. The clock port driven off-chip is phase aligned with the clock input for a minimal delay between the clock input and the external clock output.

- No Compensation mode—The PLL feedback path is confined to the PLL loop. It has no clock network or other external source. A PLL in no-compensation mode has no clock network compensation, but clock jitter is minimized.

■ External Feedback mode—The PLL compensates for the fbin feedback input to the PLL. The delay between the input clock pin and the feedback clock pin is minimized.

For detailed information about the PLL operation modes in a specific device, refer to the *Clock Management* chapter in the relevant device handbooks.

## **Operation Modes Supported in Each Device Family**

Table 2 summarizes the operation modes supported for each device family.

**Table 2.** PLL Types and Modes Supported in Different Device Families

| Device Family | Normal         | Source-Synchronous | Zero-Delay Buffer | No Compensation | External Feedback |

|---------------|----------------|--------------------|-------------------|-----------------|-------------------|

| Arria GX      | All PLL types  | All PLL types      | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Arria II GX   | Left_Right PLL | Left_Right PLL     | Left_Right PLL    | Left_Right PLL  | _                 |

| Stratix IV    | All PLL types  | All PLL types      | All PLL types     | All PLL types   | All PLL types     |

| Stratix III   | All PLL types  | All PLL types      | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Stratix II    | All PLL types  | All PLL types      | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Stratix II GX | All PLL types  | All PLL types      | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Stratix       | All PLL types  | _                  | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Stratix GX    | All PLL types  | _                  | Enhanced PLL      | All PLL types   | Enhanced PLL      |

| Cyclone IV    | All PLL types  | All PLL types      | All PLL types     | All PLL types   | _                 |

| Cyclone III   | All PLL types  | All PLL types      | All PLL types     | All PLL types   | _                 |

| Cyclone II    | All PLL types  | All PLL types      | All PLL types     | All PLL types   |                   |

| Cyclone       | All PLL types  |                    | All PLL types     | All PLL types   | <u>-</u>          |

#### **Parameter Settings**

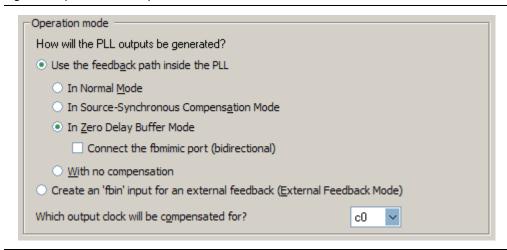

The following section describes how to set the operation mode for the PLL using the ALTPLL MegaWizard interface. The parameter settings are located on the **General/Modes** page of the ALTPLL MegaWizard interface. Figure 2 on page 5 and Figure 3 on page 6 show the options you can select from the page. Table 3 on page 6 and Table 4 on page 7 describe the options.

Figure 2. Operation Mode Options

Page 6 ALTPLL Megafunction Features

**Table 3.** Operation Mode Options and Descriptions

| Option                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use the feedback path inside the PLL                                     | Specify which operation mode to use.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                          | For source-synchronous mode, zero-delay buffer mode, and external feedback mode, you must make PLL Compensation assignments using the Assignment Editor in addition to setting the appropriate mode in the megafunction. The assignment allows you to specify an output pin as a compensation target for a PLL in zero-delay buffer mode or external feedback mode, or to specify an input pin or group of input pins as compensation targets for a PLL in source-synchronous mode. |

| Create an 'fbin' input for an external feedback (External Feedback Mode) | Select this option to set the PLL in external feedback mode. The fbin port is the input port to the PLL from the external feedback path. In this mode, the PLL compensates for the fbin port. The delay between the input clock pin and the feedback clock pin is minimized.                                                                                                                                                                                                        |

| Which output clock will be compensated for?                              | Specify which output port of the PLL is to be compensated for. The drop down list contains all output clock ports for the selected device. The correct output clock selection depends on the operation mode that you select. For example, for normal mode, select the core output clock. For zero-delay buffer mode or external feedback mode, select the external output clock.                                                                                                    |

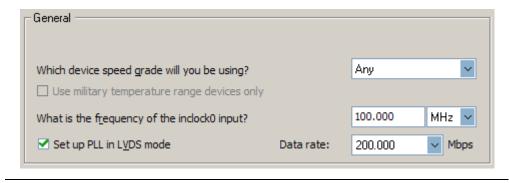

Figure 3. General Options on the General/Modes page of the ALTPLL MegWizard Interface

Option Description Which device speed grade will you be Specify the speed grade if you are not already using a usina? device with the fastest speed. The lower the number, the faster the speed grade. Specify the frequency of the input clock signal. What is the frequency of the inclock0 input? For information about how to determine the lock range of your PLL, refer to "Guidelines to Determine the PLL Lock Range" on page 7. For information about how to expand the lock range of your PLL, refer to "Guidelines to Expand the PLL Lock" Range" on page 7. Select this option when you want the PLL to supply the Set up PLL in LVDS mode necessary clocking signals to the LVDS transmitter or receiver. In this mode, the PLL type and operation mode are forced to fast PLL and normal mode. respectively. This option creates two new output ports —sclkout and enable. For details about these ports, refer to "Output Clocks" on page 10. This option is available only for the Arria GX. Stratix II. Stratix II GX, and Hard Copy II device families. Data rate Specify the data rate for the PLL in LVDS mode. This option is available only if Set up PLL in LVDS mode is enabled.

Table 4. Operation Mode Options and Descriptions

#### **Guidelines to Determine the PLL Lock Range**

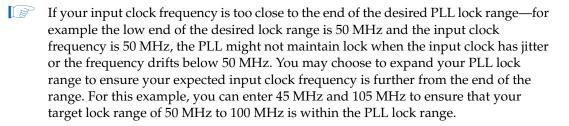

The PLL lock range is the range between the minimum (Freq min lock parameter) and maximum (Freq min lock parameter) input frequency values for which the PLL can achieve lock. The Quartus II software shows these input frequency values in the PLL Summary report located under Resource Section of the Fitter folder in the Compilation Report. Changing the input frequency may cause the PLL to lose lock, but while the input clock remains within the minimum and maximum frequency specifications, the PLL is able to achieve lock.

# **Guidelines to Expand the PLL Lock Range**

The Quartus II software does not necessarily pick values for the PLL parameters to maximize the lock range. For example, you specify a 75 MHz input clock in the ALTPLL MegaWizard interface, the actual PLL lock range may be between 70 MHz to 90 MHz. If your application requires a lock range of 50 MHz to 100 MHz, the default lock range of this PLL is insufficient.

For devices that support clock switchover in PLLs, you can use the ALTPLL MegaWizard interface to maximize the lock range

To extract valid parameter values to maximize your PLL lock range, perform the following steps:

- 1. In the schematic editor, double-click the ALTPLL instance in your design to open the ALTPLL MegaWizard interface.

- 2. For **What is the frequency of your inclock0 input?**, type the value of the low end of you desired PLL lock range. For example, if your application requires a lock range of 50 MHz to 100 MHz, type 50 MHz.

- 3. Turn on Create output file(s) using the 'Advanced' PLL parameters.

- 4. Turn on **Create an 'inclk1' for a second inclk** and enter the high end of your lock range as the frequency for inclk1. For example, if your application requires a lock range of 50 MHz to 100 MHz, type 100 MHz.

- 5. Complete the remaining pages in the ALTPLL MegaWizard interface.

- 6. Compile your project and note the lock range shown in the PLL Summary report. If it is satisfactory, note all of the values for the PLL from this report, such as the *M* value, *N* value, charge pump current, loop filter resistance, and loop filter capacitance.

- 7. In the schematic editor, double-click the ALTPLL instance in your design to open the ALTPLL MegaWizard interface.

- 8. Turn off Create an 'inclk1' for a second inclk.

- 9. Click **Finish** to update the PLL wrapper file.

- 10. In a text editor, open the PLL wrapper file. If the wrapper file is in Verilog format, go to the **defparam** section. If the wrapper file is in VHDL HDL, go to the generic map section. Modify all of the values for the parameters listed in step 6. Save the changes.

- 11. Compile your project.

- 12. Check the PLL Summary report to confirm the PLL lock range meets your requirements. The modified PLL should have the desired lock range.

The Quartus II software prompts an error message if it is unable to implement your preferred lock range using this procedure. Therefore, you have to look into other options, such as PLL reconfiguration to support your input frequency range.

## Guidelines to Set Up Stratix III and Stratix IV PLLs for LVDS Interfacing

This section describes how to configure a PLL in a Stratix III or Stratix IV device to clock the ALTLVDS megafunction block. The ALTLVDS megafunction provides SERDES transmitter and receiver functionality commonly used in LVDS interfacing.

For details about the ALTLVDS megafunction including clocking the ALTLVDS megafunction using the ALTPLL megafunction, refer to the SERDES Transmitter/Receiver (ALTLVDS) Megafunction User Guide.

To configure a PLL on a Stratix III or Stratix IV device to clock an ALTLVDS megafunction block, select the options and values shown in Table 5.

**Table 5.** Options to Configure a PLL on a Stratix III or Stratix IV Device

| Option                                 |                                                                                                     | Value                                                                                                                 |                                                                                                                 |

|----------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Which PLL type will you be using?      | Left_Right PLL                                                                                      |                                                                                                                       |                                                                                                                 |

| How will the PLL outputs be generated? | In Source-Synchronous Comp                                                                          | pensation mode                                                                                                        |                                                                                                                 |

| On the Output                          | c0                                                                                                  | c1                                                                                                                    | c2                                                                                                              |

| clocks page                            | This clock signal is the high-speed serial clock (fast clock) signal connected to the rx_inclock or | This clock signal is the load enable signal connected to the rx_enable or tx_enable port of the ALTLVDS megafunction. | This clock signal is the slow clock signal that feeds the synchronization register of the ALTLVDS megafunction. |

|                                        | tx_inclock port of the ALTLVDS megafunction                                                         | Output frequency = data rate/deserialization factor                                                                   | Output frequency = data rate/deserialization factor                                                             |

|                                        | Output frequency = data rate                                                                        | Phase shift = [(deserialization factor –                                                                              | Phase shift =                                                                                                   |

|                                        | Phase shift = -180 degrees                                                                          | 2)/deserialization factor] × 360 degrees                                                                              | (-180/deserialization factor)                                                                                   |

|                                        | Duty cycle = 50%                                                                                    | Duty cycle = (100/deserialization factor)%                                                                            | degrees                                                                                                         |

|                                        |                                                                                                     |                                                                                                                       | Duty cycle = 50%                                                                                                |

#### **Guidelines to Simulate External Feedback Board Delay**

The PLL external feedback board delay option is available for Arria GX, Cyclone, HardCopy series, Stratix, Stratix GX, Stratix II, and Stratix II GX device families only. The functional and timing models of these devices do not support the simulation of external feedback. To simulate the external feedback mode, perform the following steps:

- 1. In the Quartus II software, open an existing project or create a new project.

- 2. On the Assignments menu, click **Assignment Editor**.

- 3. In the **Category** bar, under Timing, click **All**.

- 4. In the spreadsheet, double-click an empty row in the **To** cell and either type in the pin name or click the arrow to use the **Node Finder** to search for the external feedback input pin.

- Double-click the Assignment Name cell, and select PLL External Feedback Board Delay.

Page 10 ALTPLL Megafunction Features

6. In the **Value** cell, double-click and type the amount of time for the signal to propagate between the external clock output pin through the trace on the board and into the external feedback input pin.

7. Simulate your design.

The behavioral models for the ALTPLL megafunction reside in the \quartus\eda\sim\_lib directory. The altera\_mf.vhd file contains the VHDL behavioral models and the altera\_mf.v file contains the Verilog HDL behavioral models. The behavioral model does not perform parameter error checking, so you must specify valid values.

# **Output Clocks**

The PLL can generate a number of clock output signals depending on the PLL type and the device family that you select in the ALTPLL MegaWizard interface. For example, in a Stratix IV device, a Left\_Right PLL can generate seven clock output signals, and a Top\_Bottom PLL can generate as many as 10 clock output signals. The generated clock output signals are used to clock the core or external blocks outside of the core.

The ALTPLL megafunction does not have a dedicated output enable port, you can disable the PLL output. You can use the pllena signal or the areset signal to disable the PLL output counters, and thereby disable the PLL output clocks. Another possible method is to feed the PLL output clock signals to the ALTIOBUF megafunction and use the enable output ports of the resulting buffers to disable the signals.

For information about clock networks in a specific device, refer to the "Clock Networks" section in the relevant device handbook.

#### **Parameter Settings**

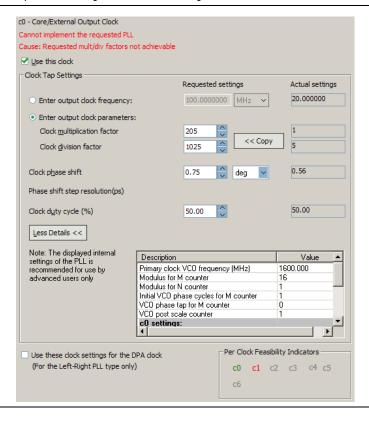

The **Output Clocks** page of the ALTPLL MegaWizard interface contains the parameter settings for the clock output signals. Figure 4 shows a screenshot of the page to configure the c0 clock output signal of the ALTPLL megafunction.

The output clock port can be used as a core output clock or an external output clock port. The core output clock is used to feed the FPGA core and the external output clock is used to feed the dedicated pins on the FPGA.

Figure 4. The Output Clocks Page of the ALTPLL MegaWizard Interface

Each option has the following two columns:

- Requested setting

- Actual setting

The requested settings are the settings that you want to implement, and the actual settings are the settings closest values that can be implemented in the PLL circuit to best approximate the requested settings. Use the values in the actual settings column as a guide to adjust the requested settings. If the requested settings for one of the output clocks cannot be approximated, the ALTPLL MegaWizard interface produces a warning message at the top of every page. To determine the output clocks that contain unachievable settings, turn on **Per Clock Feasibility Indicators** at the bottom of the

ALTPLL MegaWizard interface page. The output clock name in red is the name of the clock with unachievable settings. The clock listed in green has no settings issues, and the grayed-out names are the unselected output clocks. You must adjust the requested settings for the affected output clocks to resolve the warning messages, or use another Altera device that meets your desired timing specifications.

To generate an output clock port in your ALTPLL megafunction instance, select **Use this clock**.

The output clock port that is to be compensated for is enabled by default. It cannot be disabled, unless you select a different output clock port to be compensated for.

The rest of the options on the page allow you to set the following output clock values:

- frequency

- phase shift

- duty cycle

The phase shift option allows you to set the programmable phase shift for an output clock signals. The smallest phase shift is 1/8th of VCO period. For degree increments, the maximum step size is 45 degrees. You can set smaller steps using the clock multiplication and division factors options. For example, if the post-scale counter is 32, the smallest phase shift step is 0.1°. The up and down buttons let you cycle through phase shift values. Alternatively, you can enter a number in the phase shift field manually instead of using the buttons.

Instead of specifying frequency of the output clock signal, you can also specify the multiplication and division factors of the signal in the requested settings column. The formula for an output clock frequency is:

**Equation 1.** PLL Output Clock Frequency

Output clock frequency = Input clock frequency  $\times \frac{\text{multiplication factor}}{\text{division factor}}$

The ALTPLL MegaWizard interface calculates the simplest fraction, and displays it in the actual settings column. For example, if the input clock frequency is 100 MHz, and the requested multiplication and division factors are 205 and 1025 respectively, the output clock frequency is calculated as  $100 \times 205/1025=20$  MHz. The actual settings reflect the simplest fraction — the actual multiplication factor is 1, and the actual division factor is 5. You can use the copy button to copy values from the actual settings to the requested settings.

The actual values of multiplication and division factors are affected when you select Use these clock settings for the DPA clock or Set up PLL in LVDS mode.

Select **Use these clock settings for the DPA clock** if you want the output clock signal of the PLL to drive the input clock port of the DPA block in the ALTLVDS megafunction. This option is available only for Stratix III and Stratix IV devices.

ALTPLL Megafunction Features Page 13

# Parameter Settings When "Set up PLL in LVDS mode" Option is Enabled

The following parameter settings apply only when **Set up PLL in LVDS Mode** is turned on for Arria GX, Stratix II, Stratix II GX, and HardCopy II fast PLLs.

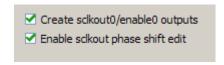

When you turn on **Set up PLL in LVDS mode**, two additional options are available on the **Output Clocks** pages for c0 and c1. Figure 5 and Figure 6 show the additional options to configure the c0 output clock signal.

Figure 5. Additional Options to Configure the c0 Output Clock Signal

Turn on **Create sclkout0/enable0 outputs** to create the sclkout0 and enable0 ports. The sclkout0 port is the serial clock output port, and the enable0 port is the enable port.

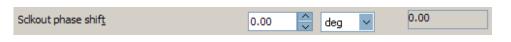

Figure 6. Sclkout Phase Shift Option

The sclkout phase shift option allows you to edit the phase shift of the sclkout signal (in this case, the sclkout0 signal).

Only two pairs of sclkout and enable ports can be created in an ALTPLL megafunction. The sclkout0 and enable0 ports are for the c0 output clock, and the sclkout1 and enable1 ports are for the c1 output clock.

Page 14 ALTPLL Megafunction Features

# **Summary of PLL Output Clocks**

Table 6 summarizes and compares properties of the clock output ports per PLL for each PLL type in the supported device families. The number of clock output ports shown in the table for each device family can be set as internal or external clock output port unless described otherwise.

Table 6. Number of Clock Output Ports per PLL

| Device Family | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL | Cyclone Series PLL |

|---------------|------------|------------|--------------|----------|--------------------|

| Arria GX      | _          | _          | 6            | 4        | _                  |

| Arria II GX   | _          | 7          | _            | _        | _                  |

| Stratix IV    | 10         | 7          | _            | _        | _                  |

| Stratix III   | 10         | 7          | _            | _        | _                  |

| Stratix II    | _          | _          | 6            | 4        | _                  |

| Stratix II GX | _          | _          | 6            | 4        | _                  |

| Stratix       | _          | _          | 6 (1)        | 3        | _                  |

| Stratix GX    | _          | _          | 6 (1)        | 3        | _                  |

| Cyclone IV    | _          | _          | _            | _        | 5                  |

| Cyclone III   | _          | _          | _            | _        | 5                  |

| Cyclone II    | _          | _          | _            | _        | 3                  |

| Cyclone       | _          | _          | _            | _        | 2 (2)              |

#### Notes to Table 6:

- (1) Only four ports can be used as the external clock output ports.

- (2) Only one port can be used as the external clock output port.

ALTPLL Megafunction Features Page 15

# **Advanced Features**

Altera devices offer on-chip PLL features previously found only in high-end discrete PLL devices. These advanced features, including gated lock, clock switchover, dynamic reconfiguration, programmable bandwidth, reconfigurable bandwidth, spread spectrum clocking, and post-scale counter cascading, increase system and device performance and provide advanced clock interfacing. The following sections define each advanced feature, and describe its application, and the parameter settings you must select in the ALTPLL MegaWizard interface to enable the feature.

# Advanced Control Signals (pllena, areset, pfdena)

You can use these three signals—pllena, areset, and pfdena—to observe and control PLL operation and resynchronization.

#### pllena

Use the pllena signal to enable or disable the PLL. When you deassert the pllena signal, the PLL does not drive any output clock signal and therefore it loses lock. All counters in the PLL, including the gated lock counter, return to the default state. When you assert the pllena signal, the PLL drives output clock signals and tries to gain lock. The single PLL enable port on each device is shared among all PLLs on the device. By default, the pllena signal is tied to VCC internally.

#### areset

The areset signal is the reset or resynchronization input for each PLL. The device input pin or internal logic can drive the areset signal. When you assert the areset signal, all counters in the PLL, including the gated lock counter, are reset to initial values, in which the PLL output is cleared and the PLL is in the out-of-lock state. The VCO is also reset to its nominal setting. When the areset signal is deasserted, the PLL resynchronizes its input and tries to gain lock.

You should include the areset signal in your designs if any of the following conditions hold:

- PLL reconfiguration or clock switchover is enabled in your design.

- Phase relationships between the PLL input and output clocks must be maintained after a loss-of-lock condition.

- The input clock to the PLL is not toggling or is unstable at power-up.

Assert the areset signal after the input clock is toggling while staying within the input jitter specification.

## pfdena

The pfdena signal enables or disables the PFD circuit. The PFD circuit is enabled by default. When the PFD circuit is disabled, the PLL output does not depend on the input clock, and tends to drift outside of the lock window. By default, the pfdena signal is tied to VCC internally.

Page 16 ALTPLL Megafunction Features

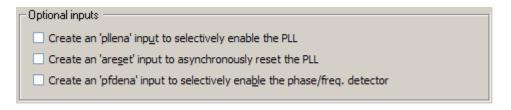

## **Parameter Settings**

For devices that support the advanced control signals—pllena, pfdena, and areset, the parameter settings for these signals are located on the **Inputs/Lock** or **Scan/Inputs/Lock** page of the ALTPLL MegaWizard interface. Figure 7 shows the options related to the advanced control signals. Turn on the control signal you want to create from the options available.

Figure 7. Options to Select the Advanced Control Signals

The deassertion of the pllena signal or the assertion of the areset signal does not disable the VCO, but instead resets the VCO to its nominal value. The only time that the VCO is completely disabled is when you do not have a PLL instantiated in your design.

## **Summary of Advanced Control Signals**

Table 7 summarizes the device families that support advanced control signals.

Table 7. Advanced Control Signals Support

| Device Family | Sup      | ported Advanced S | ignals |

|---------------|----------|-------------------|--------|

|               | pllena   | pfdena            | areset |

| Arria GX      | ✓        | ✓                 | ✓      |

| Arria II GX   |          | ✓                 | ✓      |

| Stratix IV    | _        | ✓                 | ✓      |

| Stratix III   | _        | ✓                 | ✓      |

| Stratix II    | ✓        | ✓                 | ✓      |

| Stratix II GX | ✓        | ✓                 | ✓      |

| Stratix       | ✓        | ✓                 | ✓      |

| Stratix GX    | ✓        | ✓                 | ✓      |

| Cyclone IV    | _        | ✓                 | ✓      |

| Cyclone III   | _        | ✓                 | ✓      |

| Cyclone II    | <b>✓</b> | ✓                 | ✓      |

| Cyclone       | <b>✓</b> | ✓                 | ✓      |

#### **Clock Switchover**

The clock switchover feature allows the PLL to switch between two input clocks. The clock switchover feature can be used for switching between clock inputs of different frequencies and is also useful for video applications that require a manual switch between operation frequencies. The clock switchover capability is widely implemented in telecommunication, storage, and server markets because these markets require highly reliable clocking schemes to ensure system reliability.

The following clock switchover modes are supported by the ALTPLL megafunction:

- Automatic switchover—The PLL monitors the currently used clock signal, and if

it stops toggling or loss-of-lock occurs, the PLL automatically switches to the other

clock signal (inclk0 or inclk1).

- Manual clock switchover—The clock switchover is controlled using the clkswitch signal.

The manual override feature available in automatic clock switchover is different from the manual clock switchover.

The requirements for use of the clock switchover feature vary among devices. For device-specific guidelines about how to use this feature, refer to the *Clock Networks* and *PLLs* chapter in the relevant device handbook.

# **Parameter Settings**

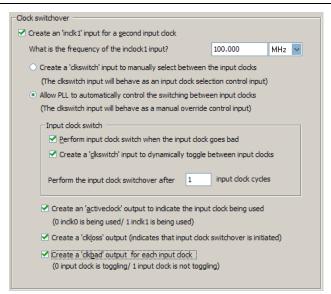

For devices that support the clock switchover feature, the parameter settings are located on the **Clock switchover** page of the ALTPLL MegaWizard interface. Figure 8 shows all the options available on the **Clock switchover** page for an Arria GX device.

Note that the options are device-dependent and what you see may differ from Figure 8.

Figure 8. Clock Switchover

Page 18 ALTPLL Megafunction Features

To enable the switchover feature, turn on **Create an 'inclk1' input for a second input clock**, and specify the frequency of the inclk1 signal. The inclk0 signal is by default the primary input clock signal of the ALTPLL megafunction.

Select the related option for manual or automatic clock switchover mode. For the automatic clock switchover mode, you can choose to create the clkswitch signal as a manual override. The automatic switchover is initiated during loss of lock or when the inclk0 signal stops toggling or when the clkswitch signal is asserted. You must specify the number of clock cycles to wait before the PLL performs the clock switchover. Note that the allowed number of clock cycles to wait is device-dependant.

You can use the optional signals – activeclock, clkloss, and clkbad—as indicators when you use the clock switchover feature.

Use the activeclock signal to monitor which input clock signal is driving the PLL. When the current clock signal is inclk0, the activeclock signal is low. When the current clock signal is inclk1, the activeclock signal is high.

Use the clkbad signals (clkbad0 and clkbad1) to monitor which input clock signal has stopped toggling. The clkbad0 signal is used to monitor the inclk0 signal, and the clkbad1 signal monitors the inclk1 signal. The clkbad0 signal goes high when the inclk0 signal stops toggling, and the clkbad1 signal goes high when the inclk1 signal stops toggling. The clkbad signals remain low when the input clock signals are toggling.

Use the clkloss signal to monitor the current status of the clock switchover. The clkloss signal goes high to indicate that loss of lock has been detected, and the clock switchover is initiated. The clkloss signal remains low when the clock switchover is not initiated. The clkloss signal is only available in Arria GX, Stratix, Stratix GX, Stratix II, and Stratix II GX devices.

The following top-level ports are created from these parameter settings:

- Input ports: inclk1 and clkswitch.

- Output ports: activeclock, clkloss, clkbad0, and clkbad1.

# **Summary of Automatic Clock Switchover Feature**

Table 8 and Table 9 summarize clock switchover support in the supported device families. Table 8 summarizes automatic clock switchover support, and Table 9 summarizes the manual clock switchover support.

**Table 8.** Automatic Clock Switchover Feature Support (Note 1)

| Device Family | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL | Cyclone Series PLL |

|---------------|------------|------------|--------------|----------|--------------------|

| Arria GX      | _          |            | Yes          | No       | _                  |

| Arria II GX   | _          | Yes        | _            | _        | _                  |

| Stratix IV    | Yes        | Yes        | _            | _        | _                  |

| Stratix III   | Yes        | Yes        | _            | _        | _                  |

| Stratix II    | _          | _          | Yes          | No       | _                  |

| Stratix II GX | _          | _          | Yes          | No       | _                  |

| Stratix       | _          | _          | Yes          | No       | _                  |

| Stratix GX    | _          | _          | Yes          | No       | _                  |

| Cyclone IV    | _          | _          | _            | _        | Yes                |

| Cyclone III   | _          | _          | _            | _        | Yes                |

| Cyclone II    | _          | _          | _            | _        | No                 |

| Cyclone       | _          | _          | _            | _        | No                 |

# Note to Table 8:

Table 9.

Manual Clock Switchover Feature Support

| Device        | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL    | Cyclone Series PLL |

|---------------|------------|------------|--------------|-------------|--------------------|

| Arria GX      | _          | _          | Yes          | Yes         | _                  |

| Arria II GX   | _          | Yes        | _            | _           | _                  |

| Stratix IV    | Yes        | Yes        | _            | _           | _                  |

| Stratix III   | Yes        | Yes        | _            | <del></del> | _                  |

| Stratix II    | _          | _          | Yes          | Yes         | _                  |

| Stratix II GX | _          | _          | Yes          | Yes         | _                  |

| Stratix       | _          |            | Yes          | No          | _                  |

| Stratix GX    | _          | _          | Yes          | No          | _                  |

| Cyclone IV    | _          | _          | _            | _           | Yes                |

| Cyclone III   | _          | _          | _            | _           | Yes                |

| Cyclone II    | _          | _          | _            | _           | Yes                |

| Cyclone       | _          | _          | _            | _           | No                 |

<sup>(1)</sup> Also supports automatic clock switchover feature with manual override control.

Page 20 ALTPLL Megafunction Features

# **Spread-Spectrum Clocking**

Spread-spectrum technology reduces electromagnetic interference (EMI) in a system. This technology works by distributing the clock energy over a broad frequency range.

The spread-spectrum clocking feature distributes the fundamental clock frequency energy throughout your design to minimize energy peaks at specific frequencies. By reducing the spectrum peak amplitudes, the feature makes your design more likely meets the EMI emission compliance standards, and reduces costs associated with traditional EMI containment.

The traditional methods for limiting EMI include shielding, filtering, and using multi-layer printed circuit boards. Multi-layer circuit boards are expensive and are not guaranteed to meet the EMI emission compliance standards. The use of spread-spectrum technology is simpler and more cost-effective than these other methods.

To use the spread-spectrum clocking feature, you must set the programmable bandwidth feature to **Auto**.

#### **Parameter Settings**

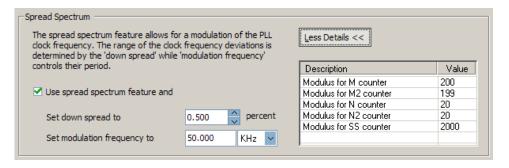

For devices that support spread-spectrum technology, the parameter settings are located on the **Bandwidth/SS** page of the ALTPLL MegaWizard interface, as shown in Figure 9.

Figure 9. Spread Spectrum Settings

To enable the spread-spectrum feature, turn on **Use spread spectrum feature**. Set the desired down spread percentage, and the modulation frequency. In Figure 9, the table on the right shows detailed descriptions of the current counter values.

The down spread percentage defines the modulation width or frequency span of the instantaneous output frequency resulting from the spread spectrum. When you use down spread, the modulation width falls at or below a specified maximum output frequency. The wider the modulation, the larger the band of frequencies over which the energy is distributed, and the more reduction is achieved from the peak. For example, with a down spread percentage of 0.5% and maximum operating frequency of 100 MHz, the output frequency is swept between 99.5 and 100 MHz.

The modulation frequency, often called sweep rate, defines how fast the spreading signal sweeps from the minimum to the maximum frequency.

Turning on spread-spectrum clocking creates no new top-level ports.

# **Summary of Spread-Spectrum Clocking Feature**

Table 10 summarizes the PLL types that support the spread-spectrum clocking feature.

**Table 10.** Spread-Spectrum Clocking Feature

| Device        | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL | Cyclone Series PLL |

|---------------|------------|------------|--------------|----------|--------------------|

| Arria GX      | _          | _          | Yes          | No       | _                  |

| Arria II GX   | _          | No         | _            | _        | _                  |

| Stratix IV    | Yes (1)    | Yes (1)    | _            | _        | _                  |

| Stratix III   | Yes (1)    | Yes (1)    | _            | _        | _                  |

| Stratix II    | _          |            | Yes          | No       | _                  |

| Stratix II GX | _          | _          | Yes          | No       | _                  |

| Stratix       | _          |            | Yes          | No       | _                  |

| Stratix GX    | _          | _          | Yes          | No       | _                  |

| Cyclone IV    | _          | _          | _            | _        | No                 |

| Cyclone III   | _          |            | _            | _        | No                 |

| Cyclone II    | _          | _          | _            | _        | No                 |

| Cyclone       | _          | _          | _            | _        | No                 |

#### Note to Table 10:

(1) This device can accept a spread-spectrum input with typical modulation frequencies, but it cannot generate spread-spectrum clock signals internally.

## **Gated Lock and Self-Reset**

The lock time of a PLL is defined as the amount of time required by the PLL to attain the target frequency and phase relationship after device power-up, after a change in the PLL output frequency, or after resetting the PLL.

A PLL might lose lock for a number of reasons, such as the following causes:

- Excessive jitter on the input clock.

- For PLL input jitter specification, refer to the *DC and Switching Characteristics* chapter in the relevant device handbook.

- Excessive switching noise on the clock inputs of the PLL.

- Excessive noise from the power supply can cause high output jitter and possible loss of lock.

- A glitch or stopping of the input clock to the PLL.

- Resetting the PLL by asserting the areset or pllena ports of the PLL.

- An attempt to reconfigure the PLL might cause the M counter, N counter, or phase shift to change, which causes the PLL to lose lock. However, changes to the post-scale counters do not affect the PLL locked signal.

- PLL input clock frequency drifts outside the lock range specification.

- The PFD is disabled using the pfdena port. When this happens, the PLL output phase and frequency tend to drift outside of the lock window.

Page 22 ALTPLL Megafunction Features

The ALTPLL megafunction allows you to monitor the PLL locking process using a lock signal named locked and also allows you to set the PLL to self-reset on loss of lock.

#### **Gated Lock**

Some devices support a gated lock signal that allows you to configure a programmable 20-bit counter that holds the lock signal low for a user-specified number of input clock transitions. This is useful to eliminate the false toggling of the lock signal as the PLL begins tracking the reference clock. Gated lock allows the PLL to lock before asserting the locked signal, providing a stabilized lock signal.

An asserted locked signal indicates the PLL clock output is aligned with the PLL reference input clock. The locked signal might toggle as the PLL begins tracking the reference clock. To avoid such a false lock indication, use a gated lock signal. A gated locked signal or an ungated locked signal can feed a logic array or an output pin. When you must reset the gated counter, reset the PLL by asserting the areset signal or the pllena signal.

Figure 10 shows the timing waveform for gated and ungated locked signals.

Reference Clock

Feedback Clock

Locked

Gated Lock

Figure 10. Input and Output Ports of the ALTPLL Megafunction Block

# Self-Reset on Loss of Lock

This feature allows the PLL to self-reset upon loss of lock, normally for the same reasons described in "Gated Lock and Self-Reset" on page 21.

#### **Parameter Settings**

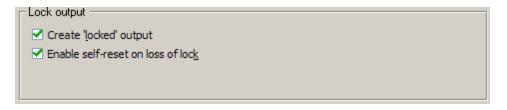

To enable the locked signal, and the self-reset feature in the ALTPLL megafunction, use the parameter settings on the **Scan/Inputs/Lock** or **Inputs/Lock** page of the ALTPLL MegaWizard interface. Figure 11 shows the related options on the **Scan/Inputs/Lock** or **Inputs/Lock** page for an Arria II GX device.

Note that the options are device-dependent and what you see may differ from Figure 11.

Figure 11. Lock Output Options

Turning on **Create 'locked' output** creates an output port named locked in the ALTPLL megafunction block.

Turning on Enable self-reset on loss of lock enables the self-reset feature.

In devices that support gated lock, another option appears on the page, as shown in Figure 12. Turning on this option enables the gated lock circuitry to gate the locked signal. You must specify the number of PLL input clock cycles to hold the locked signal low after the PLL is initialized. This value is used by the gated lock counter. The value ranges from 1 to 1,048,575 clock cycles.

Figure 12. Hold Locked Output Option

## Calculating the Value of Gated Lock Counter

To calculate the number of clock cycles needed, you must know the maximum lock time of the PLL, and the period of the PLL input clock. The lock time of the PLL is listed in the "PLL Timing Specifications" section of the DC & Switching Characteristics chapter of the device handbook. The period of the PLL input clock is user-specified. For example, if the maximum lock time of a PLL is 1 ms, and its input clock frequency is 100 MHz which corresponds to a 10 ns clock period, you calculate the value of the gated lock counter, by dividing 1 ms by 10 ns. The result is 100,000 clock cycles.

Only the locked port is created from these parameter settings.

#### Summary of Gated Lock Signals and Self-Reset on Loss of Lock

Table 11 summarizes the device families that support the gated lock and self-reset on loss of lock features.

Table 11. Gated Lock Signals and Self-Reset on Loss of Lock (Part 1 of 2)

| Device Family | Gated Lock Support | Self-Reset on Loss of Lock |

|---------------|--------------------|----------------------------|

| Arria GX      | ✓                  | _                          |

| Arria II GX   | _                  | ✓                          |

| Stratix IV    | _                  | ✓                          |

| Stratix III   | _                  | ✓                          |

| Stratix II    | ✓                  | _                          |

| Stratix II GX | <b>✓</b>           | _                          |

| Stratix       | _                  | _                          |

Page 24 ALTPLL Megafunction Features

**Table 11.** Gated Lock Signals and Self-Reset on Loss of Lock (Part 2 of 2)

| Stratix GX  | _ | _ |

|-------------|---|---|

| Cyclone IV  | _ | ✓ |

| Cyclone III | _ | ✓ |

| Cyclone II  | ✓ | _ |

| Cyclone     | _ | _ |

### **Programmable Bandwidth**

The PLL bandwidth is defined as the ability of the PLL to track the input clock and jitter. The bandwidth is measured by the -3 dB frequency of the closed-loop gain in the PLL, or approximately the unity gain point of the PLL open loop response. Altera devices provide a programmable PLL bandwidth feature that allows you to configure the characteristics of the PLL loop filter. Most loop filters contain only passive components, such as resistors and capacitors, which consumes board space. Altera FPGAs already contain these components, and by using the programmable bandwidth feature, you can control how the components affect the PLL bandwidth. This includes controlling the charge pump current, loop filter resistance, and high frequency capacitance values. The charge pump current affects the PLL bandwidth directly. The higher the charge pump current, the higher the PLL bandwidth.

For details about the PLL bandwidth range in a specific device, refer to the relevant device handbook.

#### **Parameter Settings**

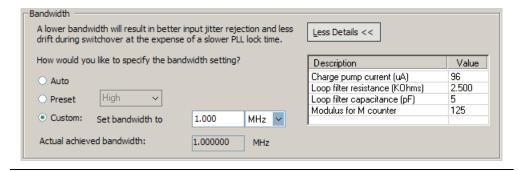

The parameter settings to configure the bandwidth of the ALTPLL megafunction are located on the **Bandwidth/SS** page of the ALTPLL MegaWizard interface.

Figure 13 shows the bandwidth configuration options on the **Bandwidth/SS** page.

Figure 13. Bandwidth Configuration Options

The following describes the preset values that you can choose:

- **Low**—PLL with a low bandwidth has better jitter rejection but a slower lock time.

- **High**—PLL with a high bandwidth has a faster lock time but tracks more jitter.

- Medium—A medium bandwidth offers a balance between lock time and jitter rejection.

If you select **Auto**, the ALTPLL MegaWizard interface chooses the best possible bandwidth values to achieve the desired PLL settings. In some cases, you can get a bandwidth value outside the **Low** and **High** preset range.

To set the bandwidth manually, select **Custom**, and specify the value. The compiler attempts to achieve the value that you specify, or the closest possible value to achieve your desired setting. You can check the bandwidth value in the compilation report.

The table on the right in Figure 13 on page 24 shows the values of the charge pump current, loop filter resistance and capacitance, and the *M* counter.

An advanced level of control is also possible for precise control of the PLL loop filter characteristics. This level allows you to select the charge pump current, and loop filter resistance and capacitance values explicitly. The advanced parameters are: charge\_pump\_current, loop\_filter\_r, and loop\_filter\_c.

For more details about these parameters, refer to "Ports and Parameters" on page 40.

You can use the programmable bandwidth feature with the clock switchover or spread-spectrum features to get the PLL output settings that you desire. You must set the bandwidth to **Auto** if you want to enable the spread-spectrum feature.

For details about the PLL bandwidth range for a specific device, refer to the relevant device handbook.

These parameter settings create no additional top-level ports.

## **Summary of Programmable Bandwidth Support**

Table 12 summarizes programmable bandwidth support in the different device families.

| <b>Table 12.</b> Programmable Bandwidth Suppo | • Programmable band | յայսըը ծաքք | υrι |

|-----------------------------------------------|---------------------|-------------|-----|

|-----------------------------------------------|---------------------|-------------|-----|

| Device Family | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL    | Cyclone Series PLL |

|---------------|------------|------------|--------------|-------------|--------------------|

| Arria GX      | _          | _          | Yes          | Yes         | _                  |

| Arria II GX   | _          | Yes (1)    | _            | _           | _                  |

| Stratix IV    | Yes (1)    | Yes (1)    | _            | <del></del> | _                  |

| Stratix III   | Yes (1)    | Yes (1)    | _            | _           | _                  |

| Stratix II    | _          | _          | Yes          | Yes         | _                  |

| Stratix II GX | _          | _          | Yes          | Yes         | _                  |

| Stratix       | _          |            | Yes          | No          | _                  |

| Stratix GX    | _          | _          | Yes          | No          | _                  |

| Cyclone IV    | _          | _          | _            | _           | Yes (1)            |

| Cyclone III   | _          | _          | _            | _           | Yes (1)            |

| Cyclone II    | _          | _          | _            | _           | No                 |

| Cyclone       | _          | _          | _            | _           | No                 |

#### Note to Table 12:

(1) This device family supports only **Auto** and preset values.

Page 26 ALTPLL Megafunction Features

#### **Advanced PLL Parameters**

The ALTPLL MegaWizard interface provides an option for you to generate output files using the ALTPLL advanced parameters. Examples of advanced parameters are charge\_pump\_current, loop\_filter\_r, and loop\_filter\_c. This option is supported in all Altera devices.

This option is intended for advanced users who know the exact details of their PLL configuration and for users who understand the parameters well enough to set them optimally. The files generated are not intended to be re-used by the ALTPLL MegaWizard interface, because after the ALTPLL megafunction output files are specified using the advanced parameters, the Quartus II compiler cannot change them. For example, the compiler cannot perform optiomization. Thus, your design cannot benefit from improved algorithms to pick better settings or to make changes to some settings that the ALTPLL MegaWizard interface finds to be incompatible with your design.

## **Advanced Parameter Settings**

Altera recommends you not to use these parameters unless you are an advanced user.

The parameter settings to generate output files using advanced PLL parameters are located on the **Scan/Inputs/Lock** or **Inputs/Lock** page of the ALTPLL MegaWizard interface. Figure 14 shows the advanced PLL parameter options.

Figure 14. Advanced PLL Parameters

Advanced PLL parameters

Using these parameters is recommended for advanced users only

- Create output file(s) using the 'Advanced' PLL parameters.

- Configurations with output clock(s) that use cascade counters are not supported

- Note: PLL type setting must be explicitly set to 'Enhanced' or 'Fast' PLL

Turn on **Create output file(s) using the 'Advanced' PLL parameters** to enable the feature. You must explicitly select enhanced or fast PLL to use this option.

When this option is turned on, the generated output files contain all of the initial counter values used in the PLL. You can use these values for functional simulation in a third-party simulator.

These parameter settings create no additional top-level ports.

## **PLL Dynamic Reconfiguration**

The PLL Dynamic Reconfiguration feature allows you to reconfigure your PLL on-the-fly. You can control the configuration process using the following ports:

- Input ports: scanclk, scandata, scanclkena, and configupdate

- Output ports: scandataout and scandone

The scandone port is not available for Cyclone, Cyclone II, Stratix, and Stratix GX devices.

The Stratix and Stratix GX enhanced PLLs can be dynamically reconfigured using scan chains. Depending on the PLL type, two options are available for the scan chain – long or short. The long scan chain allows the configuration of those PLLs with six core and four external clocks, while the short scan chain limits the configuration to those PLLs with the six core clocks with no external clocks.

The scan chain method for dynamic reconfiguration is not available for all supported device families. The devices that support the normal dynamic reconfiguration scheme uses configuration files, such as the Hexadecimal-format file, .hex, or the Memory Initialization file, .mif. These files are used together with the ALTPLL\_RECONFIG megafunction to perform the dynamic configuration.

For information about the ALTPLL\_RECONFIG megafunction, refer to the *Phased-Locked Loops Reconfiguration (ALTPLL\_RECONFIG) Megafunction User Guide.*

#### **Parameter Settings**

To enable the dynamic reconfiguration feature for Stratix and Stratix GX devices, use the parameter settings located on the **Scan/Input/Lock** page of the ALTPLL MegaWizard interface.

Figure 15 shows the dynamic reconfiguration options using scan chains.

Figure 15. Dynamic Reconfiguration Options for Stratix and Stratix GX Devices

☐ Dynamic configuration

☐ Create optional inputs for dynamic reconfiguration

Some PLLs have fewer independent outputs and require less data to reconfigure. These PLLs have a shorter scan chain.

Which scan chain type will you be using?

☐ Long chain: All 6 core and 4 external clocks are available

☐ Short chain: Limited to 6 core clocks, with optional external clock

Page 28 ALTPLL Megafunction Features

Table 13 describes the dynamic reconfiguration options using scan chains.

Table 13. Dynamic Reconfiguration Options for Stratix and Stratix GX Devices

| Option                                             | Description                                                                                                                                                                                                                                      |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Create optional inputs for dynamic reconfiguration | This option enables all the PLL reconfiguration ports for this instantiation—scanclk, scanaclr, scandata, and scandataout.                                                                                                                       |  |

| Which scan chain type will you be using?           | This option lets you specify the following types of scan chain to be used in the PLL reconfiguration:                                                                                                                                            |  |

|                                                    | ■ Long chain—Specifies that you are using PLLs 5 and 6 with PLL reconfiguration. PLLs 5 and 6 have six logic array outputs and four external clock outputs and therefore, have a longer reconfiguration chain.                                   |  |

|                                                    | ■ Short chain—Specifies that you are using PLLs 11 and 12 with PLL reconfiguration. PLLs 11 and 12 have only six logic array outputs with no dedicated external clock output counters and are considered the shorter reconfiguration chain PLLs. |  |

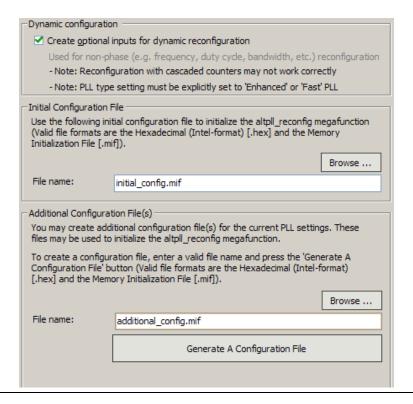

For devices that use the normal dynamic reconfiguration scheme, the parameter settings are located on the **PLL Reconfiguration** page of the ALTPLL MegaWizard interface. Figure 16 shows the normal dynamic configuration scheme options that uses configuration files.

Figure 16. Dynamic Reconfiguration Options Using Configuration Files

Table 14 describes the normal dynamic reconfiguration scheme options.

Table 14. Normal Dynamic Reconfiguration Options and Descriptions

| Option                                             | Description                                                                                                                                                      |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Create optional inputs for dynamic reconfiguration | This option enables all the PLL reconfiguration ports for this instantiation—scanclk, scanaclr, scandata, scandone, and scandataout.                             |  |  |

| Initial Configuration File                         | Specify the location of the configuration file that is used to initialize the ALTPLL_RECONFIG megafunction.                                                      |  |  |

| Additional Configuration File(s)                   | Specify additional configuration file. This file might contain additional settings for the PLL, or might be used to initialize the ALTPLL_RECONFIG megafunction. |  |  |

#### Summary of Supported Device Families for PLL Dynamic Reconfiguration Feature

Table 15 summarizes PLL dynamic reconfiguration support in the different device families and PLL types.

**Table 15.** PLL Dynamic Reconfiguration Feature Support

| Device Family | Top_Bottom | Left_Right | Enhanced PLL | Fast PLL | Cyclone Series PLL |

|---------------|------------|------------|--------------|----------|--------------------|

| Arria GX      | _          | _          | Yes          | Yes      | _                  |

| Arria II GX   | _          | Yes        | _            | _        | _                  |

| Stratix IV    | Yes        | Yes        | _            | _        | _                  |

| Stratix III   | Yes        | Yes        | _            | _        | _                  |

| Stratix II    | _          |            | Yes          | Yes      | _                  |

| Stratix II GX | _          | _          | Yes          | Yes      | _                  |

| Stratix       | _          | _          | Yes (1)      | No       | _                  |

| Stratix GX    | _          | _          | Yes (1)      | No       | _                  |

| Cyclone III   | _          | _          | _            | _        | Yes                |

| Cyclone II    | _          |            | _            | _        | No                 |

| Cyclone       | _          | _          | _            | _        | No                 |

#### Note to Table 15:

# **Dynamic Phase Configuration**

The dynamic phase configuration feature allows the output phases of individual PLL outputs to dynamically adjust relative to each other and the reference clock, without sending serial data through the scan chain of the corresponding PLL. This feature is also known as the dynamic phase stepping feature.

You can use this feature to quickly adjust the output clock phase shift in real time. This adjustment is achieved by incrementing or decrementing the VCO phase-tap selection to a C counter or to the M counter. By default, the phase is shifted by 1/8th of the VCO frequency at each step. However, you can easily modify the phase shift step resolution of the individual PLL output clock using the ALTPLL MegaWizard interface.

<sup>(1)</sup> This device family supports dynamic reconfiguration using scan chains only.

Page 30 ALTPLL Megafunction Features

For dynamic phase shifting to work correctly, the PLL must have the following ports:

- Input ports: phasecounterselect[3..0], phaseupdown, phasestep, and scanclk

- Output port: phasedone

For port descriptions, refer to "Ports and Parameters" on page 40.

## **Supported Devices**

The dynamic phase configuration feature is available only for Cyclone IV, Cyclone III, Arria II GX, Stratix III, and Stratix IV device families.

For information about how to use the ports to perform a dynamic phase shift in a specific device, refer to the PLL chapter of the relevant device handbook.

#### **Parameter Settings**

The parameter settings to enable the dynamic phase configuration feature are located on the **PLL Reconfiguration** page of the ALTPLL MegaWizard interface.

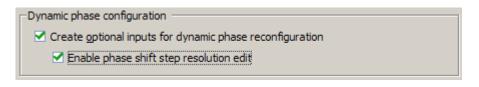

Figure 17 shows the dynamic phase configuration options.

Figure 17. Dynamic Phase Configuration

Turning on Create optional inputs for dynamic phase reconfiguration enables the feature, and create these ports - phasecounterselect[3..0], phaseupdown, phasestep, scanclk, and phasedone.

Turning on **Enable phase shift step resolution edit** allows you to modify the phase shift step resolution value for each individual PLL output clock on its **Output Clocks** page. Figure 18 shows the new option that appears on each output clock settings page. By default, the finest phase shift resolution value is 1/8th of the VCO period. If the VCO frequency is at the lower end of the supported VCO range, the phase shift resolution might be larger than you would prefer for your design. Use this option to fine tune the phase shift step resolution.

Figure 18. Phase Shift Step Configuration

## Modifying the PLL Phase Shift Step Resolution Using Advanced Parameters

The finest phase shift step resolution you can get in the ALTPLL megafunction is 1/8th of the VCO period. If the VCO frequency is at the lower end of the supported VCO range, the phase shift step resolution may be larger than you would prefer for your design.

You can modify your phase shift resolution using the dynamic phase reconfiguration feature of the PLL. If you want to modify the phase shift resolution without the dynamic phase reconfiguration feature enabled, perform the following steps:

- 1. Create an ALTPLL instance. Make sure you specify the speed grade of your target device and the PLL type.

- 2. On the PLL Reconfiguration page, turn on Create Optional Inputs for Dynamic Phase Reconfiguration and Enable Phase Shift Step Resolution Edit.

- On the Output Clocks page, set your desired phase shift for each required output clock. Click More Details to see the internal PLL settings. Note all of the settings shown.

- 4. On the **Bandwidth/SS** page, click **More Details** to see the internal PLL settings. Note all of the settings shown.

- On the Inputs/Lock page, turn on Create output file(s) using the 'Advanced' PLL Parameters.

- 6. Return to the **PLL Reconfiguration** page and turn off **Create Optional Inputs for Dynamic Phase Reconfiguration**.

- 7. Click **Finish** to generate the PLL instantiation file(s).

When using Advanced Parameters, the PLL wrapper file (*ALTPLL\_instantiation\_name*>.v|.vhd) is written in a format that allows you to identify the PLL parameters. The parameters are listed in the Generic Map section of the VHDL file, or in the defparam section of the Verilog file.

- 8. Open your PLL instantiation wrapper file and locate either the **Generic Map** or the **defparam** section.

- 9. Modify the settings to match the settings that you noted in steps 3 and 4.

- 10. Save the PLL instantiation wrapper file and compile your design.

- 11. Verify that the output clock frequencies and phases are correct in the PLL Usage report located under Resource Section of the Fitter folder in the Compilation Report.

By using this technique, you can apply valid PLL parameters as provided by the ALTPLL MegaWizard interface to optimize the settings for your design.

Alternatively, you can leave the dynamic phase reconfiguration option enabled and tie the relevant input ports—phasecounterselect[3..0], phaseupdown, phasestep, and scanclk—to constants, if you prefer not to manually edit the PLL wrapper file using Advanced PLL Parameters option.

Page 32 Design Examples

# **Design Examples**

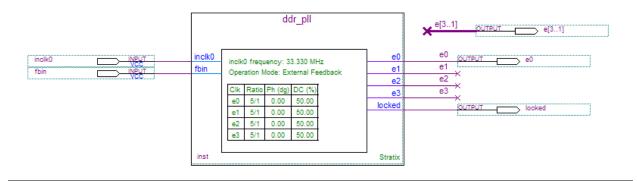

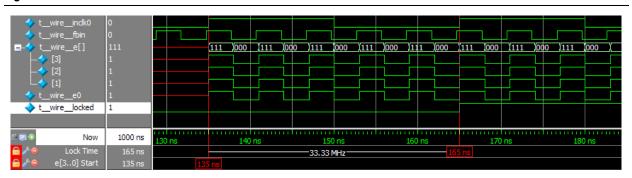

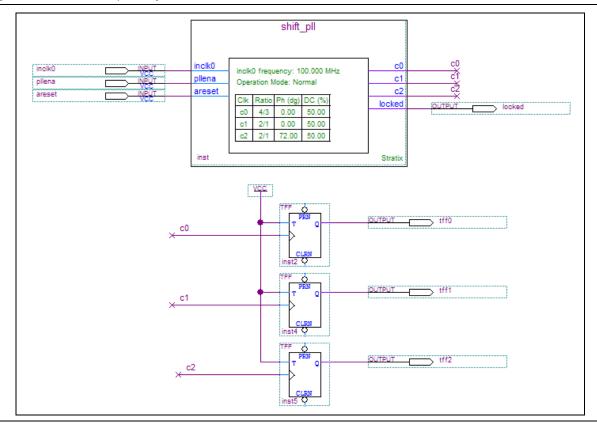

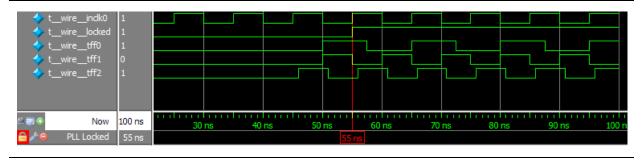

This section presents two design examples that use the ALTPLL megafunction to generate an external differential clock from an enhanced PLL (as shown in Figure 19 on page 34) and generate and modify internal clock signals (as shown in Figure 21 on page 38).

These examples use the MegaWizard Plug-In Manager in the Quartus II software. Each page of the MegaWizard is described in detail. When you are finished with the examples, you can incorporate them into your overall projects.

# **Design Files**

The design files are available on the Literature and Technical Documentation page of the Altera website. The files are located under the following sections:

- On the Quartus II Development Software Literature page, expand the Using Megafunctions section and then expand the I/O section

- Literature: User Guides section

# **Example 1: Differential Clock**

This section presents a design example that uses the ALTPLL megafunction to generate an external differential clock from an enhanced PLL. It is often necessary to generate or modify clock signals to meet design specifications. When you interface to double data rate (DDR) memory, you must generate a differential SSTL clock signal for the external device. A DDR DIMM requires three pairs of differential SSTL clocks. You can use enhanced PLLs in Stratix devices to generate these clock signals.

In this example, perform the following activities:

- Generate a 166-MHz differential SSTL external clock (ddr\_clk) output from a 33.33-MHz input clock using the ALTPLL megafunction and the MegaWizard Plug-In Manager.

- Implement the DDR\_CLK design by assigning the EP1S10F780 device to the project and compiling the project.

- Simulate the DDR\_CLK design.

#### **Generate a 166-MHz Differential SSTL External Clock**

- 1. In the Quartus II software, open the project file \ddr\_clk\ddr\_clk.qpf.

- 2. Open the top-level \ddr\_clk\ddr\_clk.bdf file. You will complete this project in this example.

- Double-click on a blank area in the block design (.bdf) file, and click MegaWizard Plug-In Manager in the Symbol window, or, on the Tools menu, click MegaWizard Plug-In Manager.

- 4. Under What action do you want to perform?, click Create a new custom megafunction. Click Next. Page 2a appears.

- 5. On Page 2a of the MegaWizard Plug-In Manager, expand the **I/O** folder and select **ALTPLL**.

- 6. For Which device family will you be using?, select Stratix.

Design Examples Page 33

- 7. In Which type of output file do you want to create?, select AHDL.

- 8. For What name do you want for the output file?, name the output file ddr\_pll.

- 9. Click **Next**. Page 3 appears.

- 10. On Page 3, in the **General** section, for **What is the frequency of the inclock0** input?, type 33.33, and select MHz.

- 11. Under PLL type, click Select the PLL type automatically.

- 12. Under Operation mode, select Create an 'fbin' input for an external feedback (External Feedback Mode).

- 13. Under Operation mode, for Which output clock will have a board-level connection?, select e0 from the drop-down menu.