# Configuration via Protocol (CvP) Implementation in Altera FPGAs

**User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-01101-1.1

Document last updated for Altera Complete Design Suite version: Document publication date: 11.1 January 2012

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

### **Chapter 1. Overview**

| Getting Started                              |  |

|----------------------------------------------|--|

| Embedded PCIe Hard IP Blocks in Altera FPGAs |  |

| Autonomous PCIe Hard IP Block                |  |

| CvP Scheme                                   |  |

| Chapter 2. FPGA Configuration in CvP         |  |

| CvP Setup Interfaces                         |  |

| Conventional Configuration Scheme            |  |

| PCIe Link                                    |  |

| CvP Configuration Image                      |  |

| CvP Modes                                    |  |

| CvP Initialization and Update mode           |  |

| CvP Update mode                              |  |

| Chapter 3. FPGA Fabric Image Update in CvP   |  |

| Fabric Image Update                          |  |

### Chapter 4. CvP Topologies

| Single End Point    |       |

|---------------------|-------|

| Multiple End Points | . 4–2 |

| Mixed Chain         | . 4–4 |

| Daisy Chain         | . 4–7 |

### **Chapter 5. Design Considerations**

| Pin Descriptions                                | 5–1 |

|-------------------------------------------------|-----|

| CvP Configuration Features                      | 5–3 |

| Data Compression                                | 5–3 |

| Data Encryption                                 | 5–3 |

| FPGA Image Update                               | 5–3 |

| Designing CvP for an Open System                | 5–4 |

| FPGA Power Supplies Ramp Time Requirement       | 5–4 |

| PCIe Wake-Up Time Requirement in an Open System | 5–5 |

| Supported Configuration Schemes for CvP Modes   | 5–8 |

|                                                 |     |

#### **Chapter 6. Software Support**

| Device and Pin Options Setting               | 6–1 |

|----------------------------------------------|-----|

| Hard IP for PCIe version 11.1                |     |

| Generating Periphery Image and Fabric Image  | 6–2 |

| VSEC                                         | 6–3 |

| Altera Defined VSEC Header                   | 6–3 |

| Altera Defined Vendor-Specific Header        | 6–4 |

| Altera Marker                                | 6–4 |

| CvP Status                                   | 6–5 |

| CvP Mode Control                             | 6–6 |

| CvP Data Register                            | 6–7 |

| CvP Programming Control Register             | 6–7 |

| Uncorrectable Internal Error Status Register | 6–8 |

| Uncorrectable Internal Error Mask Register         | 6–9  |

|----------------------------------------------------|------|

| Correctable Internal Error Status Register         | 6–10 |

| Correctable Internal Error Mask Register           | 6–10 |

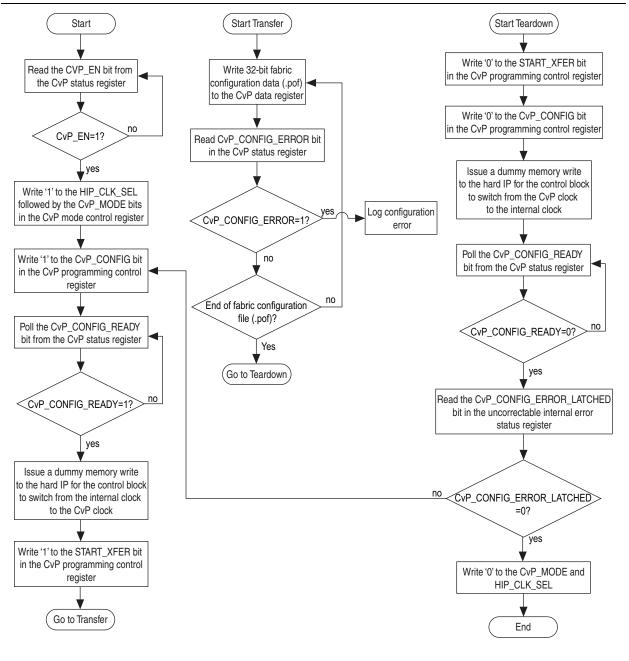

| Procedure for Configuring Stratix V FPGAs via PCIe |      |

### **Additional Information**

| Document Revision History | Info-1 |

|---------------------------|--------|

| How to Contact Altera     | Info-1 |

| Typographic Conventions   | Info-1 |

# 1. Overview

This user guide describes the features and implementations of the Configuration via Protocol (CvP) scheme in supported Altera<sup>®</sup> FPGA families. This user guide only shows you how to use the CvP scheme in the supported FPGA, and does not explain the PCI Express<sup>®</sup> (PCIe<sup>®</sup>) protocol.

This user guide uses the Stratix<sup>®</sup> V device in the illustrations, guidelines, and examples. Information specific to other device families will be stated accordingly.

## **Getting Started**

Use this user guide in conjunction with an understanding of the following PCIe specifications:

- PCI Express Base 1.1 Specification

- PCI Express Base 2.1 Specification

- PCI Express Base 3.0 Specification

- PCI Express CEM 2.0 Specification

## **Embedded PCIe Hard IP Blocks in Altera FPGAs**

Altera FPGAs contain embedded PCIe hard IP blocks that you can configure as end points or a root complex for PCIe applications. However, you cannot use the embedded PCIe hard IP block as a root complex when it is configured for CvP.

To establish the PCIe link between a root complex and an end point successfully, the end point must be functional within the time period set by the PCIe power-up and wake-up timing specification.

### **Autonomous PCIe Hard IP Block**

After the PCIe hard IP block is configured, it is in autonomous mode. The autonomous PCIe feature allows the hard IP block in the FPGA to start link training before the fabric is configured. This feature helps the FPGA to accommodate the PCIe timing requirement in open and closed systems.

In an open system, all the electronic systems attached to the open system must obey the PCIe wake-up time requirement as defined in the PCIe specifications. In a closed system, the electronic systems attached to the closed system do not need to obey the PCIe wake-up time requirement as defined in the PCIe specifications. If the FPGA fabric is not fully functional when the PCIe host starts accessing the PCIe hard IP block, the autonomous PCIe hard IP block responds to the PCIe host with a configuration retry status (CRS) transaction for configuration read and configuration write requests, or an unsupported request (UR) transaction for memory and I/O requests. The PCIe host will attempt to access the FPGA end point for one second after receiving the initial CRS or UR transaction before it recognizes that the FPGA is faulty. This delay allows the FPGA fabric to finish configuration. All PCIe hard IP blocks are part of the periphery image. Regardless of the CvP mode, the periphery image is always configured before the fabric configuration.

## **CvP Scheme**

The CvP is a new FPGA configuration scheme supported in Arria<sup>®</sup> V, Cyclone<sup>®</sup> V, and Stratix V devices. It uses the autonomous PCIe hard IP block feature of the embedded PCIe hard IP block to allow the FPGA to meet the PCIe power-up timing specification. The benefit of the autonomous PCIe hard IP block is that the embedded PCIe core is operational before the FPGA fabric is configured. Conventionally, the embedded PCIe hard IP block can only be operational after the full FPGA image is fully configured.

The CvP scheme offers a solution for configuring the FPGA fabric through the PCIe link. The following are the benefits of using the CvP scheme:

- Reduced cost—the FPGA fabric configuration data is stored in the memory of the PCIe host and the external flash is used only to store the periphery configuration data. This can reduce the flash memory size required because the periphery configuration data file size is smaller when compared with the full FPGA image configuration data, which saves system cost.

- Design protection—CvP ensures the PCIe host can exclusively access the FPGA fabric image (the most important portion of the FPGA configuration data). This provides better protection for the FPGA against unauthorized design tampering or copying.

- Image update without system down time—CvP allows the FPGA fabric to be updated through the PCIe link without a host reboot or FPGA full chip reinitialization.

# 2. FPGA Configuration in CvP

This chapter describes the interfaces involved in the CvP setup, CvP configuration image, and types of CvP modes.

### **CvP Setup Interfaces**

CvP setup involves two interfaces: the conventional configuration interface and the PCIe link.

### **Conventional Configuration Scheme**

The conventional configuration interface is to connect the FPGA to a JTAG configuration interface, the configuration device for the Active Serial (AS) configuration scheme, or the configuration host for both the Fast Passive Parallel (FPP) and Passive Serial (PS) configuration schemes. This interface is used to configure the periphery image or the full image to the FPGA.

For more information about the conventional configuration scheme in Altera FPGAs, refer to the *Configuration*, *Design Security*, *and Remote System Upgrades* chapters of the respective Altera FPGA handbooks.

#### **PCIe Link**

The PCIe link connects the PCIe hard IP block of the FPGA to the PCIe host. This interface is used to configure the FPGA with the fabric image. Only one designated PCIe hard IP block has the interface to the internal configuration control block, which you can use for CvP. You can also use this designated PCIe hard IP block to perform other PCIe applications after the FPGA enters user mode. The other PCIe hard IP blocks do not have the dedicated interface to the internal configuration control block; therefore you can use these other PCIe hard IP blocks for PCIe applications only and not to perform CvP.

For Arria V, Cyclone V, and Stratix V devices, the PCIe hard IP block located at the bottom left from the top view (which is GXB\_L0 bank) of the FPGA has the connection to the internal configuration control block, which you can use for CvP.

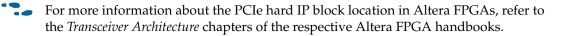

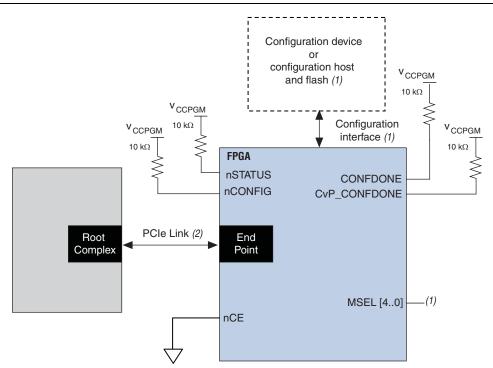

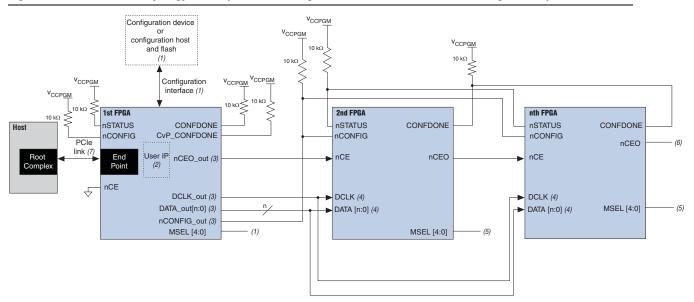

Figure 2–1 shows the high-level hardware setup for FPGA configuration in the CvP scheme.

#### Figure 2–1. CvP Hardware Setup

#### Notes to Figure 2-1:

- (1) The configuration interface can be any of the supported configuration schemes such as JTAG, FPP, PS, or AS. The choice of configuration device depends on the chosen configuration scheme.

- (2) This PCIe hard IP block is for CvP and other PCIe applications.

- (3) This PCIe hard IP blocks only support PCIe applications. You cannot use it for CvP.

## **CvP Configuration Image**

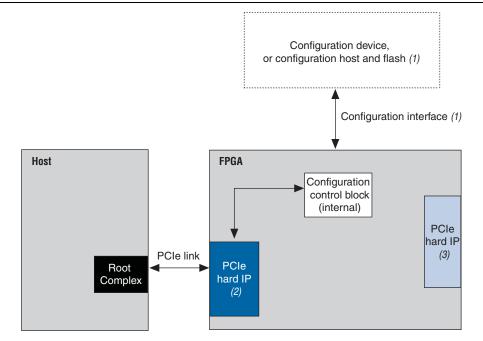

A full FPGA configuration image has two portions: the periphery image and the fabric image. The periphery image contains the configuration data for PCIe hard IP block and I/O buffer settings, which includes all user I/Os and dedicated transceiver channels. Fabric image contains the configuration data of the logic elements (LEs), digital signal processing (DSP) blocks, and embedded memory of the design.

In the conventional configuration scheme supported in previous FPGA families, the periphery image and fabric image are combined in a single configuration file.

You can generate the periphery image and fabric image in two separate configuration files for CvP scheme in a future version of the Quartus II software.

Figure 2–2 shows the periphery and fabric location of the FPGA and does not represent the transceiver and I/O bank location of the FPGA.

Figure 2–2. FPGA Periphery and Fabric

For more information about the location of the transceiver banks and I/O banks in the FPGA, refer to the *High-Speed Differential I/O Interfaces and DPA* chapters of the respective Altera FPGA handbooks.

## **CvP Modes**

FPGA configuration in the CvP scheme supports three different modes. Depending on the CvP mode, the conventional configuration interface and the PCIe link are used to transfer different FPGA configuration data. The CvP modes are described in the following sections.

Table 2–1 lists the features of each CvP mode.

Table 2–1. CvP Mode

| Feature                                        | CvP Initialization and Update Mode (1)                                                                                         | CvP Update Mode <sup>(1)</sup>                                                              |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| PCIe Link Data Rate                            | Gen1, Gen2 <sup>(4)</sup>                                                                                                      | Gen1, Gen2, Gen3                                                                            |

| PCIe Link Usage                                | Initial FPGA fabric configuration, FPGA fabric image update, and PCIe application in user mode                                 | FPGA fabric image update and PCIe application in user mode                                  |

| FPGA Configuration<br>Method                   | Periphery configuration through conventional schemes<br>(AS, PS, FPP, and JTAG). Fabric configuration through<br>the PCIe link | Full configuration through<br>conventional configuration<br>schemes (AS, PS, FPP, and JTAG) |

| FPGA Fabric Image Update through the PCIe Link | Supported                                                                                                                      | Supported                                                                                   |

#### Notes to Table 2-1:

(1) The CvP mode is set in the Quartus II software. For more information, refer to "CvP Setting in Device and Pin Options" on page 7–1.

(2) The FPGA CvP and the PCIe application in a user design must use the same PCIe configuration settings.

(3) PCIe Gen1 and Gen2 support x1, x4, and x8 modes.

(4) PCIe Gen3 requires physical medium attachment (PMA) calibration for the PCIe link training before the link transitions to active (L0) state. The PMA calibration block is part of the fabric image, hence it is not supported in CvP Initialization and Update mode.

## **CvP** Initialization and Update mode

There are two steps to configure the FPGA using CvP Initialization and Update mode: periphery configuration and fabric configuration. Therefore, the configuration image in CvP Initialization and Update mode is split into two different files. The first configuration file contains the periphery image (stored in the external configuration device) and the second configuration file contains the fabric image (stored in a memory that is accessible by the PCIe host).

During device power up, the periphery image is loaded from the external configuration device to the FPGA through the conventional configuration interface. The configuration bits for the PCIe hard IP blocks are part of the periphery image.

After the periphery configuration is completed, the CONF\_DONE signal goes high and allows the FPGA to start the PCIe link training. When the PCIe link training completes, the PCIe link transitions to L0 state and the PCIe host begins to initiate the fabric configuration through the PCIe link. After the fabric is successfully configured, the CvP\_CONFDONE pin goes high, signifying the completion of the full FPGA configuration. In CvP Initialization and Update mode, you must observe both CONF\_DONE and CvP\_CONFDONE to verify that the FPGA is fully configured. After the FPGA is fully configured, the FPGA enters initialization and user mode. If INIT\_DONE signal is enabled, the INIT\_DONE signal goes high after the initialization completes and FPGA enters user mode.

After the device enters user mode, you can use the PCIe link for normal PCIe transactions. In CvP Initialization and Update mode, you can also use the PCIe link to perform an FPGA fabric image update. To achieve this, generate multiple FPGA fabric images in the Quartus<sup>®</sup> II software that keep the existing same periphery functionality. For more information about fabric image updates in CvP Initialization and Update mode, refer to the "FPGA Fabric Image Update in CvP" on page 3–1.

### **CvP Update mode**

In CvP Update mode, the FPGA is fully configured through a conventional configuration scheme on device power up. A single configuration file that contains the full FPGA configuration image is stored in the external configuration device and is loaded to the FPGA. The CONF\_DONE signal goes high after the completion of the full FPGA configuration. After the FPGA is fully configured, the FPGA enters initialization and user mode. If INIT\_DONE signal is enabled, the INIT\_DONE signal goes high after the initialization completes and FPGA enters user mode. After the device enters user mode, the PCIe links are available for the normal PCIe application.

Besides the normal PCIe applications, you can use the PCIe link for an FPGA fabric image updates. To achieve this, you can generate multiple FPGA fabric images in the Quartus II software that keep the same periphery functionality.

For the image update in CvP Update mode, refer to the "FPGA Fabric Image Update in CvP" on page 3–1.

# 3. FPGA Fabric Image Update in CvP

This chapter describes the process of the FPGA fabric image update through CvP.

## **Fabric Image Update**

After the FPGA enters user mode, the PCIe host triggers an FPGA fabric image update through the PCIe link. FPGA fabric image update is supported in CvP Initialization and Update mode, and CvP Update mode. You cannot update the periphery image through CvP.

Altera recommends that you fix the periphery functionality for each fabric image design in CvP. After each fabric image update, the core fabric designs keep the same functionality to the periphery interface. If the periphery image and the first core image are generated with encryption, compression or both features turned on, you must ensure the encryption, compression or both features are turned on for the other fabric images that you will use for fabric image update via CvP.

• You can update the PLLs and transceivers using dynamic reconfiguration. For more information about dynamic reconfiguration, refer to the *Dynamic Reconfiguration* chapters of the respective Altera FPGA handbooks.

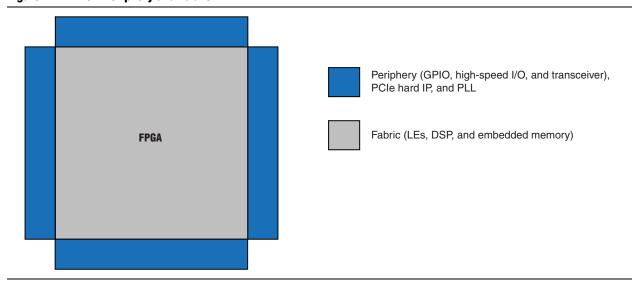

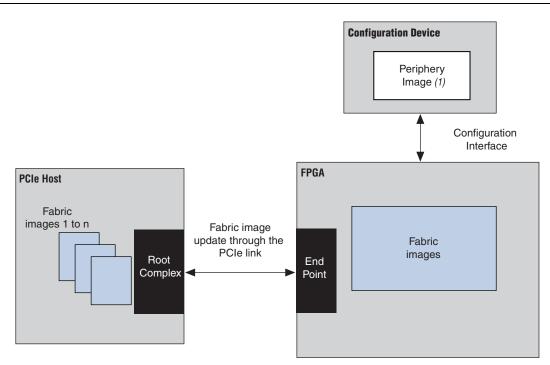

Figure 3–1 shows an example of how you can create multiple FPGA fabric images for use with CvP Update.

#### Figure 3–1. Example of Multiple User Design Planning for CvP Fabric Image Update

In Figure 3–1, the periphery design is fixed from user design revision 1 to revision n. However, the fabric design changes in every user design revision. These fabric designs must have the same functionality to the periphery interface. You must ensure the system keeps the same periphery functionality for each fabric image that is created. In the Quartus II software, you can generate multiple fabric images within a single design project. However, you must generate only one periphery image for that design project because the periphery image must remain the same for all the fabric images to work with CvP Update. The periphery image is stored in the configuration device and you may not modify or update the periphery image during the fabric image update. The multiple fabric images are stored in memory that is accessible by the PCIe host, as shown in Figure 3–2.

If a fabric image update attempt is triggered, the CvP\_CONFDONE pin is pulled low, which indicates that a fabric image update has started. The FPGA fabric is reinitialized and reconfigured with the new fabric image. During the fabric image update through a PCIe link, the nCONFIG and nSTATUS pins of the FPGA are logic high. When the fabric image update completes, the CvP\_CONFDONE pin is released high again and indicates that the FPGA has entered user mode.

Support for multiple fabric images creation will be available in a future version of the Quartus II software.

Figure 3–2 shows the arrangement of the periphery image and multiple fabric images stored for fabric image update.

#### Note to Figure 3-2:

(1) The periphery image remains the same for different fabric image updates. If you change the periphery image, you must reprogram the configuration device with the new periphery image.

# 4. CvP Topologies

This chapter describes some of the topologies that can be used with CvP. The CvP is supported for single FPGA or multiple FPGAs configurations.

### **Single End Point**

Use the single end point topology for a single FPGA configuration. In this topology, the PCIe link involves only one PCIe end point in the FPGA and the PCIe root complex in the host. Depending on the CvP mode you select, the conventional configuration interface is used to configure the periphery image or the full FPGA image after system power up. The PCIe link can be used for fabric image configurations or updates, in addition to the usual PCIe link application.

Figure 4–1 shows the single end point topology.

#### Figure 4–1. Single End Point Topology in CvP

#### Notes to Figure 4-1:

- (1) The configuration interface can be any of the supported configuration schemes such as AS, PS, FPP, or JTAG. The MSEL [4..0] are used to indicate the chosen configuration scheme.

- (2) The PCIe link includes the PERST# signal and other PCIe signals as defined in the PCIe base specification.

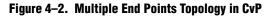

## **Multiple End Points**

Use the multiple end points topology to configure multiple FPGAs. In this topology, one root complex connects to multiple FPGA end points through a PCIe switch. The PCIe switch controls the fabric image configuration through the PCIe link to the targeted FPGA end point. This topology provides flexibility for you to select the FPGA that you must configure or update through the PCIe link. There is no limitation on the number of FPGAs that can be configured using this topology. The root complex must have the ability to respond to the PCIe switch and direct the configuration data transaction to the designated end point based on the end point media access control (MAC) address reported by the PCIe switch.

Figure 4–2 shows the multiple end points topology.

#### Notes to Figure 4-2:

- (1) The configuration interface can be any of the supported configuration schemes such as AS, PS, FPP, and JTAG. The MSEL [4..0] signals are used to indicate the configuration scheme.

- (2) The PCIe link includes the PERST# signal and other PCIe signals as defined in the PCIe base specification.

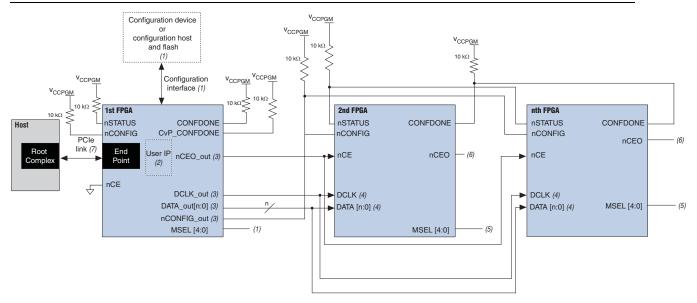

## **Mixed Chain**

Use mixed chain topology to support multiple FPGA configurations. In this topology, the root complex of the host only responds to the end point in the master FPGA (the first FPGA in the chain) through the PCIe link. You can configure the slave FPGAs in the chain through a PS or FPP configuration scheme. Only the master FPGA is configured in CvP mode.

You must design user IP in the master FPGA to fetch the data from the root complex to the slave devices in the chain. The data is latched out from the master FPGA through GPIOs and latched into the slave FPGAs through the PS or FPP configuration pins such as DCLK, DATA line, or DATA bus.

The DCLK, DATA bus, nCONFIG, nSTATUS, and CONF\_DONE pins of the slave devices are tied together, allowing the slave devices to enter user mode at the same time. If there is a configuration error during the slave device configuration, the slave device chain reinitializes and reconfigures by having the nSTATUS line pulled low and released by the FPGAs again. You must ensure there is a suitable line buffering on the DCLK and DATA bus if there are more than four slave devices in the chain.

You can cascade the slave devices in two ways:

- If the slave devices are configured with different configuration files, the nCEO pin of one slave device is connected to the nCE pin of the next slave device in the chain. If the first slave device completes the configuration, the device pulls the nCEO pin that enables the next slave device. The next slave device starts its configuration and pulls the nCEO pin low to enable the subsequent device. This process continues until the last slave device in the chain is configured. You can leave the nCEO pin of the last device unconnected or use as a user I/O, as shown in Figure 4–3 with the slave devices configured in FPP mode.

- If the slave devices are configured with the same configuration file for identical user applications, the nCE pins of the slave devices are connected to the nCEO pins of the master device. The nCEO pins of the slave devices are left unconnected or used as user I/Os. In this topology, all the slave devices are configured at the same time, as shown in Figure 4–4 with the slave devices configured in FPP mode.

#### Figure 4–3 shows the mixed chain topology.

#### Notes to Figure 4-3:

- (1) The configuration interface can be any of the supported configuration schemes such as AS, PS, FPP, or JTAG. The MSEL[4..0] signals are used to indicate the configuration scheme.

- (2) User IP is a user-designed IP programmed in the first FPGA to fetch data from the root complex through the PCIe link, which is sent to the slave FPGAs in the chain through a PS or FPP configuration interface.

- (3) DCLK\_out and DATA\_out are the GPIO pins used to fetch the PS or FPP configuration data. The nCONFIG\_out and nCEO\_out are the GPIO pins used to connect to the nCONFIG and nCE pins of the slave device.

- (4) Configuration data input to the slave FPGAs through PS or FPP configuration pins.

- (5) Connect the MSEL pins to the PS or FPP scheme.

- (6) You can leave the nCEO pin of the last FPGA in the chain unconnected or use it as a GPIO.

- (7) The PCIe link includes the PERST# signal and other PCIe signals as defined in the PCIe base specification.

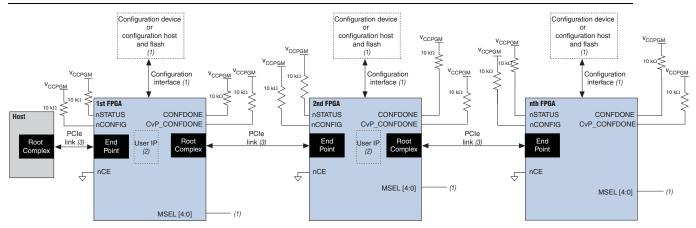

Figure 4–4 shows the mixed-chain topology in CvP with all the slave devices configured at the same time.

#### Notes to Figure 4-4:

- (1) The configuration interface can be any of the supported configuration schemes such as AS, PS, FPP, or JTAG. The MSEL [4..0] signal and choice of configuration device depend on the chosen configuration scheme.

- (2) User IP is a user-designed IP programmed in the first FPGA to fetch data from the root complex through the PCIe link, which is sent to the slave FPGAs in the chain through a PS or FPP configuration interface.

- (3) DCLK\_out and DATA\_out are the GPIO pins used to fetch the PS or FPP configuration data. The nCONFIG\_out and nCEO\_out are the GPIO pins used to connect to the nCONFIG and nCE pins of the slave device.

- (4) Configuration data input to the slave FPGAs through PS or FPP configuration pins.

- (5) Connect the MSEL pins to the PS or FPP scheme.

- (6) You can leave the nCEO pin of the last FPGA in the chain or use it as a GPIO.

- (7) The PCIe link includes the PERST# signal and other PCIe signals as defined in the PCIe base specification.

## **Daisy Chain**

A daisy chain is a CvP topology for configuring multiple FPGAs. Configuration devices are attached to each FPGA for periphery configuration (CvP Initialization and Update mode) or full FPGA configuration (CvP Update mode) after the system powers up. The nCE, nSTATUS, nCONFIG, CONFDONE, and CvP\_CONFDONE pins of the FPGAs are not tied together, allowing the FPGAs to receive the configuration data individually from their respective configuration device.

Each FPGA in the daisy chain has two PCIe IP cores configured as an end point and a root complex, respectively. In this topology, the root complex in the host responds to the end point of the first FPGA in the chain. The fabric image of the first FPGA is configured through the PCIe link between the host and its end point. After the configuration is completed, the first FPGA enters user mode and the user IP in the first FPGA initiates the fabric configuration of the subsequent device. The process continues until the last device in the chain is configured. You must design a user IP as part of the FPGA fabric image. The user IP routes data from the host to the FPGA root complexes. The root complex of the first FPGA is connected to the end point of the subsequent FPGA through the PCIe link. The fabric image of the second FPGA is fetched from the host and is routed through the first FPGA before it is loaded into the second FPGA through the PCIe link. This process continues until the last FPGA in the chain is configured.

Figure 4–5 shows the daisy chain topology.

#### Figure 4–5. Daisy Chain Topology in CvP

#### Notes to Figure 4–5:

(1) The configuration interface can be any of the supported configuration schemes such as AS, PS, FPP, or JTAG. The MSEL[4..0] signal is used to indicate the chosen configuration scheme.

(2) User IP is a user-design IP programmed in the first FPGA to data from the root complex through the PCIe link and send to the slave FPGAs in the chain through FPP configuration interface.

(3) The PCIe link includes the PERST# signal and other PCIe signals as defined in the PCIe base specification.

# 5. Design Considerations

This section discusses the hardware design considerations if your FPGA design is configured in CvP mode.

## **Pin Descriptions**

Depending on the CvP mode chosen, configuration involves the conventional configuration interface and the PCIe link. This section covers only the CvP pins that are not included in the conventional configuration interface and the typical PCIe link.

For more information about the configuration pins involved in the conventional configuration interface, refer to the *Configuration, Design Security, and Remote System Upgrades* chapters of the respective Altera FPGA handbooks.

Table 5–1 lists the additional CvP pin descriptions and connections that are not listed in the *Configuration, Design Security, and Remote System Upgrades* chapters of the respective Altera FPGA handbooks and the PCI Express Base Specification.

Table 5–1.

CvP Pin Descriptions and Connections

| Pin Name     | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CvP_CONFDONE | Output   | Driven low during fabric configuration and<br>released or driven high after the completion<br>of the fabric configuration.<br>During FPGA configuration in CvP<br>Initialization and Update mode, you must<br>observe this pin after the CONF_DONE pin<br>goes high to determine if the FPGA is fully<br>configured. During FPGA fabric image<br>update, you must observe this pin to<br>determine if the fabric image update is<br>completed.<br>If CvP mode is turned off, you can use this<br>pin as a user I/O pin. | If this pin is set as dedicated output, the $V_{CCPGM}$ power supply must meet the input voltage specification of the receiving side.<br>If this pin is set as an open drain output, the pin must be connected to an external 10 k $\Omega$ -pull-up resistor to the $V_{CCPGM}$ power supply or a different pull-up voltage that meets the input voltage specification of the receiving side. This gives an advantage on the voltage leveling.                                                                                                                                                                                                                                                                               |

| nPERSTL0     | Input    | This pin is connected to the PCIe hard IP<br>block as a dedicated fundamental reset pin<br>for PCIe usage. If the signal is low, the<br>transceivers and dedicated PCIe (CvP) hard<br>IP block are in reset mode. If this signal is<br>high, the transceivers and dedicated PCIe<br>(CvP) hard IP block are released from the<br>reset mode.<br>If the PCIe hard IP block is not in use, you<br>can use this pin as a user I/O pin.                                                                                     | <ul> <li>Connect the nPERSTL0 to the PERST# pin of the PCle slot.</li> <li>During CvP, this pin is powered by the V<sub>CCPGM</sub> power supply. In the case that the V<sub>CCPGM</sub> power supply is not at 3.3 V, you can still drive an input signal to this pin at 3.3-V volts without requiring a voltage level shifter with the following requirements to conform to the PCle electrical standards:</li> <li>The input signal must meet the V<sub>IH</sub>/V<sub>IL</sub> specification of 3.3-V LVTTL I/O standard.</li> <li>The input signal must not exceed the overshoot specification for 100% operation as stated in the <i>Device Data Sheet</i> chapters of the respective Altera FPGA handbooks.</li> </ul> |

## **CvP Configuration Features**

CvP supports configuration features such as data decompression, decryption, and partial reconfiguration.

Table 5–2 lists the configuration features supported in each CvP mode.

Table 5–2. CvP with Configuration Features

| CvP Mode                      | Decompression <sup>(1)</sup> | Decryption <sup>(1)</sup> | Remote System<br>Upgrade     | Partial Reconfiguration <sup>(1)</sup> |

|-------------------------------|------------------------------|---------------------------|------------------------------|----------------------------------------|

| CvP Initialization and Update | Supported                    | Supported                 | Not supported <sup>(2)</sup> | Supported                              |

| CvP Update Mode               | Supported                    | Supported                 | Not supported <sup>(2)</sup> | Supported                              |

Notes to Table 5-2:

(1) Feature support is not available in the Quartus II software version 11.1. This feature will be available in a future release of the Quartus II software.

(2) The system upgrade feature is supported through fabric image update through the PCIe link.

### **Data Compression**

The data compression reduces the size of the fabric image. The periphery image is not compressed. Enabling data compression in CvP Update mode can help reduce both the external configuration memory required for full FPGA image storage and the configuration time of the full FPGA configuration.

If the data compression is enabled in CvP Initialization and Update mode, the external configuration memory required for periphery image storage remains the same but the memory size required for the fabric image in the PCIe host is reduced.

### **Data Encryption**

Use the data encryption feature to encrypt the fabric image with the Advanced Encryption Standard (AES) algorithm to protect the data against unauthorized access. The periphery image is not encrypted by this feature. To configure the FPGA with encrypted data, a security key is pre-programmed to the FPGA and is used to decrypt the incoming bitstream.

### **FPGA Image Update**

You can achieve the FPGA image update if you are not using any CvP modes with the normal remote system upgrade feature. FPGA fabric image update in CvP Initialization and Update mode, and CvP Update mode is performed through the PCIe link. Partial reconfiguration is supported in all the CvP modes. However, software support for this feature will only be available in a future release of the Quartus II software.

## **Designing CvP for an Open System**

In an open system, all the electronic systems attached to the open system must obey the PCIe wake-up time requirement as defined in the PCIe specifications. This section describes the requirements for FPGA power supply ramp time, PCIe wake-up time requirement in an open system, and configuration scheme selection for CvP modes.

### **FPGA Power Supplies Ramp Time Requirement**

This section describes the FPGA power supplies ramp-up time requirement to accommodate a CvP in an open system.

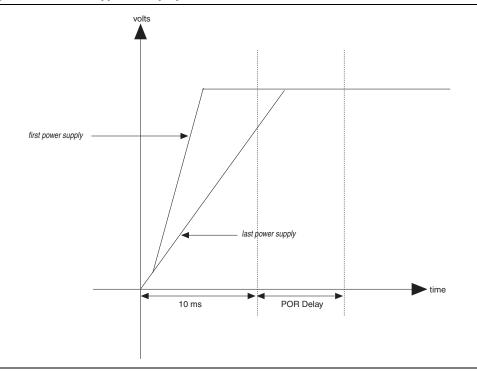

The POR circuit generates a POR signal that keeps the device in a reset state until the power supply outputs are within the operating range. If power is supplied, a POR event occurs if the POR monitored power supplies reach the recommended operating range within the maximum power supply ramp time ( $t_{RAMP}$ ).

To use CvP, the total time must be within 10 ms, from the first power supply ramp-up to the last power supply ramp-up (refer to Figure 5–1). You must set the PORSEL pin high for fast POR, in which the POR delay time is in the range of 4–12 ms, leaving enough time after the POR trip for the PCIe to start initialization and configuration.

Figure 5–1 shows the power supplies ramp-up time and POR.

Figure 5–1. Power Supplies Ramp-Up Time and POR

For more information about POR, refer to the Hot Socketing and Power-On Reset chapters of the respective Altera FPGA handbooks.

### PCIe Wake-Up Time Requirement in an Open System

To accommodate the open system of PCIe applications, the PCIe link connected to the FPGA must meet the PCIe wake-up timing specification that must transition from power-on to the link active (L0) state within 200 ms. The overall timing from FPGA power up to the PCIe hard IP block in the FPGA is ready for link training must be within 120 ms.

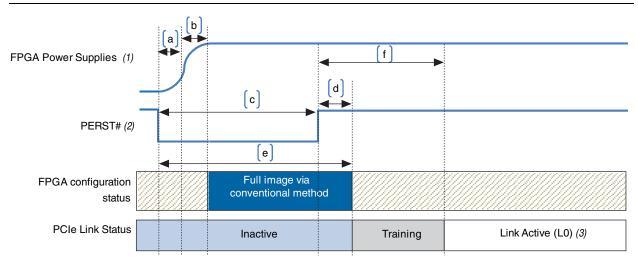

For CvP Update mode, the full FPGA image is configured through the conventional configuration schemes after device power-up. To accommodate your system into an open system, the first full FPGA configuration must be within 120 ms. Therefore, you must choose the right conventional configuration scheme for your device to ensure the configuration time is able to meet the 120-ms requirement. For more information about the supported configuration scheme that you can choose to design an open system with the CvP Update mode, refer to Table 5–3.

Figure 5–2 shows the PCIe power-up sequence and the FPGA configuration timing in CvP Update mode.

#### Notes to Figure 5-2:

- (1) To ensure successful configuration, all the POR-monitored power supplies to the FPGA must ramp up monotonically to operating range within the 10 ms ramp-up time.

- (2) One of the auxiliary signals specified in the PCIe electromechanical specification. The PERST# signal is sent from host to the FPGA and it is used to indicate if the power supplies of the FPGA are within their specified voltage tolerance and are stable. It also initializes the FPGA state machines and other logic after power supplies are stabilized.

- (3) When the PCIe link turns active, the PCIe function starts up. The PCIe link supports PCIe application in user mode for CvP Update mode, you can also use the PCIe link for fabric image update.

Table 5–3 lists the power-up sequence timing in CvP Update mode, as shown in Figure 5–2.

| Timing Sequence in Figure 5–2 | Timing Range (ms) | Description                                                                                                                       |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| а                             | 10                | Maximum ramp-up time requirement for all POR-monitored<br>power supplies in the FPGA to reach their respective operating<br>range |

| b                             | 4–12              | FPGA POR delay time                                                                                                               |

| C                             | 100               | Minimum perst# signal active time                                                                                                 |

| d                             | 20                | Minimum PERST# signal inactive time before the PCIe link enters training state                                                    |

| e                             | 120               | Maximum time from the FPGA power up to the end of the full FPGA configuration in CvP Update mode                                  |

| f                             | 100               | Minimum PERST# signal inactive time before the PCIe link enter active state                                                       |

Table 5–3. Power-Up Sequence Timing in CvP Update Mode

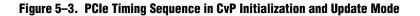

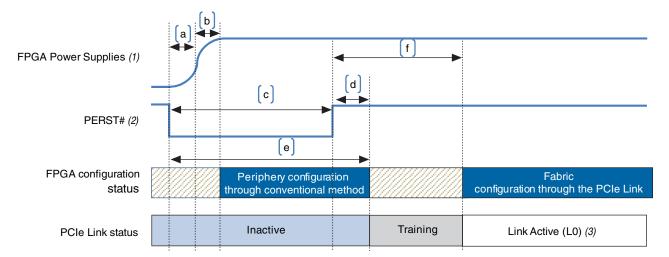

For CvP Initialization and Update mode, the PCIe hard IP block is guaranteed to meet the 120 ms time limit because the periphery image configuration time is significantly smaller when compared with the full FPGA configuration time. When designing CvP for an open system in CvP Initialization and Update mode, you can choose any of the conventional configuration schemes for the periphery image configuration. However, the ramp-up time for the POR-monitored power supplies of the FPGA must not exceed 10 ms. Figure 5–3 shows the PCIe power up and the FPGA configuration timing in CvP Initialization and Update mode.

#### Notes to Figure 5-3:

- (1) To ensure successful configuration, all POR-monitored power supplies to the FPGA must ramp up monotonically to the operating range within the 10 ms ramp-up time.

- (2) One of the auxiliary signals specified in the PCIe electromechanical specification. The PERST# signal is sent from the host to the FPGA and it is used to indicate if the power supplies of the FPGA are within their specified voltage tolerance and are stable. It also initializes the FPGA state machines and other logic after power supplies stabilize.

- (3) After the PCIe link turns active, the PCIe function starts up. For CvP Initialization and Update mode, the PCIe link supports the FPGA fabric configuration, FPGA fabric image update, and PCIe application in user mode.

Table 5–4 lists the power-up sequence timing in CvP Initialization and Update mode, as shown in Figure 5–3.

| Timing Sequence in Figure 5–3 | Timing Range (ms) | Description                                                                                                                       |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| а                             | 10                | Maximum ramp-up time requirement for all POR-monitored<br>power supplies in the FPGA to reach their respective operating<br>range |

| b                             | 4-12              | FPGA POR delay time                                                                                                               |

| С                             | 100               | Minimum perst# signal active time                                                                                                 |

| d                             | 20                | Minimum PERST# signal inactive time before the PCIe link enters training state                                                    |

| е                             | 120               | Maximum time from the FPGA power up to the end of periphery configuration in CvP Initialization and Update mode                   |

| f                             | 100               | Minimum PERST# signal inactive time before the PCIe link enter active state                                                       |

| Table 5-4. Power-Up S | Sequence Timing in CvP | Initialization and Update mode |

|-----------------------|------------------------|--------------------------------|

|-----------------------|------------------------|--------------------------------|

### **Supported Configuration Schemes for CvP Modes**

Figure 5–2 on page 5–5 shows the first FPGA configuration time after device power-ups for CvP Update mode that is constrained to 120 ms to meet the 200-ms PCIe wake-up timing specification for an open system. You must ensure the chosen configuration scheme for full FPGA configuration in CvP Update mode is able to meet the configuration time requirement. If your are not using CvP mode, you must perform your own evaluation on the configuration time to meet the PCIe wake-up timing specification.

Table 5–5 lists supported configuration schemes for different CvP modes to meet the 200-ms PCIe wake-up timing specification.

| Family                                                    | Device                                    | CvP Initialization and<br>Update | CvP Update                 |

|-----------------------------------------------------------|-------------------------------------------|----------------------------------|----------------------------|

|                                                           | 5AGXA1<br>5AGXA3<br>5AGXA5<br>5AGXA7      | (3)                              | FPP x8<br>FPP x16          |

| Arria V GX –                                              | 5AGXB1<br>5AGXB3<br>5AGXB5<br>5AGXB7      | (3)                              | FPP x16                    |

| Arria V GT                                                | 5AGTD3<br>5AGTD7                          | (3)                              | FPP x16                    |

| Arria V SX 5ASXB3<br>5ASXB5                               |                                           | (3)                              | TBD                        |

| Arria V ST 5ASTD3<br>5ASTD5                               |                                           | (3)                              | TBD                        |

| Cyclone V E (4)                                           | 5CEA2<br>5CEA4<br>5CEA5<br>5CEA7<br>5CEA9 | _                                | _                          |

|                                                           | 5CGXC3                                    | (3)                              | AS x4<br>FPP x8<br>FPP x16 |

| Cyclone V GX                                              | 5CGXC4<br>5CGXC5<br>5CGXC7                | (3)                              | FPP x8<br>FPP x16          |

|                                                           | 5CGXC9                                    | (3)                              | FPP x16                    |

| 5CGTD5<br>Cyclone V GT 5CGTD7<br>5CGTD9                   |                                           | (3)                              | TBD                        |

| Cyclone V SE <sup>(4)</sup><br>5CSEA4<br>5CSEA5<br>5CSEA6 |                                           | _                                | _                          |

Table 5–5.

Supported Configuration Schemes for CvP Modes <sup>(1)</sup> <sup>(2)</sup> (Part 1 of 2)

| Family                                    | Device                     | CvP Initialization and<br>Update | CvP Update                   |

|-------------------------------------------|----------------------------|----------------------------------|------------------------------|

| Cyclone V SX                              | 5CSXC4<br>5CSXC5<br>5CSXC6 | (3)                              | TBD                          |

| Cyclone V ST 5CSTD5<br>5CSTD6             |                            | (3)                              | TBD                          |

|                                           | 5SGXA3<br>5SGXA4           | (3)                              | FPP x16<br>FPP x32           |

| Stratix V GX                              | 5SGXA5<br>5SGXA7           | (3)                              | FPP x32                      |

|                                           | 5SGXA9<br>5SGXAB           | (3)                              | _                            |

|                                           | 5SGXB5<br>5SGXB6           | (3)                              | FPP x32                      |

| Stratix V GT                              | 5SGTC5<br>5SGTC7           | (3)                              | FPP x32                      |

|                                           | 5SGSD2<br>5SGSD3           | (3)                              | FPP x8<br>FPP x16<br>FPP x32 |

| Stratix V GS                              | 5SGSD4<br>5SGSD5           | (3)                              | FPP x16<br>FPP x32           |

| -                                         | 5SGSD6<br>5SGSD8           | (3)                              | FPP x32                      |

| Stratix V E <sup>(4)</sup> 5SEE9<br>5SEEB |                            | -                                | _                            |

| Table 5–5. Supported Configuration Schemes for CvP Modes <sup>(1)</sup> <sup>(2)</sup> (Part 2 of 2 | Table 5-5. | 5. Supported Config | uration Schemes for C | vP Modes <sup>(1)</sup> <sup>(2)</sup> | (Part 2 of 2) |

|-----------------------------------------------------------------------------------------------------|------------|---------------------|-----------------------|----------------------------------------|---------------|

|-----------------------------------------------------------------------------------------------------|------------|---------------------|-----------------------|----------------------------------------|---------------|

Notes to Table 5-5:

(1) Data compression and encryption feature are disabled. These features require different data to clock ratio, which causes the total configuration time to prolong and does not meet the 200-ms PCIe wake-up timing specification.

(2) The configuration schemes suggested in this table are based on the fastest DCLK frequency.

(3) For periphery configuration in CvP Initialization and Update mode, all the conventional configuration schemes such as AS, PS, FPP, or JTAG are supported.

(4) No PCIe hard IP, CvP is not supported in this family.

To design CvP in a closed system, you must perform the configuration time estimation to ensure the total FPGA configuration time—either for full FPGA configuration in CvP Update mode, or the periphery configuration in CvP Initialization and Update mode—is within the permitted time given by the PCIe host.

Use the data in Table 5–6 to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal (.hex) or tabular text file (.ttf) format, have different file sizes. For the different types of configuration file and file sizes, refer to the Quartus II software. However, for a specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size. If you are using compression, the file size can vary after each compilation because the compression ratio depends on your design.

Table 5–6 lists the uncompressed raw binary file (**.rbf**) sizes for Altera FPGAs.

| Family          | Device | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) |

|-----------------|--------|--------------------------------|------------------------|

|                 | 5AGXA1 | 69,034,936                     | 1,380,699              |

|                 | 5AGXA3 | 69,034,936                     | 1,380,699              |

|                 | 5AGXA5 | 101,511,640                    | 2,030,233              |

|                 | 5AGXA7 | 101,511,640                    | 2,030,233              |

| Arria V GX –    | 5AGXB1 | 138,416,696                    | 2,768,334              |

| F               | 5AGXB3 | 138,416,696                    | 2,768,334              |

| F               | 5AGXB5 | 185,327,416                    | 3,706,548              |

|                 | 5AGXB7 | 185,327,416                    | 3,706,548              |

|                 | 5AGTD3 | 138,416,696                    | 2,768,334              |

| Arria V GT      | 5AGTD7 | 138,416,696                    | 2,768,334              |

|                 | 5CEA2  | 5,748,552                      | 114,971                |

|                 | 5CEA4  | 9,534,304                      | 190,686                |

| Cyclone V E (2) | 5CEA5  | 14,889,560                     | 297,791                |

| F               | 5CEA7  | 19,965,752                     | 399,315                |

| F               | 5CEA9  | 39,425,016                     | 788,500                |

|                 | 5CGXC3 | 20,651,605                     | 413,032                |

|                 | 5CGXC4 | 51,307,993                     | 1,026,160              |

| Cyclone V GX    | 5CGXC5 | 51,307,993                     | 1,026,160              |

|                 | 5CGXC7 | 99,342,419                     | 1,986,848              |

|                 | 5CGXC9 | 198,526,878                    | 3,970,538              |

|                 | 5CGTD5 | 14,889,560                     | 297,791                |

| Cyclone V GT    | 5CGTD7 | 19,965,752                     | 399,315                |

|                 | 5CGTD9 | 39,425,016                     | 788,500                |

|                 | 5SGXA3 | 139,255,840                    | 1,689,600              |

|                 | 5SGXA4 | 139,255,840                    | 1,689,600              |

|                 | 5SGXA5 | 266,599,584                    | 2,239,436              |

| Strativ V CV    | 5SGXA7 | 266,599,584                    | 2,239,436              |

| Stratix V GX    | 5SGXA9 | 387,394,048                    | 2,141,440              |

|                 | 5SGXAB | 387,394,048                    | 2,141,440              |

| F               | 5SGXB5 | 266,798,896                    | 2,236,416              |

|                 | 5SGXB6 | 266,798,896                    | 2,236,416              |

| Strativ V CT    | 5SGTC5 | 266,035,472                    | 2,195,200              |

| Stratix V GT    | 5SGTC7 | 266,035,472                    | 2,195,200              |

Table 5–6. Uncompressed .rbf Sizes for Altera FPGAs <sup>(1)</sup> (Part 1 of 2)

| · · ·                      |        |                                |                        |

|----------------------------|--------|--------------------------------|------------------------|

| Family                     | Device | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) |

| Stratix V GS               | 5SGSD2 | 93,080,448                     | 933,120                |

|                            | 5SGSD3 | 93,080,448                     | 933,120                |

|                            | 5SGSD4 | 209,935,224                    | 2,004,480              |

|                            | 5SGSD5 | 209,935,224                    | 2,004,480              |

|                            | 5SGSD6 | 266,798,896                    | 2,236,416              |

|                            | 5SGSD8 | 266,798,896                    | 2,236,416              |

| Stratix V E <sup>(2)</sup> | 5SEE9  | 387,394,048                    | 2,141,440              |

|                            | 5SEEB  | 387,394,048                    | 2,141,440              |

#### Table 5–6. Uncompressed .rbf Sizes for Altera FPGAs <sup>(1)</sup> (Part 2 of 2)

Notes to Table 5-6:

(1) These values are preliminary.

(2) No PCIe hard IP, CvP is not supported in this family.

This chapter discusses the software support for CvP mode in the Quartus II software version 11.1.

Table 6–1 lists the features for CvP support that are not enabled in the Quartus II software version 11.1, but will be available in a future release of the Quartus II software.

Table 6–1. Upcoming CvP Support

| Upcoming CvP Feature                                                                         | Description                                                                                                                        |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Programming file generation for periphery and fabric image                                   | Generate programming file for periphery image and fabric image.                                                                    |  |

| Multiple fabric images compilation and generation                                            | Compile multiple fabric image designs in a single project and generate multiple fabric images for fabric image update in CvP mode. |  |

| CvP with configuration features<br>(compression, encryption, and partial<br>reconfiguration) | Enable compression, encryption, and partial reconfiguration feature in CvP mode.                                                   |  |

## **Device and Pin Options Setting**

By default, CvP mode is turned off in the Quartus II software. Before compiling your design, you must set the CvP mode and the CvP\_CONFDONE pin behavior accordingly.

Table 6–2 lists the settings you can specify in the **Device and Pin Options** dialog box to enable CvP mode in your design.

Table 6-2. CvP Settings in Device and Pin Options

| Setting                       | Option                                     | Description                                                                                                                                                                                                                                                              |

|-------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration via<br>Protocol | Power up and subsequent core configuration | Enable CvP Initialization and Update mode. The FPGA periphery is<br>configured through the conventional configuration scheme and the FPGA<br>fabric is configured through the PCIe link. Use the PCIe link for fabric<br>image update or PCIe applications in user mode. |

|                               | Subsequent core reconfiguration            | Enable CvP Update mode. The FPGA is fully configured through the conventional configuration scheme. Use the PCIe link for the fabric image update or PCIe applications in user mode.                                                                                     |

| Cvp_CONFDONE<br>pin           | Enable Cvp_Confdone<br>pin                 | Enable $CvP\_CONFDONE$ . If you turn on this option, the $CvP\_CONFDONE$ pin is used to indicate whether or not the fabric configuration is successfully completed. If you turn off this option, the $CvP\_CONFDONE$ pin functions as a normal user I/O.                 |

|                               | Enable open drain on<br>CvP_CONFDONE pin   | Enable $CvP\_CONFDONE$ as an open drain output pin. If you turn on this option, the $CvP\_CONFDONE$ pin functions as an open drain output. If you turn off this option, the $CvP\_CONFDONE$ is a dedicated output pin.                                                   |

## Hard IP for PCIe version 11.1

IP Compiler for PCIe is the parameter entry tool for the PCIe hard IP block. To use CvP in your design, you must include the hard IP compiler as part of your design. You must enable the **Select the CvP capable HIP block** check box and set the parameter settings according to the PCIe link of your system.

- **For complete information about the IP Compiler for PCIe, refer to the** *IP Compiler for PCI Express User Guide.*

- **For complete information about the Arria V Hard IP Compiler for PCIe, refer to the** *Arria V Hard IP for PCI Express User Guide.*

- **For complete information about the Cyclone V Hard IP Compiler for PCIe, refer to the** *Cyclone V Hard IP for PCI Express User Guide*.

- **For complete information about the Stratix V Hard IP Compiler for PCIe, refer to the** *Stratix V Hard IP for PCI Express User Guide*.

For example, to perform CvP applications on a Stratix V device, follow these steps:

- 1. Open the MegaWizard<sup>™</sup> Plug-In Manager.

- 2. In the MegaWizard Plug-In Manager, select **Stratix V Hard IP for PCI Express v11.1**.

- 3. In the MegaWizard Parameter settings, specify the PCIe settings according to your system.

- 4. Turn on the Select the CvP capable HIP block option.

- 5. Click **Finish**.

### **Generating Periphery Image and Fabric Image**

You can use the **Convert Programming Files** dialog box in the Quartus II Programmer in the Quartus II software to convert programming files for CvP. To generate the periphery image and fabric image for CvP, you must enable the **Create CvP files** check box in the **Convert Programming Files** dialog box. The Quartus II Programmer will generate the following files:

- A **.pof** for the full FPGA image

- A **.pof** for the periphery image

- A **.rbf** for the fabric image

The file extension name for periphery image is *<file\_name>*.**periph.pof** and file extension name for fabric image is *<file\_name>*.**core.rbf**

For more information about the settings in the **Convert Programming Files** dialog box, refer to the *Quartus II programmer* chapter.

# **VSEC**

These Vendor-Specific Extended Capability (VSEC) registers for Configuration Space enhancement have been added to the PCIe hard IP for CvP mode. The PCIe host will write to and poll status bits in these registers to communicate with the FPGA control block. This capability structure occupies byte addresses 200h–240h in the Configuration Space, and its contents are summarized in Table 6–3.

|                 | Register Name                                  |                  |                     |             |  |  |

|-----------------|------------------------------------------------|------------------|---------------------|-------------|--|--|

| 3124            | 2316                                           | 158              | 70                  | Byte Offset |  |  |

| Next Cap Offset | Version                                        | PCI Express Exte | ended Capability ID | 00h         |  |  |

| VSEC Length     | VSEC Rev                                       | VS               | EC ID               | 04h         |  |  |

|                 | Altera Marker                                  |                  |                     |             |  |  |

|                 | Res                                            | erved            |                     | 0Ch         |  |  |

|                 | Res                                            | erved            |                     | 10h         |  |  |

|                 | Res                                            | erved            |                     | 14h         |  |  |

|                 | Reserved                                       |                  |                     |             |  |  |

| CvP S           | CvP Status Reserved                            |                  |                     |             |  |  |

|                 | CvP Mod                                        | le Control       |                     | 20h         |  |  |

|                 | Res                                            | erved            |                     | 24h         |  |  |

|                 | CvP Data                                       |                  |                     |             |  |  |

|                 | CvP Programming Control                        |                  |                     |             |  |  |

|                 | Reserved (for possible CvP expansion)          |                  |                     |             |  |  |

|                 | Uncorrectable Internal Error Status Register   |                  |                     |             |  |  |

|                 | Uncorrectable Internal Error Mask Register 38h |                  |                     |             |  |  |

|                 | Correctable Error Status Register 3Ch          |                  |                     |             |  |  |

|                 | Correctable Erro                               | or Mask Register |                     | 40h         |  |  |

#### **Altera Defined VSEC Header**

Table 6–4 lists the description of the Altera defined VSEC header in the Configuration Space.

| Bits   | Reset Value | PCIe Access<br>Mode | Register Description                                                                                                        |

|--------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

| [150]  | 000Bh       | RO                  | PCI Express Extended Capability ID—PCIe specification defined value for<br>VSEC Capability ID                               |

| [1916] | 1h          | RO                  | Version—PCIe specification defined value for VSEC version                                                                   |

| [3120] | Variable    | RO                  | Next Capability Offset —value is the starting address of the next Capability Structure implemented, if any (per k_xxx bits) |

Table 6-4. Altera Defined VSEC Capability Header (Offset 00h)

#### **Altera Defined Vendor-Specific Header**

Table 6–5 lists the description of the Altera defined vendor-specific header in the Configuration Space.

Table 6–5. Altera defined Vendor-Specific Header (Offset 04h)

| Bits   | Reset Value | PCIe Access<br>Mode | Register Description                                                                                                                                                      |

|--------|-------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [150]  | 1172h       | RO                  | VSEC ID—this will be a user configurable VSEC ID, the default value will 1172h (the Altera Vendor ID) but can be changed in case of conflicts with the other user VSEC ID |

| [1916] | 0           | RO                  | VSEC—user configurable VSEC revision                                                                                                                                      |

| [3120] | 12'h44      | RO                  | VSEC length—total length of this structure in bytes                                                                                                                       |

#### **Altera Marker**

This read only register is an additional marker so that if the user uses the Quartus II software to configure the device using CvP, the Quartus II software can perform an additional check to make sure it is operating with the correct VSEC.

Table 6–6 lists the description of the Altera marker in the Configuration Space.

Table 6-6. Altera Marker (Offset 08h)

| Bits  | Reset Value | PCIe Access<br>Mode | Register Description                                                                                                                                                   |

|-------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |             |                     | Altera Marker—an additional marker for the Quartus II software to be able to verify that this is the right structure to try to use CvP.                                |

| [310] | 11721172h   | RO                  | The upper most byte now indicates a device revision number. The upper 4 bits indicates device type (Stratix $V = 1$ ), the lower 4 bits indicates revision (RevA = 1). |

#### **CvP Status**

The CvP status register provides visibility to software of several control block status signals used in the programming algorithm.

Table 6–7 lists the description of the CvP status in the Configuration Space.

Table 6–7. CvP Status (Offset 1Eh)

| Bits   | Reset Value  | PCIe Access<br>Mode | Register Description                                                                                                                                                                                                                                                                                                  |

|--------|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1510] | 00h          | RO                  | Reserved                                                                                                                                                                                                                                                                                                              |

| [9]    | Signal Value | RO                  | Reserved                                                                                                                                                                                                                                                                                                              |

| [8]    | Signal Value | RO                  | $\tt PLD\_CLK\_IN\_USE\_from$ clock switch module to FPGA fabric. Status bit is provided for debug.                                                                                                                                                                                                                   |

| [7]    | Signal Value | RO                  | CVP_CONFIG_DONE—this signal indicates that the control block has<br>completed the device configuration using CvP and there were no errors. This<br>signal is mutually exclusive with CVP_CONFIG_ERROR. IE for a given<br>configuration attempt either CVP_CONFDONE or CVP_CONFIG_ERROR will come<br>on, but not both. |

| [6]    | 0            | RO                  | Reserved                                                                                                                                                                                                                                                                                                              |

| [5]    | Signal Value | RO                  | USERMODE—indicates if the configurable FPGA fabric is in user mode.                                                                                                                                                                                                                                                   |

| [4]    | Signal Value | RO                  | $\tt CVP\_EN-$ reflects value of the control block signal, indicates if the control block is enabling CvP mode.                                                                                                                                                                                                       |

| [3]    | Signal Value | RO                  | CVP_CONFIG_ERROR—reflects the value of this signal from the control block, checked by software to determine if there was an error during configuration.                                                                                                                                                               |

| [2]    | Signal Value | RO                  | CVP_CONFIG_READY—reflects the value of this signal from the control block, checked by the Quartus II software during programming algorithm.                                                                                                                                                                           |

| [1]    | 0            | RO                  | Indicates that CvP data is treated as compressed.                                                                                                                                                                                                                                                                     |

| [0]    | 0            | RO                  | Indicates that CvP data is treated as encrypted.                                                                                                                                                                                                                                                                      |

#### **CvP Mode Control**

The CvP mode control register provides some global control of the CvP operation. The bits in this register are separated from the bits toggled during programming to provide some form of protection from an accidental flipping of these global control bits that could render the hard IP non-operational.

Table 6–8 lists the description of the CvP mode control byte in the Configuration Space.

| Bits   | Reset Value | PCIe Access<br>Mode | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|