# TVP9900 VSB/QAM Receiver

# Data Manual

Literature Number: SLEA064 March 2007

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### Contents

| 1 | Introd | duction.             |                                                  | . <u>7</u> |

|---|--------|----------------------|--------------------------------------------------|------------|

|   | 1.1    | Feature              | IS                                               | . Z        |

|   | 1.2    | Orderin              | g Information                                    | . <u>7</u> |

| 2 | Block  | c Diagra             | ım                                               | . <u>8</u> |

| 3 | Term   | inal Ass             | signments                                        | . 9        |

|   | 3.1    | Pinout.              | -                                                | . 9        |

|   | 3.2    | Termina              | al Functions                                     | <u>10</u>  |

| 4 | Func   | tional D             | escription                                       | 12         |

|   | 4.1    | Analog               | Front End                                        | 12         |

|   | 4.2    | VSB/QA               | AM Demodulator                                   | <u>12</u>  |

|   | 4.3    | Forward              | d Error Correction                               | <u>12</u>  |

|   | 4.4    | Output               | Formatter                                        | <u>13</u>  |

|   | 4.5    | I <sup>2</sup> C Hos | t Interface                                      | <u>14</u>  |

|   |        | 4.5.1                | I <sup>2</sup> C Write Operation                 | <u>15</u>  |

|   |        | 4.5.2                | I <sup>2</sup> C Read Operation                  | <u>16</u>  |

|   | 4.6    | Tuner C              | Control Interface                                | <u>17</u>  |

|   |        | 4.6.1                | Tuner Write Operation                            | <u>18</u>  |

|   |        | 4.6.2                | Tuner Read Operation                             | <u>18</u>  |

|   | 4.7    | Antenna              | a Control Interface                              | <u>19</u>  |

|   |        | 4.7.1                | Antenna Interrogation/Initialization             | <u>20</u>  |

|   |        | 4.7.2                | Transmit Data to Antenna Operation               | <u>21</u>  |

|   |        | 4.7.3                | Receive Data from Antenna Operation              | <u>21</u>  |

|   | 4.8    | Genera               | I-Purpose IO (GPIO)                              | <u>21</u>  |

|   | 4.9    |                      | Circuits                                         |            |

|   | 4.10   |                      | Up Sequence                                      |            |

|   | 4.11   |                      |                                                  |            |

|   | 4.12   |                      | Down                                             |            |

|   | 4.13   |                      | Supply Voltage Requirements                      |            |

| 5 | -      |                      | Design Recommendations                           |            |

| 6 |        |                      | sor I <sup>2</sup> C Register Summary            |            |

|   | 6.1    |                      | W                                                |            |

|   | 6.2    | -                    | jister Definitions                               |            |

|   |        | 6.2.1                | Receiver Control Register 1 / Soft Reset         |            |

|   |        | 6.2.2                | Receiver Control Register 2                      |            |

|   |        | 6.2.3                | VSB Control Register                             |            |

|   |        | 6.2.4                | AGC Control Register                             |            |

|   |        | 6.2.5                | VSB FEC Time Counter Register 1                  |            |

|   |        | 6.2.6                | VSB FEC Time Counter Register 2                  |            |

|   |        | 6.2.7                | VSB FEC Time Counter Register 3                  |            |

|   |        | 6.2.8                | QAM FEC Time Counter Register 1                  |            |

|   |        | 6.2.9                | QAM FEC Time Counter Register 2                  |            |

|   |        | 6.2.10               | QAM FEC Time Counter Register 3                  |            |

|   |        | 6.2.11               | VSB FEC Segment Error Count Threshold Register 1 |            |

|   |        | 6.2.12               | VSB FEC Segment Error Count Threshold Register 2 |            |

|   |        | 6.2.13               | Update Status Control Register                   |            |

|   |        | 6.2.14               | Receiver Status Register                         |            |

|   |        | 6.2.15               | AGC Status Register 1                            |            |

|   |        | 6.2.16               | AGC Status Register 2                            |            |

|   |        | 6.2.17               | AGC Status Register 3                            |            |

|   |        | 6.2.18               | NTSC Rejection Filter Status Register            | <u>34</u>  |

7

VSB/QAM Receiver SLEA064-MARCH 2007

|       | 6.2.19    | Timing Recovery Status Register 1                                        | <u>34</u> |

|-------|-----------|--------------------------------------------------------------------------|-----------|

|       | 6.2.20    | Timing Recovery Status Register 2                                        | <u>34</u> |

|       | 6.2.21    | Timing Recovery Status Register 3                                        | <u>35</u> |

|       | 6.2.22    | Timing Recovery Status Register 4                                        | <u>35</u> |

|       | 6.2.23    | Timing Recovery Status Register 5                                        | 35        |

|       | 6.2.24    | Timing Recovery Status Register 6                                        | 35        |

|       | 6.2.25    | Pilot Tracking Status Register 1                                         |           |

|       | 6.2.26    | Pilot Tracking Status Register 2                                         |           |

|       | 6.2.27    | Pilot Tracking Status Register 3                                         |           |

|       | 6.2.28    | Carrier Recovery Status Register 1                                       |           |

|       | 6.2.29    | Carrier Recovery Status Register 2                                       |           |

|       | 6.2.30    | Carrier Recovery Status Register 3                                       |           |

|       | 6.2.31    | Carrier Recovery Status Register 4                                       |           |

|       | 6.2.32    | Carrier Recovery Status Register 5                                       |           |

|       | 6.2.33    | Carrier Recovery Status Register 6                                       |           |

|       | 6.2.34    | FEC Status Register 1                                                    |           |

|       | 6.2.34    | FEC Status Register 2                                                    |           |

|       |           |                                                                          |           |

|       | 6.2.36    | FEC Status Register 3                                                    |           |

|       | 6.2.37    | FEC Status Register 4                                                    |           |

|       | 6.2.38    | GPIO Alternate Function Select Register                                  |           |

|       | 6.2.39    | GPIO Output Data Register                                                |           |

|       | 6.2.40    | GPIO Output Enable Register                                              |           |

|       | 6.2.41    | GPIO Input Data Register                                                 |           |

|       | 6.2.42    | MPEG Interface Output Enable Register 1                                  |           |

|       | 6.2.43    | MPEG Interface Output Enable Register 2                                  |           |

|       | 6.2.44    | Tuner Control Interface – I <sup>2</sup> C Slave Device Address Register |           |

|       | 6.2.45    | Tuner Control Interface – Data Register 1 Through 8                      |           |

|       | 6.2.46    | Tuner Control Interface – Control and Status Register                    |           |

|       | 6.2.47    | Antenna Control Interface – Control and Status Register                  |           |

|       | 6.2.48    | Antenna Control Interface – Transmit Data Register 1                     |           |

|       | 6.2.49    | Antenna Control Interface – Transmit Data Register 2                     |           |

|       | 6.2.50    | Antenna Control Interface – Receive Data Register 1                      |           |

|       | 6.2.51    | Antenna Control Interface – Receive Data Register 2                      |           |

|       | 6.2.52    | Firmware ID – ROM Version Register                                       |           |

|       | 6.2.53    | Firmware ID – RAM Major Version Register                                 | <u>46</u> |

|       | 6.2.54    | Firmware ID – RAM Minor Version Register                                 | <u>46</u> |

|       | 6.2.55    | Device ID LSB Register                                                   | <u>47</u> |

|       | 6.2.56    | Device ID MSB Register                                                   | <u>47</u> |

|       | 6.2.57    | Miscellaneous Control Register                                           | 47        |

|       | 6.2.58    | Software Interrupt Raw Status Register                                   | <u>48</u> |

|       | 6.2.59    | Software Interrupt Status Register                                       | <u>48</u> |

|       | 6.2.60    | Software Interrupt Mask Register                                         | <u>49</u> |

|       | 6.2.61    | Software Interrupt Clear Register                                        | <u>50</u> |

| Elect | rical Spe | ecifications                                                             | 51        |

| 7.1   | -         | e Maximum Ratings                                                        |           |

| 7.2   |           | nended Operating Conditions                                              |           |

| 7.3   |           | trical Characteristics                                                   |           |

| 7.4   |           | Input Characteristics                                                    |           |

| 7.5   | •         | Characteristics                                                          |           |

|       | 7.5.1     | Crystal and Input Clock                                                  |           |

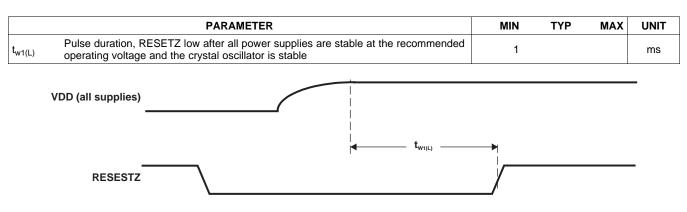

|       | 7.5.2     | Device Reset                                                             |           |

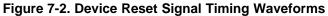

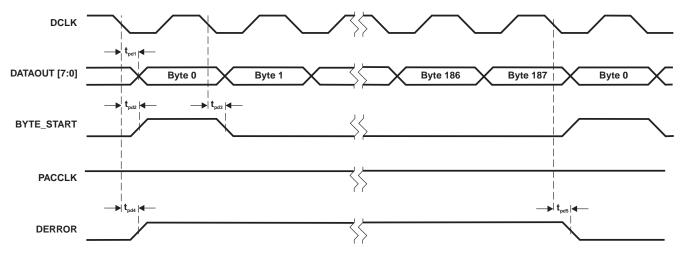

|       | 7.5.3     | MPEG Interface                                                           |           |

|       | 7.5.3.1   | Parallel Mode (Data Only)                                                |           |

|       |           |                                                                          |           |

### TVP9900

### **VSB/QAM** Receiver

SLEA064-MARCH 2007

| 0 | Application   | /// Out                                   |           |

|---|---------------|-------------------------------------------|-----------|

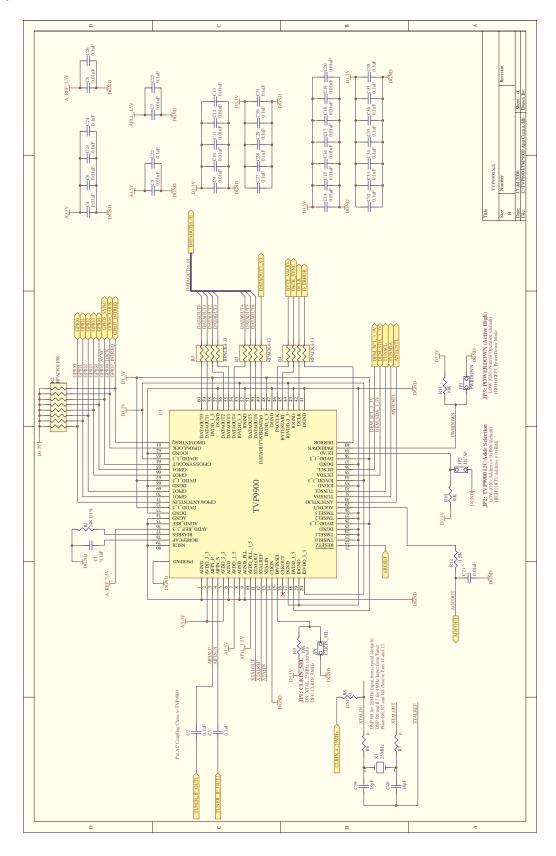

| 8 | Application ( | Sircuit                                   | 60        |

|   | 7.5.4         | Host and Tuner I <sup>2</sup> C Interface | <u>59</u> |

|   | 7.5.3.4       | Serial Mode (Data With Redundancy)        | <u>58</u> |

|   | 7.5.3.3       | Parallel Mode (Data With Redundancy)      | <u>57</u> |

|   | 7.5.3.2       | Serial Mode (Data Only)                   | <u>56</u> |

|   |               |                                           |           |

## List of Figures

| 2-1 | TVP9900 Block Diagram                                                  | . <u>8</u> |

|-----|------------------------------------------------------------------------|------------|

| 4-1 | Parallel Transport Stream Timing Diagram (Data Only)                   | <u>13</u>  |

| 4-2 | Serial Transport Stream Timing Diagram (Data Only)                     | <u>13</u>  |

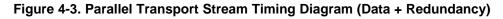

| 4-3 | Parallel Transport Stream Timing Diagram (Data + Redundancy)           | <u>14</u>  |

| 4-4 | Serial Transport Stream Timing Diagram (Data + Redundancy)             | <u>14</u>  |

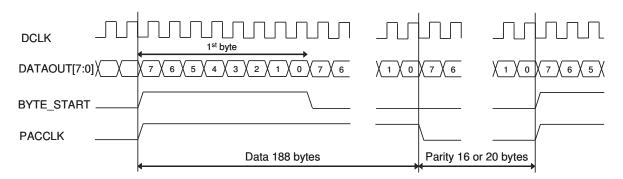

| 4-5 | Tuner Control Interface System                                         | <u>17</u>  |

| 4-6 | Antenna Control Interface System                                       | <u>19</u>  |

| 4-7 | 25-MHz Crystal Oscillation                                             | <u>22</u>  |

| 4-8 | 4-MHz Clock Input                                                      | <u>22</u>  |

| 5-1 | Thermal Land Size and Via Array                                        | <u>24</u>  |

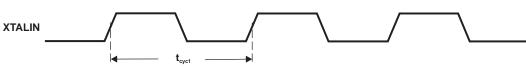

| 7-1 | Crystal or Clock Timing Waveform                                       | <u>54</u>  |

| 7-2 | Device Reset Signal Timing Waveforms                                   | <u>54</u>  |

| 7-3 | MPEG Interface – Parallel Mode (Data Only) Timing Waveforms            | <u>55</u>  |

| 7-4 | MPEG Interface – Serial Mode (Data Only) Timing Waveforms              | <u>56</u>  |

| 7-5 | MPEG Interface – Parallel Mode (Data With Redundancy) Timing Waveforms | <u>57</u>  |

| 7-6 | MPEG Interface – Serial Mode (Data with Redundancy) Timing Waveforms   | <u>58</u>  |

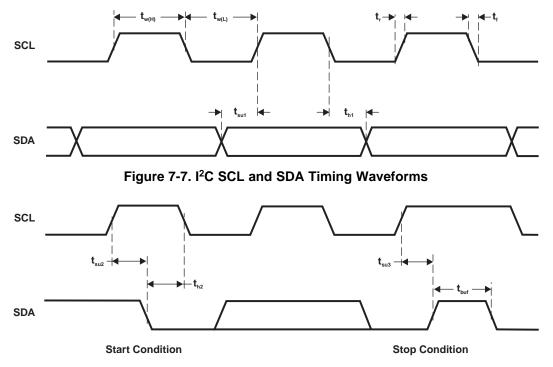

| 7-7 | I <sup>2</sup> C SCL and SDA Timing Waveforms                          | <u>59</u>  |

| 7-8 | I <sup>2</sup> C Start and Stop Conditions Timing Waveforms            | <u>59</u>  |

|     |                                                                        |            |

SLEA064-MARCH 2007

### List of Tables

| 3-1 | Terminal Functions                                     | <u>10</u> |

|-----|--------------------------------------------------------|-----------|

| 4-1 | MPEG-2 Transport Stream Interface                      | <u>13</u> |

| 4-2 | MPEG-2 Transport Stream Output Clock Frequency         | <u>14</u> |

| 4-3 | I <sup>2</sup> C Terminal Description                  | <u>15</u> |

| 4-4 | I <sup>2</sup> C Host Interface Device Write Addresses | <u>15</u> |

| 4-5 | I <sup>2</sup> C Host Interface Device Read Address    | <u>16</u> |

| 4-6 | Tuner Control Interface Registers                      | <u>17</u> |

| 4-7 | Antenna Control Interface Registers                    | <u>19</u> |

| 4-8 | Antenna Control Interface Pins                         | <u>20</u> |

| 6-1 | I <sup>2</sup> C Host Interface Registers              | <u>25</u> |

| 7-1 | Crystal and Input Clock Timing                         | <u>54</u> |

| 7-2 | Device Reset Timing                                    | <u>54</u> |

| 7-3 | Parallel Mode (Data Only) Timing                       | <u>55</u> |

| 7-4 | Serial Mode (Data Only) Timing                         | <u>56</u> |

| 7-5 | Parallel Mode (Data With Redundancy) Timing            | <u>57</u> |

| 7-6 | Serial Mode (Data With Redundancy) Timing              | <u>58</u> |

| 7-7 | Host and Tuner I <sup>2</sup> C Interface Timing       | <u>59</u> |

#### 1 Introduction

The TVP9900 is a cost-effective digital TV (DTV) front-end IC targeted for low-cost high-volume DTV receivers. The TVP9900 is a system-on-chip (SoC) device that integrates the main functions of a DTV front-end system, including programmable gain amplifier (PGA), A/D converter, VSB demodulator, ATSC forward error correction (FEC), QAM demodulator, and ITU-T Annex B FEC. It provides rich peripheral support including AGC control, tuner control, CEA-909 antenna control, and host I<sup>2</sup>C interface. The TVP9900 supports processing of ATSC VSB or ITU-T Annex B QAM IF inputs.

#### 1.1 Features

- ATSC 8-VSB Demodulation and FEC

- ITU-J.83B Compliant 64/256 QAM Demodulation and FEC

- Direct 44-MHz IF Sampling Eliminates Need for External Downconverter

- Integrated IF PGA

- Integrated High-Speed 10-bit A/D Converter

- Integrated Digital Filter Relaxes External Tuner Filters

- Sigma-Delta DAC for AGC Control

- Adjacent Channel Filter

- NTSC Co-Channel Rejection Filter

- All Digital Timing Recovery

- Pilot Tracking Loop With Lock Status Indicator Signal

- Decision-Directed Carrier Phase Tracking Loop

- Field and Segment Synchronization With Sync Status Indicator Signal

- Host Interrupt for Remote Monitoring of Signal Quality

- SNR Monitor

- BER Monitor

- Integrated De-Interleaver RAM

- Parallel/Serial MPEG Output Interface With Error Packet Indicator

- Direct Tuner Control Interface

- EIA/CEA-909 Antenna Control Interface

- Option for 4-MHz Clock Input Driven by MOP IC in Tuner, So No Quartz Crystal Required for Demodulator

- External DAC and VCXO for Clock Recovery Not Required

- Equalizer Covers Echo Profile Required by ATSC A.74 Guideline

- Superior Multipath Performance Demodulating for Brazil Ensembles A Through E

- Power-Down Mode

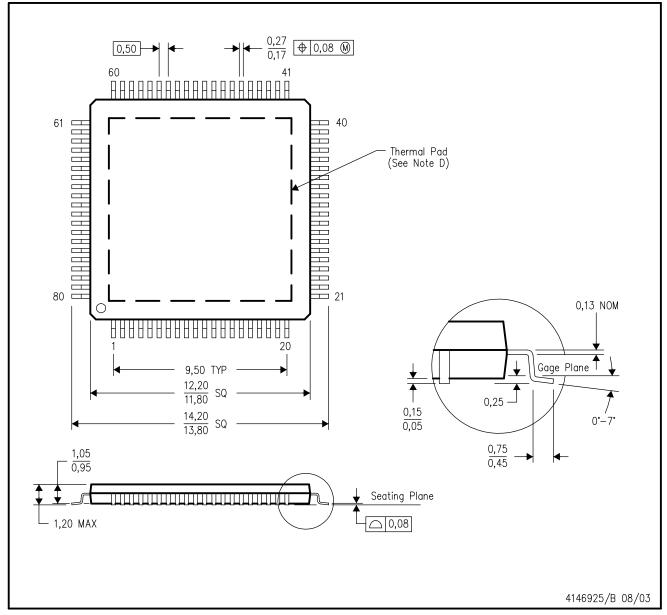

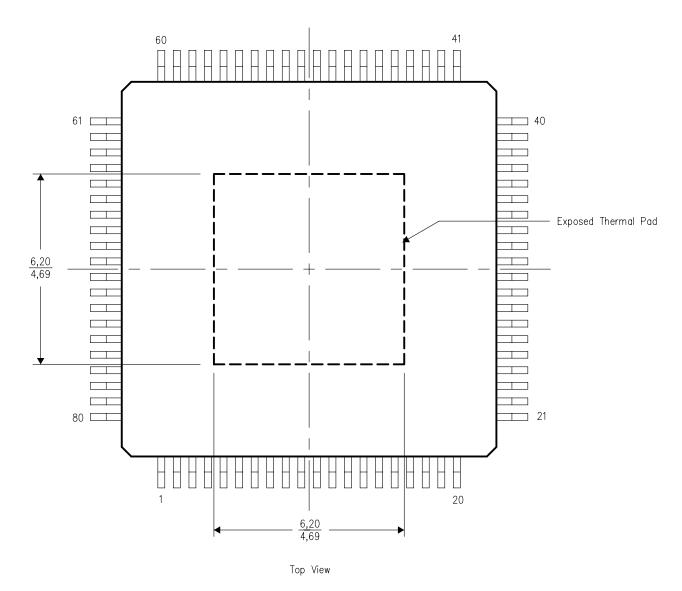

- 80-Pin TQFP Package

#### **1.2** Ordering Information<sup>(1)</sup>

| <b>.</b>       | PACKAGED DEVICES     | PACKAGE OPTION    |  |

|----------------|----------------------|-------------------|--|

| I <sub>A</sub> | 80-Pin TQFP-PowerPAD | - PACKAGE OF TION |  |

| 0°C to 70°C    | TVP9900PFP           | Tray              |  |

|                | TVP9900PFPR          | Tape and Reel     |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at <u>www.ti.com</u>.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

SLEA064-MARCH 2007

#### 2 Block Diagram

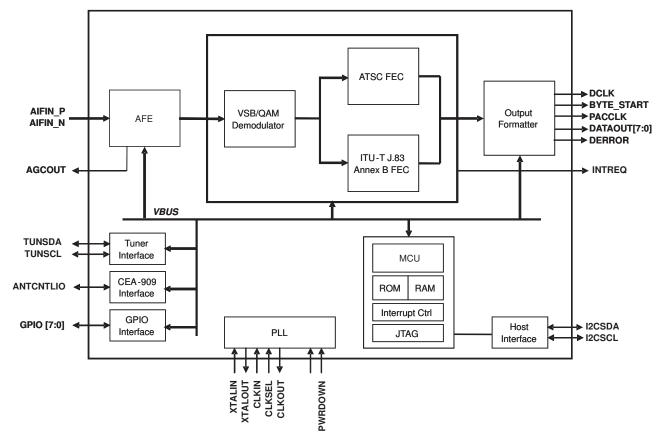

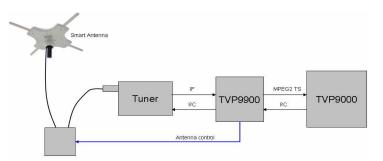

Figure 2-1. TVP9900 Block Diagram

#### **3** Terminal Assignments

#### 3.1 Pinout

SLEA064-MARCH 2007

#### 3.2 Terminal Functions

### Table 3-1. Terminal Functions

| TERMINAL            |                                     |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------------|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | NO.                                 | I/O |                                                                                                                                                                                                                                                                                                                                                                               |  |

| IF INTERFACE        |                                     |     |                                                                                                                                                                                                                                                                                                                                                                               |  |

| AIFIN_P             | 3                                   | I   | Analog positive differential IF input                                                                                                                                                                                                                                                                                                                                         |  |

| AIFIN_N             | 4                                   | I   | Analog negative differential IF input                                                                                                                                                                                                                                                                                                                                         |  |

| TRANSPORT STREAM IN | ITERFACE                            |     |                                                                                                                                                                                                                                                                                                                                                                               |  |

| DCLK                | 42                                  | 0   | MPEG-2 data clock output                                                                                                                                                                                                                                                                                                                                                      |  |

| BYTE_START          | 45                                  | 0   | MPEG-2 Byte Start signal. An active high output signal that indicates the first byte of a transport stream data packet.                                                                                                                                                                                                                                                       |  |

| PACCLK              | 46                                  | 0   | MPEG-2 interface packet framing signal. An active high output signal that remains high for the entire length of the valid data packet.                                                                                                                                                                                                                                        |  |

| DERROR              | 40                                  | 0   | MPEG-2 interface data error. An active high output signal that indicates an error in the data output packet. Indicates an error in the input data. This pin should be tied low if not in use.                                                                                                                                                                                 |  |

| DATAOUT7/SERDATA0   | 49                                  | 0   | <ol> <li>MPEG-2 parallel data output. Bit 7 is the first bit of the transport stream.</li> <li>MPEG-2 serial data output</li> </ol>                                                                                                                                                                                                                                           |  |

| DATAOUT[6:0]        | 50, 51,<br>54, 55,<br>56, 59,<br>60 | 0   | MPEG-2 parallel data output bits 6-0.                                                                                                                                                                                                                                                                                                                                         |  |

| CLOCK SIGNALS       | L                                   |     |                                                                                                                                                                                                                                                                                                                                                                               |  |

| XTALIN              | 13                                  | I   | Crystal input. Input to the on-chip oscillator from an external crystal. The required crystal frequency is 25 MHz. This input can also be driven by an external clock source instead of a crystal. When using an external clock source, a 4 MHz or 25 MHz clock must be used. NOTE: If an external clock source is used, the input can only be used with 1.5-V signal levels. |  |

| XTALOUT             | 11                                  | 0   | Crystal output. Output from the on-chip oscillator to an external crystal.                                                                                                                                                                                                                                                                                                    |  |

| XTALREF             | 12                                  | I   | External crystal reference. This pin is used for the external crystal capacitor ground reference.                                                                                                                                                                                                                                                                             |  |

| CLKIN               | 14                                  | I   | Test clock input. For normal operation, this input should be tied low.                                                                                                                                                                                                                                                                                                        |  |

| DIVINSEL            | 15                                  | I   | PLL VCO divider default input select. This input is used to select the default VCO divider value for the PLL. If a 25-MHz crystal or clock is used for XTALIN, then DIVINSEL should be driven low. If a 4-MHz crystal or clock is used for XTALIN, then DIVINSEL should be driven high.                                                                                       |  |

| CLKOUT 16           |                                     | 0   | Test clock output. For normal operation, this output is not used.                                                                                                                                                                                                                                                                                                             |  |

| MISCELLANEOUS SIGN  | ALS                                 |     |                                                                                                                                                                                                                                                                                                                                                                               |  |

| AGCOUT              | 28                                  | 0   | AGC control Delta-Sigma DAC output.                                                                                                                                                                                                                                                                                                                                           |  |

| ANTCNTLIO           | 29                                  | I/O | Smart antenna control interface input/output.                                                                                                                                                                                                                                                                                                                                 |  |

| TUNSDA              | 30                                  | I/O | Tuner I <sup>2</sup> C serial data input/output. NOTE: The output functions as an open-drain.                                                                                                                                                                                                                                                                                 |  |

| TUNSCL              | 31                                  | I/O | Tuner I <sup>2</sup> C serial clock. NOTE: The output functions as an open-drain.                                                                                                                                                                                                                                                                                             |  |

| GPIO7/INTREQ        | 61                                  | I/O | 1. General purpose I/O     2. Interrupt request output                                                                                                                                                                                                                                                                                                                        |  |

| GPIO6               | 62                                  | I/O | 1. General purpose I/O<br>2. Reserved                                                                                                                                                                                                                                                                                                                                         |  |

| GPIO5/SYNCOUT       | 65                                  | I/O | 1. General purpose I/O<br>2. Sync output                                                                                                                                                                                                                                                                                                                                      |  |

| GPIO[4:2]           | 66, 67,<br>70                       | I/O | General purpose I/O                                                                                                                                                                                                                                                                                                                                                           |  |

| GPIO1               | 71                                  | 0   | Dedicated to Smart Antenna support. Outputs direction of signal on pin 29 in Smart<br>Antenna 1-pin mode.<br>0 = Signal input from antenna to TVP9900, pin 29<br>1 = Signal output from TVP9900 pin 29 to antenna                                                                                                                                                             |  |

| TERMINAL            |                                         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                        |  |  |

|---------------------|-----------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                | NO.                                     |     |                                                                                                                                                                                                                                                                    |  |  |

| GPIO0/ANTCNTLIN     | 72                                      | I/O | Control Input     Antenna Control Input                                                                                                                                                                                                                            |  |  |

| RESETZ              | 21                                      | I   | System reset. An active-low asynchronous input that initializes the device to the default state.                                                                                                                                                                   |  |  |

| PWRDOWN             | 39                                      | I   | Power down terminal. An active high signal puts the device in a low power state.                                                                                                                                                                                   |  |  |

| TMSEL[3:0]          | 22, 23,<br>26, 27                       | Ι   | Test mode select. Tie low for normal operation.                                                                                                                                                                                                                    |  |  |

| HOST INTERFACE      |                                         |     |                                                                                                                                                                                                                                                                    |  |  |

| I2CSDA              | 34                                      | I/O | Host I <sup>2</sup> C serial data input/output. <b>NOTE:</b> The pin functions as an open-drain output.                                                                                                                                                            |  |  |

| I <sup>2</sup> CSCL | 35                                      | I/O | Host I <sup>2</sup> C serial clock. <b>NOTE:</b> The pin functions as an open-drain output.                                                                                                                                                                        |  |  |

| I <sup>2</sup> CA0  | 38                                      | I   | Host I <sup>2</sup> C device address select. Determines address for I <sup>2</sup> C (sampled during reset). A pullup or pulldown 10-k $\Omega$ resistor is needed to program the terminal to the desired address.<br>0 = Address is 0xB8h<br>1 = Address is 0xBAh |  |  |

| POWER SUPPLIES      | 1                                       |     |                                                                                                                                                                                                                                                                    |  |  |

| DVDD_1_5            | 18, 25,<br>37, 48,<br>58, 68,<br>73     | Ρ   | Digital power supply. Connect to 1.5-V digital supply.                                                                                                                                                                                                             |  |  |

| DGND                | 17, 24,<br>36, 41,<br>47, 57,<br>69, 74 | Ρ   | Digital power supply return. Connect to digital ground.                                                                                                                                                                                                            |  |  |

| IOVDD_3_3           | 20, 33,<br>44, 53,<br>64                | Ρ   | IO power supply. Connect to 3.3-V digital supply.                                                                                                                                                                                                                  |  |  |

| IOGND               | 19, 32,<br>43, 52,<br>63                | Ρ   | IO power supply return. Connect to digital ground.                                                                                                                                                                                                                 |  |  |

| AVDD_3_3            | 2, 5                                    | Р   | Analog power supply. Connect to 3.3-V analog supply.                                                                                                                                                                                                               |  |  |

| AVDD_1_5            | 7                                       | Р   | Analog power supply. Connect to 1.5-V analog supply.                                                                                                                                                                                                               |  |  |

| AGND                | 1, 6, 8,<br>75                          | Ρ   | Analog power supply return. Connect to analog ground.                                                                                                                                                                                                              |  |  |

| AVDD_PLL_1_5        | 10                                      | Р   | PLL power supply. Connect to 1.5-V analog supply.                                                                                                                                                                                                                  |  |  |

| AGND_PLL            | 9                                       | Р   | PLL power supply return. Connect to analog ground.                                                                                                                                                                                                                 |  |  |

| NSUB                | 80                                      | Р   | Die substrate. Connect to PCB ground.                                                                                                                                                                                                                              |  |  |

| AVDD_REF_3_3        | 77                                      | Р   | Analog reference power supply. Connect to 3.3-V analog supply.                                                                                                                                                                                                     |  |  |

| AGND_REF            | 76                                      | Р   | Analog reference ground. Connect to analog ground.                                                                                                                                                                                                                 |  |  |

| BGREFCAP            | 79                                      | 0   | Band-gap reference capacitor connection                                                                                                                                                                                                                            |  |  |

| BIASRES             | 78                                      | 0   | Analog bias register. Connect through a 24-k $\Omega$ resistor to PCB ground.                                                                                                                                                                                      |  |  |

#### 4 Functional Description

#### 4.1 Analog Front End

The TVP9900 receiver has an analog input channel that accepts one differential or single-ended 44-MHz center frequency IF input, which are ac-coupled. The receiver supports a maximum input differential voltage range of 1 Vpp with PGA setting at unity gain. The programmable gain amplifier (PGA) and the AGC circuit work together and ensure that the input signal is amplified sufficiently to ensure the proper input range for the ADC. The ADC has 10 bits of resolution. The clock input for the ADC comes from the PLL. An external downconverter is not required to use this IF direct sampling method. The analog front end and adjacent digital filter can potentially relax the requirement for external analog filters, and only one external SAW filter is required.

#### 4.2 VSB/QAM Demodulator

The VSB/QAM demodulator is designed for 8-VSB demodulation compliant with ATSC, and 64/256 QAM demodulation compliant with ITU-T J83 Annex B. The VSB/QAM demodulator in the TVP9900 is composed of the following blocks:

- Automatic gain control

- Adjacent channel filter

- NTSC rejection filter

- Timing recovery

- Pilot tracking

- Matched filter

- Decision feedback equalizer

- Carrier recovery

The all-digital demodulator architecture does not require an external downconverter, AGC control DAC, clock recovery VCXO, or carrier recovery VCXO. This architecture makes a low-cost system implementation possible.

#### 4.3 Forward Error Correction

Forward Error Correction (FEC) in the TVP9000 includes the following blocks:

- QAM FEC

- Trellis decoder

- Synchronizer

- De-randomizer

- De-interleaver

- Reed Solomon decoder

- MPEG deframer

- VSB FEC

- Trellis decoder

- Synchronizer

- De-interleaver

- Reed Solomon decoder

- De-randomizer

The Trellis decoder is designed for help protect against short-burst interference. The VSB synchronizer performs segment and frame synchronization and outputs the synchronization signal with data. An internal RAM is shared by both VSB and QAM modes, and additional external RAM is not required.

#### 4.4 Output Formatter

The TVP9900 transport stream interfaces directly to the back-end IC, which provides transport stream compliance with ISO/IEC 13818-1 in parallel or serial modes. The details of the transport stream interface are shown in Table 4-1. In serial mode, DATAOUT[7] is used as the serial data output, with the MSB output first. The maximum output rate is 42.1 Mbit/s in serial mode. The polarity of DCLK, BYTE\_START, DERROR, and PACCLK is programmable.

| TERMINAL                            | TYPE | DESCRIPTION                                                                                                                                              |

|-------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCLK O Parallel/serial clock output |      | Parallel/serial clock output                                                                                                                             |

| DATAOUT[7:0]                        | 0    | Parallel/serial data output<br>DATAOUT7 is the first bit of the transport stream in parallel mode.<br>DATAOUT7 is the serial data output in serial mode. |

| BYTE_START                          | 0    | Packet sync, indicates the start byte of a transport packet                                                                                              |

| PACCLK                              | 0    | Packet enable, indicates the valid packet data                                                                                                           |

#### Table 4-1. MPEG-2 Transport Stream Interface

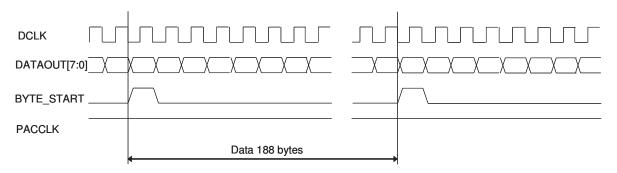

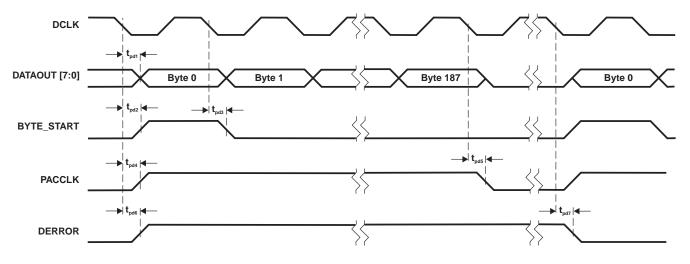

Figure 4-1 and Figure 4-2 show the parallel and serial transport stream timing diagrams in data-only mode. In data-only mode, 188 bytes of data is transferred from the transport stream interface continuously. PACCLK is always kept high.

Figure 4-1. Parallel Transport Stream Timing Diagram (Data Only)

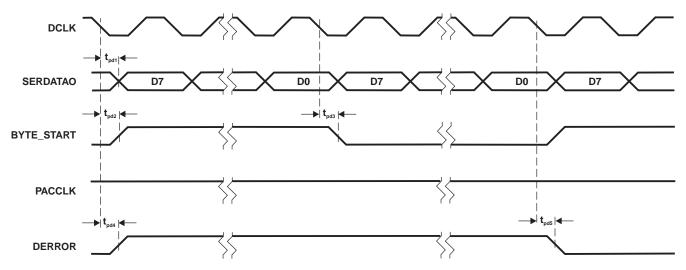

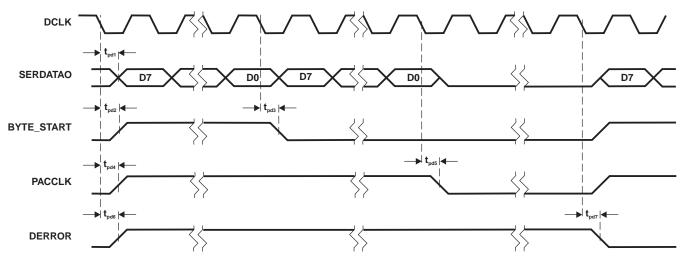

#### Figure 4-2. Serial Transport Stream Timing Diagram (Data Only)

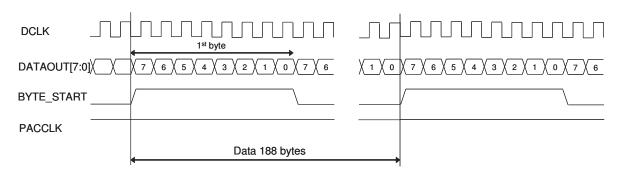

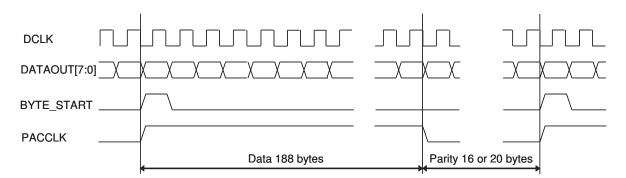

Figure 4-3 and Figure 4-4 show the parallel and serial transport stream timing diagrams in data and redundancy mode. In data and redundancy mode, 188 bytes of data is transferred from the transport stream interface with redundant data bytes. PACCLK only becomes high when the data is valid. Redundancy data is 20 bytes in the ATSC standard and 16 bytes in ITU-T J.83 Annex B.

Table 4-2 shows the transport stream clock frequency in each mode.

|        | BIT RATE | DATA ONLY             |                         | DATA + REDUNDANCY     |                         |

|--------|----------|-----------------------|-------------------------|-----------------------|-------------------------|

| MODE   | (Mbps)   | SERIAL CLOCK<br>(MHz) | PARALLEL CLOCK<br>(MHz) | SERIAL CLOCK<br>(MHz) | PARALLEL CLOCK<br>(MHz) |

| 8VSB   | 19.39266 | 19.39266              | 2.42408                 | 21.45571              | 2.68196                 |

| 64QAM  | 26.97035 | 26.97035              | 3.37129                 | 29.26570              | 3.65821                 |

| 256QAM | 38.81070 | 38.81070              | 4.85133                 | 42.11374              | 5.26422                 |

#### Table 4-2. MPEG-2 Transport Stream Output Clock Frequency

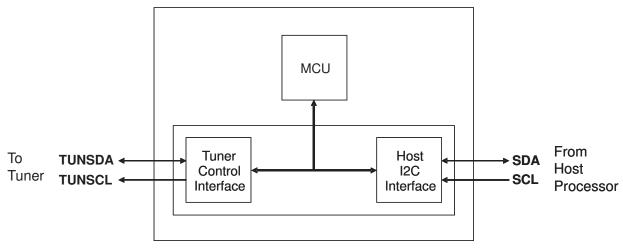

#### 4.5 I<sup>2</sup>C Host Interface

Communication with the TVP9900 receiver is via an I<sup>2</sup>C host interface. The I<sup>2</sup>C standard consists of two signals, the serial input/output data (I2CSDA) line and the input/output clock line (I2CSCL), which carry information between the devices connected to the bus. A 1-bit control signal (I2CA0) is used for slave address selection. Although an I<sup>2</sup>C system can be multi-mastered, the TVP9900 can function as a slave device only. Since I2CSDA and I2CSCL are kept open-drain at logic high output level or when the bus is not driven, the user should connect I2CSDA and I2CSCL to I0VDD\_3.3 via a pullup resistor on the board. At the trailing edge of reset, the status of the I2CA0 line is sampled to determine the device address used. Table 4-3 summarizes the terminal functions of the I<sup>2</sup>C-mode host interface. Table 4-4 and Table 4-5 show the device address selection options.

#### Table 4-3. I<sup>2</sup>C Terminal Description

| SIGNAL | TYPE             | DESCRIPTION             |

|--------|------------------|-------------------------|

| I2CA0  | I                | Slave address selection |

| I2CSCL | I/O (open drain) | Input/output clock line |

| I2CSDA | I/O (open drain) | Input/output data line  |

#### Table 4-4. I<sup>2</sup>C Host Interface Device Write Addresses

| I2CA0 | WRITE ADDRESS |

|-------|---------------|

| 0     | B8h           |

| 1     | BAh           |

Data transfer rate on the bus is up to 400 kbits/s. The number of interfaces connected to the bus is dependent on the bus capacitance limit of 400 pF. The data on the SDA line must be stable during the high period of the SCL, except for start and stop conditions. The high or low state of the data line can only change with the clock signal on the SCL line being low. A high-to-low transition on the SDA line while the SCL is high indicates an I<sup>2</sup>C start condition. A low-to-high transition on the SDA line while the SCL is high indicates an I<sup>2</sup>C stop condition.

Every byte placed on the SDA must be 8 bits long. The number of bytes that can be transferred is unrestricted. Each byte must be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the I<sup>2</sup>C master.

#### 4.5.1 *I*<sup>2</sup>C Write Operation

Data transfers occur utilizing the following illustrated formats. An I<sup>2</sup>C master initiates a write operation to the TVP9900 receiver by generating a start condition (S), followed by the TVP9900 I<sup>2</sup>C address (as shown below), in MSB first bit order, followed by a 0 to indicate a write cycle. After receiving an acknowledge from the TVP9900 receiver, the master presents the sub-address of the register or the first of a block of registers it wants to write, followed by one or more bytes of data, MSB first. The TVP9900 receiver acknowledges each byte after completion of each transfer. The I<sup>2</sup>C master terminates the write operation by generating a stop condition (P).

| Step 1                                           | 0    |      |      |      |      |      |      |      |

|--------------------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C Start (master)                  | S    | ]    |      |      |      |      |      |      |

| Step 2                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (master)        | 1    | 0    | 1    | 1    | 1    | 0    | х    | 0    |

| Step 3                                           | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | А    |      |      |      |      |      |      |      |

| Step 4                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write register address (master) | Addr |

| Step 5                                           | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | А    | ]    |      |      |      |      |      |      |

| Step 6                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write data (master)             | Data |

| Step 7 <sup>(1)</sup>                            | 9    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | A    | ]    |      |      |      |      |      |      |

| Step 8                                           | 0    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (master)                   | Р    | ]    |      |      |      |      |      |      |

(1) Repeat steps 6 and 7 until all data have been written.

#### 4.5.2 PC Read Operation

The read operation consists of two phases. The first phase is the address phase. In this phase, an  $I^2C$  master initiates a write operation to the TVP9900 receiver by generating a start condition (S) followed by the TVP9900  $I^2C$  address, in MSB first bit order, followed by a 0 to indicate a write cycle. After receiving acknowledges from the TVP9900 receiver, the master presents the sub-address of the register or the first of a block of registers it wants to read. After the cycle is acknowledged, the master terminates the cycle immediately by generating a stop condition (P).

#### Table 4-5. I<sup>2</sup>C Host Interface Device Read Address

| I2CA0 | READ ADDRESS |

|-------|--------------|

| 0     | B8h          |

| 1     | BAh          |

The second phase is the data phase. In this phase, an  $I^2C$  master initiates a read operation to the TVP9900 receiver by generating a start condition, followed by the TVP9900  $I^2C$  address (as shown below for a read operation), in MSB-first bit order, followed by a 1 to indicate a read cycle. After an acknowledge from the TVP9900 receiver, the  $I^2C$  master receives one or more bytes of data from the TVP9900 receiver. The  $I^2C$  master acknowledges the transfer at the end of each byte. After the last data byte desired has been transferred from the TVP9900 receiver to the master, the master generates a not acknowledge, followed by a stop.

| Read Phase 1                                     |      |      |      |      |      |      |      |      |

|--------------------------------------------------|------|------|------|------|------|------|------|------|

| Step 1                                           | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (master)                  | S    |      |      |      |      |      |      |      |

| Step 2                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (master)        | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

| Step 3                                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | А    |      |      |      |      |      |      |      |

| Step 4                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Write register address (master) | Addr |

| Step 5                                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | A    |      |      |      |      |      |      |      |

| Step 6                                           | 0    | ]    |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (master)                   | Р    | -    |      |      |      |      |      |      |

| Read Phase 2                                     |      |      |      |      |      |      |      |      |

| Step 7                                           | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (master)                  | S    |      |      |      |      |      |      |      |

| Step 8                                           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (master)        | 1    | 0    | 1    | 1    | 1    | 0    | Х    | 0    |

| Step 9                                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)             | А    |      |      |      |      |      |      |      |

| Step 10                                          | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read data (slave)               | Data |

| Step 11 <sup>(1)</sup>                           | 9    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Not Acknowledge (master)        | A    |      |      |      |      |      |      |      |

| Step 12                                          | 0    |      |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (master)                   | Р    |      |      |      |      |      |      |      |

|                                                  |      | -    |      |      |      |      |      |      |

(1) Repeat steps 10 and 11 for all bytes read. Master does not acknowledge the last read data received.

#### 4.6 **Tuner Control Interface**

The TVP9900 has an  $I^2C$ -compatible two-wire serial interface that can be used by the host processor for tuner control. This dedicated tuner interface can be used by the host processor to transfer data to/from the tuner in order to isolate the tuner from the main system  $I^2C$  bus. As a result, noise coupling to the tuner from host processor  $I^2C$  bus transfers should be minimized.

The TVP9900 tuner control interface operates as an  $I^2C$  bus master and supports both 100-kbps and 400-kbps data transfer rates. The mode and transfer rate is set in the Tuner Control Interface – Control and Status Register (5Eh), bit 0. The device does not support a multi-master bus environment (bus arbitration is not supported).

To transfer data to/from the tuner, the host processor first writes the transaction to a set of registers in the TVP9900 via the host processor  $I^2C$  interface. Then the TVP9900 internal MCU transfers the data to/from the tuner via the tuner control interface.

TUNSCL and TUNSDA need to be pulled up to the 3.3-V supply (IOVDD) and not to a 5-V supply.

Figure 4-5 shows the block diagram of the tuner control interface system.

Figure 4-5. Tuner Control Interface System

Table 4-6 lists the I<sup>2</sup>C registers and their functions used to control the tuner interface.

| Table 4-6 | . Tuner | Control | Interface | Registers |

|-----------|---------|---------|-----------|-----------|

|-----------|---------|---------|-----------|-----------|

| REGISTER        | FUNCTION                                                                                   |

|-----------------|--------------------------------------------------------------------------------------------|

| 55h             | Tuner I <sup>2</sup> C slave address and R/W control                                       |

| 56h to 5Dh      | Data registers 1 through 8                                                                 |

| 5Eh             | Byte Count, Transaction Start, and I <sup>2</sup> C Mode                                   |

| F9, FB, FD, FFh | Software Interrupt Raw Status, Status, Mask, and Clear – Transaction Error and Done Status |

When the TVP9900 tuner I<sup>2</sup>C interface is used, rather than controlling the tuner over the host processor I<sup>2</sup>C bus interface, two status bits are provided in the TVP9900 to indicate a transaction error or the completion of a successful transaction. The TCIERROR bit in the TVP9900 Software Interrupt Status Register (FBh) gets set as a result of a transaction error. The TCIDONE bit in the same register gets set at the end of a normal transaction; it does not get set for an abnormal transaction. The TVP9900 can be configured so that setting the TCIERROR or TCODONE status bits can assert the INTREQ output of the TVP9900; this requires the mask bits to be configured correctly in the TVP9900 Software Interrupt Mask Register (FDh).

SLEA064-MARCH 2007

If the host INTREQ is not used, the TCIDONE and TCIERROR interrupts should be masked and the host should poll the TCIDONE status bit to determine when the transaction is complete, and the host should poll the TCIERROR status bit to determine when an error has occurred.

Tuner data transfers occur utilizing the following illustrated formats.

#### 4.6.1 Tuner Write Operation

The following steps are required to initiate a write operation to the tuner. The host processor first writes the required transaction data to a set of registers in the TVP9900 via the host processor  $I^2C$  interface.

| Step 1               |                                                                                                             |  |

|----------------------|-------------------------------------------------------------------------------------------------------------|--|

| Register 55h         | Set tuner $I^2C$ slave address (bits 7:1) and read/write control (bit 0 = 0)                                |  |

| Step 2               |                                                                                                             |  |

| Registers 56h to 5Dh | Write data bytes to be sent to tuner; 56h is first byte sent                                                |  |

| Step 3               |                                                                                                             |  |

| Register 5Eh         | Set byte count (bits 7:5) and I <sup>2</sup> C mode (bit 0)<br>Set bit 2 to 1 to start transaction to tuner |  |

| Step 4               |                                                                                                             |  |

| Register FBh         | Check state of bits 1:0 or INTREQ pin to verify successful transaction                                      |  |

After the transaction has been initiated, the TVP9900 internal MCU transfers the data to the tuner via the tuner control interface. Acting as the I<sup>2</sup>C master, the TVP9900 initiates a write operation to the tuner (as shown below), by generating a start condition, followed by the tuner I<sup>2</sup>C address, in MSB-first bit order, followed by a 0 to indicate a write cycle. After receiving an acknowledge from the tuner, the TVP9900 presents the sub-address of the register, if needed, followed by one or more bytes of data, MSB first. The tuner acknowledges each byte after completion of each transfer. The TVP9900 terminates the write operation by generating a stop condition.

#### **TVP9900/Tuner Write Operation**

#### 4.6.2 Tuner Read Operation

The following steps are required to initiate a read operation from the tuner. The host processor first writes the required transaction data to a set of registers in the TVP9900 via the host processor  $I^2C$  interface, then reads the data bytes received from the tuner stored in TVP9900 registers.

| Step 1               |                                                                                                             |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| Register 55h         | Set tuner I <sup>2</sup> C slave address (bits 7:1) and read/write control (bit 0 = 1)                      |

| Step 2               |                                                                                                             |

| Register 5Eh         | Set byte count (bits 7:5) and I <sup>2</sup> C mode (bit 0)<br>Set bit 2 to 1 to start transaction to tuner |

| Step 3               |                                                                                                             |

| Register FBh         | Check state of bits 1:0 or INTREQ pin to verify successful transaction                                      |

| Step 4               |                                                                                                             |

| Registers 56h to 5Dh | Read data bytes from tuner; 56h is first byte received                                                      |

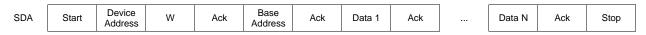

After the transaction has been initiated, the TVP9900 internal MCU transfers the data from the tuner via the tuner control interface. The read operation consists of two phases, as shown below. The first phase is the address phase. In this phase, the TVP9900 I<sup>2</sup>C master initiates a write operation to the tuner by generating a start condition, followed by the tuner I<sup>2</sup>C address, in MSB-first bit order, followed by a 0 to indicate a write cycle. After receiving an acknowledge from the tuner, the TVP9900 presents the sub-address of the register, if needed. After the cycle is acknowledged, the master terminates the cycle immediately by generating a stop condition.

The second phase is the data phase. In this phase, the TVP9900 I<sup>2</sup>C master initiates a read operation to the tuner by generating a start condition, followed by the tuner I<sup>2</sup>C address, in MSB-first bit order, followed by a 1 to indicate a read cycle. After an acknowledge from the tuner, the TVP9900 receives one or more bytes of data from the tuner. The TVP9900 acknowledges the transfer at the end of each byte. After the last data byte desired has been transferred from the tuner to the TVP9900, the TVP9900 generates a not acknowledge, followed by a stop.

#### TVP9900/Tuner Set Start Address, Then Read Operation

| SDA | Start | Device<br>Address | W | Ack | Base<br>Address | Ack | Stop |        |     |      |

|-----|-------|-------------------|---|-----|-----------------|-----|------|--------|-----|------|

| SDA | Start | Device<br>Address | R | Ack | Data 1          | Ack |      | Data N | Ack | Stop |

#### 4.7 Antenna Control Interface

The TVP9900 has an antenna control interface compliant with EIA/CEA-909. The TVP9900 receives the antenna parameters from the host processor via I<sup>2</sup>C, and sends a modulated PWM signal to the antenna. The antenna parameters include antenna direction, antenna polarization, preamplifier gain and channel number. This interface can be used to automatically optimize the signal by adjusting the antenna configuration for the best possible reception.

Figure 4-6 shows the block diagram of the antenna control interface system.

Figure 4-6. Antenna Control Interface System

Table 4-7 lists the I<sup>2</sup>C registers and their functions used with the antenna control interface.

| Table 4-7. | Antenna | Control | Interface | Registers |

|------------|---------|---------|-----------|-----------|

|------------|---------|---------|-----------|-----------|

| REGISTER        | FUNCTION                                                                                         |

|-----------------|--------------------------------------------------------------------------------------------------|

| 4Fh             | GPIO Alternate Function Select                                                                   |

| 5Fh             | Antenna Control Interface – Control and Status                                                   |

| 60h to 61h      | Antenna Control Interface – Transmit Data                                                        |

| 62h to 63h      | Antenna Control Interface – Receive Data                                                         |

| F9, FB, FD, FFh | Software Interrupt Raw Status, Status, Mask, and Clear – Transaction Complete and Timeout Status |

The TVP9900 supports two modes of antenna control: Mode A for basic control (transmit transaction only) and Mode B for advanced control (transmit and receive transactions) as defined in the CEA-909 standard. For Mode B operation, the TVP9900 supports both 1-pin and 2-pin operation. In 1-pin mode, the data input and output are muxed into one pin (pin 29), and in 2-pin mode the input and output use separate pins (pin 29 for output, pin 72 for input.) The desired pin mode is selected by setting register 5Fh, bit 0.

Table 4-8 lists the TVP9900 pins and their functions used with the antenna control interface.

#### Table 4-8. Antenna Control Interface Pins

| PIN | NAME            | FUNCTION                                |  |  |  |

|-----|-----------------|-----------------------------------------|--|--|--|

| 29  | ANTCNTLIO       | Antenna control interface input/output  |  |  |  |

| 71  | GPIO1           | ignal direction of pin 29 in 1-pin mode |  |  |  |

| 72  | GPIO0/ANTCNTLIN | Antenna control input for 2-pin mode    |  |  |  |

The GPIO1 pin provides dedicated smart antenna control support, and in 1-pin mode this pin outputs the direction of the signal on pin 29:

GPIO1 = 0 indicates signal input from antenna to TVP9900 pin 29

GPIO1 = 1 indicates signal output from TVP9900 pin 29 to antenna

Four status bit are provided in the TVP9900 to indicate the completion of a successful receive or transmit transaction, or if a transaction timeout has occurred.

- The ACIRXCT bit in the TVP9900 Software Interrupt Status Register (FBh) gets set when the receive transaction from a Mode B antenna is complete.

- The ACITXCT bit in the same register gets set when the transmit transaction to the antenna is complete.

- The ACIRXTO bit in the same register gets set when an interface timeout has occurred due to no reply form the antenna following a transmit transaction, or an incomplete receive transaction from the antenna.

- The RXERR bit in the Antenna Control Interface Control and Status Register (5Fh) is set if an incomplete receive transaction occurs.

The TVP9900 can be configured so that setting the ACIRXCT, ACITXCT, or ACIRXTO status bits can assert the INTREQ output of the TVP9900; this requires the mask bits to be configured correctly in the TVP9900 Software Interrupt Mask Register (FDh).

If the host INTREQ is not used, the ACIRXCT, ACITXCT, and ACIRXTO interrupts should be masked and the host should poll the ACIRXCT and ACITXCT status bits to determine when the transactions are complete, and the host should poll the ACIRXTO and RXERR status bits to determine when a receive timeout or error has occurred.

Antenna control data transfers occur utilizing the following illustrated formats.

#### 4.7.1 Antenna Interrogation/Initialization

The following steps are required to interrogate and initialize a smart antenna. The host processor first writes the required transaction data to a set of registers in the TVP9900 via the host processor  $I^2C$  interface.

- 1. The system host processor transmits to the antenna a basic Mode A 14-bit serial data stream with an RF channel number of zero.

- 2. The system tri-states the line and waits 100 ms for a reply message from the antenna controller. If no response is received, a timeout occurs, and the antenna controller is assumed to be a Mode A system. The system uses only transmit operations for antenna control.

- 3. If the antenna responds with a 10-bit program identifier, the antenna controller is assumed to be a Mode B system, and the system uses transmit and receive operations for antenna control.

This initialization is optional. If the system has only Mode A enabled, with no Mode B support, then this initialization step may be omitted.

#### 4.7.2 Transmit Data to Antenna Operation

The following steps are required to transmit data to the antenna. The host processor writes the required transaction data to a set of registers in the TVP9900, as described below, via the host processor  $I^2C$  interface.

| Step 1               |                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Register 5Fh         | Set TXRXSEL (bit 2 = 1) to select a transmit data transaction, and set MODE (bit 4 = 1) to enable auto receive mode |

| Step 2               |                                                                                                                     |

| Registers 60h to 61h | Load 14-bit data value to be transmitted to antenna                                                                 |

| Step 3               |                                                                                                                     |

| Register 5Fh         | Set TXSTART (bit 3) to 1 to start transmit transaction to tuner                                                     |

| Step 4               |                                                                                                                     |

| Register FBh         | Check state of bit 4 or INTREQ pin to verify successful transaction                                                 |

#### 4.7.3 Receive Data from Antenna Operation

After an antenna transmit transaction is executed, a Mode B antenna should respond with a 10-bit data value within 100 ms. If the receive data is not received within 100 ms, then a receive timeout occurs. The following steps are required to receive data from the antenna. The host processor first writes the required transaction data to a set of registers in the TVP9900, as described below, via the host processor I<sup>2</sup>C interface, then reads the data bytes received from the antenna stored in TVP9900 registers.

| Step 1               |                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Register 5Fh         | Set TXRXSEL (bit 2 = 0) to select a receive data transaction, and set MODE (bit 4 = 1) to enable auto receive mode  |

| Step 2               |                                                                                                                     |

| Register FBh         | Check state of bit 5 or INTREQ pin to verify successful transaction, or wait for timeout interrupt (bit 3) to occur |

| Step 3               |                                                                                                                     |

| Registers 62h to 63h | Read 10-bit data value received from antenna                                                                        |

| Step 4               |                                                                                                                     |

| Register 5Fh         | Read RXERR value (bit 5)                                                                                            |

The RXERR bit is set to 1 to indicate an error occurred when receiving data from a Mode B antenna. If a non-zero data value was received from the antenna and no error occurred, then the data is valid and the antenna is a Mode B antenna. If the data value is zero and no error occurred, then a receive transaction did not occur and it is assumed that the antenna is a Mode A antenna.

#### 4.8 General-Purpose IO (GPIO)

The TVP9900 has eight general-purpose IO pins, GPIO0–GPIO7. GPIO1 is a dedicated pin for Smart Antenna support. GPIO0, GPIO5, GPIO6, and GPIO7 are shared pins and can be programmed as the following dedicated functions. See register 4Fh description for details about selecting these alternate functions. All pins are configured as inputs at device power-up.

- GPIO0 Antenna control input

- GPIO5 Sync output

- GPIO6 Reserved

- GPIO7 Interrupt request output

#### 4.9 Clock Circuits

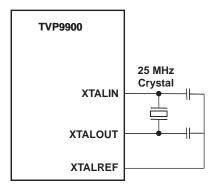

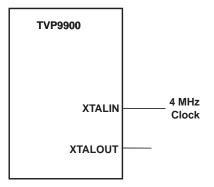

An internal PLL generates all clocks required in the chip. A 25-MHz clock is required to derive the PLL. Most tuner devices have a 4-MHz crystal oscillator that can be output to the demodulator as a clock source. In the TVP9900, a 4-MHz clock input also can be used as the clock source. A 4-MHz clock is input to the TVP9900 receiver on terminal 13 (XTALIN), or a crystal of 25-MHz fundamental resonant frequency may be connected across terminals 13 (XTALIN) and 11 (XTALOUT). Figure 4-7 shows the reference clock configuration of 25-MHz crystal oscillation. NOTE: The oscillator input, XTALIN, is not 3.3-V tolerant and only works at 1.5-V signal levels.

Figure 4-7. 25-MHz Crystal Oscillation

Figure 4-8 shows the reference clock configuration of 4-MHz clock input.

Figure 4-8. 4-MHz Clock Input

#### 4.10 Power-Up Sequence

No specific power-supply sequence is required, as long as all power supplies are ramped to valid operating levels within 500 ms of one another. Output or bidirectional buffers power-up with the output buffers in tri-state mode.

#### 4.11 Reset

The reset signal, RESETZ, is an active-low asynchronous reset that is used to initialize the device at power-up. The RESETZ signal may be low during power-up but must remain active low for a minimum of 1 ms after all power-supply voltages are stable at the recommended operating voltage. Internal circuits synchronize the power-on reset with internal clocks; therefore, the RESETZ signal must remain active low for a minimum of 1  $\mu$ s after the crystal oscillator and clocks are stable.

Reset may be asserted any time after power up and stable crystal oscillation and must remain asserted for at least 1  $\mu$ s. A minimum of 200  $\mu$ s must be allowed after reset before commencing l<sup>2</sup>C operations.

#### 4.12 Power Down

There is no required power-down sequence for the TVP9900.

#### 4.13 Power-Supply Voltage Requirements

The digital core uses a 1.5-V power supply. The digital IO cells use a 3.3-V power supply. Note that the exception is for the oscillator input, XTALIN, which is not 3.3-V tolerant and only works at 1.5-V signal levels. The analog circuitry uses both a 1.5-V and a 3.3-V power supply.

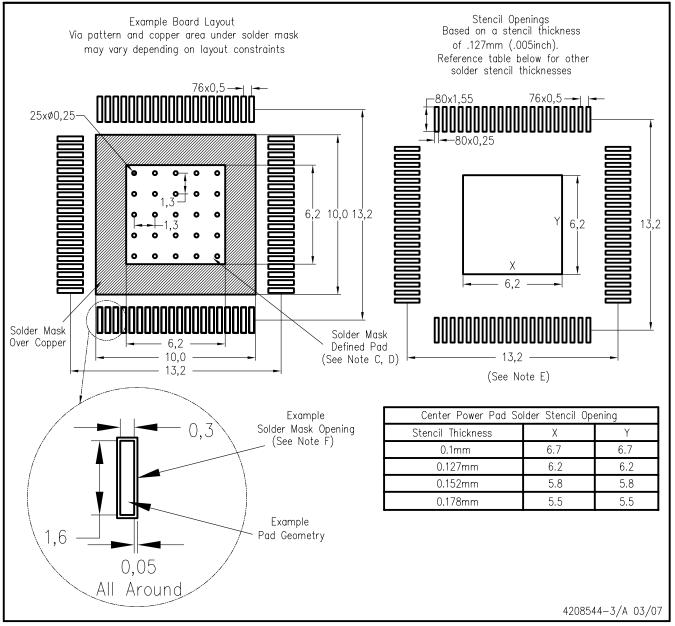

#### 5 High-K PCB Design Recommendations

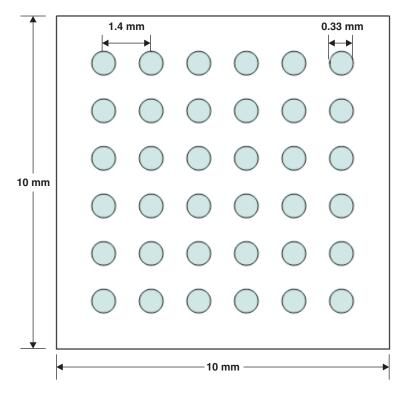

In order to effectively transfer heat out of the package and to keep the die junction temperature below 105°C, the TVP9900 is packaged in the thermal PowerPAD<sup>™</sup> package, which has an exposed metal pad on the bottom of the device. To effectively use this package, the following PCB design requirements must be followed.

- An array of thermal vias should be placed in the board at the placement location of the TVP9900, as shown in Figure 5-1.

- The ideal thermal land size is 10 mm  $\times$  10 mm, and the ideal thermal via pattern is a 6  $\times$  6 array.

- The vias should be connected to the PCB ground plane.

- The exposed metal pad of the TVP9900 should be soldered to these vias.

- The copper trace thickness should be 0.071 mm (2 oz), if possible.

10-mm × 10-mm thermal land size 6 × 6 array of vias 1.4-mm via spacing 0.33-mm via diameter

#### Figure 5-1. Thermal Land Size and Via Array