NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

July 28, 2006

FN8202.1

# Dual Two-wiper Digitally-Controlled (XDCP™) Potentiometer

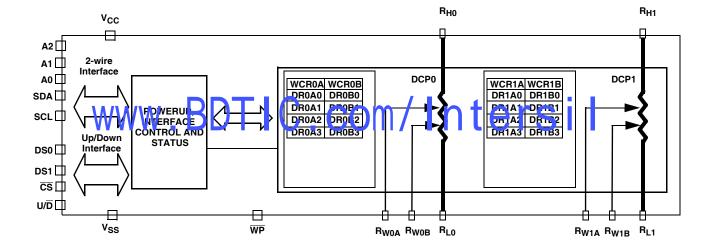

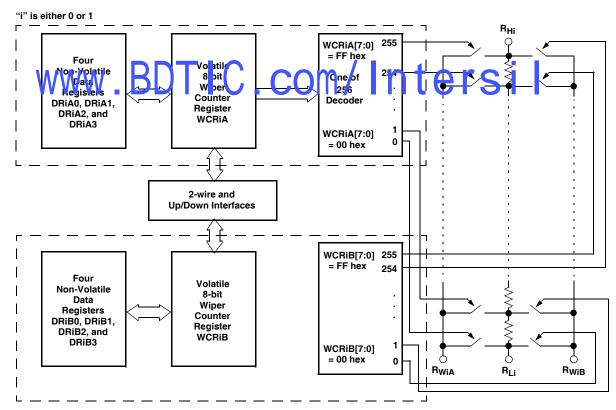

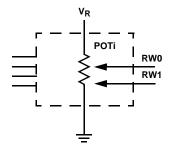

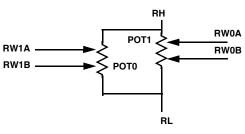

The X9455 integrates 2 digitally controlled potentiometers (XDCP), each one with dual wipers, on a monolithic CMOS integrated circuit.

The digitally controlled potentiometer is implemented using 255 resistive elements in a series array. Between each element are tap points connected to wiper terminals through switches. The position of each wiper on the array is controlled by the user through the U/D or 2-wire bus interface. Each potentiometer wiper has associated with it two volatile Wiper Counter Register (WCR) and each WCR has associated with it four non-volatile Data Registers that can be directly written to and read by the user. The contents of the WCR controls the position of the wiper on the resistor array though the switches. The contents of the default data registers (DR0A0, DR0B0, DR1A0, DR1B0) are loaded into the WCR on power up.

The DCP can be used as a four-terminal potentiometer in a wide variety of applications including the programming of bias voltages, window comparators, and three resistor programmable networks IIC.com/

#### **Features**

- Dual two-wiper solid state potentiometer

- · 256 resistor tap points-0.4% resolution

- 2-wire serial interface for write, read, and transfer operations of the potentiometer

- Up/Down interface for individual potentiometer wipers

- Wiper resistance, 40Ω typical

- Non-volatile storage of wiper positions

- Power on recall loads saved wiper position on power-up.

- Standby current < 20µA Max

- Maximum wiper current: 3mA

- V<sub>CC</sub>: 2.7V to 5.5V operation

- 2.8kΩ,10kΩ, 50kΩ, 100kΩ version of total pot resistance

- Endurance: 100,000 data changes per bit per register

- 100 yr. data retention

- 24 Ld TSSOP

- Pb-free lus anneal available (RoHS compliant)

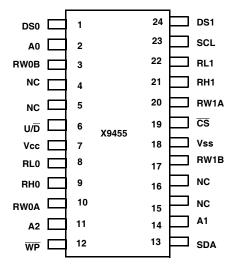

#### **Pinout**

#### X9455 (24 LD TSSOP) TOP VIEW

# **Ordering Information**

| PART NUMBER            | PART<br>MARKING | V <sub>CC</sub> LIMITS (V) | R <sub>TOTAL</sub> (kΩ) | TEMP RANGE (°C) | PACKAGE                       | PKG. DWG. # |

|------------------------|-----------------|----------------------------|-------------------------|-----------------|-------------------------------|-------------|

| X9455TV24I-2.7         | X9455TV G       | 2.7 to 5.5                 | 100                     | -40 to 85       | 24 Ld TSSOP (4.4mm)           | MDP0044     |

| X9455TV24IZ-2.7 (Note) | X9455TV ZG      |                            |                         | -40 to 85       | 24 Ld TSSOP (4.4mm) (Pb-free) | MDP0044     |

| X9455UV24I-2.7         | X9455UV G       |                            | 50                      | -40 to 85       | 24 Ld TSSOP (4.4mm)           | MDP0044     |

| X9455UV24IZ-2.7 (Note) | X9455UV ZG      |                            |                         | -40 to 85       | 24 Ld TSSOP (4.4mm) (Pb-free) | MDP0044     |

| X9455WV24I-2.7         | X9455WV G       |                            | 10                      | -40 to 85       | 24 Ld TSSOP (4.4mm)           | MDP0044     |

| X9455WV24IZ-2.7 (Note) | X9455WV ZG      |                            |                         | -40 to 85       | 24 Ld TSSOP (4.4mm) (Pb-free) | MDP0044     |

| X9455YV24I-2.7         | X9455YV G       |                            | 2.8                     | -40 to 85       | 24 Ld TSSOP (4.4mm)           | MDP0044     |

| X9455YV24IZ-2.7 (Note) | X9455YV ZG      |                            |                         | -40 to 85       | 24 Ld TSSOP (4.4mm) (Pb-free) | MDP0044     |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# Functional Diagram

intersil

# Pin Descriptions

| TSSOP PIN       | SYMBOL | BRIEF DESCRIPTION                             |

|-----------------|--------|-----------------------------------------------|

| 1               | DS0    | Wiper Selection input for Up/Down interface   |

| 2               | A0     | Device Address for 2-wire interface           |

| 3               | RW0B   | Second Wiper Terminal of DCP0                 |

| 4               | NC     | No Connect                                    |

| 5               | NC     | No Connect                                    |

| 6               | U/D    | Increment/Decrement for Up/Down interface     |

| 7               | VCC    | System Supply Voltage                         |

| 8               | RL0    | Low Terminal of DCP0                          |

| 9               | RH0    | High Terminal of DCP0                         |

| 10              | RW0A   | First Wiper Terminal of the DCP0              |

| 11              | A2     | Device Address for 2-wire interface           |

| 12              | WP     | Hardware Write Protect (Active low)           |

| 13              | SDA    | Serial Data Input/Output for 2-wire interface |

| 14              | A1     | Device Address for 2-wire interface           |

| 15              | NC     | No Connect                                    |

| 16              | NC     | No Connect                                    |

| 17              | RW1B   | Second Wiper Terminal of DCP1                 |

| 18              | VSS    | System Ground                                 |

| 19              | CS     | Chip select for Up/Down interface             |

| 20              | RWIA   | FI st W per Terminal of DCP1                  |

| 21 <b>VV VV</b> | RI 1   | High Trimnal of DC 21                         |

| 22              | RL1    | Low Terminal of DCP1                          |

| 23              | SCL    | Serial Clock for 2-wire interface             |

| 24              | DS1    | Wiper selection input for Up/Down interface   |

3

#### **Absolute Maximum Ratings**

#### Junction Temperature under bias. . . . . . . . . . -65°C to +135°C Storage temperature .....-65°C to +150°C Voltage at any digital interface pin with respect to V<sub>SS</sub> . . . . . . . . . . . . -1V to +7V V<sub>CC</sub> . . . . . . . -1V to +7V Voltage at any DCP pin with respect to V<sub>SS</sub>.....-1V to V<sub>CC</sub>

#### **Recommended Operating Conditions**

| Commercial                                  | 0°C to +70°C   |

|---------------------------------------------|----------------|

| Industrial                                  | 10°C to +85°C  |

| Supply Voltage (V $_{CC}$ ) (Note 4) Limits | . 2.7V to 5.5V |

CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Analog Specifications** Over recommended operating conditions unless otherwise stated.

| SYMBOL                                         | PARAMETER                                        | TEST CONDITIONS                                         | MIN               | TYP<br>(Note 4)     | MAX  | UNIT       |

|------------------------------------------------|--------------------------------------------------|---------------------------------------------------------|-------------------|---------------------|------|------------|

| R <sub>TOTAL</sub>                             | End to end resistance                            | Y, W, U, T versions respectively                        |                   | 2.8, 10, 50,<br>100 |      | kΩ         |

|                                                | End to end resistance tolerance                  |                                                         | -20               |                     | +20  | %          |

|                                                | Power rating                                     | 25 C, each DCP                                          |                   |                     | 50   | mW         |

| R <sub>TOTAL</sub><br>Matching                 | DCP to DCP resistance matching                   |                                                         |                   | 0.75                | 2.0  | %          |

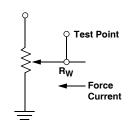

| I <sub>W</sub> (Note 5)                        | Wiper current                                    | See test circuit                                        | -3.0              |                     | +3.0 | mA         |

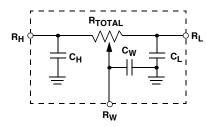

| R <sub>W</sub>                                 | Wiper resistance                                 | Wiper current = $\frac{V_{CC}}{R_{TOTAL}}$              |                   | 50                  | 150  | Ω          |

| V <sub>TERM</sub>                              | Voltage on an VCP pir                            | C.com/L                                                 | V <sub>SS</sub> ( | rsi                 | /cc  | V          |

|                                                | Noise (Note 5)                                   | Ref: 1kHz                                               |                   | -120                |      | dBV        |

|                                                | Resolution                                       |                                                         |                   | 0.4                 |      | %          |

|                                                | Absolute linearity (Note 1) V(R <sub>H0</sub> ): | V(R <sub>H0</sub> )=V(R <sub>H1</sub> )=V <sub>CC</sub> | -1                |                     | +1   | MI (Note 3 |

|                                                | Relative linearity (Note 2)                      | $V(R_{L0})=V(R_{L1})=V_{SS}$                            | -0.3              |                     | +0.3 | MI (Note 3 |

|                                                | Temperature coefficient of resistance (Note 5)   |                                                         |                   | ±300                |      | ppm/°C     |

|                                                | Ratiometric Temperature (Note 5)<br>Coefficient  |                                                         | -20               |                     | +20  | ppm/ C     |

| C <sub>H</sub> /C <sub>L</sub> /C <sub>W</sub> | Potentiometer Capacitance (Note 5)               | See equivalent circuit                                  |                   | 10/10/25            |      | pF         |

| I <sub>OL</sub>                                | Leakage on DCP pins                              | Voltage at pin from V <sub>SS</sub> to V <sub>CC</sub>  |                   | 0.1                 | 10   | μA         |

# **DC Electrical Specifications** Over the recommended operating conditions unless otherwise specified.

|                  | · · · · · · · · · · · · · · · · · · ·                |                                                                                                       |     |     |       |  |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-------|--|

| SYMBOL           | PARAMETER                                            | TEST CONDITIONS                                                                                       | MIN | MAX | UNITS |  |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (Volatile write/read) | f <sub>SCL</sub> = 400kHz; SDA = Open; (for 2-Wire, Active, Read and Volatile Write States only)      |     | 3   | mA    |  |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current (active)              | $f_{SCL} = 200kHz$ ; (for U/ $\overline{D}$ interface, increment, decrement)                          |     | 3   | mA    |  |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current (nonvolatile write)   | f <sub>SCL</sub> = 400kHz; SDA = Open;<br>(for 2-Wire, Active, Nonvolatile Write State only)          |     | 5   | mA    |  |

| I <sub>SB</sub>  | V <sub>CC</sub> current (standby)                    | $V_{CC}$ = +5.5V; $V_{IN}$ = $V_{SS}$ or $V_{CC}$ ; SDA = $V_{CC}$ ; (for 2-Wire, Standby State only) |     | 20  | μΑ    |  |

| ΙL               | Leakage current, bus interface pins                  | Voltage at pin from V <sub>SS</sub> to V <sub>CC</sub>                                                | -10 | 10  | μA    |  |

FN8202.1 intersil July 28, 2006

# DC Electrical Specifications Over the recommended operating conditions unless otherwise specified. (Continued)

| SYMBOL          | PARAMETER                  | TEST CONDITIONS       | MIN                   | MAX                   | UNITS |

|-----------------|----------------------------|-----------------------|-----------------------|-----------------------|-------|

| V <sub>IH</sub> | Input HIGH voltage         |                       | V <sub>CC</sub> x 0.7 | V <sub>CC</sub> + 1   | V     |

| $V_{IL}$        | Input LOW voltage          |                       | -1                    | V <sub>CC</sub> x 0.3 | V     |

| V <sub>OL</sub> | SDA pin output LOW voltage | I <sub>OL</sub> = 3mA |                       | 0.4                   | V     |

#### **Endurance and Data Retention**

| PARAMETER         | MIN     | UNITS                |

|-------------------|---------|----------------------|

| Minimum endurance | 100,000 | Data changes per bit |

| Data retention    | 100     | Years                |

# Capacitance

| SYMBOL                       | TEST                                                                                                                          | TEST CONDITIONS       | MAX | UNITS |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-------|

| C <sub>IN/OUT</sub> (Note 5) | Input / Output capacitance (SDA)                                                                                              | V <sub>OUT</sub> = 0V | 8   | pF    |

| C <sub>IN</sub> (Note 5)     | Input capacitance (DS0, DS1, $\overline{\text{CS}}$ , U/ $\overline{\text{D}}$ , SCL, $\overline{\text{WP}}$ , A2, A1 and A0) | V <sub>IN</sub> = 0V  | 6   | pF    |

# **Power-Up Timing**

| SYMBOL                      | PARAMETER                                                                                                                                          | MAX | UNITS | l |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---|

| t <sub>D</sub> (Notes 5, 9) | Power Up Delay from $V_{CC}$ power up ( $V_{CC}$ above 2.7V) to wiper position recall completed, and communication interfaces ready for operation. | 2   | ms    | 1 |

#### A.C. Test Conditions

| A.G. Test conditions                    | /                                                              |  |  |

|-----------------------------------------|----------------------------------------------------------------|--|--|

| Input Pulse Levels                      | V (1 1 €V cc × 0.5                                             |  |  |

| Input rise and fall times               | 10ns                                                           |  |  |

| Input and output timing threshold level | V <sub>CC</sub> x 0.5                                          |  |  |

| External load at pin SDA                | 2.3k $\Omega$ to V <sub>CC</sub> and 100 pF to V <sub>SS</sub> |  |  |

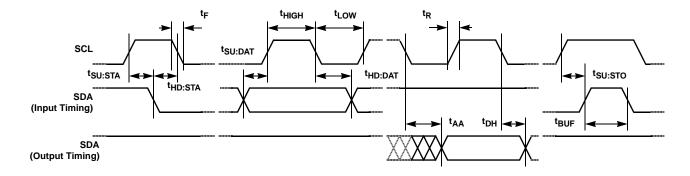

# 2-Wire Interface Timing (s)

| SYMBOL                    | PARAMETER                                          | MIN  | MAX | UNITS |

|---------------------------|----------------------------------------------------|------|-----|-------|

| f <sub>SCL</sub>          | Clock Frequency                                    |      | 400 | kHz   |

| tHIGH                     | Clock High Time                                    | 600  |     | ns    |

| t <sub>LOW</sub>          | Clock Low Time                                     | 1300 |     | ns    |

| t <sub>SU:STA</sub>       | Start Condition Setup Time                         | 600  |     | ns    |

| t <sub>HD:STA</sub>       | Start Condition Hold Time                          | 600  |     | ns    |

| tsu:sto                   | Stop Condition Setup Time                          | 600  |     | ns    |

| t <sub>SU:DAT</sub>       | SDA Data Input Setup Time                          | 100  |     | ns    |

| tHD:DAT                   | SDA Data Input Hold Time                           | 30   |     | ns    |

| t <sub>R</sub> (Note 5)   | SCL and SDA Rise Time                              |      | 300 | ns    |

| t <sub>F</sub> (Note 5)   | SCL and SDA Fall Time                              |      | 300 | ns    |

| t <sub>AA</sub> (Note 5)  | SCL Low to SDA Data Output Valid Time              |      | 0.9 | μs    |

| t <sub>DH</sub>           | SDA Data Output Hold Time                          | 0    |     | ns    |

| t <sub>IN</sub> (Note 5)  | Pulse Width Suppression Time at SCL and SDA inputs |      | 50  | ns    |

| t <sub>BUF</sub> (Note 5) | Bus Free Time (Prior to Any Transmission)          | 1200 |     | ns    |

FN8202.1 July 28, 2006

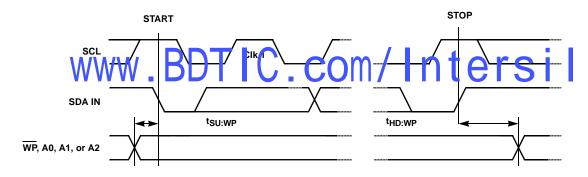

# 2-Wire Interface Timing (s) (Continued)

| SYMBOL                          | PARAMETER                    | MIN | MAX | UNITS |

|---------------------------------|------------------------------|-----|-----|-------|

| t <sub>SU:WPA</sub><br>(Note 5) | A0, A1, A2 and WP Setup Time | 600 |     | ns    |

| <sup>t</sup> HD:WPA<br>(Note 5) | A0, A1, A2 and WP Hold Time  | 600 |     | ns    |

# SDA vs. SCL Timing

# WP, A0, A1, and A2 Pin Timing

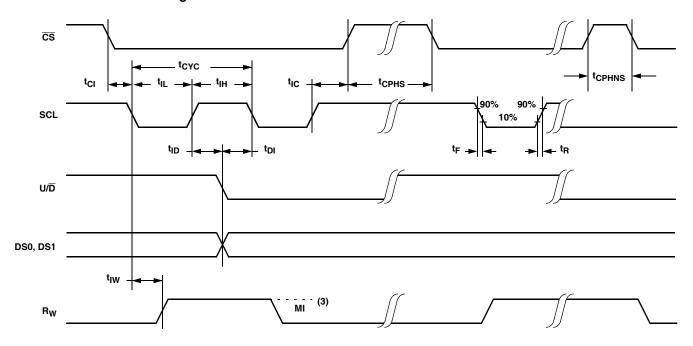

#### **Increment/Decrement Timing**

| SYMBOL                                   | PARAMETER                                                  | MIN | TYP (Note 4) | MAX | UNITS |

|------------------------------------------|------------------------------------------------------------|-----|--------------|-----|-------|

| <sup>t</sup> CI                          | CS to SCL Setup                                            | 600 |              |     | ns    |

| t <sub>ID</sub> (Note 5)                 | SCL HIGH to U/D, DS0 or DS1 change                         | 600 |              |     | ns    |

| t <sub>DI</sub> (Note 5)                 | U/D, DS0 or DS1 to SCL setup                               | 600 |              |     | ns    |

| t <sub>IL</sub>                          | SCL LOW period                                             | 2.5 |              |     | μs    |

| t <sub>IH</sub>                          | SCL HIGH period                                            | 2.5 |              |     | μs    |

| t <sub>IC</sub>                          | SCL inactive to CS inactive (Nonvolatile Store Setup Time) | 1   |              |     | μs    |

| t <sub>CPHS</sub>                        | CS deselect time (STORE)                                   | 10  |              |     | ms    |

| tCPHNS<br>(Note 5)                       |                                                            |     |              |     | μs    |

| t <sub>IW</sub> (Note 5)                 | SCL to R <sub>W</sub> change                               |     | 100          | 500 | μs    |

| t <sub>CYC</sub>                         | SCL cycle time                                             | 5   |              |     | μs    |

| t <sub>R</sub> , t <sub>F</sub> (Note 5) | SCL input rise and fall time                               |     |              | 500 | μs    |

intersil

#### Increment/Decrement Timing

#### **High-Voltage Write Cycle Timing**

| SYMBOL                          | PARAMETER                     | TYP             | MAX            | UNITS |

|---------------------------------|-------------------------------|-----------------|----------------|-------|

| t <sub>WC</sub><br>(Notes 5, 8) | Non-volatile write cycle time | 5               | 10             | ms    |

| (110103 0, 0)                   | <del>'www.BDIIC.com/In</del>  | <del>ters</del> | <del>311</del> |       |

#### **XDCP Timing**

| SYMBOL | PARAMETER                                                                                                   | MIN | MAX | UNITS |

|--------|-------------------------------------------------------------------------------------------------------------|-----|-----|-------|

|        | SCL rising edge to wiper code changed, wiper response time after instruction issued (all load instructions) | 5   | 20  | μs    |

#### NOTES:

- 1. Absolute linearity is utilized to determine actual wiper voltage versus expected voltage =  $[V(R_{W(n)(actual)})-V(R_{W(n)(expected)})]/MIV(R_{W(n)(expected)}) = n(V(R_H)-V(R_L))/255 + V(R_L)$ , with n from 0 to 255.

- 2. Relative linearity is a measure of the error in step size between taps =  $[V(R_{W(n+1)})-(V(R_{W(n)})+MI)]/MI$ , with n from 0 to 254

- 3. 1 MI = Minimum Increment = [V(R<sub>H</sub>)-V(R<sub>I</sub>)]/255.

- 4. Typical values are for  $T_A = 25$  C and nominal supply voltage.

- 5. This parameter is not 100% tested.

- 6. Ratiometric temperature coefficient =  $(V(R_W)_{T1(n)}-V(R_W)_{T2(n)})/[V(R_W)_{T1(n)}(T1-T2)] \times 10^6$ , with T1 & T2 being 2 temperatures, and n from 0 to 255.

- 7. Measured with wiper at tap position 255, R<sub>I</sub> grounded, using test circuit.

- 8. t<sub>WC</sub> is the minimum cycle time to be allowed for any nonvolatile write by the user, unless Acknowledge Polling is used. It is the time from a valid STOP condition at the end of a write sequence of a 2-wire interface write operation, or from the rising edge of CS of a valid "Store" operation of the Up/Down interface, to the end of the self-timed internal nonvolatile write cycle.

- 9. The recommended power up sequence is to apply V<sub>CC</sub>/V<sub>SS</sub> first, then the potentiometer voltages. During power up, the data sheet parameters for the DCP do <u>not</u> fully apply until t<sub>D</sub> after V<sub>CC</sub> reaches its final value. In order to prevent unwanted tap position changes, or an inadvertant store, bring the <del>CS</del> pin high before or concurrently with the V<sub>CC</sub> pin on power up.

FN8202.1 July 28, 2006

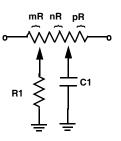

#### **Test Circuit**

#### **Equivalent Circuit**

# Pin Descriptions

#### **Bus Interface Pins**

#### Serial Data Input/Output (SDA)

The SDA is a bidirectional serial data input/output pin for the 2-wire interface. It receives device address, operation code, wiper register address and data from a 2-wire external master device at the listing adge of the serial clock SCL, and COM/ NTERS it shifts out data after each falling eage of the serial clock. SCL.

SDA requires an external pull-up resistor, since it's an open drain output.

#### Serial Clock (SCL)

This input is the serial clock of the 2-wire and Up/Down interface.

#### **Device Address (A2-A0)**

The Address inputs are used to set the least significant 3 bits of the 8-bit 2-wire interface slave address. A match in the slave address serial data stream must be made with the Address input pins in order to initiate communication with the X9455. A maximum of 8 devices may occupy the 2-wire serial bus.

# **Chip Select (CS)**

When the CS pin is low, increment or decrement operations are possible using the SCL and U/D pins. The 2-wire interface is disabled at this time. When CS is high, the 2-wire interface is enabled.

#### Up or Down Control (U/D)

The U/D input pin is held HIGH during increment operations and held LOW during decrement operations.

#### DCP Select (DS1-DS0)

The DS1-DS0 select one of the four DCPs for an Up/Down interface operation.

#### **Hardware Write Protect Input (WP)**

When the WP pin is set low, "write" operations to non volatile DCP Data Registers are disabled. This includes both 2-wire interface non-volatile "Write", and Up/Down interface "Store" operations.

#### **DCP Pins**

#### RHO, RLO, RH1, RL1

These pins are equivalent to the terminal connections on mechanical potentiometers. Since there are two DCPs, there is one set of RH and RI for each DCP.

#### RWOA, RWOB, RW1A, and RW1B

The wiper pins are equivalent to the wiper terminals of mechanical potentiometers. Since there are two wipers per DCP, there are four R<sub>W</sub> pins.

### Principles of Operation

The X9455 is an integrated circuit incorporating two resistor arrays with dual wipers on each array, their associated registers and counters, and the serial interface logic providing direct communication between the host and the digitally controlled potentiometers. This section provides detail description of the following:

- · Resistor Array

- · Up/Down Interface

- · 2-wire Interface

#### Resistor Array Description

The X9455 is comprised of two resistor arrays. Each array contains 255 discrete resistive segments that are connected in series. The physical ends of each array are equivalent to the fixed terminals of a mechanical potentiometer (RHi and R<sub>I i</sub> inputs). (See Figure 1.)

Each array has two independent wipers. At both ends of each array and between each resistor segment are two

switches, one connected to each of the wiper pins (RWiA and

Within each individual array only one switch of each wiper may be turned on at a time.

These switches are controlled by two Wiper Counter Register (WCR). The 8-bits of the WCR are decoded to select and enable one of 256 switches. Note that each wiper has a dedicated WCR. When all bits of a WCR are zeroes, the switch closest to the corresponding R<sub>I</sub> pin is selected. When all bits of a WCR are ones, the switch closest to the corresponding RH pin is selected.

The WCRs are volatile and may be written directly. There are four non-volatile Data Registers (DR) associated with each WCR. Each DR can be loaded into WCR. All DRs and WCRs can be read or written.

#### Power Up and Down Requirements

During power up CS must be high to avoid inadvertant "store" operations. At power up, the contents of Data Registers Level 0 (DR0A0, DR0B0, DR1A0, and DR1B0), are loaded into the corresponding wiper counter register.

FIGURE 1. DETAILED BLOCK DIAGRAM OF ONE DCP

intersil FN8202.1 July 28, 2006

### **Up/Down Interface Operation**

The SCL, U/ $\overline{D}$ ,  $\overline{CS}$ , DS0 and DS1 inputs control the movement of the wiper along the resistor array. With  $\overline{CS}$  set LOW the device is selected and enabled to respond to the U/ $\overline{D}$  and SCL inputs. HIGH to LOW transitions on SCL will increment or decrement (depending on the state of the U/ $\overline{D}$  input) a wiper counter register selected by DS0 and DS1. The output of this counter is decoded to select one of 256 wiper positions along the resistor array.

The value of the counter is stored in nonvolatile data register Level 0 of the corresponding WCR whenever  $\overline{CS}$  transitions HIGH while the SCL and  $\overline{WP}$  inputs are HIGH (See Table 1). During a "Store" operation bits WCRSel1 and WCRSel0 in the status register must be both "0", which is their power up default value. Other combinations are reserved and must not be used.

The system may select the X9455, move a wiper, and deselect the device without having to store the latest wiper position in nonvolatile memory. After the wiper movement is performed as described above and once the new position is reached, the system must keep SCL LOW while taking  $\overline{\text{CS}}$  HIGH. The new wiper position is maintained until changed by the system or until a power-down/up cycle recalled the previously stored data.

This procedure allows the system to always power-up to a preset value stored in nonvolatile memory than curing system operation minor adjustments equic be made. The adjustments might be based on user preference, system parameter changes due to temperature drift, etc.

The state of  $U/\overline{D}$  may be changed while  $\overline{CS}$  remains LOW. This allows the host system to enable the device and then move the wiper up and down until the proper trim is attained. The 2-wire interface is disabled while  $\overline{CS}$  remains LOW.

TABLE 1. DCP SELECTION FOR UP/DOWN CONTROL

| DS1 | DS0 | SELECTED WIPER CONTROL REGISTER |

|-----|-----|---------------------------------|

| 0   | 0   | Wiper A of DCP0                 |

| 1   | 1   | Wiper B of DCP0                 |

| 1   | 0   | Wiper A of DCP1                 |

| 0   | 1   | Wiper B of DCP1                 |

TABLE 2. MODE SELECTION FOR UP/DOWN CONTROL

| CS | SCL | U/D | MODE                                                                                                         |

|----|-----|-----|--------------------------------------------------------------------------------------------------------------|

| L  | 7   | Н   | Wiper Up                                                                                                     |

| L  | _   | L   | Wiper Down                                                                                                   |

|    | Н   | Х   | Store Wiper Position to nonvolatile memory if WP pin is high. No store, return to standby, if WP pin is low. |

| Н  | Х   | Х   | Standby*                                                                                                     |

|    | L   | Х   | No Store, Return to Standby                                                                                  |

| ~_ | L   | Н   | Wiper Up (not recommended)                                                                                   |

| _  | L   | L   | Wiper Down (not recommended)                                                                                 |

<sup>\*</sup>While in Standby, the 2-wire interface is enabled

# com/Intersil

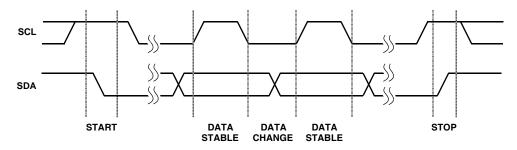

FIGURE 2. VALID DATA CHANGES, START, AND STOP CONDITIONS

#### 2-Wire serial interface

#### **Protocol Overview**

The device supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is called the master and the device being controlled is called the slave. The master always initiates data transfers, and provides the clock for both transmit and receive operations. The X9455 operates as a slave in all applications.

All 2-wire interface operations must begin with a START, followed by a Slave Address byte. The Slave Address selects the X9455, and specifies if a Read or Write operation is to be performed.

All Communication over the 2-wire interface is conducted by sending the MSB bletch by e of data first.

#### Serial Clock and Data

Data states on the SDA line can change only while SCL is LOW. SDA state changes while SCL is HIGH are reserved for indicating START and STOP conditions (See Figure 2). On power up of the X9455, the SDA pin is in the input mode.

#### Serial Start Condition

All commands are preceded by the START condition, which is a HIGH to LOW transition of SDA while SCL is HIGH. The device continuously monitors the SDA and SCL lines for the START condition and does not respond to any command until this condition has been met (See Figure 2).

#### Serial Stop Condition

All communications must be terminated by a STOP condition, which is a LOW to HIGH transition of SDA while SCL is HIGH. The STOP condition is also used to place the device into the Standby power mode after a read sequence. A STOP condition can only be issued after the transmitting device has released the bus (See Figure 2).

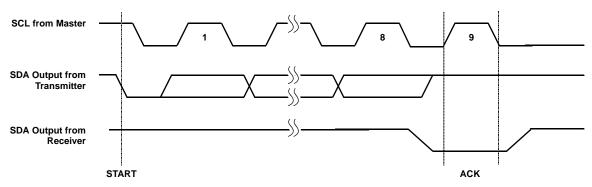

#### Serial Acknowledge

An ACK (Acknowledge), is a software convention used to indicate a successful data transfer. The transmitting device, either master or slave, releases the bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDA line LOW to acknowledge the reception of the eight bits of data (See Figure 3).

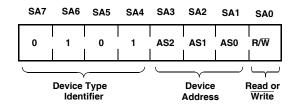

The device responds with an ACM after recognition of a START co dit or followed by a valid Slave Address byte. A valid Slave Address byte must contain the Device Type Identifier 0101, and the Device Address bits matching the logic state of pins A2, A1, and A0 (See Figure 4).

If a write operation is selected, the device responds with an ACK after the receipt of each subsequent eight-bit word.

In the read mode, the device transmits eight bits of data, releases the SDA line, and then monitors the line for an ACK. The device continues transmitting data if an ACK is detected. The device terminates further data transmissions if an ACK is not detected. The master must then issue a STOP condition to place the device into a known state.

FIGURE 3. ACKNOWLEDGE RESPONSE FROM RECEIVER

#### Slave Address Byte

Following a START condition, the master must output a Slave Address Byte (Refer to figure 4.). This byte includes three parts:

- The four MSBs (SA7-SA4) are the Device Type Identifier, which must always be set to 0101 in order to select the X9455.

- The next three bits (SA3-SA1) are the Device Address bits (AS2-AS0). To access any part of the X9455's memory, the value of bits AS2, AS1, and AS0 must correspond to the logic levels at pins A2, A1, and A0 respectively.

- The LSB (SA0) is the R/W bit. This bit defines the operation to be performed on the device being addressed. When the R/W bit is "1", then a Read operation is selected. A "0" selects a Write operation.

| SLAVE ADDRESS<br>BIT(S) | DESCRIPTION                    |

|-------------------------|--------------------------------|

| SA7-SA4                 | Devite Type dent fiel          |

| SA3-SA1                 | Device Address                 |

| SA0                     | Read or Write Operation Select |

FIGURE 4. SLAVE ADDRESS (SA) FORMAT

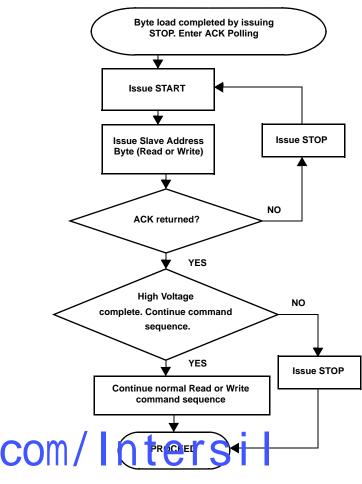

#### Nonvolatile Write Acknowledge Polling

After a nonvolatile write command sequence is correctly issued (including the final STOP condition), the X9455 initiates an internal high voltage write cycle. This cycle typically requires 5 ms. During this time, any Read or Write command is ignored by the X9455. Write Acknowledge Polling is used to determine whether a high voltage write cycle is completed.

During acknowledge polling, the master first issues a START condition followed by a Slave Address Byte. The Slave Address Byte contains the X9455's Device Type Identifier and Device Address. The LSB of the Slave Address (R/W) can be set to either 1 or 0 in this case. If the device is busy within the high voltage cycle, then no ACK is returned. If the high voltage cycle is completed, an ACK is returned and the master can then proceed with a new Read or Write operation. (Refer to figure 5.)

FIGURE 5. ACKNOWLEDGE POLLING SEQUENCE

### 2-Wire Serial Interface Operation

#### X9455 Digital Potentiometer Register Organization

Refer to the Functional Diagram on page 1. There are 2 Digital Potentiometers, referred to as DCP0, and DCP1. Each potentiometer has two volatile Wiper Control Registers (WCRs). Each wiper has four non-volatile registers to store wiper position or general data. See Table 2 for register numbering.

intersil FN8202.1

July 28, 2006

**TABLE 3. REGISTER NUMBERING**

|          | STATUS REG (NOTE 1) (Addr: 07H) |       |          |             | REGISTERED SELECTED (NOTE 2) |             |             |  |  |

|----------|---------------------------------|-------|----------|-------------|------------------------------|-------------|-------------|--|--|

| Reserved | DRSel1 DRSel0                   |       | NVEnable | DCP0        |                              | DCP2        |             |  |  |

| bits 7-3 | bit 2                           | bit 1 | bit 0    | (Addr: 00h) | (Addr: 11h)                  | (Addr: 02h) | (Addr: 01h) |  |  |

| Reserved | Х                               | X     | 0        | WCR0A       | WCR0B                        | WCR1A       | WCR1B       |  |  |

|          | 0                               | 0     | 1        | DR0A0       | DR0B0                        | DR1A0       | DR1B0       |  |  |

|          | 0                               | 1     | 1        | DR0A1       | DR0B1                        | DR1A1       | DR1B1       |  |  |

|          | 1                               | 0     | 1        | DR0A2       | DR0B2                        | DR1A2       | DR1B2       |  |  |

|          | 1                               | 1     | 1        | DR0A3       | DR0B3                        | DR1A3       | DR1B3       |  |  |

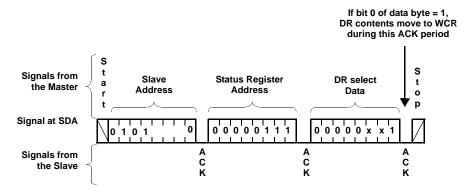

#### NOTES:To read or write the contents of a single Data Register or Wiper Register:

1. Load the status register (using a write command) to select the row. (See Figure 6.)

Writing a 1, 3, 5, or 7 to the Status Register specifies that the subsequent read or write command will access a Data Register. This Status Register operation also initiates a transfer of the contents of the selected data register to its associated WCR for all DCPs. So, for example, writing '03h' to the status register causes the value in DR01 to move to WCR0, DR11 to move to WCR1, DR21 to move to WCR2, and DR31 to move to WCR3.

Writing a 0 to bit '0' of the Status Register specifies that the subsequent read or write command will access a Wiper Counter Register. Each WCR can be written to individually, without affecting the contents of any other.

2. Access the desired DR or WCR using a new write or read command (see Figure 7 for write and Figure 9 for read.) Specify the desired column (DCP number) by sending the DCP address as part of this read or write command.

The registers are organized in pages of four, with one page consisting of the four volatile WCRs, a second page consisting of the Level 0 Data Registers, and so forth. These pages can be written four bytes at time to this manner all four potentiometer WCRs can be undated in a sir gle serial write (see Page Write Operation), as well as all four registers of a given page in the DR array.

The unique feature of the X9455 device is that writing or reading to a Data Register of a given wiper automatically updates the WCR of that wiper with the new value. In this manner data can be moved from a particular wiper register to that wiper's WCR just by performing a 2-wire read operation. Simultaneously, that data byte can be utilized by the host.

#### Status Register Organization

The Status Register (SR) is used in read and write operations to select the appropriate wiper register. Before any wiper register can be accessed, the SR must be set to the correct value. It is accessed by setting the Address Byte to 07h. See Table 3. Do this by writing the slave address followed by a byte address of 07h. The SR is volatile and defaults to 00h on power up. It is an 8-bit register containing three control bits in the 3 LSBs as follows:

| 7 | 6        | 5 | 4       | 3       | 2        | 1 | 0 |

|---|----------|---|---------|---------|----------|---|---|

|   | Reserved |   | WCRSel1 | WCRSel0 | NVEnable |   |   |

Bits WCRSel1 and WCRSel0 determine which Data Register of a wiper is selected for a given operation. NVEnable is used to select the volatile WCR if "0", and one of the non

volatile wiper registers if "1". Table 3 shows this register organization.

#### Wiper Addressing for 2-wire Interface

once the Lataneg sterney rhas been solected by a 2-wire instruction then he wiver is determined by the Address Byte of the following instruction. Note again that this enables a complete page write of all four potentiometers at once a particular Wiper Register has been chosen. The register addresses accessible in the X9455 include:

FN8202.1

July 28, 2006

FIGURE 6. STATUS REGISTER WRITE (USES STANDARD BYTE WRITE SEQUENCE TO SET UP ACCESS TO A DATA REGISTER)

**STOP**

TABLE 4. ADDRESSING FOR 2-WIRE INTERFACE ADDRESS BYTE

| ADDRESS (HEX) | CONTENTS        |

|---------------|-----------------|

| 0             | Wiper 0A        |

| 1             | Wiper 1B        |

| 2             | Wiper 1A        |

| 3             | Wiper 0B        |

| 4             | Not Used        |

| 5             | Not Used        |

| 6 \//         | Uct Usec        |

| 7             | Status Register |

All other address bits in the address byte must be set to "0" during 2-wire write operations and their value should be ignored when read.

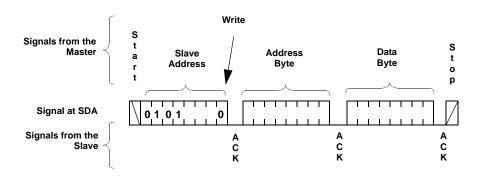

#### **Byte Write Operation**

For any Byte Write operation, the X9455 requires the Slave Address byte, an Address Byte, and a Data Byte (See Figure 7). After each of them, the X9455 responds with an ACK. The master then terminates the transfer by generating a STOP condition. At this time, if the write operation is to a volatile register (WCR, or SR), the X9455 is ready for the next read or write operation. If the write operation is to a nonvolatile register (DR), and the  $\overline{\text{WP}}$  pin is high, the X9455 begins the internal write cycle to the nonvolatile memory. During the internal nonvolatile write cycle, the X9455 does not respond to any requests from the master. The SDA output is at high impedance.

The SR bits and  $\overline{\text{WP}}$  pin determine the register being accessed through the 2-wire interface. See Table 2 on page 9

As noted before, any write operation to a Data Register (DR), also transfers the contents of all the data registers in that row to their corresponding WCR.

For example, to write 3Ahex to the Level 1 Data Register of wiper 1A (DR1A1) the following sequence is required:

|   | START                 |                  |                                             |

|---|-----------------------|------------------|---------------------------------------------|

|   | Slave Address         | 0101 0000        | (Hardware Address = 000,                    |

|   | ACK                   |                  | and a Write command)                        |

|   | Address Byte          | 0000 0111        | (Indicates Status Register                  |

|   | ACK                   |                  | address)                                    |

|   | Data Byte             | 0000 0011        | (Data Register Level 1 and                  |

|   | ACK                   |                  | NVEnable selected)                          |

|   | (note: at this ACK, t | he WCRs are all  | updated with their                          |

|   | respective DR.)       |                  |                                             |

|   | STOP,                 |                  |                                             |

| ١ | 19fler                | $t \triangle r $ | (Ha dwa e address = 000,<br>Write co.nmand) |

| J | Slave Address         | 0107 0000        | Write co.nmand)                             |

|   | ACK                   | 0101 0000        | (Access Wiper 1A)                           |

|   | Address Byte          | 0000 0010        | (Access Wiper TA)                           |

|   | ACK                   | 0000 0010        | /// '' D : D : 041)                         |

|   | Data Byte             | 0011 1010        | (Write Data Byte 3Ah)                       |

|   | ACK                   | 0011 1010        |                                             |

|   | AOIN                  |                  |                                             |

During the sequence of this example,  $\overline{WP}$  pin must be high, and A0, A1, and A2 pins must be low. When completed, the DR1A1 register and the WCR1A of Wiper 1A will be set to 3Ah, and the other data registers in Row 1 will transfer their contents to the respective WCRs.

intersil FN8202.1 July 28, 2006

FIGURE 7. BYTE WRITE SEQUENCE

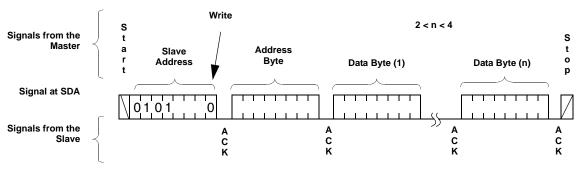

#### Page Write Operation

As stated previously, the memory is organized as a single Status Register (SR), and four pages of four registers each. Each page contains one Data Register for each wiper. Normally a page write operation will be used to efficiently update all four Data Registers and WCR in a single Write command. Note the special sequence for writing to a page: First wiper 0A, then 1B, then 1A, then 0B as shown in Figure 9.

| WCR        | WCR0A $\rightarrow$ WCR1B $\rightarrow$ WCR1A $\rightarrow$ WCR0B |

|------------|-------------------------------------------------------------------|

| DR Level 0 | $DR0A0 \rightarrow DR1B0 \rightarrow DR1A0 \rightarrow DR0B0$     |

| DR Level 1 | $DR0A1 \rightarrow DR1B1 \rightarrow DR1A1 \rightarrow DR0B1$     |

| DR Level 2 | DR442 → DR1B2 → DR142 → DR0B2                                     |

| DR Level 3 | DR0A3 → DR1B3 → DR1A3 → DR0B3                                     |

FIGURE 8. PAGE WRITE SEQUENCE\*

In order to perform a Page Write operation to the memory array, the NVEnable bit in the SR must first be set to "1".

A Page Write operation is initiated in the same manner as the Byte Write operation; but instead of terminating the write cycle after the first data byte is transferred, the master can transmit up to 4 bytes (See Figure 9). After the receipt of each byte, the X9455 responds with an ACK, and the internal WCR address is incremented by one. The page address remains constant. When the address reaches the end of the page, it "rolls over" and goes back to the first byte of the same page.

For example, if the master writes three bytes to a page starting at location DR1A2, the first two bytes are written to locations DR1A2 and DR0B2, while the last byte is written to location DR0A2. Afterwards, the WCR address would point to location DR1B2. If the master supplies more than four bytes of data, then new data overwrites the previous data, one byte at a time.

The master term nates the loading of Data Bytes by issuing a STOP condition, which initiates the nonvolatile write cycle. As with the Byte Write operation, all inputs are disabled until completion of the internal write cycle. If the WP pin is low, the nonvolatile write cycle doesn't start and the bytes are discarded.

Notice that the Data Bytes are also written to the WCR of the corresponding WCRs, therefore in the above example, WCR1A, WCR0B, and WCR0A are also written, and WCR1B is updated with the contents of DR1B2.

FIGURE 9. PAGE WRITE OPERATION

<sup>\*</sup>Page writes may wrap around to the first address on a page from the last address.

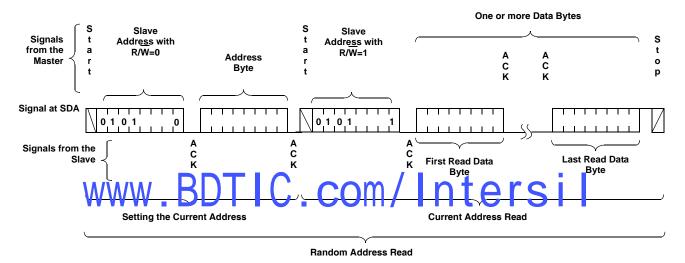

#### Move/Read Operation

The Move/Read operation simultaneously reads the contents of a data register and moves the contents into the corresponding DCP's WCR and all wipers will have their WCR's updated with the data register values from the row that was read. Move/Read operation consists of a one byte, or three byte instruction followed by one or more Data Bytes (See Figure 10). To read an arbitrary byte, the master initiates the operation issuing the following sequence: a START, the Slave Address byte with the R/W bit set to "0", an Address Byte, a second START, and a second Slave Address byte with the R/W bit set to "1". After each of the three bytes, the X9455 responds with an ACK. Then the X9455 transmits Data Bytes as long as the master responds

with an ACK during the SCL cycle following the eighth bit of each byte. The master terminates the Move/Read operation (issuing a STOP condition) following the last bit of the last Data Byte.

The first byte being read is determined by the current wiper address and by the Status Register bits, according to Table 1 on page 11. If more than one byte is read, the WCR address is incremented by one after each byte, in the same way as during a Page Write operation. After reaching WCR0B, the WCR address "rolls over" to WCR0A.

On power up, the Address pointer is set to the Data Register 0 of WCR0A.

FIGURE 10. MOVE/READ SEQUENCE

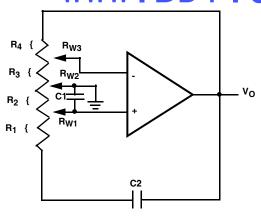

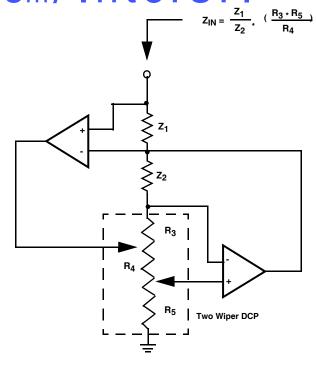

# Applications information

# **Basic Configurations of Electronic Potentiometers**

Four terminal Potentiometer; Variable voltage divider

Four-Wiper DCP

# **Application Circuits**

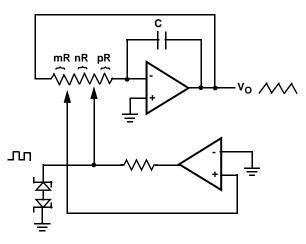

#### **FUNCTION GENERATOR**

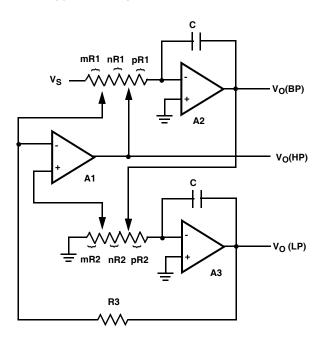

#### PROGRAMMABLE STATE VARIABLE FILTER

#### PROGRAMMABLE LADDER NETWORKS

# WIEN BRIDGE OSCILLATOR BDT IC. COM/INTERS

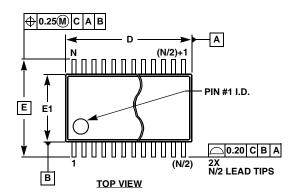

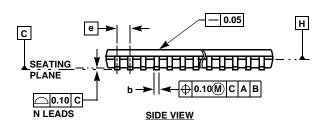

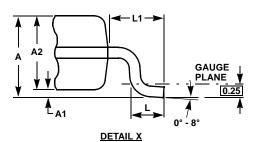

# Thin Shrink Small Outline Package Family (TSSOP)

#### **MDP0044** THIN SHRINK SMALL OUTLINE PACKAGE FAMILY

| SYMBOL | 14 LD | 16 LD | 20 LD | 24 LD | 28 LD | TOLERANCE   |

|--------|-------|-------|-------|-------|-------|-------------|

| Α      | 1.20  | 1.20  | 1.20  | 1.20  | 1.20  | Max         |

| A1     | 0.10  | 0.10  | 0.10  | 0.10  | 0.10  | ±0.05       |

| A2     | 0.90  | 0.90  | 0.90  | 0.90  | 0.90  | ±0.05       |

| b      | 0.25  | 0.25  | 0.25  | 0.25  | 0.25  | +0.05/-0.06 |

| С      | 0.15  | 0.15  | 0.15  | 0.15  | 0.15  | +0.05/-0.06 |

| D      | 5.00  | 5.00  | 6.50  | 7.80  | 9.70  | ±0.10       |

| Е      | 6.40  | 6.40  | 6.40  | 6.40  | 6.40  | Basic       |

| E1     | 4.40  | 4.40  | 4.40  | 4.40  | 4.40  | ±0.10       |

| е      | 0.65  | 0.65  | 0.65  | 0.65  | 0.65  | Basic       |

| L      | 0.60  | 0.60  | 0.60  | 0.60  | 0.60  | ±0.15       |

| L1     | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | Reference   |

Rev. E 12/02

#### NOTES:

- 1. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

- 2. Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm per

- 3. Dimensions "D" and "E1" are measured at dAtum Plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

19

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com