### Data Sheet

### September 13, 2005

# FN9175.3

# Dual Output LNB Supply and Control Voltage Regulator with I<sup>2</sup>C Interface for Advanced Satellite Set-Top Box Designs

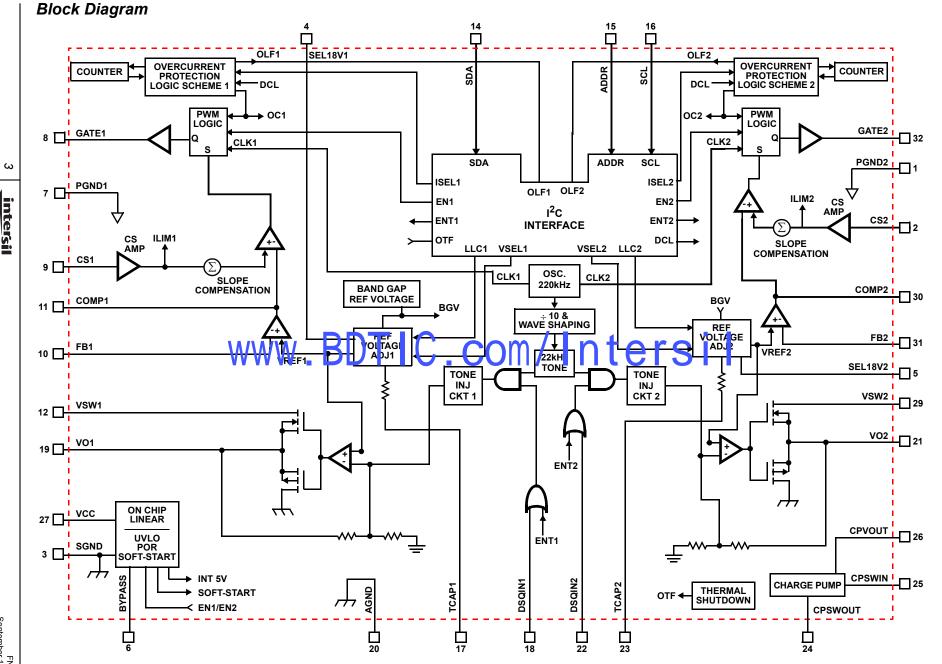

The ISL6424 is a highly integrated voltage regulator and interface IC, specifically designed for supplying power and control signals from advanced satellite set-top box (STB) modules to the low noise blocks (LNBs) of two antenna ports. The device is comprised of two independent current-mode boost PWMs and two low-noise linear regulators along with the circuitry required for 22kHz tone generation, modulation and  $I^2C$  device interface. The device makes the total LNB supply design simple, efficient and compact with low external component count.

Two independent current-mode boost converters provide the linear regulators with input voltages that are set to the final output voltages, plus typically 1.2V to insure minimum power dissipation across each linear regulator. This maintains constant voltage drops across each linear pass element while permitting adequate voltage range for tone injection.

The final regulated output voltages are available at two output terminals to support simultaneous operation of two antenna ports for dual tuners. The cutputs for eacl PVM are set to 13V or 18V ov independent voltage select commands (VSEL1, VSEL2) through the I<sup>2</sup>C bus. Additionally, to compensate for the voltage drop in the coaxial cable, the selected voltage may be increased by 1V with the line length compensation (LLC) feature. All the functions on this IC are controlled via the I<sup>2</sup>C bus by writing 8 bits on System Register (SR, 8 bits). The same register can be read back, and two bits will report the diagnostic status. Separate enable commands sent on the I<sup>2</sup>C bus provide independent standby mode control for each PWM and linear combination, disabling the output into shutdown mode.

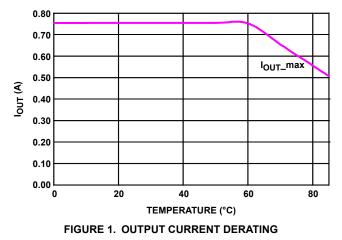

Each output channel is capable of providing 750mA of continuous current. The overcurrent limit can be digitally programmed. The SEL18V pin allows the 13V to 18V transition with an external pin, overriding the  $I^2C$  input.

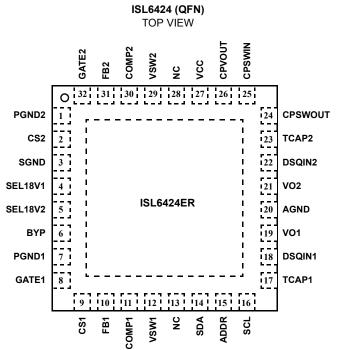

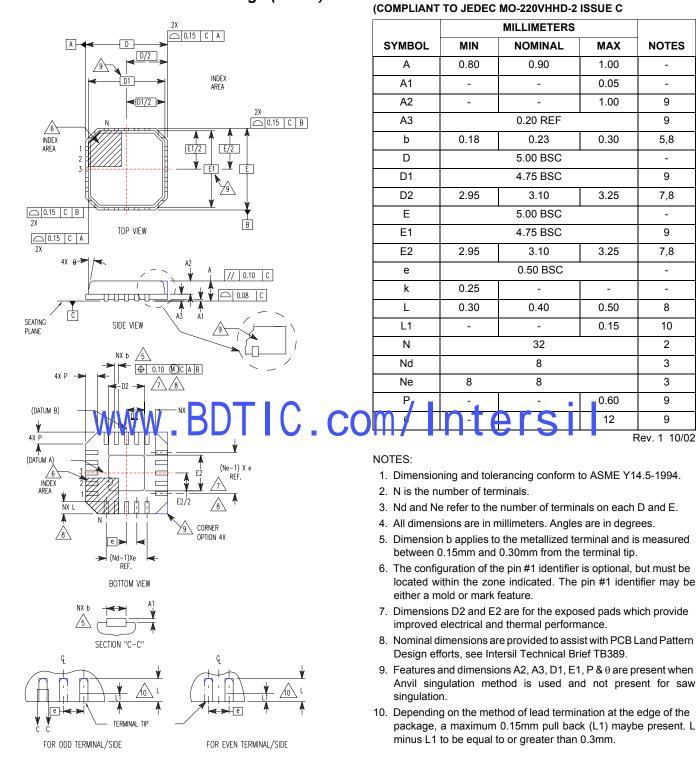

The ISL6424 is offered in a 32 Ld 5x5 QFN.

# Features

- Single Chip Power Solution

- True Dual Operation for 2-Tuner/2-Dish Applications

- Both Outputs May be Enabled Simultaneously at Maximum Power

- Integrated DC-DC Converter and I<sup>2</sup>C Interface

- Switch-Mode Power Converter for Lowest Dissipation

- Boost PWMs with > 92% Efficiency

- Selectable 13V or 18V Outputs

- Digital Cable Length Compensation (1V)

- I<sup>2</sup>C Compatible Interface for Remote Device Control

Registered Slave Address 0001 00XX

- Full 3.3V/5V Operation up to 400kHz

- External Pins to Select 13V/18V Option

- DSQIN1&2 and SEL18V1&2 pins 2.5V Logic Compatible

- Built-In Tone Oscillator Factory Trimmed to 22kHz

Facilitates DiSEqC (EUTELSAT) Encoding

- Internal Over-Temperature Protection and Diagnostics

- Internal Overload and Overtemp Flags (Visible on I<sup>2</sup>C)

- · LNB Short-Circuit Protection and Diagnostics

- QFN,Package

COmpliant JEDEO PUBSOMC-220 QFN - Quad Flat No Le ads - Product Ou line

- Near Chip-Scale Package Footprint

- Pb-Free Plus Anneal Available (RoHS Compliant)

# Applications

LNB Power Supply and Control for Satellite Set-Top Box

# References

Tech Brief 389 (TB389) - "PCB Land Pattern Design and Surface Mount Guidelines for QFN Packages"; Available on the Intersil website, www.intersil.com

# **Ordering Information**

| PART # *          | PART<br>MARKING | TEMP.<br>(°C) | PACKAGE                    | PKG.<br>DWG. # |

|-------------------|-----------------|---------------|----------------------------|----------------|

| ISL6424ER         | ISL6424ER       | -20 to 85     | 32 Ld 5x5 QFN              | L32.5x5        |

| ISL6424ERZ (Note) | ISL6424ERZ      | -20 to 85     | 32 Ld 5x5 QFN<br>(Pb-free) | L32.5x5        |

\*Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# www.BDTIC.com/Intersil

ISL6424

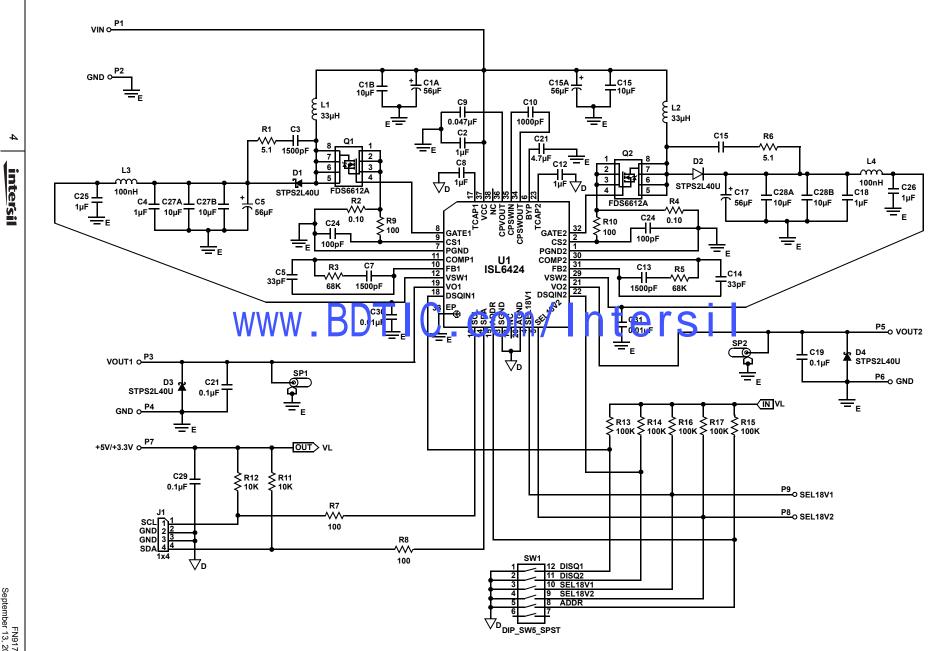

### **Typical Application Schematic**

### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>CC</sub>        | 8.0V to 18.0V |

|----------------------------------------|---------------|

| Logic Input Voltage Range              |               |

| (SDA, SCL, ENT, DSQIN 1&2, SEL18V 1&2) | 0.5V to 7V    |

### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|------------------------|------------------------|

| QFN Package                              | 32                     | 4                      |

| Maximum Junction Temperature (Note 3)    |                        | 150°C                  |

| Maximum Storage Temperature Range        | 4                      | 0°C to 150°C           |

| Maximum Lead Temperature (Soldering 1)   | 0s)                    | 300°C                  |

| Operating Temperature Range              |                        | 20°C to 85°C           |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 3. The device junction temperature should be kept below 150°C. Thermal shut-down circuitry turns off the device if junction temperature exceeds +150°C typically.

| Electrical Specifications | $V_{CC}$ = 12V, $T_A$ = -20°C to +85°C, unless otherwise noted. Typical values are at $T_A$ = 25°C. EN1 = EN2 = H, |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|

|                           | LLC1 = LLC2 = L, ENT1 = ENT2 = L, DCL = L, DSQIN1 = DSQIN2 = L, lout = 12mA, unless otherwise noted.               |

|                           | See software description section for $I^2C$ access to the system.                                                  |

| PARAMETER                            | SYMBOL            | TEST CONDITIONS                                                       | MIN   | TYP      | MAX   | UNITS  |

|--------------------------------------|-------------------|-----------------------------------------------------------------------|-------|----------|-------|--------|

| Operating Supply Voltage Range       |                   |                                                                       | 8     | 12       | 14    | V      |

| Standby Supply Current               |                   | EN1 = EN2 = L                                                         | -     | 1.5      | 3.0   | mA     |

| Supply Current                       | I <sub>IN</sub>   | EN1 = EN2 = LLC1 = LLC2 = VSEL1 =<br>VSEL2 = ENT1 = ENT2 = H, No Load | -     | 4.0      | 8.0   | mA     |

| UNDERVOLTAGE LOCKOUT                 |                   | •                                                                     |       |          |       |        |

| Start Threshold                      |                   |                                                                       | 7.5   | <u> </u> | 7.95  | V      |

| Stop Threshold                       | דענ               |                                                                       | 70    | 51       | 7.55  | V      |

| Start to Stop Hysteresis             |                   |                                                                       | 350   | 400      | 500   | mV     |

| SOFT-START                           |                   | •                                                                     |       | •        | •     |        |

| COMP Rise Time (Note 4)              |                   | (Note 5)                                                              | -     | 512      | -     | Cycles |

| Output Voltage (Note 5)              | V <sub>O1</sub>   | VSEL1 = L, LLC1 = L                                                   | 12.74 | 13.0     | 13.26 | V      |

|                                      | V <sub>O1</sub>   | VSEL1 = L, LLC1 = H                                                   | 13.72 | 14.0     | 14.28 | V      |

|                                      | V <sub>O1</sub>   | VSEL1 = H, LLC1 = L                                                   | 17.64 | 18.0     | 18.36 | V      |

|                                      | V <sub>O1</sub>   | VSEL1 = H, LLC1 = H                                                   | 18.62 | 19.0     | 19.38 | V      |

|                                      | V <sub>O2</sub>   | VSEL2 = L, LLC2 = L                                                   | 12.74 | 13.0     | 13.26 | V      |

|                                      | V <sub>O2</sub>   | VSEL2 = L, LLC2 = H                                                   | 13.72 | 14.0     | 14.28 | V      |

|                                      | V <sub>O2</sub>   | VSEL2 = H, LLC2 = L                                                   | 17.64 | 18.0     | 18.36 | V      |

|                                      | V <sub>O2</sub>   | VSEL2 = H, LLC2 = H                                                   | 18.62 | 19.0     | 19.38 | V      |

| Line Regulation                      | DV <sub>O1,</sub> | V <sub>IN</sub> = 8V to 14V; V <sub>O1</sub> , V <sub>O2</sub> = 13V  | -     | 4.0      | 40.0  | mV     |

|                                      | DV <sub>O2</sub>  | V <sub>IN</sub> = 8V to 14V; V <sub>O1</sub> , V <sub>O2</sub> = 18V  | -     | 4.0      | 60.0  | mV     |

| Load Regulation                      | DV <sub>O1,</sub> | I <sub>O</sub> = 12mA to 350mA                                        | -     | 50       | 80    | mV     |

|                                      | DV <sub>O2</sub>  | I <sub>O</sub> = 12mA to 750mA (Note 6)                               | -     | 100      | 200   | mV     |

| Dynamic Output Current Limiting      | IMAX              | DCL = L, ISEL1/2 = L                                                  | 425   | -        | 550   | mA     |

|                                      |                   | DCL = L, ISEL1/2 = H (Note 6)                                         | 775   | 850      | 950   | mA     |

| Dynamic Overload Protection Off Time | TOFF              | DCL = L, Output Shorted (Note 6)                                      | -     | 900      | -     | ms     |

| Dynamic Overload Protection On Time  | TON               | ]                                                                     | -     | 20       | -     | ms     |

# **Electrical Specifications**

$V_{CC}$  = 12V,  $T_A$  = -20°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C. EN1 = EN2 = H, LLC1 = LLC2 = L, ENT1 = ENT2 = L, DCL = L, DSQIN1 = DSQIN2 = L, lout = 12mA, unless otherwise noted. See software description section for I<sup>2</sup>C access to the system. **(Continued)**

| PARAMETER                       | SYMBOL                          | TEST CONDITIONS                   | MIN      | TYP      | MAX  | UNITS |

|---------------------------------|---------------------------------|-----------------------------------|----------|----------|------|-------|

| 22kHz TONE SECTION              |                                 |                                   |          |          |      |       |

| Tone Frequency                  | f <sub>tone</sub>               | ENT1/2 = H                        | 20.0     | 22.0     | 24.0 | kHz   |

| Tone Amplitude                  | V <sub>tone</sub>               | ENT1/2 = H                        | 500      | 680      | 800  | mV    |

| Tone Duty Cycle                 | dc <sub>tone</sub>              | ENT1/2 = H                        | 40       | 50       | 60   | %     |

| Tone Rise or Fall Time          | T <sub>r</sub> , T <sub>f</sub> | ENT1/2 = H                        | 5        | 8        | 14   | μs    |

| LINEAR REGULATOR                |                                 |                                   |          |          |      |       |

| Drop-out Voltage                |                                 | lout = 750mA (Note 6)             | -        | 1.2      | -    | V     |

| DSQIN PIN 1&2, SEL18V 1&2 INPUT | PINs (Note 11)                  | )                                 |          |          |      |       |

| Asserted LOW                    |                                 |                                   | -        | -        | 0.8  | V     |

| Asserted HIGH                   |                                 |                                   | 1.7      | -        | -    | V     |

| Input Current                   |                                 |                                   | -        | 1        | -    | μΑ    |

| CURRENT SENSE                   |                                 |                                   |          |          |      |       |

| Input Bias Current              | I <sub>BIAS</sub>               |                                   | -        | 700      | -    | nA    |

| Over Current Threshold          |                                 | Static current mode, DCL = H      | 325      | 400      | 500  | mV    |

| ERROR AMPLIFIER                 |                                 |                                   |          |          |      |       |

| Open Loop Voltage Gain          | A <sub>OL</sub>                 | (Note 6)                          | 70       | 88       | -    | dB    |

| Gain Bandwidth Product          | GBP                             | (Note 6)                          | 10       | -        | -    | MHz   |

| PWM                             | DNT                             |                                   | <b>C</b> | <u> </u> |      |       |

| Maximum Duty Cyle VV            | דעם                             |                                   | <u> </u> | 3        | -    | %     |

| Minimum Pulse Width             |                                 | (Note 6)                          | -        | 20       | -    | ns    |

| OSCILLATOR                      |                                 |                                   |          |          |      |       |

| Oscillator Frequency            | f <sub>o</sub>                  | Fixed at (10)(f <sub>tone</sub> ) | 200      | 220      | 240  | kHz   |

| THERMAL SHUTDOWN                |                                 |                                   |          |          |      |       |

| Temperature Shutdown Threshold  |                                 | (Note 6)                          | -        | 150      | -    |       |

| Temperature Shutdown Hysteresis |                                 | (Note 6)                          | -        | 20       | -    |       |

NOTES:

4. Internal digital soft-start.

VO1 for LNB1, VO2 for LNB2. Voltage programming signals VSEL1, VSEL2, LLC1, and LLC2 are implemented via the I<sup>2</sup>C bus. IO1 = IO2 = 350mA/750mA.

6. Guaranteed by design.

7. Unused DSQIN 1&2 pins should be connected to GND. SEL18V1&2 pins have 200K internal pulldown resistors.

# **Typical Performance Curves**

NOTE: With both channels in simultaneous operation at rated output

# Functional Pin Description

| SYMBOL                        | FUNCTION                                                                                                                                                                                                                  |   |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| SDA                           | Bidirectional data from/to I <sup>2</sup> C bus.                                                                                                                                                                          |   |

| SCL                           | Clock from I <sup>2</sup> C bus.                                                                                                                                                                                          |   |

| VSW1, 2                       | Input of the linear post-regulator.                                                                                                                                                                                       |   |

| PGND1, 2                      | Dedicated ground for the output gate driver of respective PWM.                                                                                                                                                            |   |

| CS1, 2                        | Current sense input; coni ect Rsc at his r n for<br>desired/over current valu i for respective I W 1.                                                                                                                     | ( |

| SGND                          | Small signal ground for the IC.                                                                                                                                                                                           |   |

| AGND                          | Analog ground for the IC.                                                                                                                                                                                                 |   |

| TCAP1, 2                      | Capacitor for setting rise and fall time of the output of LNB A and LNB B respectively. Use this capacitor value 1µF or higher.                                                                                           |   |

| BYPASS                        | Bypass capacitor for internal 5V.                                                                                                                                                                                         |   |

| DSQIN1, 2                     | When HIGH enables internal 22kHz modulation for LNB A and LNA B respectively, Use this pin for tone enable function for LNB A and LNB B.                                                                                  |   |

| VCC                           | Main power supply to the chip.                                                                                                                                                                                            |   |

| GATE1, 2                      | These are the device outputs of PWM A and PWM B respectively. These high current driver outputs are capable of driving the gate of a power FET. These outputs are actively held low when Vcc is below the UVLO threshold. | - |

| VO1, 2                        | Output voltage of LNB A and LNB B respectively.                                                                                                                                                                           |   |

| ADDR                          | Address pin to select two different addresses per voltage level at this pin.                                                                                                                                              |   |

| COMP1, 2                      | Error amp outputs used for compensation.                                                                                                                                                                                  |   |

| FB1, 2                        | Feedback pins for respective PWMs                                                                                                                                                                                         |   |

| CPVOUT,<br>CPSWIN,<br>CPSWOUT | Charge pump connections.                                                                                                                                                                                                  |   |

| SEL18V1, 2                    | When connected HIGH, this pin will change the output of the respective PWM to 18V.                                                                                                                                        |   |

# **Functional Description**

The ISL6424 dual output voltage regulator makes an ideal choice for advanced satellite set-top box and personal video recorder applications. Both supply and control voltage outputs for two low-noise blocks (LNBs) are available simultaneously in any output configuration. The device utilizes built-in DC/DC step-converters that, from a single supply source ranging from 8V to 14V, generate the voltages that enable the linear post-regulators to work with a m n m un c f d ss pa ed power. An uncervoltage lockout circuit disables the circuit when VCC drops below a fixed threshold (7.5V typ).

# DiSEqC Encoding

The internal oscillator is factory-trimmed to provide a tone of 22kHz in accordance with DiSEqC (EUTELSAT) standards. No further adjustment is required. The 22kHz oscillator can be controlled either by the I<sup>2</sup>C interface (ENT1/2 bit) or by a dedicated pin (DSQIN1/2) that allows immediate DiSEqC data encoding separately for each LNB. (Please see Note 1 at the end of this section.) All the functions of this IC are controlled via the I<sup>2</sup>C bus by writing to the system registers (SR1, SR2). The same registers can be read back, and two bits will report the diagnostic status. The internal oscillator operates the converters at ten times the tone frequency. The device offers full I<sup>2</sup>C compatible functionality, 3.3V or 5V, and up to 400kHz operation.

If the Tone Enable (ENT1/2) bit is set LOW through I<sup>2</sup>C, then the DSQIN1/2 terminal activates the internal tone signal, modulating the dc output with a 0.3V, 22kHz, symmetrical waveform. The presence of this signal usually gives the LNB information about the band to be received.

Burst coding of the 22kHz tone can be accomplished due to the fast response of the DSQIN1/2 input and rapid tone response. This allows implementation of the DiSEqC (EUTELSAT) protocols. When the ENT1/2 bit is set HIGH, a continuous 22kHz tone is generated regardless of the DSQIN1/2 pin logic status for the corresponding regulator channel (LNB-A or LNB-B). The ENT1/2 bit must be set LOW when the DSQIN1 and/or DSQIN2 pin is used for DiSEqC encoding.

### Linear Regulator

The output linear regulator will sink and source current. This feature allows full modulation capability into capacitive loads as high as  $0.25\mu$ F. In order to minimize the power dissipation, the output voltage of the internal step-up converter is adjusted to allow the linear regulator to work at minimum dropout.

When the device is put in the shutdown mode (EN1, EN2 = LOW), both PWM power blocks are disabled. (i.e. when EN1 = 0, PWM1 is disabled, and when EN2 = 0, PWM2 is disabled).

When the regulator blocks are active (EN1, EN2 = HIGH), the output can be logic controlled to be 13V or 18V (typical) by means of the VSEL bit (Voltage Select) for remote controlling of non-DiSEqC LNBs. Additionally, it is possible to increment by 1V (typical) the selected voltage value to compensate for the excess voltage drop along the coaxial cable (LLC1/2 bit HIGH).

### **Output Timing**

The programmed output voltage rise and fall times can be set by an external capacitor. The output rise and fall times will be approximately 1400 times the TCAP value. For the recommended range of  $0.47\mu$ F to  $2.2\mu$ F, the rise and fall time would be 1.6ms to 7.6ms. Using a  $0.47\mu$ F capacitor insures the PWM stays below its overcurrent threshold when charging a  $120\mu$ F VSW filter cap during the worst case 13V to 19V transition. A typical value of  $1.0\mu$ F is recommended. This feature only affects the turn-on and programmed voltage rise and fall times.

# **Current Limiting**

The current limiting block has two thresholds that can be selected by the ISEL bit of the SR and can work either statically (simple current clamp) or dynamically. The lower threshold is between 425mA and 550mA (ISEL = L), while the higher threshold is between 775mA and 950mA (ISEL = H). When the DCL (Dynamic Current Limiting) bit is set to LOW, the overcurrent protection circuit works dynamically: as soon as an overload is detected, the output is shutdown for a time t<sub>OFF</sub>, typically 900ms. Simultaneously the OLF bit of the System Register is set to HIGH. After this time has elapsed, the output is resumed for a time  $t_{ON}$  = 20ms. During t<sub>ON</sub>, the device output will be current limited to 425mA min. or 775mA min., depending on the ISEL bits. At the end of  $t_{ON}$ , if the overload is still detected, the protection circuit will cycle again through t<sub>OFF</sub> and t<sub>ON</sub>. At the end of a full t<sub>ON</sub> in which no overload is detected, normal operation is resumed and the OLF bit is reset to LOW. Typical tON + tOFF time is 920ms as determined by an internal timer. This

8

dynamic operation can greatly reduce the power dissipation in a short circuit condition, still ensuring excellent power-on start-up in most conditions.

However, there could be some cases in which a highly capacitive load on the output may cause a difficult start-up when the dynamic protection is chosen. This can be solved by initiating any power start-up in static mode (DCL = HIGH) and then switching to the dynamic mode (DCL = LOW) after a chosen amount of time. When in static mode, the OLF1/2 bit goes HIGH when the current limit threshold at the CS pin reaches 0.45V typ and returns LOW when the overload condition is cleared. The OLF1/2 bit will be LOW at the end of initial power-on soft-start.

### **Thermal Protection**

This IC is protected against overheating. When the junction temperature exceeds 150°C (typical), the step-up converter and the linear regulator are shut off and the OTF bit of the SR is set HIGH. Normal operation is resumed and the OTF bit is reset LOW when the junction is cooled down to 135°C (typical).

In over temperature conditions, the OTF Flag goes HIGH and the I<sup>2</sup>C data will be cleared. The user may need to monitor the I<sup>2</sup>C enable bits and OTF flag continuously and enable the chip, if I<sup>2</sup>C data is cleared. OTF conditions may also make the OLF flags go HIGH, when high capacitive loads are present or self-heating conditions occur at higher

# External Output Voltage Selection

The output voltage can be selected by the I<sup>2</sup>C bus. Additionally, the package offers two pins (SEL18V1, SEL18V2) for independent 13V/18V output voltage selection. When using these pins, the I<sup>2</sup>C bits should be initialized to 13V status.

| IADLE 1.              |               |             |  |  |  |  |  |  |  |

|-----------------------|---------------|-------------|--|--|--|--|--|--|--|

| I <sup>2</sup> C BITS | SEL18V (1, 2) | O/P VOLTAGE |  |  |  |  |  |  |  |

| 13V                   | Low           | 13V         |  |  |  |  |  |  |  |

| 14V                   | Low           | 14V         |  |  |  |  |  |  |  |

| 13V                   | High          | 18V         |  |  |  |  |  |  |  |

| 14V                   | High          | 18V         |  |  |  |  |  |  |  |

# I<sup>2</sup>C Bus Interface for ISL6424

(Refer to Philips I<sup>2</sup>C Specification, Rev. 2.1)

Data transmission from main microprocessor to the ISL6424 and vice versa takes place through the two wire I<sup>2</sup>C bus interface, consisting of the two lines SDA and SCL. Both SDA and SCL are bidirectional lines, connected to a positive supply voltage via a pull up resistor. (Pull up resistors to positive supply voltage must be externally connected). When the bus is free, both lines are HIGH. The output stages of ISL6424 will have an open drain/open collector in order to perform the wired-AND function. Data on the I<sup>2</sup>C bus can be transferred up to 100Kbps in the standard-mode or up to 400Kbps in the fast-mode. The level of logic "0" and logic "1" is dependent of associated value of  $V_{DD}$  as per electrical specification table. One clock pulse is generated for each data bit transferred.

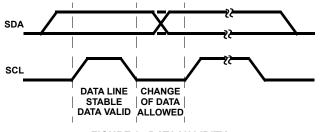

### Data Validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. Refer to Figure 2.

FIGURE 2. DATA VALIDITY

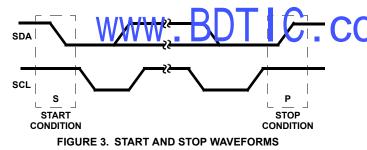

### START and STOP Conditions

As shown in Figure 3, START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH.

The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

### Byte Format

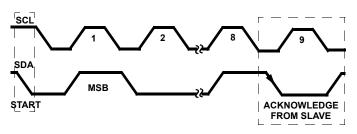

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit first (MSB).

### Acknowledge

The master (microprocessor) puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (Figure 4). The peripheral that acknowledges has to pull down (LOW) the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during this clock pulse. (Of course, set-up and hold times must also be taken into account.) The peripheral which has been addressed has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains at the HIGH level during the ninth clock pulse time. In this case, the master transmitter can generate the STOP information in order to abort the transfer. The ISL6424 will not generate the acknowledge if the POWER OK signal from the UVLO is LOW.

FIGURE 4. ACKNOWLEDGE ON THE I<sup>2</sup>C BUS

### Transmission Without Acknowledge

Avoiding detection of the acknowledgement, the microprocessor can use a simpler transmission; it waits one clock without checking the slave acknowledging, and sends the new data.

This approach, though, is less protected from error and decreases the noise immunity.

# ISL6424 Software Description

The interface Protocol is comprised of the following, as shown below in Table 2:

- · A start condition (S)

- A chip address byte (MSB on left; the LSB bit determines read (1) or write (0) transmission) (the assigned I<sup>2</sup>C slave address for the ISL6424 is 0001 00XX)

- A sequence of data (1 byte + Acknowledge)

- A stop condition (P)

### TABLE 2. INTERFACE PROTOCOL

| S | 0 | 0 | 0 | 1 | 0 | 0 | 0 | R/W | ACK | Data (8 bits) | ACK | Ρ |

|---|---|---|---|---|---|---|---|-----|-----|---------------|-----|---|

### System Register Format

- R, W = Read and Write bit

- R = Read-only bit

- All bits reset to 0 at Power-On

### TABLE 3. SYSTEM REGISTER 1 (SR1)

| R, W | R, W | R, W  | R, W | R, W | R, W  | R, W | R    |

|------|------|-------|------|------|-------|------|------|

| SR1  | DCL  | ISEL1 | ENT1 | LLC1 | VSEL1 | EN1  | OLF1 |

#### TABLE 4. SYSTEM REGISTER 2 (SR2)

|      |       |      |      | . ,   |      |     |      |

|------|-------|------|------|-------|------|-----|------|

| R, W | R, W  | R, W | R, W | R, W  | R, W | R   | R    |

| SR2  | ISEL2 | ENT2 | LLC2 | VSEL2 | EN2  | OTF | OLF2 |

### Transmitted Data (I<sup>2</sup>C bus WRITE mode)

When the R/W bit in the chip is set to 0, the main microprocessor can write on the system registers (SR1/SR2) of the ISL6424 via  $I^2C$  bus. These will be written by the

microprocessor as shown below. The spare bits of SR1/SR2 can be used for other functions.

| SR | DCL   | ISEL1           | ENT1 | LLC1  | VSEL1 | EN1 | OLF1 | FUNCTION                               |

|----|-------|-----------------|------|-------|-------|-----|------|----------------------------------------|

| 0  | Х     | Х               | Х    | 0     | 0     | Х   | Х    | SR1 is selected                        |

| 0  | Х     | Х               | Х    | 0     | 0     | 1   | Х    | Vout1 = 13V, Vboost1 = 13V + Vdrop     |

| 0  | Х     | Х               | Х    | 0     | 1     | 1   | Х    | Vout1 = 18V, Vboost1 = 18V + Vdrop     |

| 0  | Х     | Х               | Х    | 1     | 0     | 1   | Х    | Vout1 = 14V, Vboost1 = 14V + Vdrop     |

| 0  | Х     | <b>\/\{\</b> /\ | X    | RD    | 1     | 1   | CY)  | VDNt1 = 19 (, VDO)st = 19Y + VdrDD     |

| 0  | Х     | Х               | 0    | X     | Х     | 1   | X    | 22kHz tone is controlled by DSQIN1 pin |

| 0  | Х     | Х               | 1    | Х     | Х     | 1   | Х    | 22kHz tone is ON, DSQIN1 is disabled   |

| 0  | Х     | 0               | Х    | Х     | Х     | 1   | Х    | lout1 = 425mA max.                     |

| 0  | Х     | 1               | Х    | Х     | Х     | 1   | Х    | lout1 = 775mA max.                     |

| 0  | 1     | Х               | Х    | Х     | Х     | 1   | Х    | Dynamic current limit NOT selected     |

| 0  | 0     | Х               | Х    | Х     | Х     | 1   | Х    | Dynamic current limit selected         |

| 0  | Х     | Х               | Х    | Х     | Х     | 0   | Х    | PWM and Linear for channel 1 disabled  |

| SR | ISEL2 | ENT2            | LLC2 | VSEL2 | EN2   | OTF | OLF2 | FUNCTION                               |

| 1  | Х     | Х               | Х    | Х     | Х     | Х   | Х    | SR2 is selected                        |

| 1  | х     | Х               | 0    | 0     | 1     | Х   | Х    | Vout2 = 13V, Vboost2 = 13V + Vdrop     |

| 1  | х     | Х               | 0    | 1     | 1     | Х   | Х    | Vout2 = 18V, Vboost2 = 18V + Vdrop     |

| 1  | Х     | Х               | 1    | 0     | 1     | Х   | Х    | Vout2 = 14V, Vboost2 = 14V + Vdrop     |

| 1  | х     | Х               | 1    | 1     | 1     | Х   | Х    | Vout2 = 19V, Vboost2 = 19V + Vdrop     |

| 1  | Х     | 0               | Х    | Х     | 1     | Х   | Х    | 22kHz tone is controlled by DSQIN2 pin |

| 1  | Х     | 1               | Х    | Х     | 1     | Х   | Х    | 22kHz tone is ON, DSQIN2 is disabled   |

| 1  | 0     | Х               | Х    | Х     | 1     | Х   | Х    | lout2 = 425mA max.                     |

| 1  | 1     | Х               | Х    | Х     | 1     | Х   | Х    | lout2 = 775mA max.                     |

| 1  | х     | Х               | Х    | Х     | 0     | Х   | Х    | PWM and Linear for channel 2 disabled  |

### TABLE 5. SYSTEM REGISTER (SR1 AND SR2) CONFIGURATION

NOTE: OTF and OLF1&2 are "Read Only" bits and X is a "Don't Care" for the function specified.

# Received Data (I<sup>2</sup>C bus READ MODE)

The ISL6424 can provide to the master a copy of the system register information via the  $I^2C$  bus in read mode. The read mode is Master activated by sending the chip address with R/W bit set to 1. At the following Master generated clock bits, the ISL6424 issues a byte on the SDA data bus line (MSB transmitted first).

At the ninth clock bit the MCU master can:

- Acknowledge the reception, starting in this way the transmission of another byte from the ISL6424.

- Not acknowledge, stopping the read mode communication.

While the whole register is read back by the microprocessor, the read-only bits OLF1, OLF2, and OTF convey diagnostic information about the ISL6424.

### Power-On I<sup>2</sup>C Interface Reset

The  $I^2C$  interface built into the ISL6424 is automatically reset at power-on. The  $I^2C$  interface block will receive a Power OK logic signal from the UVLO circuit. This signal will go HIGH when chip power is OK. As long as this signal is LOW, the interface will not respond to any I<sup>2</sup>C commands and the system register SR1 and SR2 are initialized to all zeros, thus keeping the power blocks disabled. Once the Vcc rises above UVLO, the POWER OK signal given to the I<sup>2</sup>C interface block will be HIGH, the I<sup>2</sup>C interface becomes operative and the SRs can be configured by the main microprocessor. About 400mV of hysteresis is provided in the UVLO threshold to avoid false triggering of the Power-On reset circuit. (I<sup>2</sup>C comes up with EN = 0; EN goes HIGH at the same time as (or later than) all other I<sup>2</sup>C data for that PWM becomes valid).

### ADDRESS Pin

Connecting this pin to GND the chip  $I^2C$  interface address is 0001000, but, it is possible to choose between two different addresses simply by setting this pin at one of the two fixed voltage levels as shown in Table 8.

### TABLE 6. ADDRESS PIN CHARACTERISTICS

| V <sub>ADDR</sub>                 | MINIMUM | TYPICAL | MAXIMUM |

|-----------------------------------|---------|---------|---------|

| V <sub>ADDR</sub> -1<br>"0001000" | 0V      | -       | 2V      |

| V <sub>ADDR</sub> -2<br>"0001001" | 2.7V    | -       | 5V      |

| DCL ISEL1/2 ENT1/2 LLC12 VSET1/1 EN1/2                          | OTF2 | OLF1/2 |                                                        |

|-----------------------------------------------------------------|------|--------|--------------------------------------------------------|

| These bits are read as they were after the last write op ration |      | ЛП7    | T j ≤ 13 P°C nc mai operation                          |

|                                                                 |      |        | $T_J > 150^{\circ}C$ , power blocks disabled           |

|                                                                 |      | 0      | I <sub>OUT</sub> < I <sub>MAX</sub> , normal operation |

|                                                                 |      | 1      | $I_{OUT} > I_{MAX}$ , overload protection triggered    |

### TABLE 7. READING SYSTEM REGISTERS

# *I<sup>2</sup>C Electrical Characteristics*

### TABLE 8. I<sup>2</sup>C SPECIFICATIONS

| PARAMETER                | TEST CONDITION                             | MINIMUM | TYPICAL               | MAXIMUM |

|--------------------------|--------------------------------------------|---------|-----------------------|---------|

| Input Logic High, VIH    | SDA, SCL                                   |         | 0.7 x V <sub>DD</sub> |         |

| Input Logic Low, VIL     | SDA, SCL                                   |         | 0.3 x V <sub>DD</sub> |         |

| Input Logic Current, IIL | SDA, SCL;<br>0.4V < V <sub>IN</sub> < 4.5V |         |                       | 10μΑ    |

| SCL Clock Frequency      |                                            | 0       | 100kHz                | 400kHz  |

L32.5x5

32 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com