Data Sheet

# April 18, 2007

Two Independent 8-Tap FIR Filters Configurable as a

On-Board Storage for 32 Programmable Coefficient Sets

• Up To: 256 FIR Taps, 16x16 2-D Kernels, or 10x19-Bit

Pb-Free Plus Anneal Available (RoHS Compliant)

Features

Single 16-Tap FIR

· 10-Bit Data and Coefficients

Data and Coefficients

Applications

Image Processing

Polyphase Filtering

Adaptive Filtering

Programmable Decimation to 16

Programmable Rounding on Output

Standard Microprocessor Interface

Quadrature, Complex Filtering

com/Intersil

# **Dual FIR Filter**

intercil

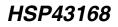

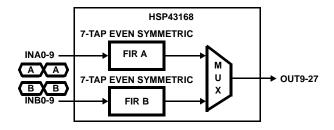

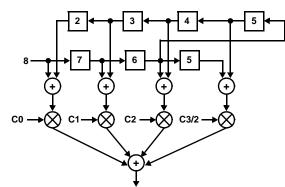

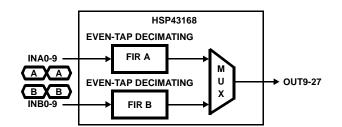

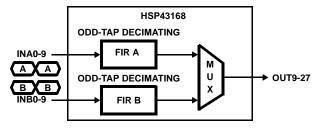

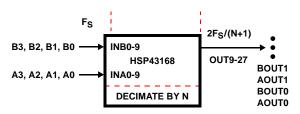

The HSP43168 Dual FIR Filter consists of two independent 8-tap FIR filters. Each filter supports decimation from 1 to 16 and provides on-board storage for 32 sets of coefficients. The Block Diagram shows two FIR cells each fed by a separate coefficient bank and one of two separate inputs. The outputs of the FIR cells are either summed or multiplexed by the MUX/Adder. The compute power in the FIR Cells can be configured to provide quadrature filtering, complex filtering, 2-D convolution, 1-D/2-D correlations, and interpolating/decimating filters.

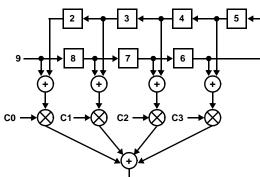

The FIR cells take advantage of symmetry in FIR coefficients by pre-adding data samples prior to multiplication. This allows an 8-tap FIR to be implemented using only 4 multipliers per filter cell. These cells can be configured as either a single 16-tap FIR filter or dual 8-tap FIR filters. Asymmetric filtering is also supported.

Decimation of up to 16 is provided to boost the effective number of filter taps from 2 to 16 times. Further, the Decimation Registers provide the delay necessary for fractional data conversion and 2-D filtering with kernels to 16x16.

The flexibility of the **Dual is further behanced by 32 sets** of user programmable coefficients. Coefficient selection of aybe changed asynchronously from clock to clock. The ability to toggle between coefficient sets further simplifies applications such as polyphase or adaptive filtering.

The HSP43168 is a low power fully static design implemented in an advanced CMOS process. The configuration of the device is controlled through a standard microprocessor interface.

# **Ordering Information**

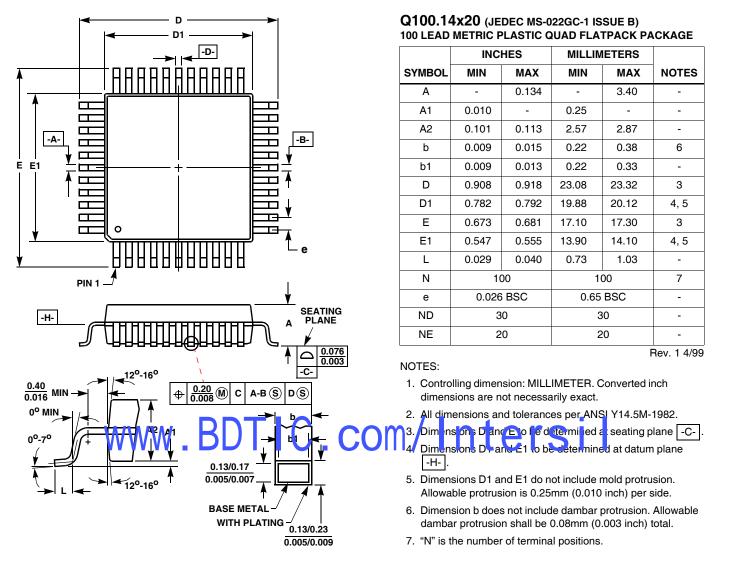

| PART NUMBER           | PART MARKING   | TEMP. RANGE (°C) | PACKAGE               | PKG.<br>DWG. # |

|-----------------------|----------------|------------------|-----------------------|----------------|

| HSP43168VC-45         | HSP43168VC-45  | 0 to +70         | 100 Ld MQFP           | Q100.14x20     |

| HSP43168VC-45Z (Note) | HSP43168VC-45Z | 0 to +70         | 100 Ld MQFP (Pb-free) | Q100.14x20     |

| HSP43168JC-33         | HSP43168JC-33  | 0 to +70         | 84 Ld PLCC            | N84.1.15       |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# Block Diagram

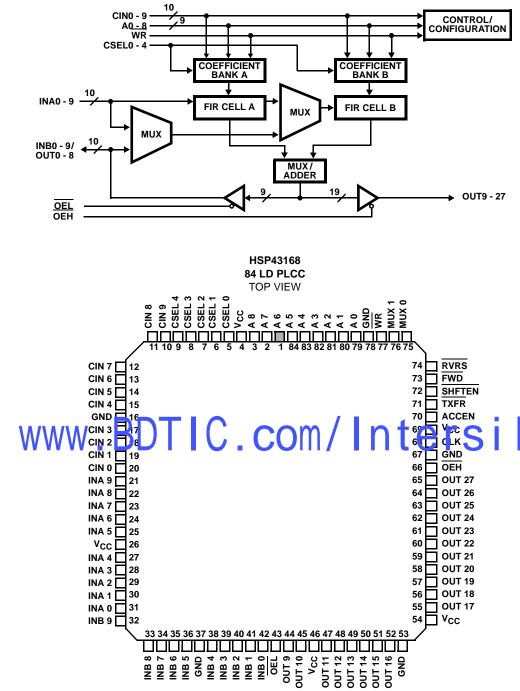

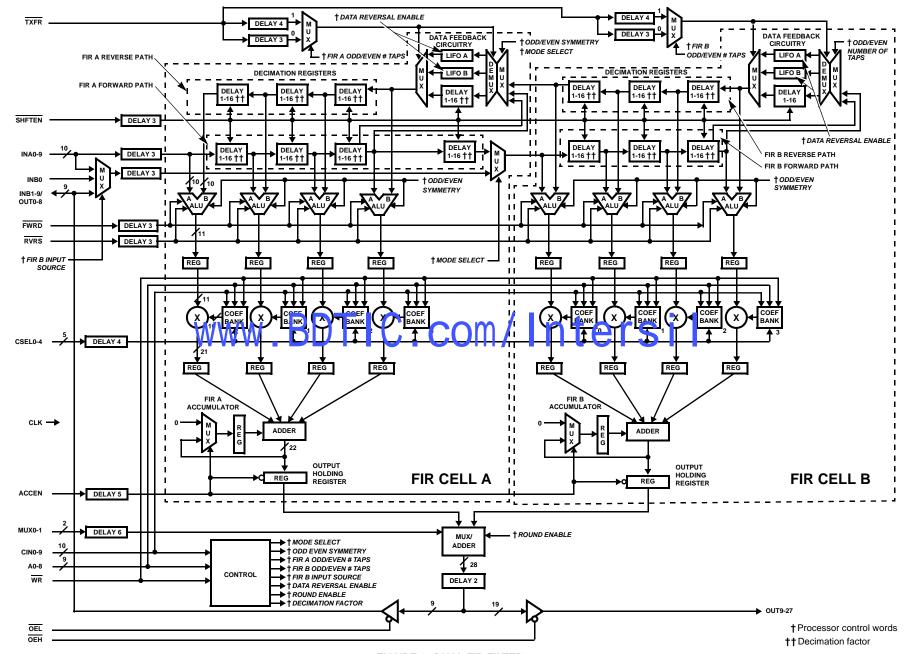

**Pinouts**

**Pinouts** (Continued)

# **Pin Description**

| SYMBOL          | TYPE | DESCRIPTION                                                                                                                                                                                                                               |

|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> |      | V <sub>CC</sub> : +5V power supply pin.                                                                                                                                                                                                   |

| GND             |      | Ground.                                                                                                                                                                                                                                   |

| CIN0-9          | I    | Control/Coefficient Data Bus. Processor interface for loading control data and coefficients. CIN0 is the LSB.                                                                                                                             |

| A0-8            | I    | Control/Coefficient Address Bus. Processor interface for addressing Control and Coefficient Registers. A0 is the LSB.                                                                                                                     |

| WR              | I    | Control/Coefficient Write Clock. Data is latched into the Control and Coefficient Registers on the rising edge of WR.                                                                                                                     |

| CSEL0-4         | I    | Coefficient Select. This input determines which of the 32 coefficient sets are to be used by FIR A and B. This inpu is registered and CSEL0 is the LSB.                                                                                   |

| INA0-9          | I    | Input to FIR A. INA0 is the LSB.                                                                                                                                                                                                          |

| INB0-9          | I/O  | Bidirectional Input for FIR B. INB0 is the LSB and is input only. When used as output, INB1-9 are the LSBs of the output bus, and INB9 is the MSB of these bits.                                                                          |

| OUT9-27         | 0    | 19 MSBs of Output Bus. Data format is either unsigned or two's complement depending on configuration. OUT27 is the MSB.                                                                                                                   |

| SHFTEN          | I    | Shift Enable. This active low input enables clocking of data into the part and shifting of data through the Decimation Registers.                                                                                                         |

| FWRD            | I    | Forward ALU Input Enable. When active low, data from the forward decimation path is input to the ALUs through the "a" input. When high, the "a" inputs to the ALUs are zeroed.                                                            |

| RVRS            | I    | Reverse ALU Input Enable. When active low, data from the reverse decimation path is input to the ALUs through the "b" input. When high, the "b" inputs to the ALUs are zeroed.                                                            |

| TXFR            | WWW  | Data Transier Control. This active Id winnut switcher the LIF Dit sing reacting the rove se discimation path with the LIF or being written from the forward decimation path (see Figure 1).                                               |

| MUX0-1          | I    | Adder/Mux Control. This input controls data flow through the output Adder/Mux. Table 5 lists the various configurations.                                                                                                                  |

| CLK             | I    | Clock. All inputs except those associated with the processor interface (CIN0-9, A0-8, $\overline{WR}$ ) and the output enable (OEL, $\overline{OEH}$ ) are registered by the rising edge of CLK.                                          |

| OEL             | I    | Output Enable Low. This three-state control enables the LSBs of the output bus to INB1-9 when OEL is low.                                                                                                                                 |

| OEH             | I    | Output Enable High. This three-state control enables OUT9-27 when OEH is low.                                                                                                                                                             |

| ACCEN           | I    | Accumulate Enable. This active high input allows accumulation in the FIR Cell Accumulator. A low on this input latches the FIR Accumulator contents into the Output Holding Registers while zeroing the feedback pass in the Accumulator. |

HSP43168

**FIGURE 1. DUAL FIR FILTER**

ч 5

intersil

# Functional Description

As shown in Figure 1, the HSP43168 consists of two 4-multiplier FIR filter cells which process 10-bit data and coefficients. The FIR cells can operate as two independent 8-tap FIR filters or two 4-tap asymmetric filters at maximum I/O rates. A single filter mode is provided which allows the FIR cells to operate as one 16-tap FIR filter or one 8-tap asymmetric filter. On board coefficient storage for up to 32 sets of 8 coefficients is provided. The coefficient sets are user selectable and are programmed through a microprocessor interface. Programmable decimation to 16 is also provided. By utilizing Decimation Registers together with the coefficient sets, polyphase filters are realizable which allow the user to trade data rate for filter taps. The MUX/Adder can be configured to either add or multiplex the outputs of the filter cells depending upon whether the cells are operating in single or dual filter mode. In addition, a shifter in the MUX/Adder is provided for implementation of filters with 10-bit data and 20-bit coefficients or vice versa.

# Preparing the Dual FIR for Operation

Two configuration steps are required to prepare the Dual FIR Filter for normal operation: 1) loading the Configuration Control Registers, and 2) loading the FIR Filter Coefficients.

Configuration Control Registers are loaded by placing the control register address on address lines A0-8, placing the configuration data on the configuration input nes CINO.9, and asserting the WR line (tollower b) a release of the assertion). This action creates a rising edge on the WR line, which clocks the address and configuration data into the part. The details of the "Load Configuration" process are outlined in "Microprocessor Interface" on page 6.

FIR Coefficients are loaded by placing the address of the Coefficient Data Bank on the address lines A0-8, placing the FIR 10-bit coefficient values on the configuration input lines CIN0-9 and then asserting the WR line (followed by a release of the assertion). This action creates a rising edge on the WR line, which clocks the FIR Coefficient Band address and FIR Coefficient data into the part. The details of the "Load FIR Coefficient" process are outlined in "Coefficient Bank" on page 8.

Both the Configuration Load and FIR Coefficient Load can be done as a sequence of asynchronous write commands to the Dual FIR Filter. Once these actions are complete, the part is ready for normal filter operation. The CLK, TXFR, FWRD, RVRS, ACCEN, and SHFTEN signals must be asserted in a manner determined by the application. MUX0-1 must meet the setup and hold times with respect to clock for proper filter operation. Details of the MUX1-0 control can be found in "Output MUX/Adder" on page 9. Details of the ACCEN control can be found in "FIR Cell Accumulator" on page 9. Bit locations for the various filter control/configuration signals can be found in "Input/Output Formats" on page 10.

6

The Dual FIR Filter has a "pipeline" delay of 8 CLK periods, once normal filtering operations begin. Five typical filtering operation examples are provided in "Application Examples" on page 10 as a guide to configuration and control of the Dual FIR Filter.

During normal filter operations, the location and duration of the TXFR signal assertions are determined by the filter configuration and operation mode. Once set, these signal parameters must be maintained during normal operation to ensure proper data alignment in the part. Once the part is reset, do not change TXFR unless you load the configuration again.

<u>NOTE</u>: The fixed or periodic relationship between the TXFR signal and CLK must be maintained for valid filter operation. This relationship can only change when CLK is halted and new configuration control words are loaded into the device.

# Microprocessor Interface

Control Block

The Dual FIR has a 20 pin write only microprocessor interface for loading data into the Control Block and Coefficient Banks. The interface consists of a 10-bit data bus (CIN0-9), a 9-bit address bus (A0-8), and a write input (WR) to latch the data into the on-board registers on a rising edge. The configuration control and coefficient data loading is asynchronous to CLK.

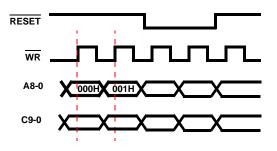

The Dual FIR is configured by writing to the registers within the Control Block. Figure 2 shows the timing diagram for writing to the Configuration Control Registers. These Control Registers are memory mapped to Address 000H (H = Hexadecimal) and 001H on A0-8. The Filter Coefficient Registers are mapped to 1XXH (X = value described in "Coefficient Bank" on page 8).

#### FIGURE 2. LATCHING C9-0 VALUES INTO ADDRESS A8-0 REGISTERS

The format of the Control Registers is shown in Table 1 and Table 2. Writing to any of the Control/Configuration Registers causes a reset which lasts for 6 CLK cycles following the assertion of  $\overline{WR}$ . The reset caused by Writing Registers in the Control Block will not clear the contents of the Coefficient Bank. As shown in Figure 2, either Configuration Control Register can be written to during reset.

#### TABLE 1. CONFIGURATION/CONTROL WORD 0 BIT DEFINITIONS

|      | CONTROL A                               | ADDRESS 000H                                                                         |

|------|-----------------------------------------|--------------------------------------------------------------------------------------|

| BITS | FUNCTION                                | DESCRIPTION                                                                          |

| 3-0  | Decimation Factor (N)                   | R = N + 1<br>0000 = No Decimation.<br>1111 = Decimation by 16.                       |

| 4    | Mode Select                             | 0 = Single Filter Mode.<br>1 = Dual Filter Mode.<br>(also 20-Bit Coefficient Filter) |

| 5    | Odd/Even Filter<br>Coefficient Symmetry | 0 = Even Symmetric Coefficients.<br>1 = Odd Symmetric Coefficients.                  |

| 6    | FIR A Odd/Even<br>Number of Taps        | 0 = Odd Number of Taps in Filter.<br>1 = Even Number of Taps in Filter.              |

| 7    | FIR B Odd/Even<br>Number of Taps        | (Defined Same as FIR A Above).                                                       |

| 8    | FIR B Input Source                      | 0 = Input from INA0-9.<br>1 = Input from INB0-9.                                     |

| 9    | Not Used                                | Set to 0 for Proper Operation.                                                       |

NOTE:

1. Address locations 002H to 011H are reserved, and writing to these locations will have unpredictable effects on part configuration.

# TABLE 2. CONFIGURATION/CONTROL WORD 1 BIT DEFINITIONS

|      | CONTROL ADI              | DRESS 001H                                                    |

|------|--------------------------|---------------------------------------------------------------|

| BITS | FUNCTION                 |                                                               |

| 0    | FIR A Input Found        | 0 = U signed.<br>1 = Two's Complement.                        |

| 1    | FIR A Coefficient Format | (Defined same as FIR A input).                                |

| 2    | FIR B Input Format       | (Defined same as FIR A input).                                |

| 3    | FIR B Coefficient        | (Defined same as FIR A input).                                |

| 4    | Data Reversal Enable     | 0 = Enabled.<br>1 = Disabled.                                 |

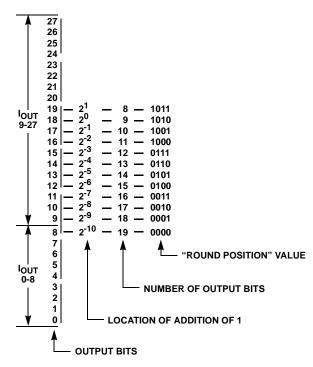

| 8-5  | Round Position           | $0000 = 2^{-10.}$<br>1011 = 2 <sup>1.</sup><br>(See Figure 4) |

| 9    | Round Enable             | 0 = Enabled.<br>1 = Disabled.                                 |

NOTE:

2. Address locations 002H to 011H are reserved, and writing to these locations will have unpredictable effects on part configuration.

The 4 LSBs of the control word loaded at address 000H are used to select the decimation factor. The Decimation Factor is programmed to one less than the number of delays between filter taps

DF = (CLK delays between taps) - 1 (EQ. 1)

For example, if the 4 LSBs are programmed with a value of 0010, the Forward and Reverse Shifting Decimation Registers are each configured with a delay of 3. Bit 4 is used to select whether the FIR cells operate as two independent filters or one extended length filter. Dual filter mode assumes Filter A

7

and Filter B are separate independent filters. In the single filter mode, the data is routed through the forward paths of Filters A and B before entering the reverse paths of Filters A and B (see Figure 1). Coefficient symmetry is selected by bit 5. Bits 6 and 7 are programmed to configure the FIR cells for odd or even filter lengths (number of taps). Bit 8 selects the FIR B input source when the FIR cells are configured for independent operation. Bit 9 must be programmed to 0. <u>NOTE:</u> When the filter is programmed for even-taps, the TXFR signal is delayed by only three CLKS (see Figure 1). For odd-taps, the TXFR signal is delayed by four CLKS.

The 4 LSBs of the control word loaded at address 001H are used to configure the format of the FIR cell's data and coefficients. Bit 4 is programmed to enable or disable the reversal of data sample order prior to entering the Reverse Path Decimation Registers. Data reversal is required for symmetric filter coefficient sets of both even or odd numbers of filter taps. Asymmetric filters and some decimated symmetric filters require the data reversal to be off. Bits 5-9 are used to support programmable rounding on the output.

# FIR Filter Cells

Each FIR filter cell is based on an array of four 11x10-bit two's complement multipliers. One input of the multipliers comes from the ALU's which combine data shifting through the Forward and Reverse Decimation Registers. The second multiplier input comes from the user programmable coefficient bank. The nultiplier outputs are ed to an a ccumulator whose lesult is passed to the output section where it is multiplexed or added with the result from the other FIR cell.

# **Decimation Registers**

The Forward and Reverse Decimation Shift Registers can be configured for decimation factors from 1 to 16 (see Table 1, bits 0-3). **NOTE: Setting the decimation factor only affects the Delay Registers between filter taps, not the filter control multiplexers.** Example 4 and Example 5 in "Application Examples" on page 10 discuss how to configure the part for actual decimation applications.

The Reverse Shifting Registers with the data reversal logic are used to take advantage of symmetry in linear phase filters by aligning data at the ALUs for pre-addition prior to multiplication by the common coefficient. When the FIR cells are configured in single filter mode, the Decimation Registers in FIR cell A and FIR cell B are cascaded. This extended filter tap delay path allows computation of a filter which is twice the size of that capable using a single cell. The Decimation Registers also provide data storage for polyphase or 2-D filtering applications (See "Application Examples" on page 10).

The Data Feedback Circuitry in each FIR cell is responsible for transferring data from the Forward to the Reverse Shifting Decimation Registers. This circuitry feeds blocks of samples into the reverse shifting decimation path in either reversed or non-reversed sample order. The MUX/DEMUX structure at the input to the Feedback Circuitry routes data to the LIFOs or the delay stage depending on the selected configuration. The MUX on the Feedback Circuitry Output selects which storage element feeds the Reverse Shifting Decimation Registers.

In applications requiring reversal of sample order, the FIR cells are configured with data reversal enabled (see Table 2, CW5, bit 4 = 0). In this mode, data is transferred from the forward to the backward Shifting Registers through a pingponged LIFO structure. While one LIFO is being read into the backward shifting path, the other LIFO is written with data samples. The MUX/DEMUX controls which LIFO is being read. A low on TXFR and SHIFTEN, switches the LIFOs being read and written, which causes the block of data to be read from the structure in reversed in sample order (See Example 4 in "Application Examples" on page 10).

The frequency with which TXFR is asserted determines size of the data blocks in which sample order is reversed. For example, if TXFR is asserted once every three CLKs, blocks of 3 data samples with order reversed, would be fed into the Backward Decimation Registers. **NOTE:** Altering the frequency or phase of TXFR assertion once a filtering operation has begun will invalidate the filtering result.

In applications which dongt require a mple order reversal, the FIR cells must be configured vitte data rever al disabled (see Table 2, CW5, bit 4 = 1). In addition, TXFR must be asserted to ensure proper data flow. In this configuration, data to the backward shifting decimation path is routed though a delay stage instead of the pingpong LIFOs. The number of registers in the delay stage is based on the programmed decimation factor. **NOTE: Data reversal must be disabled and TXFR must be asserted for filtering applications which do not use decimation**.

The shifting of data through the Forward and Reverse Decimation Registers is enabled by asserting the SHFTEN input. When SHFTEN is high, data shifting is disabled, and the data sample latched into the part on the previous clock is the last input to the filter structure. The data sample at the filter input when SHFTEN is asserted, will be the next data sample into the forward decimation path.

When operating the FIR cells as two independent filters, FIR A receives input data via INA0-9 and FIR B receives data from either INA0-9 or INB0-9 depending on the application (see Table 1).

When the FIR cells are configured as a single extended length filter, the forward and reverse decimation paths of the two FIR cells are cascaded. In this mode, data is transferred from the forward decimation path to the reverse decimation path by the Data Feedback Circuitry in FIR B. Thus, the manner in which data is read into the reverse decimation

8

path is determined by FIR B's configuration. When the decimation paths are cascaded, data is routed through the fourth delay stage in FIR A's forward path to FIR B.

The configuration of the FIR cells as even or odd length filters determines the point in the forward decimation path from which data is multiplexed to the Data Feedback Circuitry. For example, if the FIR cell is configured as an odd length filter, data prior to the last register in the third forward decimation stage is routed to the Feedback Circuitry. If the FIR cell is configured as an even length filter, data output from the third forward decimation stage is multiplexed to ensure proper data alignment with symmetric filter coefficients (See "Application Examples" on page 10).

# ALUs

Data shifting through the forward and reverse decimation paths feed the "a" and "b" inputs of the ALUs respectively. The ALUs perform an "b+a" operation if the FIR cell is configured for even symmetric coefficients or an "b-a" operation if configured for odd symmetric coefficients. Control Word 0, Bit 5 is used to set the ALU operation.

For applications in which a pre-add or subtract is not required, the "a" or "b" input can be zeroed by disabling FWRD or RVRS respectively. This has the effect of producing an ALU output which is either "a", "-a", or "b" depending on the filter symmetry hosen. For example, if the FIR bell is configured to an ever symmetric mer with FWRD low and RVRS high, the data shifting through the Forward Decimation Registers would appear on the ALU output.

Table 3 details the ALU configurations, where "a" is the ALU data input from the front decimation delay registers and "b" is the ALU data from the back decimation delay registers.

| ALU<br>OUT | SYMMETRY | FWD | RVS | DESCRIPTION                                       |

|------------|----------|-----|-----|---------------------------------------------------|

| a+b        | 0 (Even) | 0   | 0   | Even Number of Taps, Even<br>Symmetry (Example 1) |

| +b         | 0 (Even) | 0   | 1   | Even Symmetry                                     |

| +a         | 0 (Even) | 1   | 0   | Even Symmetry                                     |

| -          | 0 (Even) | 1   | 1   | Even Symmetry                                     |

| b-a        | 1 (Odd)  | 0   | 0   | Even Number of Taps, Odd<br>Symmetry (Example 2)  |

| +b         | 1 (Odd)  | 0   | 1   | Odd Symmetry                                      |

| -a         | 1 (Odd)  | 1   | 0   | Odd Symmetry                                      |

| -          | 1 (Odd)  | 1   | 1   | Odd Symmetry                                      |

TABLE 3. ALU CONFIGURATIONS

# **Coefficient Bank**

The output of the ALU is multiplied by a coefficient from one of 32 user programmable coefficient sets. Each set consists of 8 coefficients (4 coefficients for FIR A and 4 for FIR B). CSEL0-4 is used to select a coefficient set to be used.

Coefficient sets may be switched every clock to support polyphase filtering operations.

The coefficients are loaded into On-Board Registers using the microprocessor interface, CIN0-9, A0-8, and WR. Each multiplier within the FIR Cells is driven by a coefficient bank with one of 32 coefficients. These coefficients are addressed as shown in Table 4. The inputs A0-1 specify the Coefficient Bank for one of the four multipliers in each FIR Cell; A2 specifies FIR Cell A or B; Bits A7-3 specify one of 32 sets in which the coefficient is to be stored. For example, an address of 10dH would access the coefficient for the second multiplier in FIR B in the second coefficient set.

| FIR<br>COEFF | CSEL (4-0)<br>COEFF.<br>SET | CELL<br>A/B | MULTIPLIER | DESTINATION |      |  |

|--------------|-----------------------------|-------------|------------|-------------|------|--|

| A8           | A7-3                        | A2          | A1-0       | FIR         | BANK |  |

| 1            | XXXX X                      | 0           | 00         | А           | 0    |  |

| 1            | XXXX X                      | 0           | 01         | А           | 1    |  |

| 1            | XXXX X                      | 0           | 10         | А           | 2    |  |

| 1            | XXXX X                      | 0           | 11         | А           | 3    |  |

| 1            | XXXX X                      | 1           | 00         | В           | 0    |  |

| 1            | XXXX X                      | 1           | 01         | В           | 1    |  |

| 1            | XXXX X                      | 1           | 10         | В           | 2    |  |

| 1            | XXXX X                      | 1           | 11         | В           | 3    |  |

### TABLE 4. FIR COEFFICIENT WRITE ADDRESSES

# **Output MUX/Adder**

The contents of each FIR Cell's Output Holding Register is summed or multiplexed in the Mux/Adder. The operation of the Mux/Adder is controlled by the MUX1-0 inputs as shown in Table 5. Applications requiring 10-bit data and 20-bit coefficients or 20-bit data and 10-bit coefficients are made possible by configuring the MUX/Adder to scale FIR B's output by 2<sup>-10</sup> prior to summing with FIR A. When the Dual FIR is configured as two independent filters, the MUX1-0 inputs would be used to multiplex the filter outputs of each cell. For applications in which FIR A and B are configured as a single filter, the MUX/Adder is configured to sum the output of each FIR cell.

NOTE: While a 20-bit coefficient filter is a single filter, the mode select is set to 1 and MUX1-0 is set to 00.

|        | MUX1-0 DECODING                                 |  |  |  |  |  |  |  |  |

|--------|-------------------------------------------------|--|--|--|--|--|--|--|--|

| MUX1-0 | OUT0-27                                         |  |  |  |  |  |  |  |  |

| 00     | FIRA + FIRB (FIR B Scaled by 2 <sup>-10</sup> ) |  |  |  |  |  |  |  |  |

| 01     | FIRA + FIRB                                     |  |  |  |  |  |  |  |  |

| 10     | FIRA                                            |  |  |  |  |  |  |  |  |

| 11     | FIRB                                            |  |  |  |  |  |  |  |  |

# FIR Cell Accumulator BDT C COM/ Intersi

feed an accumulator. The ACCEN input controls each accumulator's running sum and the latching of data from the accumulator into the Output Holding Registers. When ACCEN is low, feedback from the accumulator adder is zeroed which disables accumulation. Also, output from the accumulator is latched into the Output Holding Registers. When ACCEN is asserted, accumulation is enabled and the contents of the Output Holding Registers remain unchanged.

# Input/Output Formats

The Dual FIR supports mixed mode arithmetic with both unsigned and two's complement data and coefficients. The input and output formats for both data types are shown below. If the Dual FIR is configured as an even symmetric filter with unsigned data and coefficients, the output will be unsigned. Otherwise, the output will be two's complement.

The MUX/Adder can be configured to implement programmable rounding at bit locations 2-10 through 21. The round is implemented by adding a 1 to the specified location (see Table 2). Figure 4 illustrates the rounding operation. For example, to configure the part such that the output is rounded to the 10 MSBs, OUT18 - 27, the round position would be chosen to be 2-1. The negative sign on the MSB indicates 2's complement format.

> INPUT DATA FORMAT INA0-9, INB0-9 FRACTIONAL TWO'S COMPLEMENT

| 9               | 8                | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| -2 <sup>0</sup> | .2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

OUTPUT DATA FORMAT OUT9-27 FRACTIONAL TWO'S COMPLEMENT

| 27              | 26             | 25             | 24             | 23             | 22             | 21             | 20             | 19             | 18             | 17   | 16  | 15  | 14  | 13              | 12              | 11  | 10              | 9               |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------|-----|-----|-----|-----------------|-----------------|-----|-----------------|-----------------|

| -2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | .2-1 | 2-2 | 2-3 | 2-4 | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2-7 | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

|                  | (<br>FF          | DUTPL<br>RAUTO   | T DA T           | A FOF            |                  | <b>)U 10-</b><br>Le ие | }<br>\T          | С                | . ( |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------------|------------------|------------------|-----|

| 8                | 7                | 6                | 5                | 4                | 3                | 2                      | 1                | 0                |     |

| 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup>       | 2 <sup>-17</sup> | 2 <sup>-18</sup> |     |

INPUT DATA FORMAT INA0-9, INB0-9 FRACTIONAL UNSIGNED

| 9              | 8                | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 2 <sup>0</sup> | .2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

#### OUTPUT DATA FORMAT OUT9-27 FRACTIONAL UNSIGNED

| 27             | 26             | 25             | 24             | 23             | 22             | 21             | 20             | 19             | 18             | 17               | 16              | 15              | 14              | 13              | 12              | 11              | 10              | 9               |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | .2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2 <sup>-9</sup> |

OUTPUT DATA FORMAT OUT0-8 FRACTIONAL UNSIGNED

| 8                | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 2 <sup>-10</sup> | 2 <sup>-11</sup> | 2 <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> | 2 <sup>-18</sup> |

FIGURE 3. INPUT/OUTPUT FORMAT DEFINITIONS

FIGURE 4. ROUND POSITION BIT DEFINITION

# Application Examples

In this section a number of examples are presented which detail even odd, symmetric, asymmetric, decimating and heal F.R filler confit unitions. These champles are intended to illustrate the different operational features of the HSP43168 and should be used as a guide in developing an application specific filter configuration. Use Table 6 to select and find the example that best matches your application.

| TABLE 6. | FILTER | EXAMPLE | SELECTION | GUIDE |

|----------|--------|---------|-----------|-------|

| FILTER TYPE             | EXAMPLE NUMBER |

|-------------------------|----------------|

| Even Tap Even Symmetric | 1              |

| Odd Tap Even Symmetric  | 2              |

| Asymmetric              | 3              |

| Even Tap Decimating     | 4              |

| Odd Tap Decimating      | 5              |

| Dual Decimating         | 6              |

Examples 1 through 5 are explained using a single four tap FIR cell, but the same concept applies to FIR filters which use both FIR cells (A and B) in a single filter configuration. Example 6 details a dual filter mode where FIR cell A and B implement different digital filters. All examples are functionally verified configurations. Each example details a complete design solution, including a block diagram, a data/coefficient alignment illustration, a data flow diagram and a control signal timing diagram.

Two programmable Configuration Control Registers define a unique FIR filter configuration. Register 000H has all filter

configuration unique parameters, while Register 001H, bit 4, is filter configuration unique. Table 7 details the configuration control register values, the number of filter coefficient banks required and the MUX1-0 control values for each filter example.

| FILTER TYPE                               | REG<br>000<br>HEX | REG<br>001<br>HEX | # OF FILTER<br>COEFFICIENT<br>BANKS | MUX<br>1-0   |  |  |  |  |  |

|-------------------------------------------|-------------------|-------------------|-------------------------------------|--------------|--|--|--|--|--|

| Even Tap Even<br>Symmetric                | 1d0               | 010               | 1                                   | 10           |  |  |  |  |  |

| Odd Tap Even Symmetric                    | 110               | 010               | 1                                   | 10           |  |  |  |  |  |

| Asymmetric                                | 110               | 010               | 2                                   | 10           |  |  |  |  |  |

| Even Tap Decimate by N+1                  | 1dN               | 000               | N+1                                 | 10           |  |  |  |  |  |

| Odd Tap Decimate by N+1                   | 11N               | 000               | N+1                                 | 10           |  |  |  |  |  |

| Dual: Even and Odd Tap<br>Decimate by N+1 | 15N or<br>19N     | 000<br>▲<br>Bit 4 | N+1                                 | 10 and<br>11 |  |  |  |  |  |

#### TABLE 7. CONFIGURATION CONTROL REGISTER VALUES

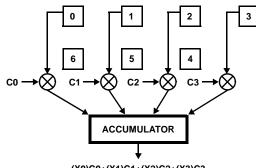

# Example 1. Even-Tap Even Symmetric Filter Example

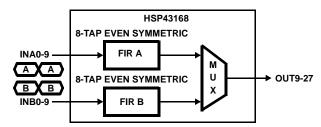

The HSP43168 may be configured as two independent 8-tap symmetric filters as shown by the Block Diagram in Figure 5. Each of the FIR cells takes advantage of symmetric filter coefficients by pre-adding data samples common to a given coefficient. As a result, each FIR cell can implement an 8 tap symmetric filter using or y our multipliers. Similarly, when he HSP43163 is configured in single filter mode a 16-tap symmetric filter is possible by using the multipliers in both cells.

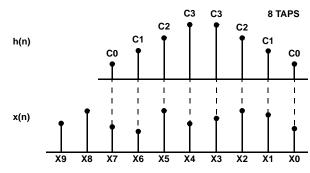

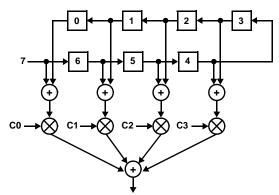

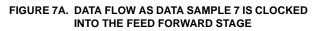

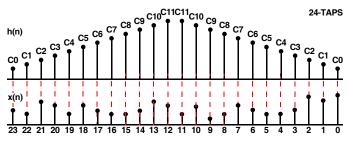

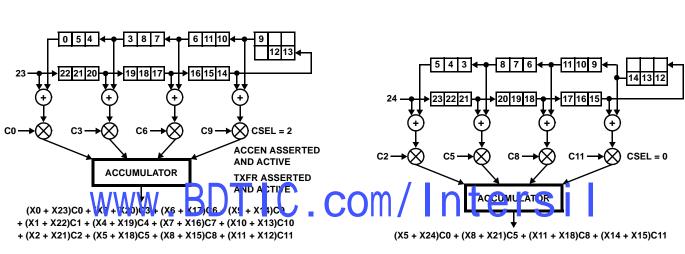

The operation of the FIR cell is better understood by comparing the data and coefficient alignment for a given filter output, Figure 6, with the data flow through the FIR cell, as shown in Figure 7. The Block Diagrams in Figure 7 are a simplification of the FIR cell shown in Figure 1. For simplicity, the ALUs and FIR Cell Accumulators were replaced by adders, and the Pipeline Delay Registers were omitted. In this example, we will only show the data flow through one of the two FIR cells.

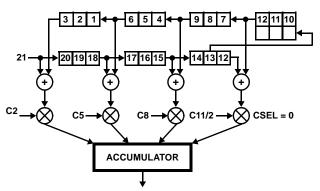

In Figure 7, the order of the data samples within the filter cell is shown by the numbers in the forward and backward shifting decimation paths. The output of the filter cell is given by the equation at the bottom of each block diagram. Figure 7A shows the data sample alignment at the preadders for the data/coefficient alignment shown in Figure 6.

#### FIGURE 6. DATA/COEFFICIENT ALIGNMENT FOR 8-TAP EVEN SYMMETRIC FILTER

The dual filter application is configured by writing 1d0H to address 000H via the microprocessor interface, CIN0-9, A0-8, and  $\overline{WR}$ . Since this application does not use decimation, the 4th bit of the Control Register at Address 001H must be set to disable data reversal (see Table 2). Failure to disable data reversal will produce erroneous results.

Using this architecture, only the unique coefficients need to be stored in the Coefficient Bank. For example, the above filter would be stored in the first coefficient set for FIR A by writing C0, C1, C2, and C3 to Address 100H, 101H, 102H, and 103H respectively. To write the same filter to the first coefficient set for FIR B, the address sequence would change to 104H, 105H, 106H, and 107H.

To operate the HSP43168 in this mode,  $\overrightarrow{T}$  FR is tied low to prove proper data low Poth FV/RD and VRS are tied low to enable data samples from the forward and reverse data paths to the ALUs for pre-adding; ACCEN is tied low to prevent accumulation over multiple CLKs; SHFTEN is tied low to allow shifting of data through the Decimation Registers; MUX0-1 is programmed to multiplex the output the of either FIR A or FIR B; CSEL0-4 is programmable to access the stored coefficient set, in this example CSEL = 00000.

(X7 + X0)C0 + (X6 + X1)C1 + (X5 + X2)C2 + (X4 + X3)C3

(X8 + X1)C0 + (X7 + X2)C1 + (X6+X3)C2 + (X5 + X4)C3

#### FIGURE 7B. DATA FLOW AS DATA SAMPLE 8 IS CLOCKED INTO THE FEED FORWARD STAGE

(X9 + X2)C

FIGURE 7C. DA

Filter Example

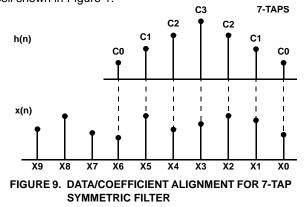

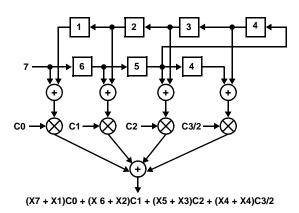

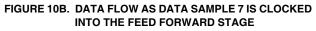

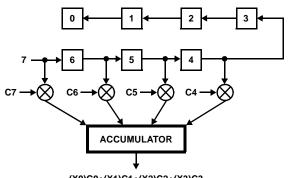

The operation of the FIR cell for odd length filters is better understood by comparing the data/coefficient alignment in Figure 9 with the Data Flow Diagrams in Figure 10. The Block Diagrams in Figure 10 are a simplification of the FIR cell shown in Figure 1.

For odd length filters, proper data/coefficient alignment is ensured by routing data entering the last register in the third forward decimation stage to the Backward Shifting Registers. In this configuration, the center coefficient must be scaled by 1/2 to compensate for the summation of the same data sample from both the Forward and Backward Shifting Registers.

The HSP43168 may be configured as two independent 7-tap symmetric filters with a Functional Block Diagram shown in Figure 8. Again, this example shows data flow through one of the two FIR cells. As in the 8-tap filter example, the HSP43168 implements the filtering operation by summing data samples sharing a common coefficient prior to multiplication by that coefficient. However, for odd length filters the pre-addition requires that the center coefficient be scaled by 1/2.

FIGURE 8. USING HSP43168 AS TWO INDEPENDENT FILTERS

12

(X6 + X0)C0 + (X5 + X1)C1 + (X4 + X2)C2 + (X3 + X3)C3/2

FIGURE 10A. DATA FLOW AS DATA SAMPLE 6 IS CLOCKED INTO THE FEED FORWARD STAGE

int<u>ersi</u>l

(X8+X2)C0+(X7+X3)C1+(X6+X4)C2+(X5+X5)C3/2

#### FIGURE 10C. DATA FLOW AS DATA SAMPLE 8 IS CLOCKED INTO THE FEED FORWARD STAGE FIGURE 10. DATA FLOW DIAGRAMS FOR 7-TAP SYMMETRIC FILTER

In the Data Flow Diagrams of Figure 10, the order of the data samples input in to the filter cell is shown by the numbers in the forward and backward shifting decimation paths. The output of the filter cell is given by the equation at the bottom of the block. The diagram in Figure 10A shows data sample alignment at the pre-adders for the Data/Coefficient Alignment shown in Figure 9.

This dual filter application is configured by writing 110H to Address 000H via the microprocessor interface, CIN0-9, A0-8, and WR. Also, data reversal must be disabled by setting bit 4 of the Control Register at Address C001 H. As n the 8 (ap example, only the unique coefficients need to be stored in the Coefficient Bank. These coefficients are stored in the first coefficient set for FIR A by writing C0, C1, C2, and C3 to Address 100H, 101H, 102H, and 103H respectively. To write the same filter to the first coefficient set for FIR B, the address sequence would change to 104H, 105H, 106H, and 107H. The control signals TXFR, FWRD, RVRS, ACCEN, SHFTEN, and CSEL0-4 are controlled as described in Example 1.

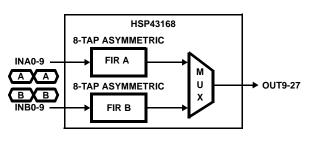

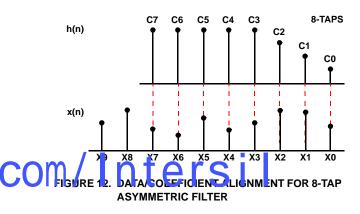

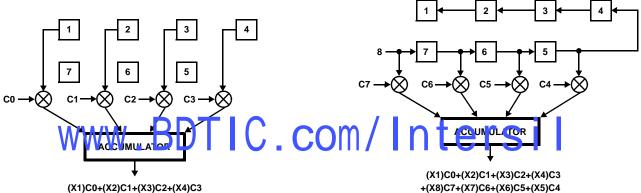

# Example 3. Asymmetric Filter Example

The FIR cells within the HSP43168 can each calculate 4 asymmetric taps on each clock. Thus, a single FIR cell can implement an 8-tap asymmetric filter if the HSP43168 is clocked at twice the input data rate. Similarly, if the Dual is configured as a single filter, a 16-tap asymmetric filter is realizable. Only one of the two FIR cells are used in this example for the Block Diagram shown in Figure 11.

For this example, the FIR cells are configured as two 8-tap asymmetric filters which are clocked at twice the input data rate. New data is shifted into the forward and backward decimation paths every other CLK by the assertion of SHFTEN. The filter output is computed by passing data from each decimation path to the multipliers on alternating clocks. Two sets of coefficients are required, one for data on the forward decimation path, and one for data on the reverse path. The filter output is generated by accumulating the multiplier outputs for two CLKs.

#### FIGURE 11. USING HSP43168 AS TWO INDEPENDENT FILTERS

The operation of this configuration is better understood by comparing the Data/Coefficient Alignment in Figure 12 with the Data Flow Diagrams in Figure 13. The ALUs have been omitted from the FIR cell diagrams because data is fed to the multipliers directly from the forward and reverse decimation paths. The data samples within the FIR cell are shown by the numbers in the decimation paths.

(X0)C0+(X1)C1+(X2)C2+(X3)C3

(X0)C0+(X1)C1+(X2)C2+(X3)C3 +(X7)C7+(X6)C6+(X5)C5+(X4)C4

FIGURE 13B. SHIFTING OF DATA SAMPLE 7 INTO FIR CELL ENABLED, FORWARD SHIFTING REGISTERS FEEDING MULTIPLIERS

FIGURE 13C. DATA SHIFTING DISABLED, BACKWARD SHIFTING DECIMATION REGISTERS FEEDING MULTIPLIERS +(X8)C7+(X7)C6+(X6)C5+(X5)C4

FIGURE 13D. SHIFTING OF DATA SAMPLE 8 INTO FIR CELL ENABLED, FORWARD SHIFTING REGISTERS FEEDING MULTIPLIERS

### FIGURE 13. DATA FLOW DIAGRAMS FOR 8-TAP ASYMMETRIC FILTER

For this application, each filter cell is configured as an odd length filter by writing 110H to the Control Register at Address 000H. Even though an even tap filter is being implemented, the filter cells must be configured as odd length to ensure proper data flow. In addition, the filters must be set to even symmetry. Also, the 4th bit at Control Address 001H must be set to disable data reversal, and TXFR must be tied low. Since an 8-tap asymmetric filter is being implemented, two sets of coefficients must be stored. These eight coefficients could be loaded into the first two coefficient sets for FIR A by writing C0, C1, C2, C3, C7, C6, C5, and C4 to address 100H, 101H, 102H, 103H, 108H, 109H, 10aH, and 10bH respectively.

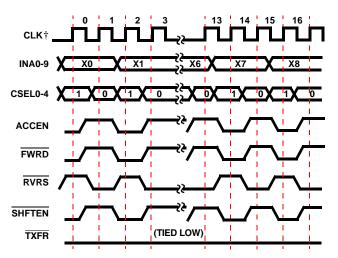

The sum of products required for this 8-tap filter require dynamic control over FWRD, RVRS, ACCEN, and CSEL0-4. The relative timing of these signals is shown in Figure 14.

†Note that CLK is 2X data rate.

FIGURE 14. CONTROL TIMING FOR 8-TAP ASYMMETRIC FILTER

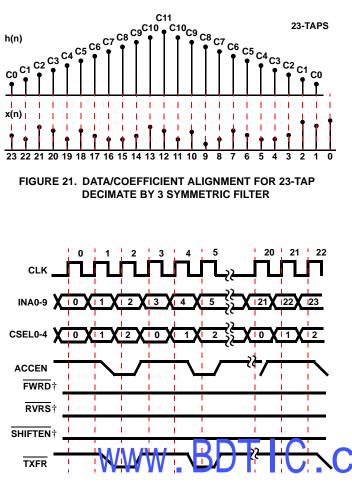

#### Example 4. Even-Tap Decimating Filter Example

The HSP43168 supports filtering applications requiring decimation to 16. In these applications the output data rate is reduced by a factor of N. As a result, N clock cycles can be used for the computation of the filter output. For example, each FIR cell can calculate 8 symmetric or 4 asymmetric taps in one clock. If the application requires decimation by two, the filter output can be calculated over two clocks thus, boosting the number ontable per FIR cell to 10 symmetric or 8 asymmetric. For this example, each FIR cell is consigured as an independent 24-tap decimate x3 filter. Again, the data flow diagrams show only one of the FIR cells shown in Figure 15.

FIGURE 15. EVEN-TAP DECIMATING FILTER, 24-TAP DEC = 3

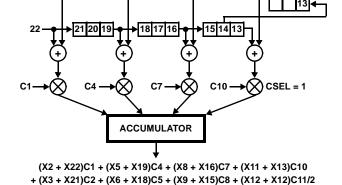

The alignment of data relative to the 24 filter coefficients for a particular output is depicted graphically in Figure 16. As in previous examples, the HSP43168 implements the filtering operation by summing data samples prior to multiplication by the common coefficient. In this example an output is required every third CLK which allows 3 CLKs for computation. On each CLK, one of three sets of coefficients are used to calculate 8 of the filter taps. The Block Diagrams in Figure 17 show the data flow and accumulator output for the data/coefficient alignment in Figure 16.

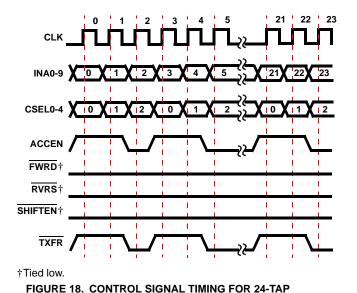

Proper data and coefficient alignment is achieved by asserting TXFR once every three CLKs to switch the LIFOs which are being read and written. This has the effect of feeding blocks of three samples into the backward shifting decimation path which are reversed in sample order. In addition, ACCEN is deasserted once every three clocks to allow accumulation over three CLKs. The three sets of coefficients required in the calculation of a 24-tap symmetric filter are cycled through using CSEL0-4. The timing relationship between the CSEL0-4, ACCEN, and TXFR are shown in Figure 18.

To operate in this mode the Dual is configured by writing 1d2 to Address 000H via the microprocessor interface, CIN0-9, A0-8, and WR. Data reversal must be enabled see (Table 2). The 12 unique coefficients for this example are stored as three sets of coefficients for either FIR cell. For FIR A, the coefficient are loaded into the Coefficient Bank by writing C2, C5, C4, C11 C1, C4, C7, C40 C), C3, C6, and C9 to Address [100H, 101H, 102H, 103H], CSEL = 0; [108H, 109H, 10aH, 10bH], CSEL = 1; [110H, 111H, 112H, and 113H], CSEL = 2, respectively.

FIGURE 16. DATA/COEFFICIENT ALIGNMENT FOR 24-TAP DECIMATE BY 3 FIR FILTER

11 10 9

CSEL = 0

(X1 + X22)C1 + (X4 + X19)C4 + (X7 + X16)C7 + (X10 + X13)C10 +(X2 + X21)C2 + (X5 + X18)C5 + (X8 + X15)C8 + (X11 + X12)C11

FIGURE 17B. COMPUTATIONAL FLOW AS DATA SAMPLE 22 IS CLOCKED INTO THE FEED FORWARD STAGE

2 1 0 🗲 🕈 5 4 3 🗲 🕈 8 7 6 🖣

16 15

**C**8

ACCUMULATOR

(X2 + X21)C2 + (X5 + X18)C5 + (X8 + X15)C8 + (X11 + X12)C11

FIGURE 17A. COMPUTATIONAL FLOW AS DATA SAMPLE 21 IS

**CLOCKED INTO THE FEED FORWARD STAGE**

14 13 12

C11

21

C2

20 19 18

C5

FIGURE 17D. COMPUTATIONAL FLOW AS DATA SAMPLE 24 IS CLOCKED INTO THE FEED FORWARD STAGE

FIGURE 17. DATA FLOW DIAGRAMS FOR 24-TAP DECIMATED BY 3 FIR FILTER

**DECIMATE X3 FILTER**

### Example 5. Odd-Tap Decimating Symmetric Filter

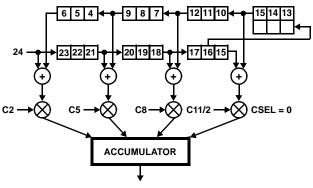

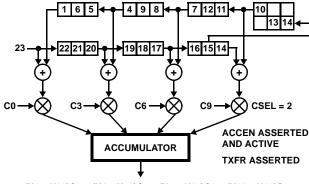

This example highlights the use of the HSP43168 as two independent, 23-tap, symmetric, decimate by 3 filters. In this example, the operational differences in the control signals and data reversal structure may be compared to the previously discussed even-tap decimating filter. Figure 19 shows two FIR cells. The data flow in this example uses only one of the FIR cells.

FIGURE 19. USING HSP43168 AS TWO INDEPENDENT FILTERS

As in the 24-tap example, an output is required every third CLK which allows 3 CLKs for computation. On each CLK, one of three sets of coefficients are used to calculate the filter taps. Since this is an odd length filter, the center coefficient must be scaled by 1/2 to compensate for the summation of the same data sample from the forward and backward shifting decimation paths. The Block Diagrams in Figure 20 show the data flow, and the accumulator output for the data coefficient alignment is shown in Figure 21.

Proper data and coefficient alignment is achieved by asserting TXFR once every three CLKs to switch the LIFOs which are being read and written. In the odd-tap mode, TXFR is internally delayed by one clock cycle with respect to ACCEN so that the convolutional sum will be computed correctly. For odd length filters, data prior to the last register in the forward decimation path is routed to the feedback circuitry. As a result, TXFR should be asserted one cycle prior to the input data samples which align with the center tap. The timing relationship between the CSEL0-5, ACCEN, and TXFR are shown in Figure 22.

<sup>(</sup>X3 + X21)C2 + (X6 + X18)C5 + (X9 + X15)C8 + (X12 + X12)C11/2

FIGURE 20A. COMPUTATIONAL FLOW AS DATA SAMPLE 21 IS

6

FIGURE 20B. COMPUTATIONAL FLOW AS DATA SAMPLE 22 IS CLOCKED INTO THE FEED FORWARD STAGE

(X6 + X24)C2 + (X9 + X21)C5 + (X12 + X18)C8 + (X15 + X15)C11/2

FIGURE 20D. COMPUTATIONAL FLOW AS DATA SAMPLE 24 IS CLOCKED INTO THE FEED FORWARD STAGE TXFR TAKES AFFECT ON THIS CLOCK CYCLE

(X1 + X23)C0 + (X4 + X20)C3 + (X7 + X17)C6 + (X14 + X10)C9 + (X2 + X22)C1 + (X5 + X19)C4 + (X8 + X16)C7 + (X11 + X13)C10 + (X3 + X21)C2 + (X6 + X18)C5 + (X9 + X15)C8 + (X12 + X12)C11/2

FIGURE 20C. COMPUTATIONAL FLOW AS DATA SAMPLE 23 IS **CLOCKED INTO THE FEED FORWARD STAGE**

†Tied low.

#### FIGURE 22. CONTROL SIGNAL TIMING FOR 23-TAP SYMMETRIC FILTER

To operate in this mode, the Dual is configured by writing 112H to Address 000H via the microprocessor interface, CIN0-9, A0-8, and  $\overline{WR}$ . Data reversal must be enabled (see Table 2). The 12 unique coefficients for this example are stored as three sets of coefficients for either FIR cell. For FIR A, the coefficients are loaded into the Coefficient Bank by writing [C2, C5, C8, (C11)/ 2], CSEL = 0; [C1, C4, C7, C10], CSEL = 1; [C0, C3, C6, and C9], CSEL = 2; to address 100H, 101H, 102H, 103H, 108H, 109H, 10aH, 10bH, 110H, 111H, 112H, and 113H, respectively.

# Example 6. Dual Decimation Example

The purpose of this example is to give an overview of one of the more complex applications of the HSP43168. The input is two data streams (A) and (B) samples. Figure 23 shows the upper level block diagram of the system being implemented. The decimation rate was set to N. N-1 is loaded into the decimation factor in Control Word 000H.

#### FIGURE 23. MULTIPLEXED DECIMATION BLOCK DIAGRAM

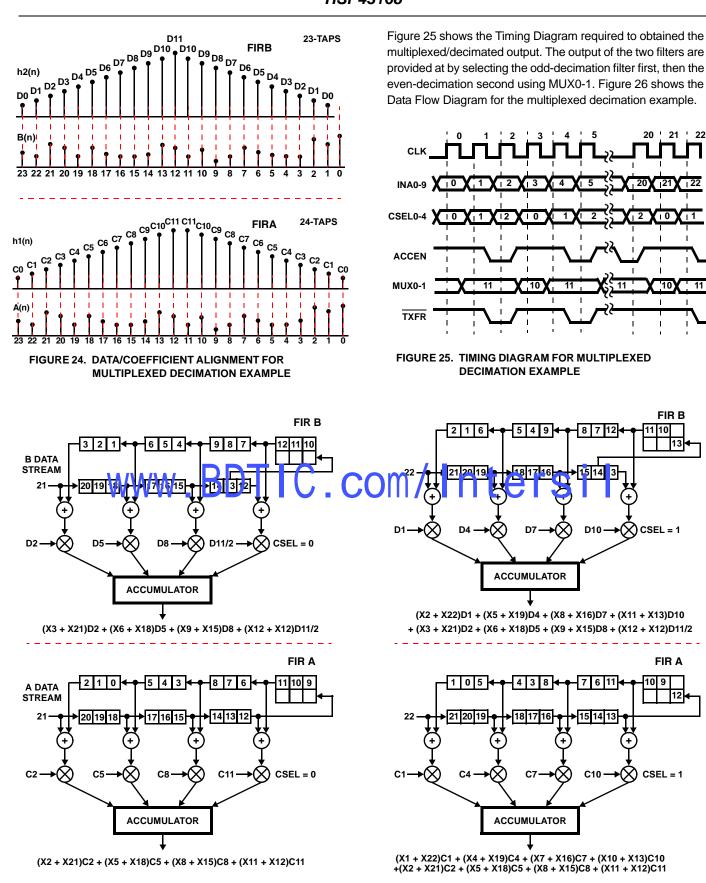

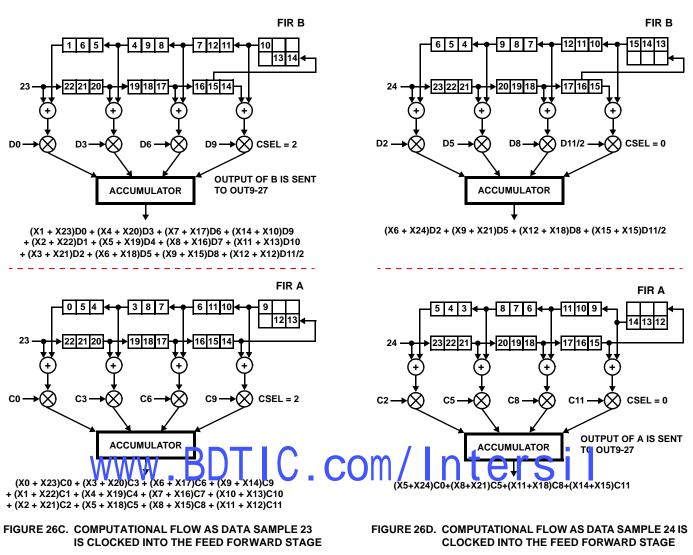

To demonstrate the muxed decimation, lets suppose that the application requires filter A to be configured as an even-decimate-by-3 filter and filter B to be configured as a odd-decimate-by-3 filter. The output data is made of the two decimated data streams multiplexed together and has a data rate equal to 2 times the input sampling rate divided by the decimation factor. Figure 24 shows the data/coefficient alignment for FIR A and FIR B.

To operate in this mode, Control Word 000H must be written with a  $0 \times 152$ . Data reversal must be enabled by setting bit 4 of Control Vord 001H = 0. The filter set selected by CSIEL0-4 = 0 should be readed by writing C2, C5, C8, C11, D2, D5, D8, and (D11)/2 into 100H, 101H, 102H, 103H, 104H, 105H, 106H, and 107H. The filter set selected by CSEL0-4 = 1 should be loaded by writing C1, C4, C7, C10, D1, D4, D7, and D10 into 108H, 109H, 10aH, 10bH, 10cH, 10dH, 10eH, and 10fH. The filter set selected by CSEL0-4 = 2 should be loaded by writing C0, C3, C6, C9, D0, D3, D6, and D9 into 110H, 111H, 112H, 113H, 114H, 115H, 116H, and 117H.

FIGURE 26B. COMPUTATIONAL FLOW AS DATA SAMPLE 22 IS **CLOCKED INTO THE FEED FORWARD STAGE**

22

11

10

FIR B

13

**FIR A**

12

FIGURE 26A. COMPUTATIONAL FLOW AS DATA SAMPLE 21 IS **CLOCKED INTO THE FEED FORWARD STAGE**

FIGURE 26. DATA FLOW DIAGRAM FOR MULTIPLEXED DECIMATION EXAMPLE

# **Absolute Maximum Ratings**

| Supply Voltage               | +6.0V                              |

|------------------------------|------------------------------------|

| Input, Output or I/O Voltage | GND -0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification           |                                    |

# **Operating Conditions**

| Voltage Range                     | 5V ±5%   |

|-----------------------------------|----------|

| Temperature Range, Commercial 0°C | to +70°C |

| Temperature Range, Industrial     | to +85°C |

# **Die Characteristics**

| Back Side Potential            | -5V |

|--------------------------------|-----|

| Number of Transistors or Gates | 529 |

# **Thermal Information**

| Thermal Resistance (Typical, Note 3)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| MQFP Package                             | 33                     |

| PLCC Package                             | 23                     |

| Maximum Junction Temperature             |                        |

| MQFP and PLCC Packages                   | +150°C                 |

| Maximum Storage Temperature Range65°     | C to +150°C            |

| Maximum Lead Temperature (Soldering 10s) | +300°C                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

3.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **DC Electrical Specifications**

| PARAMETER                    | PARAMETER SYMBOL TEST CONDITIONS                                                               |                                                                        |        | МАХ   | UNITS |

|------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------|-------|-------|

| Power Supply Current         | Supply Current I <sub>CCOP</sub> V <sub>CC</sub> = Max<br>CLK Frequency 33MHz<br>Notes 5, 6, 7 |                                                                        | -      | 363   | mA    |

| Standby Power Supply Current | ICCSB                                                                                          | V <sub>CC</sub> = Max, Outputs Not Loaded                              | -      | - 500 |       |

| Input Leakage Current        | l                                                                                              | $V_{CC}$ = Max, Input = 0V or $V_{CC}$                                 | -10    | 10    | μA    |

| Output Leakage Current       |                                                                                                | V <sub>CC</sub> = Max, Input = 0V or V <sub>CC</sub>                   | -10    | 10    | μA    |

| Logical One Input Vol.apt    | <b>В</b> Vн                                                                                    |                                                                        | T er s |       | V     |

| Logical Zero Input Voltage   | V <sub>IL</sub>                                                                                | V <sub>CC</sub> = Min                                                  | -      | 0.8   | V     |

| Logical One Output Voltage   | V <sub>OH</sub>                                                                                | $I_{OH}$ = -400µA, $V_{CC}$ = Min                                      | 2.6    | -     | V     |

| Logical Zero Output Voltage  | V <sub>OL</sub>                                                                                | $I_{OL} = 2mA, V_{CC} = Min$                                           | -      | 0.4   | V     |

| Clock Input High             | VIHC                                                                                           | V <sub>CC</sub> = Max                                                  | 3.0    | -     | V     |

| Clock Input Low              | V <sub>ILC</sub>                                                                               | V <sub>CC</sub> = Min                                                  | -      | 0.8   | V     |

| Input Capacitance            | C <sub>IN</sub>                                                                                | CLK Frequency 1MHz                                                     | -      | 12    | pF    |

| Output Capacitance           | C <sub>OUT</sub>                                                                               | All measurements referenced<br>to GND.<br>$T_A = 25^{\circ}C$ , Note 4 | -      | 12    | pF    |

NOTES:

4. Controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or changes.

5. Power Supply current is proportional to operating frequency. Typical rating for  $I_{CCOP}$  is 11mA/MHz.

6. Output load per test load circuit and  $C_L = 40 pF$ .

7. Maximum junction temperature must be considered when operating part at high clock frequencies.

|                                                                                                     |                   |         | -33 (33MHz) |            | -40 (40.8MHz) |     | -45 (45MHz) |     |       |

|-----------------------------------------------------------------------------------------------------|-------------------|---------|-------------|------------|---------------|-----|-------------|-----|-------|

| PARAMETER                                                                                           | SYMBOL            | NOTES   | MIN         | MAX        | MIN           | MAX | MIN         | MAX | UNITS |

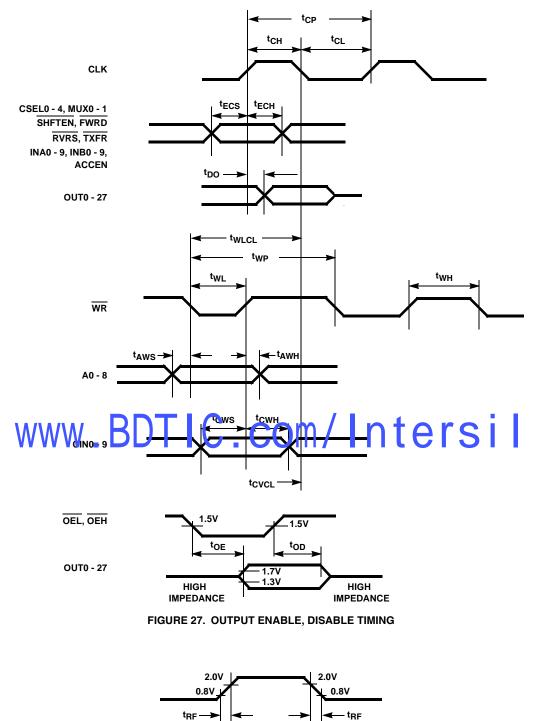

| CLK Period                                                                                          | t <sub>CP</sub>   |         | 30          | -          | 24.5          | -   | 22          | -   | ns    |

| CLK High                                                                                            | tсн               |         | 12          | -          | 10            | -   | 8           | -   | ns    |

| CLK Low                                                                                             | <sup>t</sup> CL   |         | 12          | -          | 10            | -   | 8           | -   | ns    |

| WR Period                                                                                           | t <sub>WP</sub>   |         | 30          | -          | 24.5          | -   | 22          | -   | ns    |

| WR High                                                                                             | t <sub>WH</sub>   |         | 12          | -          | 10            | -   | 10          | -   | ns    |

| WR Low                                                                                              | t <sub>WL</sub>   |         | 12          | -          | 10            | -   | 10          | -   | ns    |

| Setup Time A0-8 to WR Going Low                                                                     | t <sub>AWS</sub>  |         | 10          | -          | 8             | -   | 8           | -   | ns    |

| Hold Time A0-8 from WR Going High                                                                   | tawh              |         | 0           | -          | 0             | -   | 0           | -   | ns    |

| Setup Time CIN0-9 to WR Going High                                                                  | t <sub>CWS</sub>  |         | 12          | -          | 11            | -   | 10          | -   | ns    |

| Hold Time CIN0-9 from WR Going High                                                                 | <sup>t</sup> CWH  |         | 1           | -          | 1             | -   | 1           | -   | ns    |

| Setup Time WR Low to CLK Low                                                                        | tWLCL             | Note 9  | 5           | -          | 4             | -   | 3           | -   | ns    |

| Setup Time CIN0-9 to CLK Low                                                                        | <sup>t</sup> CVCL | Note 9  | 7           | -          | 7             | -   | 7           | -   | ns    |

| Setup Time CSEL0-5, SHFTEN, FWRD, RVRS, TXFR,<br>INA0-9, INB0-9, ACCEN, MUX0-1 to CLK<br>Going High | tECS              |         | 15          | -          | 13            | -   | 12          | -   | ns    |

| Hold Time CSEL0-5, SHFTEN, FWRD, RVRS, TXFR,<br>INA0-9, INB0-9, ACCEN, MUX0-1 to CLK<br>Going High  | <sup>t</sup> ECH  |         | 0           | -          | 0             | -   | 0           | -   | ns    |

| CLK to Output Delay OUT0-27                                                                         | t <sub>DO</sub>   |         |             | 14         | -             | 13  |             | 12  | ns    |

|                                                                                                     | t <sub>OE</sub>   | n       | <b>/</b> -  | <b>n</b> 1 | Α             |     | j.          | 12  | ns    |

| Output Disable Time                                                                                 | toD               | Note 10 | 1           | 12         |               | 12  | 1.1         | 12  | ns    |

| Output Rise, Fall Time                                                                              | <sup>t</sup> RF   | Note 10 | -           | 6          | -             | 6   | -           | 6   | ns    |

# AC Electrical Specifications $V_{CC} = +4.75V$ to +5.25V, $T_A = 0^{\circ}C$ to $+70^{\circ}C$ Commercial, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ Industrial (Note 8)

NOTES:

8. AC tests performed with  $C_L = 40pF$ ,  $I_{OL} = 2mA$ , and  $I_{OH} = -400\muA$ . Input reference level CLK = 2.0V. Input reference level for all other inputs is 1.5V. Test  $V_{IH} = 3.0V$ ,  $V_{IHC} = 4.0V$ ,  $V_{IL} = 0V$ ,  $V_{ILC} = 0V$ .

9. Setup time requirement for loading of data on CIN0-9 to guarantee recognition on the following clock.

10. Controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or changes.

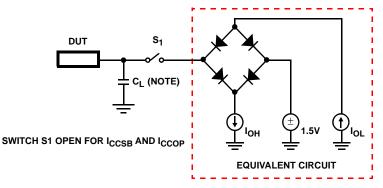

# AC Test Load Circuit

NOTE: Test head capacitance.

# Waveforms

FIGURE 28. OUTPUT RISE AND FALL TIMES

# Metric Plastic Quad Flatpack Packages (MQFP)

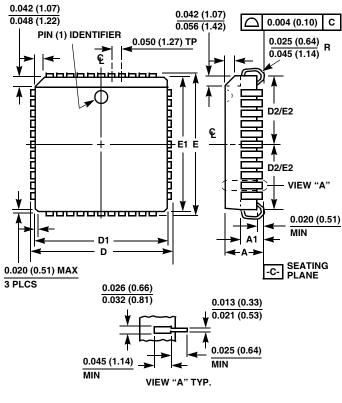

# Plastic Leaded Chip Carrier Packages (PLCC)

#### N84.1.15 (JEDEC MS-018AF ISSUE A) 84 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

|        | INCI  | HES   | MILLIN |       |       |

|--------|-------|-------|--------|-------|-------|

| SYMBOL | MIN   | MAX   | MIN    | MAX   | NOTES |

| А      | 0.165 | 0.180 | 4.20   | 4.57  | -     |

| A1     | 0.090 | 0.120 | 2.29   | 3.04  | -     |

| D      | 1.185 | 1.195 | 30.10  | 30.35 | -     |

| D1     | 1.150 | 1.158 | 29.21  | 29.41 | 3     |

| D2     | 0.541 | 0.569 | 13.75  | 14.45 | 4, 5  |

| Е      | 1.185 | 1.195 | 30.10  | 30.35 | -     |

| E1     | 1.150 | 1.158 | 29.21  | 29.41 | 3     |

| E2     | 0.541 | 0.569 | 13.75  | 14.45 | 4, 5  |

| N 84   |       |       | ł      | 6     |       |

Rev. 2 11/97

#### NOTES:

#### monsions ar COM/Intersi 1. Controlling dim Cor not necessarily exact

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- 3. Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1 and E1 include mold mismatch and are measured at the extreme material condition at the body parting line.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 guality systems. Intersil Corporation's guality certifications can be viewed at www.intersil.com/design/guality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com