Data Sheet September 2004 FN3123.4

· Pb-free Available as an Option

# High Speed, Quad SPST, CMOS Analog Switch

The HI-201HS is a monolithic CMOS Analog Switch featuring very fast switching speeds and low ON resistance. The integrated circuit consists of four independently selectable SPST switches and is pin compatible with the industry standard HI-201 switch.

Fabricated using silicon-gate technology and the Intersil Dielectric Isolation process, this TTL compatible device offers improved performance over previously available CMOS analog switches. Featuring maximum switching times of 50ns, low ON resistance of  $50\Omega$  maximum, and a wide analog signal range, the HI-201HS is designed for any application where improved switching performance, particularly switching speed, is required. (A more detailed discussion on the design and application of the HI-201HS can be found in Application Note AN543.)

# **Ordering Information**

| PART NUMBER                 | TEMP.<br>RANGE (°C) | PACKAGE                 | PKG.<br>DWG.# |

|-----------------------------|---------------------|-------------------------|---------------|

| HI1-0201HS-2                | -55 to 125          | 16 Ld CERDIP            | F16.3         |

| HI1-0201HS-4                | -25 to 85           | 16 LG CEP DIP           | F16.3         |

| HI1-0201HS-5                | 0 to 75             | 16 Ld CERDIP            | F16.3         |

| HI3-0201HS-5                | 0 to 75             | 16 Ld PDIP              | E16.3         |

| HI3-0201HS-5Z<br>(See Note) | 0 to 75             | 16 Ld PDIP<br>(Pb-free) | E16.3         |

| HI9P0201HS-5                | 0 to 75             | 16 Ld SOIC              | M16.3         |

| HI9P0201HS-5Z<br>(See Note) | 0 to 75             | 16 Ld SOIC<br>(Pb-free) | M16.3         |

| HI9P0201HS-9                | -40 to 85           | 16 Ld SOIC              | M16.3         |

| HI9P0201HS-9Z<br>(See Note) | -40 to 85           | 16 Ld SOIC<br>(Pb-free) | M16.3         |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020C.

#### **Features**

| • | Fast Switching Times                      |       |

|---|-------------------------------------------|-------|

|   | - t <sub>ON</sub>                         | 30ns  |

|   | - t <sub>OFF</sub>                        | 40ns  |

| • | Low "ON" Resistance                       | . 30Ω |

| • | Pin Compatible with Standard HI-201       |       |

| • | Wide Analog Voltage Range (±15V Supplies) | ±15V  |

- TTL Compatible

- Symmetrical Switching Analog Current Range . . . . 80mA

• Low Charge Injection (±15V Supplies) . . . . . . . . 10pC

# **Applications**

- · High Speed Multiplexing

- · High Frequency Analog Switching

- · Sample and Hold Circuits

- · Digital Filters

- Operational Amplifier Gain, Switching Natworks

Integrator Reset Circuits

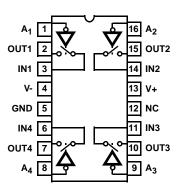

Pinout (Switches Shown For Logic "1" Input)

HI-201HS (CERDIP, PDIP, SOIC) TOP VIEW

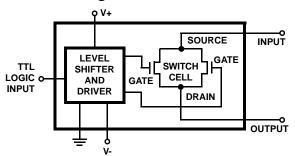

# Functional Diagram

#### TRUTH TABLE

| LOGIC | SWITCH |

|-------|--------|

| 0     | ON     |

| 1     | OFF    |

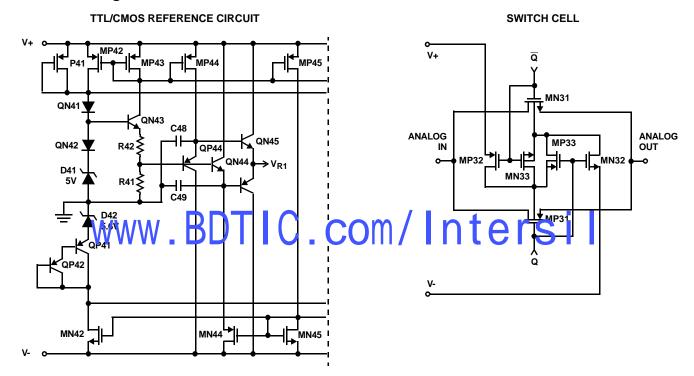

# Schematic Diagrams

# Schematic Diagrams (Continued)

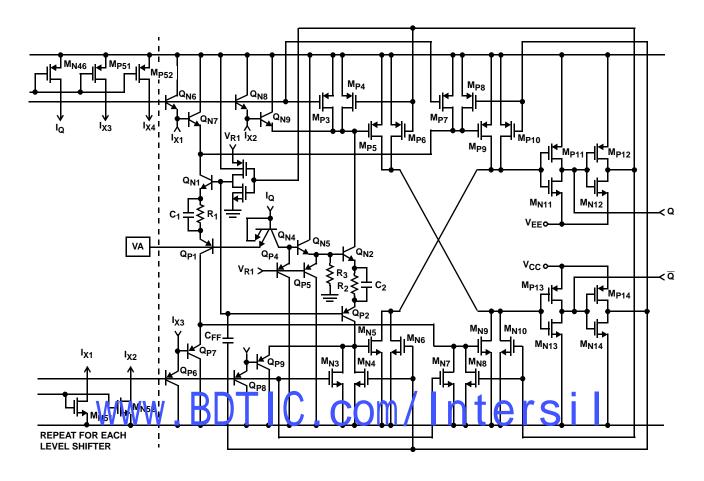

#### DIGITAL INPUT BUFFER AND LEVEL SHIFTER

#### **Absolute Maximum Ratings**

| Supply Voltage (V+ to V-)                                  |

|------------------------------------------------------------|

| Digital Input Voltage(V+) +4V to (V-) -4V                  |

| Analog Input Voltage (One Switch) (V+) +2.0V to (V-) -2.0V |

| Peak Current, S or D (Pulse 1ms, 10% Duty Cycle Max) 50mA  |

| Continuous Current Any Terminal (Except S or D)            |

### **Operating Conditions**

| Temperature Ranges |                                       |

|--------------------|---------------------------------------|

| HI-201HS-2         | 55°C to 125°C                         |

| HI-201HS-4         | 25°C to 85°C                          |

|                    | 0 <sup>o</sup> C to 75 <sup>o</sup> C |

| HI-201HS-9         | 40°C to 85°C                          |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)  | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (oC/W)               |

|---------------------------------------|------------------------|--------------------------------------|

| CERDIP Package                        | 80                     | 20                                   |

| PDIP Package                          | 90                     | N/A                                  |

| SOIC Package                          | 100                    | N/A                                  |

| Maximum Junction Temperature          |                        |                                      |

| Ceramic Package                       |                        | 175°C                                |

| Plastic Package                       |                        | 150°C                                |

| Maximum Storage Temperature           | 65                     | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1 | 0s)                    | 300°C                                |

| (SOIC - Lead Tips Only)               |                        |                                      |

|                                       |                        |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

#### Electrical Specifications

Supplies = +15V, -15V;  $V_{AH}$  (Logic Level High) = 2.4V,  $V_{AL}$  (Logic Level Low) = +0.8V, GND = 0V, Unless Otherwise Specified

|                                                   | TEST                   | TEMP        | -2          |     | -4, -5, -9 |          |     |     |       |

|---------------------------------------------------|------------------------|-------------|-------------|-----|------------|----------|-----|-----|-------|

| PARAMETER                                         | CONDITIONS             | (°C)        | MIN         | TYP | MAX        | MIN      | TYP | MAX | UNITS |

| DYNAMIC CHARACTERISTICS                           |                        | '           | <u>'</u>    |     |            | <u>'</u> | ı   |     | "     |

| Switch ON Time, t <sub>ON</sub>                   | (Note 3)               | 25          | -           | 30  | 50         | -        | 30  | 50  | ns    |

| Switch OFF Time, t <sub>OFF1</sub>                | (Note 3)               | 25          | -           | 40  | 50         | -        | 40  | 50  | ns    |

| Switch OFF Time, t <sub>OFF2</sub>                | (Note 3)               | 25          | /           | 150 | 1          |          | 150 | -   | ns    |

| Output Settling Time WW _ D                       | To ).1%                | <b>C</b> 25 | <b>M</b> -/ | 180 | te         | rs       | 180 | -   | ns    |

| Charge Injection, Q                               | (Note 6)               | 25          | -           | 10  | -          | -        | 10  | -   | рС    |

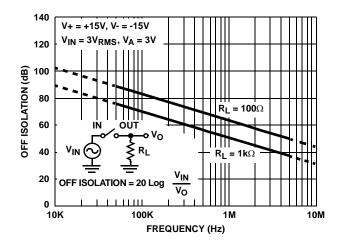

| OFF Isolation                                     | (Note 4)               | 25          | -           | 72  | -          | -        | 72  | -   | dB    |

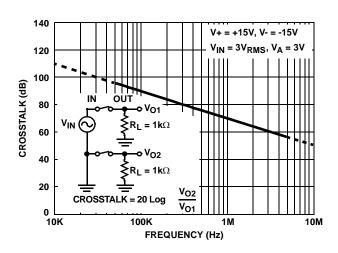

| Crosstalk                                         | (Note 5)               | 25          | -           | 86  | -          | -        | 86  | -   | dB    |

| Input Switch Capacitance, C <sub>S(OFF)</sub>     |                        | 25          | -           | 10  | -          | -        | 10  | -   | pF    |

| Output Switch Capacitance C <sub>D(OFF</sub>      | ·)                     | 25          | -           | 10  | -          | -        | 10  | -   | pF    |

| C <sub>D(ON)</sub>                                | ,                      | 25          | -           | 30  | -          | -        | 30  | -   | pF    |

| Digital Input Capacitance, CA                     |                        | 25          | -           | 18  | -          | -        | 18  | -   | pF    |

| Drain-To-Source Capacitance, C <sub>DS(OFF)</sub> |                        | 25          | -           | 0.5 | -          | -        | 0.5 | -   | pF    |

| DIGITAL INPUT CHARACTERISTICS                     | ,                      | •           | 1           | 1   |            | •        |     |     | •     |

| Input Low Threshold, V <sub>AL</sub>              |                        | Full        | -           | -   | 0.8        | -        | -   | 8.0 | V     |

| Input High Threshold, V <sub>AH</sub>             |                        | 25          | 2.0         | -   | -          | 2.0      | -   | -   | V     |

|                                                   |                        | Full        | 2.4         | -   | -          | 2.4      | -   | -   | V     |

| Input Leakage Current (Low), IAL                  |                        | 25          | -           | 200 | -          | -        | 200 | -   | μА    |

|                                                   |                        | Full        | -           | -   | 500        | -        | -   | 500 | μА    |

| Input Leakage Current (High), I <sub>AH</sub>     | V <sub>AH</sub> = 4.0V | 25          | -           | 20  | -          | -        | 20  | -   | μА    |

|                                                   |                        | Full        | -           | -   | 40         | -        | -   | 40  | μА    |

| ANALOG SWITCH CHARACTERISTICS                     |                        |             |             |     |            |          |     |     | 1     |

| Analog Signal Range, V <sub>S</sub>               |                        | Full        | -15         | -   | +15        | -15      | -   | +15 | V     |

| ON Resistance, r <sub>ON</sub>                    | (Note 2)               | 25          | -           | 30  | 50         | -        | 30  | 50  | Ω     |

|                                                   |                        | Full        | -           | -   | 75         | -        | -   | 75  | Ω     |

**Electrical Specifications**  $Supplies = +15 \text{V}, -15 \text{V}; \ V_{AH} \ (\text{Logic Level High}) = 2.4 \text{V}, \ V_{AL} \ (\text{Logic Level Low}) = +0.8 \text{V}, \ GND = 0 \text{V},$ Unless Otherwise Specified (Continued)

|                                                 | TEST       | TEMP | -2  |     |      | -4, -5, -9 |     |      |       |

|-------------------------------------------------|------------|------|-----|-----|------|------------|-----|------|-------|

| PARAMETER                                       | CONDITIONS | _    | MIN | TYP | MAX  | MIN        | TYP | MAX  | UNITS |

| r <sub>ON</sub> Match                           |            | 25   | -   | 3   | -    | -          | 3   | -    | %     |

| OFF Input Leakage Current, I <sub>S(OFF)</sub>  |            | 25   | -   | 0.3 | 10   | -          | 0.3 | 10   | nA    |

|                                                 |            | Full | ı   | -   | 100  | -          | -   | 50   | nA    |

| OFF Output Leakage Current, I <sub>D(OFF)</sub> |            | 25   | 1   | 0.3 | 10   | -          | 0.3 | 10   | nA    |

|                                                 |            | Full |     | -   | 100  | -          | -   | 50   | nA    |

| ON Leakage Current, I <sub>D(ON)</sub>          |            | 25   | -   | 0.1 | 10   | -          | 0.1 | 10   | nA    |

|                                                 |            | Full |     | -   | 100  | -          | -   | 50   | nA    |

| POWER SUPPLY CHARACTERISTICS (Note              | 7)         |      |     |     | 1    |            |     |      |       |

| Power Dissipation, P <sub>D</sub>               |            | 25   | -   | 120 | -    | -          | 120 | -    | mW    |

|                                                 |            | Full | -   | -   | 240  | -          | -   | 240  | mW    |

| Current, I+ (Pin 13)                            |            | 25   | -   | 4.5 | -    | -          | 4.5 | -    | mA    |

|                                                 |            | Full | -   | -   | 10.0 | -          | -   | 10.0 | mA    |

| Current, I- (Pin 4)                             |            | 25   | -   | 3.5 | -    | -          | 3.5 | -    | mA    |

|                                                 |            | Full | -   | -   | 6    | -          | -   | 6    | mA    |

#### NOTES:

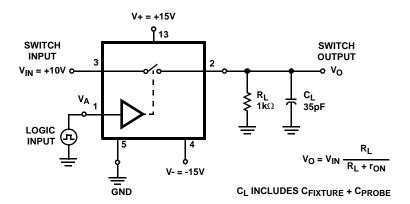

- 2.  $V_{OUT} = \pm 10V$ ,  $I_{OUT} = 1mA$ .

- 3.  $R_L = 1k\Omega$ ,  $C_L = 35pF$ ,  $V_{IN} = +10V$ ,  $V_A = +3V$ . (See Figure 1).

- 4.  $V_A = 3V$ ,  $R_L = 1k\Omega$ ,  $C_L = 10pF$ ,  $V_{II} = 3V_{RV}$

- C.com/Intersil 5.  $V_A = 3V$ ,  $R_L = \langle Q_1 \rangle V_{MI} = 3V_{RMS}$ , r = 100kHz6.  $C_L = 1nF$ ,  $V_{IN} = 0V$ ,  $Q = C_L \times \Delta V_Q$ .

- 7.  $V_A = 3V$  or  $V_A = 0$  for all switches.

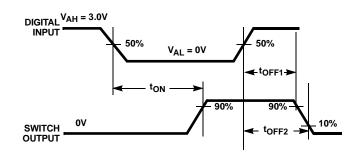

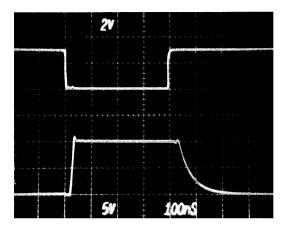

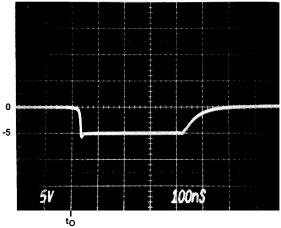

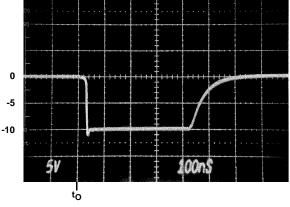

#### Test Circuits and Waveforms

TOP: Logic Input (2V/Div.) BOTTOM: Output (5V/Div.) HORIZONTAL: 100ns/Div.

FIGURE 1A. MEASUREMENT POINTS

FIGURE 1B. WAVEFORMS

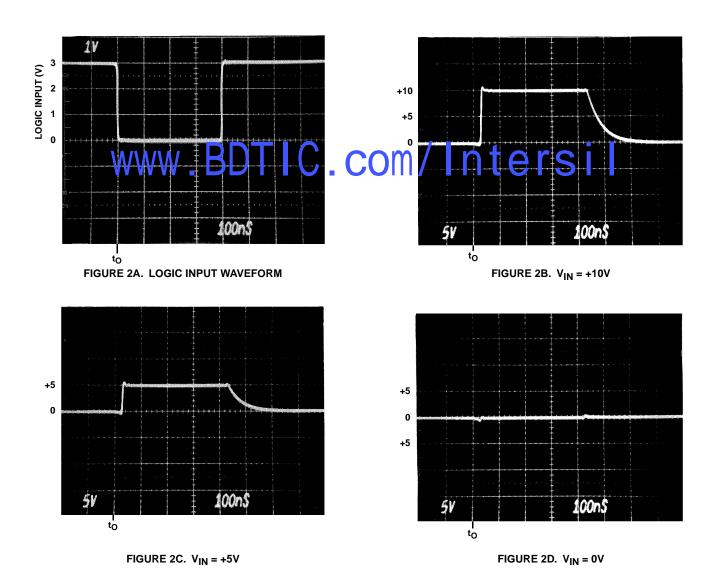

# Test Circuits and Waveforms (Continued)

FIGURE 1C. TEST CIRCUIT FIGURE 1. SWITCH  $t_{\mbox{ON}}$  AND  $t_{\mbox{OFF}}$

#### Test Circuits and Waveforms (Continued)

#### Logic Compatibility

The HI-201HS is TTL compatible. Its logic inputs (pins 1, 8, 9, and 16) are designed to react to digital inputs which exceed a fixed, internally generated TTL switching threshold. The HI-201HS can also be driven with CMOS logic (0V-15V), although the switch open formance with CMOS logic will be inferior to that with TTL logic (0V-54).

The logic input design of the HI-201HS is largely responsible for its fast switching speed. It is a design which features a unique input stage consisting of complementary vertical PNP and NPN bipolar transistors. This design differs from that of the standard HI-201 product where the logic inputs are MOS transistors.

Although the new logic design enhances the switching speed performance, it also increases the logic input leakage currents. Therefore, the HI-201HS will exhibit larger digital input leakage currents in comparison to the standard HI-201 product.

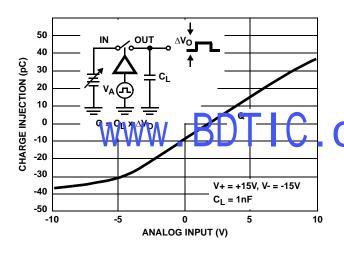

#### Charge Injection

Charge injection is the charge transferred, through the internal gate-to-channel capacitances, from the digital logic input to the analog output. To optimize charge injection performance for the HI-201HS, it is advisable to provide a TTL logic input with fast rise and fall times.

If the power supplies are reduced from  $\pm 15$ V, charge injection will become increasingly dependent upon the digital input frequency. Increased logic input frequency will result in larger output error due to charge injection.

# Power Supply Considerations

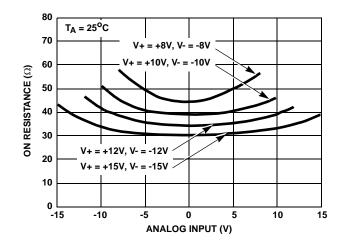

The electrical characteristics specified in this data sheet are guaranteed for power supplies  $V_S = \pm 15 \text{V}$ . Power supply voltages less than  $\pm 15 \text{V}$  will result in reduced switch performance. The following information is intended as a design aid only.

| MOWER SUPFLY VOLTAGES                                | E SWITCH PERFORMANCE                                                                               |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| $\pm 12 \leq V_{\mbox{\scriptsize S}} \leq \pm 15 V$ | Minimal Variation                                                                                  |

| V <sub>S</sub> < ±12V                                | Parametric variation becomes increasingly large (increased ON resistance, longer switching times). |

| V <sub>S</sub> < ±10V                                | Not Recommended.                                                                                   |

| V <sub>S</sub> > ±16V                                | Not Recommended.                                                                                   |

#### Single Supply

The switch operation of the HI-201HS is dependent upon an internally generated switching threshold voltage optimized for  $\pm 15$ V power supplies. The HI-201HS does not provide the necessary internal switching threshold in a single supply system. Therefore, if single supply operation is required, the HI-300 series of switches is recommended. The HI-300 series will remain operational to a minimum +5V single supply.

Switch performance will degrade as power supply voltage is reduced from optimum levels ( $\pm 15V$ ). So it is recommended that a single supply design be thoroughly evaluated to ensure that the switch will meet the requirements of the application.

For further information see Application Notes AN520, AN521, AN531, AN532, AN543 and AN557.

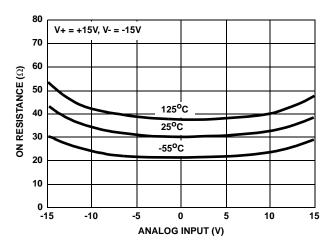

# Typical Performance Curves

FIGURE 3. ON RESISTANCE vs ANALOG SIGNAL LEVEL

FIGURE 4. ON RESISTANCE vs ANALOG SIGNAL LEVEL

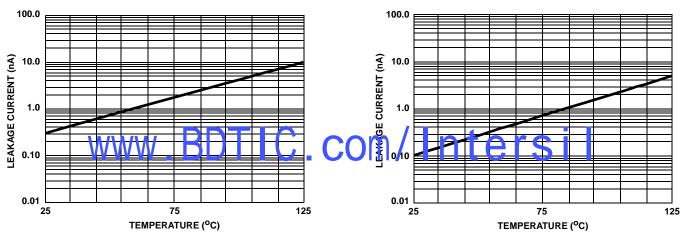

FIGURE 5.  $I_{S(OFF)}$  OR  $I_{D(OFF)}$  vs TEMPERATURE †

FIGURE 6.  $I_{D(ON)}$  vs TEMPERATURE †

<sup>†</sup> Theoretically, leakage current will continue to decrease below 25°C. But due to environmental conditions, leakage measurements below this temperature are not representative of actual switch performance.

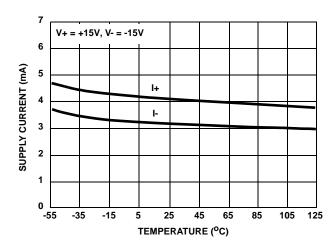

FIGURE 7. SUPPLY CURRENT vs TEMPERATURE

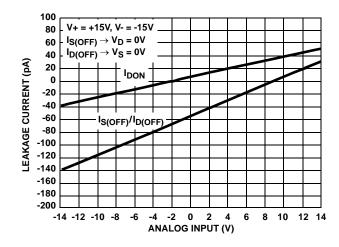

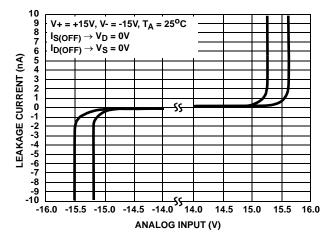

FIGURE 8. LEAKAGE CURRENT vs ANALOG INPUT VOLTAGE

## Typical Performance Curves (Continued)

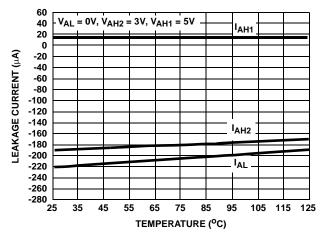

FIGURE 9. DIGITAL INPUT LEAKAGE CURRENT vs TEMPERATURE †

FIGURE 10. LEAKAGE CURRENT vs ANALOG INPUT VOLTAGE

† Theoretically, leakage current will continue to decrease below 25°C. But due to environmental conditions, leakage measurements below this temperature are not representative of actual switch performance.

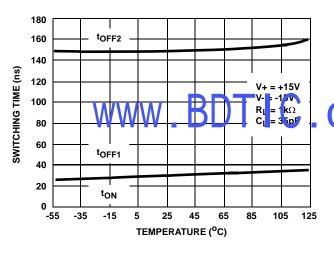

FIGURE 11. SWITCHING TIME vs TEMPERATURE

350

300

250

200

150

100

50

O

7 8 9

SWITCHING TIME (ns)

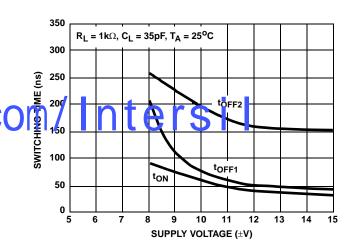

FIGURE 12. SWITCHING TIME vs SUPPLY VOLTAGE

FIGURE 13. SWITCHING TIME vs POSITIVE SUPPLY VOLTAGE

POSITIVE SUPPLY (V)

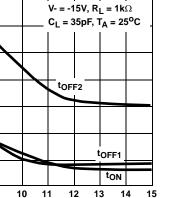

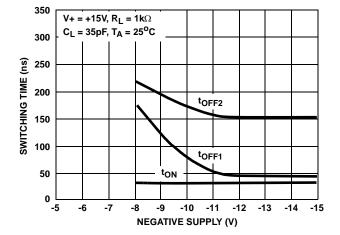

FIGURE 14. SWITCHING TIME vs NEGATIVE SUPPLY VOLTAGE

### Typical Performance Curves (Continued)

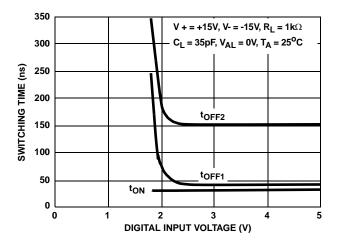

FIGURE 15. SWITCHING TIME vs INPUT LOGIC VOLTAGE

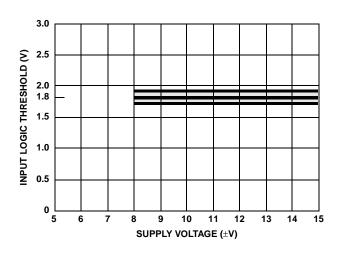

FIGURE 16. INPUT SWITCHING THRESHOLD vs SUPPLY VOLTAGE

FIGURE 17. CHARGE INJECTION vs ANALOG VOLTAGE

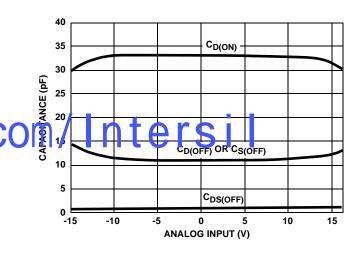

FIGURE 18. CAPACITANCE vs ANALOG VOLTAGE

FIGURE 19. OFF ISOLATION vs FREQUENCY

FIGURE 20. CROSSTALK vs FREQUENCY

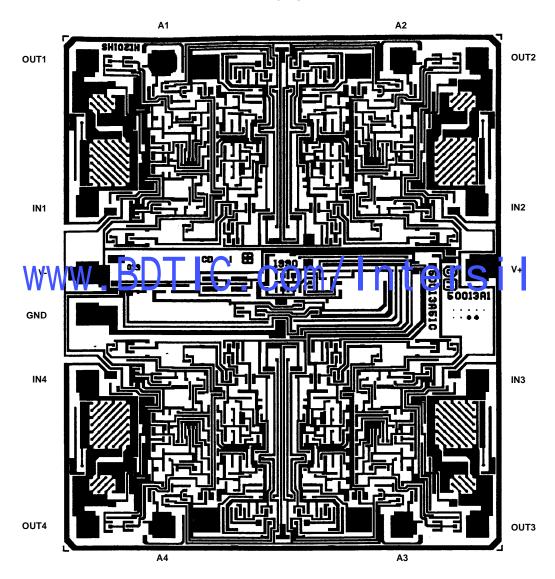

#### Die Characteristics

#### **DIE DIMENSIONS**

2440µm x 2860µm x 485µm

#### **METALLIZATION**

Type: CuAl

Thickness: 16kÅ ±2kÅ

#### **PASSIVATION**

Type: Nitride Over Silox Nitride Thickness: 3.5kÅ ±1kÅ Silox Thickness: 12kÅ ±2kÅ

#### **WORST CASE CURRENT DENSITY**

$9.5 \times 10^4 \text{ A/cm}^2$

### Metallization Mask Layout

HI-201HS

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com