BDTIC www.bdtic.com/Semiconductor

# **Atmel AT29 Flash Memories**

## Introduction

As the industry recognizes the benefits of field reprogrammability for systems, the need for a cost effective, easy to update non-volatile memory arises. To fill this role. Flash memory devices have shown great promise to become the memory of choice. But, as with the early days of EPROM and EEPROM devices, there is much confusion about what features and voltages the ideal Flash memorv device should contain. The ideal Flash device provides the designer the cleanest hardware implementation, requiring the fewest number of external components. In addition the device should provide the software designer with the highest level of flexibility, yet very simple and straightforward commands for programming. Atmel has developed their Flash memories with these ideas in mind.

Atmel Flash memories (programmable erasable read-only memories) are implemented on an advanced sub-micron process using a highly efficient memory cell to store each bit of data. Unlike first generation Flash memories, Fowler-Nordheim tunneling is used in both the erasing and programming of the memory cell. This programming method requires only nanoamps of high voltage (15V to 20V) programming current, allowing the use of an on-chip charge pump to generate the necessary programming voltages. The low programming current also permits sector programming. Typical first generation Flash devices are made with EPROM cell structures which use hot electron injection for programming. Hot electron injection typically requires several milliamps of high voltage programming current. This current requirement is why multiple external voltages are required for programming and why only one byte at a time can be programmed for first generation Flash devices.

### Flash Memory Device Features

The Atmel AT29 family of Flash PEROM devices consists of five capacities ranging from 256K to 4 megabit. All devices are single voltage, either 3-volt only or 5-volt only, and can be programmed using the same deterministic (i.e., fixed maximum time) programming algorithm.

# Flash Programmable Erasable ROM

# Application Note (AN-1)

Table 1. Atmel AT29 Series Flash Memory Devices

| Devices    |             |                | Number        | Sector             | Manu-          | Device ID |    |

|------------|-------------|----------------|---------------|--------------------|----------------|-----------|----|

| 5V         | 3V          | Memory<br>Size | of<br>Sectors | Size<br>(bytes)    | facturer<br>ID | 5V        | 3V |

| AT29C256/7 | AT29LV256/7 | 32K x 8        | 512           | 64                 | 1F             | DC        | BC |

| AT29C512   | AT29LV512   | 64K x 8        | 512           | 128                | 1F             | 5D        | 3D |

| AT29C010A  | AT29LV010A  | 128K x 8       | 1024          | 128                | 1F             | D5        | 35 |

| AT29C1024  | AT29LV1024  | 64K x 16       | 512           | 128 <sup>(1)</sup> | 1F             | 25        | 26 |

| AT29C020   | AT29LV020   | 256K x 8       | 1024          | 256                | 1F             | DA        | BA |

| AT29C040A  | AT29LV040A  | 512K x 8       | 2048          | 256                | 1F             | A4        | C4 |

Note: 1. 128 Words.

The Atmel AT29 Flash memory devices are all designed as large memory arrays broken up into small individually reprogrammable sectors. For example, the AT29C010A (128K x 8) is divided into 1024 sectors of 128 bytes. Table 1 describes this organization for each AT29 Flash PEROM device.

Key features are implemented on a Flash memory to improve system performance and simplify hardware and software development, as described below:

#### **Small Sectors**

Atmel AT29 Flash memories are organized into small sectors for reprogramming. Unlike first generation devices that require erasing large blocks of memory before reprogramming (at least several thousand bytes to as much as the entire chip capacity), Atmel's sector organization allows for fast and easy data updates. Each sector's contents may be altered independently by simply loading new data into the on-chip sector buffer, at full bus speed, then waiting 10 to 20 ms while the chip's built-in sequencer programs the contents of the newly loaded buffer into the array. No preerase is required. When only a small portion of the total memory must be altered, the small sector approach saves considerable time. It also eliminates the need for large system buffer memory space to hold unchanging information that would have to be copied out of a large area of the Flash component and rewritten back into it after the small portion is updated. These differences can be very significant: Write time for the Atmel Flash PEROM is always 10 ms per sector (20 ms for 3-volt write), while write time for large-sectored or whole chip Flash devices is variable and can extend to several minutes. The several-hundred-byte Flash memory sector typically requires no additional buffering, while the large sector devices require tens to hundreds of Kbytes of system memory or extra hardware memory to contain not-to-be-changed memory contents during the mandatory pre-erase activity.

#### **Data Protection**

The Atmel Flash memory has both hardware and software data protection on-chip to prevent the contents of memory from being inadvertently altered. The following five mechanisms exist on each Flash memory:

- 1. **Noise Filter:** All control line inputs have filtering circuitry to eliminate any noise spikes less than 15 ns in duration.

- 2. **V<sub>cc</sub> sense:** If V<sub>cc</sub> falls below 3.8 volts, (typical), programming will be inhibited. For LV (low voltage) devices V<sub>cc</sub> sense is typically 1.8 volts.

- 3. **Power on Delay:** When  $V_{CC}$  rises above the  $V_{CC}$  sense level a 5-ms timer is started which will inhibit programming until it has completed its time-out, allowing all system power transients to settle and initialization routines to proceed without disturbing the Flash PEROM contents.

- Three-Line Control: To initiate a write cycle all three control lines must be in the correct state. If OE is not high, or CE is not low, or if WE is not low a write cycle will be inhibited.

- Software Data Protection (SDP): This protection 5. mechanism is the only one that may be optionally activated or disabled under software control. When it is activated, the Flash memory requires a specific 3-byte temporary unlock write sequence prior to each sector load cycle to enable programming. If a sector load cycle is executed without the 3-byte write sequence, no information will be altered and the device will lock out all activity, (reads and writes), for 10 ms. Activation is accomplished by the first occurrence of the specific 3-byte temporary unlock write sequence. Thereafter, all sector writes must be preceded by the same 3-byte write sequence. SDP can be explicitly disabled by a specific 6-byte write sequence.

#### **Product ID**

Built into every Flash memory is the ability to interrogate the device to determine the manufacturer and device type. Simply write the proper 3-byte code into the device, wait the write cycle time ( $t_{WC}$ ), and read from locations 0000H and 0001H. No special voltages are required. Reading from location 0000H will access the manufacturer code. All Atmel devices read 1F. Reading from location 0001H will access the device ID code. See Table 1 for the device ID codes for each Flash device. Note that device ID codes are different for the standard 5-volt parts and for the 3-volt (LV) devices. Product ID information can also be accessed by applying a 12-volt signal to pin A9. This is available to maintain compatibility with high voltage Flash or EPROMs when used with external programming hardware.

#### **Data Polling**

Maximum programming time for a Flash memory is specified as 10 ms, (20 ms for LV devices). Typically, this programming time is only 5 to 7 ms, (10 to 15 ms for LV devices). To take advantage of this typical programming time and to speed up the overall programming process, a data polling feature is available in the Flash memory device. To utilize this feature, the user must read from the final address written following a sector write. During programming, Bit 7 will be inverted from the state in which it was written. When a read produces true data on all outputs, the programming process is complete. The device is then ready for the next operation.

#### **Toggle Bit**

An alternate method of indicating when programming is complete is to use the toggle bit. Programming completion is indicated by monitoring Bit 6 of any byte location. On successive reads from a fixed location, Bit 6 will toggle logic states during programming. When Bit 6 does not change on successive reads, the device has completed programming.

Flash

Flash

### AT29 Flash Memory Programming Description

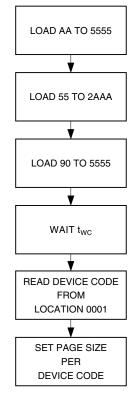

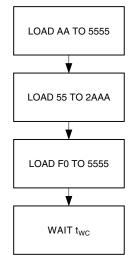

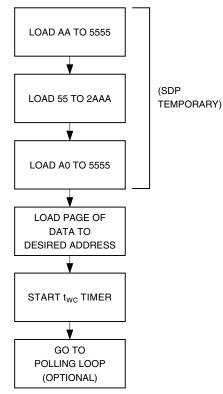

Atmel AT29 Flash memories are designed to allow all devices to be programmed using the same deterministic algorithm. As shown in the accompanying flow charts, Figure 1 through Figure 4, the user simply has to interrogate the device ID code and set the sector size. This operation need only be done once if the sector size variable is saved. The sector size variable can be hard-set in software and the device ID interrogation eliminated if only one density device will ever be used.

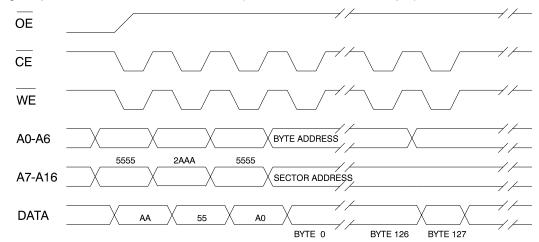

Following sector size determination, a sector load cycle can be initiated. The following will describe programming the 3V Flash and the 5V Flash using software data protection. Programming begins with a 3-byte sequence to temporarily unlock the software data protection, followed by loading the sector of data to the device. This sequence of activity is shown in Figure 5. If a complete sector of data is not loaded, the byte locations within the sector that were not loaded will be cleared to FF during programming. All addresses must be within the same physical sector or errors may occur. It is not necessary to load the sector buffer in any address order. A random addressing sequence is perfectly acceptable, with each byte accompanied by its address within the sector. During the sector load cycle, a maximum time of 150  $\mu$ s (t<sub>BLC</sub>) is allowed between successive byte loads. If this byte load time is exceeded, the device will begin programming mode prematurely.

$t_{BLC}$  time after loading the sector, the Flash memory device will enter its programming mode. While programming, the device will ignore any further write commands and any attempt to read will output only Data Poll and toggle bit data.

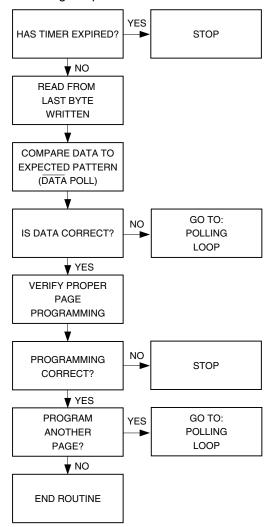

Before entering into a polling loop, it is good practice to start a programming cycle watchdog timer. This will prevent your software from being caught in an endless loop if something goes wrong with programming the device.

The polling loop should consist of two operations. The first is to check status of the watchdog timer, and the second to check Data Poll data. The watchdog timer should never time-out in normal programming. If a time-out does occur, check the hardware and software for possible problems. To check Data Poll, simply read the device at the address of the last byte programmed in the sector. The data should be compared against the data that was written. When the data matches, the programming is complete.

Before going on to another operation, it is recommended to verify that the sector was properly programmed.

Figure 1. Software Product Identification Entry

Figure 2. Software Product Identification Entry

## Summary

Programming the Atmel AT29 Flash memory is a simple process, akin to loading an SRAM. Facilities in the device minimize the software and system overhead and architectural and circuit features simplify the interface and speed performance, while improving system integrity. The programming procedures described above will insure that devices will always be properly programmed, and require only about one-tenth of the typical software, buffer memory and performance overhead of first generation Flash components.

#### Figure 3. Page Loop

Figure 4. Polling Loop

Flash

- Notes: 1.  $\overline{OE}$  must be high when  $\overline{WE}$  and  $\overline{CE}$  are both low.

- 2. A7 through A16 must specify the sector address during each high to low transition of WE (or CE) after the software code has been entered.

- 3. All bytes that are not loaded within the sector being programmed will be indeterminate.