## Octal Sample-and-Hold with Multiplexed Input

### SMP18

### FEATURES

High Speed Version of SMP08 Internal Hold Capacitors Low Droop Rate TTL/CMOS Compatible Logic Inputs Single or Dual Supply Operation Break-Before-Make Channel Addressing Compatible With CD4051 Pinout Low Cost

**APPLICATIONS**

Multiple Path Timing Deskew for A.T.E. Memory Programmers Mass Flow/Process Control Systems Multichannel Data Acquisition Systems Robotics and Control Systems Medical and Analytical Instrumentation Event Analysis Stage Lighting Control

#### **GENERAL DESCRIPTION**

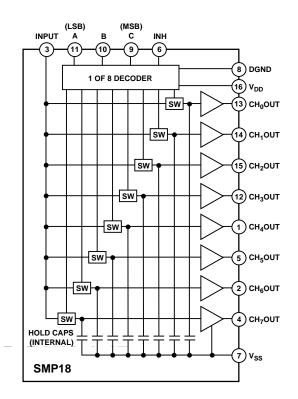

The SMP18 is a monolithic octal sample-and-hold; it has eight internal buffer amplifiers, input multiplexer, and internal hold capacitors. It is manufactured in an advanced oxide isolated CMOS technology to obtain high accuracy, low droop rate, and fast acquisition time. The SMP18 has a typical linearity error of only 0.01% and can accurately acquire a 10-bit input signal to  $\pm 1/2$  LSB in less than 2.5 microseconds. The SMP18's output swing includes the negative supply in both single and dual supply operation.

The SMP18 was specifically designed for systems that use a calibration cycle to adjust a multiple of system parameters. The low cost and high level of integration make the SMP18 ideal for calibration requirements that have previously required an ASIC, or high cost multiple D/A converters.

The SMP18 is also ideally suited for a wide variety of sampleand-hold applications including amplifier offset or VCA gain adjustments. One or more SMP18s can be used with single or multiple DACs to provide multiple set points within a system.

### FUNCTIONAL BLOCK DIAGRAM

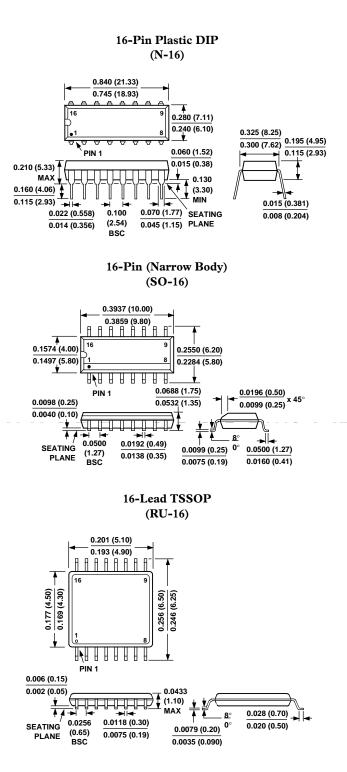

The SMP18 offers significant cost and size reduction over discrete designs. It is available in a 16-pin plastic DIP, a narrow body SO-16 surface-mount SOIC package or the thin TSSOP-16 package. The SMP18 is a higher speed direct replacement for the SMP08.

### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

World Wide Web Site: http://www.analog.com

Fax: 617/326-8703

© Analog Devices, Inc., 1996

# SMP18-SPECIFICATIONS

**ELECTRICAL CHARACTERISTICS** (@  $V_{DD} = +5 V$ ,  $V_{SS} = -5 V$ , DGND = 0 V,  $R_L = No Load$ ,  $T_A = -40^{\circ}C$  to +85°C for SMP18F, unless otherwise noted)

| Parameter                        | Symbol                   | Conditions                                                    | Min  | Тур  | Max  | Units |

|----------------------------------|--------------------------|---------------------------------------------------------------|------|------|------|-------|

| Linearity Error                  |                          | $-3 \text{ V} \le \text{V}_{\text{IN}} \le +3 \text{ V}$      |      | 0.01 |      | %     |

| Buffer Offset Voltage            | Vos                      | $T_A = +25^{\circ}C, V_{IN} = 0 V$                            |      | 2.5  | 10   | mV    |

|                                  |                          | $-40^{\circ}C \le T_A \le +85^{\circ}C, V_{IN} = 0 V$         |      | 3.5  | 20   | mV    |

| Hold Step                        | V <sub>HS</sub>          | $V_{IN} = 0 V, T_A = +25^{\circ}C \text{ to } +85^{\circ}C$   |      | 4    | 6    | mV    |

|                                  |                          | $V_{IN} = 0 V, T_A = -40^{\circ}C$                            |      |      | 8    | mV    |

| Droop Rate                       | $\Delta V_{CH}/\Delta t$ | $T_A = +25^{\circ}C, V_{IN} = 0 V$                            |      | 2    | 40   | mV/s  |

| Output Source Current            | I <sub>SOURCE</sub>      | $V_{IN} = 0 V^1$                                              | 1.2  |      |      | mA    |

| Output Sink Current              | I <sub>SINK</sub>        | $V_{IN} = 0 V^1$                                              | 0.5  |      |      | mA    |

| Output Voltage Range             |                          | $R_L = 20 k\Omega$                                            | -3.0 |      | +3.0 | V     |

| LOGIC CHARACTERISTICS            |                          |                                                               |      |      |      |       |

| Logic Input High Voltage         | V <sub>INH</sub>         |                                                               | 2.4  |      |      | V     |

| Logic Input Low Voltage          | V <sub>INL</sub>         |                                                               |      |      | 0.8  | V     |

| Logic Input Current              | I <sub>IN</sub>          | $V_{IN} = 2.4 V$                                              |      | 0.5  | 1    | μΑ    |

| DYNAMIC PERFORMANCE <sup>2</sup> |                          |                                                               |      |      |      |       |

| Acquisition Time <sup>3</sup>    | t <sub>AQ</sub>          | $T_A = +25^{\circ}C, -3 V \text{ to } +3 V \text{ to } 0.1\%$ |      | 3.5  |      | μs    |

| Hold Mode Settling Time          | t <sub>H</sub>           | To $\pm 1$ mV of Final Value                                  |      | 1    |      | μs    |

| Channel Select Time              | t <sub>CH</sub>          |                                                               |      | 90   |      | ns    |

| Channel Deselect Time            | t <sub>DCS</sub>         |                                                               |      | 45   |      | ns    |

| Inhibit Recovery Time            | t <sub>IR</sub>          |                                                               |      | 90   |      | ns    |

| Slew Rate                        | SR                       |                                                               |      | 6    |      | V/µs  |

| Capacitive Load Stability        |                          | <30% Overshoot                                                |      | 500  |      | pF    |

| Analog Crosstalk                 |                          | -3 V to $+3$ V Step                                           |      | -72  |      | dB    |

| SUPPLY CHARACTERISTICS           |                          |                                                               |      |      |      |       |

| Power Supply Rejection Ratio     | PSRR                     | $V_{SS} = \pm 5 V \text{ to } \pm 6 V$                        | 60   | 75   |      | dB    |

| Supply Current                   | I <sub>DD</sub>          | $T_A = +25^{\circ}C$                                          |      | 5.5  | 7.5  | mA    |

|                                  |                          | $-40^{\circ}C \le T_A \le +85^{\circ}C$                       |      | 7.5  | 9.5  | mA    |

# **ELECTRICAL CHARACTERISTICS** (@ $V_{DD} = +12 V$ , $V_{SS} = 0 V$ , DGND = 0 V, $R_L = No Load$ , $T_A = -40^{\circ}C$ to +85°C for SMP18F, unless otherwise noted)

| Parameter                                                                                                                                                                                                                                        | Symbol                                                                                            | Conditions                                                                                                                    | Min  | Тур                                           | Max  | Limits                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------|------|------------------------------------------------|

| Linearity Error                                                                                                                                                                                                                                  |                                                                                                   | $60 \text{ mV} \le \text{V}_{\text{IN}} \le 10 \text{ V}$                                                                     |      | 0.01                                          |      | %                                              |

| Buffer Offset Voltage                                                                                                                                                                                                                            | Vos                                                                                               | $T_A = +25^{\circ}C, V_{IN} = 6 V$                                                                                            |      | 2.5                                           | 10   | mV                                             |

|                                                                                                                                                                                                                                                  |                                                                                                   | $-40^{\circ}C \le T_A \le +85^{\circ}C, V_{IN} = 6 V$                                                                         |      | 3.5                                           | 20   | mV                                             |

| Hold Step                                                                                                                                                                                                                                        | V <sub>HS</sub>                                                                                   | $V_{IN} = 6 V, T_A = +25^{\circ}C \text{ to } +85^{\circ}C$                                                                   |      | 4                                             | 6    | mV                                             |

|                                                                                                                                                                                                                                                  |                                                                                                   | $V_{IN} = 6 V, T_A = -40^{\circ}C$                                                                                            |      |                                               | 8    | mV                                             |

| Droop Rate                                                                                                                                                                                                                                       | $\Delta V_{CH}/\Delta t$                                                                          | $T_A = +25^{\circ}C, V_{IN} = 6 V$                                                                                            |      | 2                                             | 40   | mV/s                                           |

| Output Source Current                                                                                                                                                                                                                            | I <sub>SOURCE</sub>                                                                               | $V_{IN} = 6 V_{I}^{1}$                                                                                                        | 1.2  |                                               |      | mA                                             |

| Output Sink Current                                                                                                                                                                                                                              | I <sub>SINK</sub>                                                                                 | $V_{IN} = 6 V^1$                                                                                                              | 0.5  |                                               |      | mA                                             |

| Output Voltage Range                                                                                                                                                                                                                             |                                                                                                   | $R_L = 20 k\Omega$                                                                                                            | 0.06 |                                               | 10.0 | V                                              |

|                                                                                                                                                                                                                                                  |                                                                                                   | $R_L = 10 \text{ k}\Omega$                                                                                                    | 0.06 |                                               | 9.5  | V                                              |

| LOGIC CHARACTERISTICS<br>Logic Input High Voltage<br>Logic Input Low Voltage                                                                                                                                                                     | V <sub>INH</sub><br>V <sub>INL</sub>                                                              |                                                                                                                               | 2.4  |                                               | 0.8  | V<br>V                                         |

| Logic Input Current                                                                                                                                                                                                                              | I <sub>IN</sub>                                                                                   | $V_{IN} = 2.4 V$                                                                                                              |      | 0.5                                           | 1    | μA                                             |

| DYNAMIC PERFORMANCE <sup>2</sup><br>Acquisition Time <sup>3</sup><br>Hold Mode Settling Time<br>Channel Select Time<br>Channel Deselect Time<br>Inhibit Recovery Time<br>Slew Rate <sup>4</sup><br>Capacitive Load Stability<br>Analog Crosstalk | t <sub>AQ</sub><br>t <sub>H</sub><br>t <sub>CH</sub><br>t <sub>DCS</sub><br>t <sub>IR</sub><br>SR | $T_{A} = +25^{\circ}C, 0 \text{ to } 10 \text{ V to } 0.1\%$<br>To ±1 mV of Final Value<br><30% Overshoot<br>0 V to 10 V Step |      | 2.5<br>1<br>90<br>45<br>90<br>7<br>500<br>-72 | 3.25 | μs<br>μs<br>ns<br>ns<br>ns<br>V/μs<br>pF<br>dB |

| SUPPLY CHARACTERISTICS                                                                                                                                                                                                                           |                                                                                                   |                                                                                                                               |      |                                               |      |                                                |

| Power Supply Rejection Ratio                                                                                                                                                                                                                     | PSRR                                                                                              | $10.8 \text{ V} \le \text{V}_{\text{DD}} \le 13.2 \text{ V}$                                                                  | 60   | 75                                            |      | dB                                             |

| Supply Current                                                                                                                                                                                                                                   | I <sub>DD</sub>                                                                                   | $T_A = +25^{\circ}C$                                                                                                          |      | 6.0                                           | 8.0  | mA                                             |

|                                                                                                                                                                                                                                                  |                                                                                                   | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                                       |      | 8.0                                           | 10.0 | mA                                             |

NOTES

<sup>1</sup>Outputs are capable of sinking and sourcing over 10 mA but offset is guaranteed at specified load levels.

<sup>2</sup>All input control signals are specified with  $t_r = t_f = 5$  ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

<sup>3</sup>This parameter is guaranteed without test.

$^{4}$ Slew rate is measured in the sample mode with a 0 to 10 V step from 20% to 80%.

Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS

circuit board for SOIC and TSSOP packages.

| V <sub>DD</sub> to DGND0.3 V, 17 V              |

|-------------------------------------------------|

| $V_{DD}$ to $V_{SS}$ 0.3 V, 17 V                |

| $V_{LOGIC}$ to DGND                             |

| $V_{IN}$ to DGND $V_{SS}$ , $V_{DD}$            |

| $V_{OUT}$ to DGND $V_{SS}$ , $V_{DD}$           |

| Analog Output Current ±20 mA                    |

| (Not short-circuit protected)                   |

| Operating Temperature Range                     |

| FP, FS $\dots -40^{\circ}$ C to $+85^{\circ}$ C |

| Junction Temperature +150°C                     |

| Storage Temperature                             |

| Lead Temperature (Soldering, 60 sec) +300°C     |

|                                                 |

| Package Type                              | θ <sub>JA</sub> * | θ <sub>JC</sub> | Units        |

|-------------------------------------------|-------------------|-----------------|--------------|

| 16-Pin Plastic DIP (P)<br>16-Pin SOIC (S) | 76<br>92          | 33<br>27        | °C/W<br>°C/W |

| 16-Lead TSSOP (RU)                        | 180               | 35              | °C/W         |

${}^{\star}\theta_{JA} \mbox{ is specified for worst case mounting conditions, i.e., } \theta_{JA} \mbox{ is specified for device in socket for plastic DIP packages; } \theta_{JA} \mbox{ is specified for device soldered to printed }$

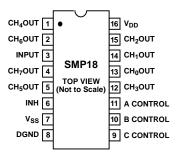

### **PIN CONNECTIONS**

### **ORDERING GUIDE**

| Model    | Temperature    | Package     | Package |

|----------|----------------|-------------|---------|

|          | Range          | Description | Option  |

| SMP18FP  | -40°C to +85°C | Plastic DIP | N-16    |

| SMP18FRU | -40°C to +85°C | TSSOP-16    | RU-16   |

| SMP18FS  | -40°C to +85°C | SO-16       | R-16A   |

### CAUTION\_

NOTES

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the SMP18 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

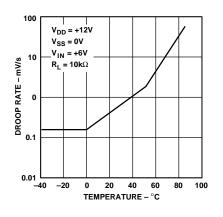

### **SMP18–Typical Performance Characteristics**

Droop Rate vs. Temperature

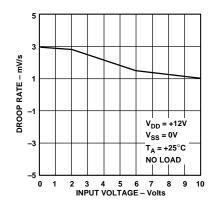

Droop Rate vs. Input Voltage

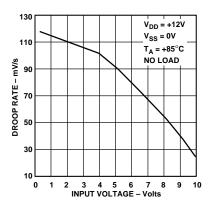

Droop Rate vs. Input Voltage

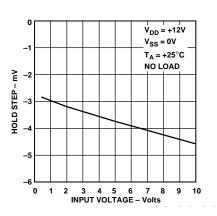

Hold Step vs. Input Voltage

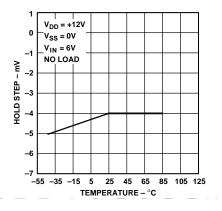

Hold Step vs. Temperature

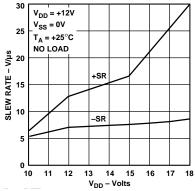

Slew Rate vs. V<sub>DD</sub>

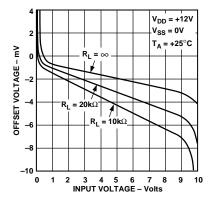

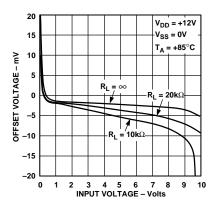

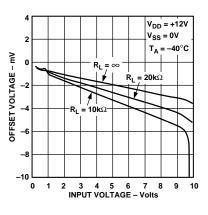

Offset Voltage vs. Input Voltage

Offset Voltage vs. Input Voltage

Offset Voltage vs. Input Voltage

### **Typical Performance Characteristics–SMP18**

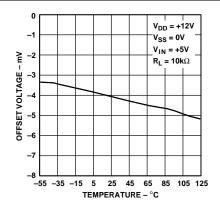

Offset Voltage vs. Temperature

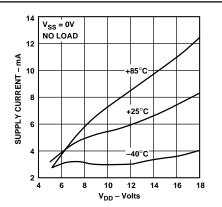

Supply Current vs. V<sub>DD</sub>

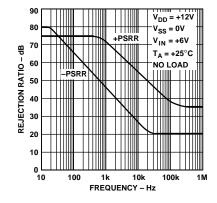

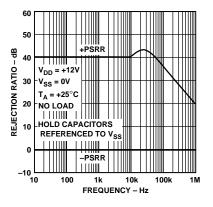

Sample Mode Power Supply Rejection

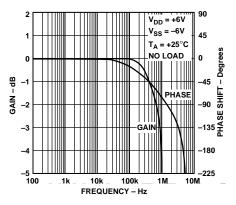

Gain, Phase Shift vs. Frequency

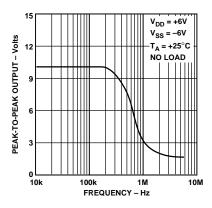

Maximum Output Voltage vs. Frequency

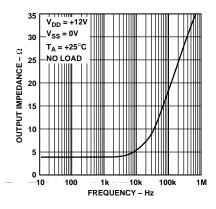

Output Impedance vs. Frequency

Hold Mode Power Supply Rejection

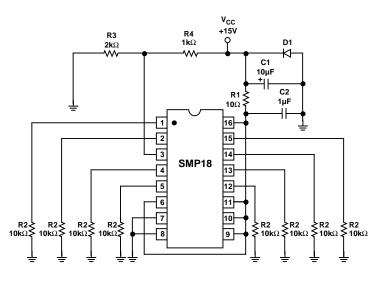

Burn-in Circuit

### APPLICATIONS INFORMATION

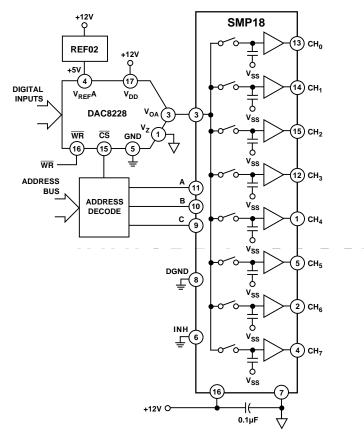

The SMP18, a multiplexed octal S/H, minimizes board space in systems requiring cycled calibration or an array of control voltages. When used in conjunction with a low cost 16-bit D/A, the SMP18 can easily be integrated into microprocessor based systems. Since the SMP18 features break-before-make switching and an internal decoder, no external logic is required. The SMP18 has an internally regulated TTL supply so that TTL/CMOS compatibility is maintained over the full supply range. See Figure 1 for channel decode address information.

### **POWER SUPPLIES**

The SMP18 is capable of operating with either single or dual supplies over a voltage range of 7 to 15 volts. Based on the supply voltages chosen,  $V_{\rm DD}$  and  $V_{\rm SS}$  establish the output voltage range, which is:

$$(V_{SS} + 0.06 V) \le V_{OUT} \le (V_{DD} - 2 V)$$

Note that several specifications, including acquisition time, offset and output voltage compliance, will degrade for supply voltages of less than 7 V.

If split supplies are used, the negative supply should be bypassed with a 0.1  $\mu$ F capacitor in parallel with a 10  $\mu$ F to ground. The internal hold capacitors are connected to this supply pin, and any noise will appear at the outputs.

In single supply applications, it is extremely important that the  $V_{SS}$  (negative supply) pin is connected to a clean ground. The hold capacitors are internally tied to the  $V_{SS}$  (negative) rail. Any ground noise or disturbance will directly couple to the output of the sample-and-hold degrading the signal-to-noise performance. The analog and digital ground traces on the circuit board should be physically separated to reduce digital switching noise from entering the analog circuitry.

### POWER SUPPLY SEQUENCING

$V_{\rm DD}$  should be applied to the SMP18 before the logic input signals. The SMP18 has been designed to be immune to latchup, but standard precautions should still be taken.

#### **OUTPUT BUFFERS** (Pins 1, 2, 4, 5, 12, 13, 14, 15)

The buffer offset specification is 10 mV; this is less than 1/2 LSB of an 8-bit DAC with 10 V full scale. The hold step (magnitude of step caused in the output voltage when switching from sample-to-hold mode, also referred to as the pedestal error or sample-to-hold offset) is about 4 mV with little variation over the full output voltage range. The droop rate of a held channel is 2 mV/s typical and 40 mV/s maximum.

The buffers are designed to drive loads connected to ground. The outputs can source more than 20 mA over the full voltage range but have limited current sinking capability near  $V_{SS}$ . In split supply operation, symmetrical output swings can be obtained by restricting the output range to 2 V from either supply.

On-chip SMP18 buffers eliminate potential stability problems associated with external buffers; outputs are stable with capacitive loads up to 500 pF. However, since the SMP18's buffer outputs are not short circuit protected, care should be taken to avoid shorting any output to the supplies or ground.

### SIGNAL INPUT (Pin 3)

The signal input should be driven from a low impedance voltage source such as the output of an op amp. The op amp should have a high slew rate and fast settling time if the SMP18's acquisition time characteristics are to be maintained. As with all CMOS devices, all input voltages should be kept within range of the supply rails ( $V_{SS} \le V_{IN} \le V_{DD}$ ) to avoid the possibility of latchup. If single supply operation is desired, op amps such as the OP183 or AD820 that have input and output voltage compliances including ground, can be used to drive the inputs. Split supplies, such as  $\pm 7.5$  V, can be used with the SMP18.

### APPLICATION TIPS

All unused digital inputs should be connected to logic LOW. For analog inputs that may become temporarily disconnected, a resistor to  $V_{\rm DD}, V_{SS}$  or analog ground should be used with a value ranging from 200 k $\Omega$  to 1 M $\Omega.$

Do not apply signals to the SMP18 with power off unless the input current is limited to less than 10 mA.

### TYPICAL APPLICATIONS

### An 8-Channel Multiplexed D/A Converter

Figure 1 illustrates a typical demultiplexing function of the SMP18. It is used to sample-and-hold eight different output voltages corresponding to eight different digital codes from a D/A converter. The SMP18's droop rate of 40 mV/s requires a refresh once every 250 ms before the voltage drifts beyond 1/2 LSB accuracy (1 LSB of an 8-bit DAC is equivalent to 19.5 mV out of a full-scale voltage of 5 V). For a 10-bit DAC the refresh rate must be less than 60 ms, and for a 12-bit system, 15 ms. This implementation is very cost effective compared to using multiple DACs as the number of output channels increases.

CHANNEL DECODING

|   | PIN 9<br>C                  | PIN 10<br>B | PIN 11<br>A | PIN 6<br>INH | сн   | PIN |

|---|-----------------------------|-------------|-------------|--------------|------|-----|

|   |                             |             |             |              |      |     |

|   | 0                           | 0           | 0           | 0            | 0    | 13  |

|   | 0                           | 0           | 1           | 0            | 1    | 14  |

|   | 0                           | 1           | 0           | 0            | 2    | 15  |

|   | 0                           | 1           | 1           | 0            | 3    | 12  |

| - | <sup>-</sup> 1 <sup>-</sup> | 0           | 0           | 0            | 4    | 1   |

|   | 1                           | 0           | 1           | 0            | 5    | 5   |

|   | 1                           | 1           | 0           | 0            | 6    | 2   |

|   | 1                           | 1           | 1           | 0            | 7    | 4   |

|   | х                           | х           | х           | 1            | NONE | -   |

Figure 1. 8-Channel Multiplexed D/A Converter

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).