# 96-Bit, 220 MHz True-Color Video RAM-DAC

# ADV7160/ADV7162

#### FEATURES

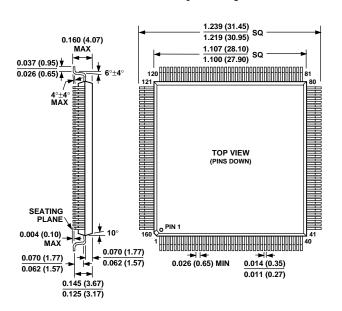

96-Bit Pixel Port for  $1600 \times 1280 \times 24$  Screen Resolution 220 MHz, 24-Bit (30-Bit Gamma Corrected) True-Color Triple 10-Bit "Gamma Correcting" D/A Converters 2% (max) DAC to DAC Color Matching Triple  $256 \times 10$  (256 x 30) Color Palette RAM On-Board User Definable Cursor ( $64 \times 64 \times 2$ ) **Three Color Overlay Cursor Palette RAM** Fully Programmable On-Board PLL RS-343A/RS-170 Compatible RGB Analog Outputs **Tri-Level SYNC Functionality TTL Compatible Digital Inputs** Standard MPU I/O Interface Programmable Pixel Port: 24-Bit, 16-Bit, 15-Bit & 8-Bit (Pseudo) **Pixel Data Serializer:** Multiplexed Pixel Input Ports; 2:1, 4:1, 8:1 +5 V CMOS Monolithic Construction 160-Lead Plastic Quad Flatpack (QFP): ADV7162

160-Lead "Thermally Enhanced" QFP (PQUAD): ADV7160

ADV is a registered trademark of Analog Devices, Inc.

#### **MODES OF OPERATION**

$1600 \times 1200 \times 30/24$ -Bit Resolution @ 85 Hz Screen Refresh  $1600 \times 1200 \times 16/15$ -Bit Resolution @ 85 Hz Screen Refresh  $1600 \times 1200 \times$  8-Bit Resolution @ 85 Hz Screen Refresh

#### APPLICATIONS

Windows Accelerators High Resolution, True Color Graphics Professional Color Prepress Imaging Digital TV (HDTV, Digital Video)

| SPEED GRADES | 5 |

|--------------|---|

| @ 220 MHz    |   |

| @ 170 MHz    |   |

| @ 140 MHz    |   |

#### **GENERAL DESCRIPTION**

The ADV7160/ADV7162® is a 96-bit pixel port Video RAM-DAC with color enhanced triple 10-bit DACs. The device also includes a PLL and  $64 \times 64$  hardware cursor. The ADV7160/ ADV7162 is specifically designed for use in the graphics subsystem of high performance, color graphics workstations and windows accelerators.

(Continued on page 15)

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1995

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

| <b>ADV7160/ADV7162—SPECIFICATIONS</b> $(V_{AA}^1 = +5 V; V_{REF} = +1.235 V; R_{SET} = 280 \Omega. IOR, IOG, IOB (R_L = 37.5 \Omega, C_L = 10 pF)$ . All specifications T <sub>MIN</sub> to T <sub>MAX</sub> <sup>2</sup> unless otherwise noted.) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                    | Min                   | Тур   | Max                        | Units        | Test Conditions/Comments                                                                 |

|----------------------------------------------|-----------------------|-------|----------------------------|--------------|------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                           |                       |       |                            |              | (DAC Gain Setting = 3996)                                                                |

| Resolution (Each DAC)                        |                       |       | 10                         | Bits         | (                                                                                        |

| Accuracy (Each DAC)                          |                       |       | 10                         | 210          |                                                                                          |

| Integral Nonlinearity                        |                       |       | $\pm 1$                    | LSB          |                                                                                          |

| Differential Nonlinearity                    |                       |       | $\pm 1$                    | LSB          | Guaranteed Monotonic                                                                     |

| Gray Scale Error                             |                       |       | $\pm 1$<br>$\pm 5$         | % Gray Scale | Guaranteed Wohlotome                                                                     |

| Coding                                       |                       |       | ± )                        | Binary       |                                                                                          |

|                                              |                       |       |                            | Dillary      |                                                                                          |

| DIGITAL INPUTS                               |                       |       |                            |              |                                                                                          |

| Input High Voltage, V <sub>INH</sub>         | 2                     |       |                            | V            |                                                                                          |

| Input Low Voltage, V <sub>INL</sub>          |                       |       | 0.8                        | V            |                                                                                          |

| Input Current, I <sub>IN</sub>               |                       |       | $\pm 10$                   | μA           | $V_{IN} = 0.4 V \text{ or } 2.4 V$                                                       |

| Input Capacitance, C <sub>IN</sub>           |                       | 10    |                            | pF           |                                                                                          |

| CLOCK INPUTS (CLOCK, CLOCK)                  |                       |       |                            |              |                                                                                          |

| Input High Voltage, V <sub>INH</sub>         | V <sub>AA</sub> - 1.0 |       |                            | v            |                                                                                          |

| Input Low Voltage, V <sub>INL</sub>          | VAA 1.0               |       | $V_{AA} - 1.6$             | v            |                                                                                          |

| Input Current, I <sub>IN</sub>               |                       |       | $t_{AA} = 1.0$<br>$\pm 10$ | μA           | $V_{IN} = 0.4 V \text{ or } 2.4 V$                                                       |

|                                              |                       |       | $\pm 10$<br>$\pm 50$       |              | $V_{IN} = 0.4 \text{ V of } 2.4 \text{ V}$<br>$V_{IN} = 0.4 \text{ V or } 2.4 \text{ V}$ |

| Input Current, I <sub>IN</sub> (JTAG Inputs) |                       | 10    | ±50                        | μA           | $v_{\rm IN} = 0.4  v  \text{or}  2.4  v$                                                 |

| Input Capacitance, C <sub>IN</sub>           |                       | 10    |                            | pF           |                                                                                          |

| DIGITAL OUTPUTS                              |                       |       |                            |              |                                                                                          |

| Output High Voltage, V <sub>OH</sub>         | 2.4                   |       |                            | V            | $I_{SOURCE} = 400 \ \mu A$                                                               |

| Output Low Voltage, V <sub>OL</sub>          |                       |       | 0.4                        | V            | $I_{SINK} = 3.2 \text{ mA}$                                                              |

| Floating-State Leakage Current               |                       |       | 20                         | μA           |                                                                                          |

| Floating-State Output Capacitance            |                       | 20    |                            | pF           |                                                                                          |

| ANALOG OUTPUTS                               |                       |       |                            |              | (DAC Gain Setting = 3996)                                                                |

| Gray Scale Current Range                     | 15                    |       | 22                         | mA           |                                                                                          |

| Output Current                               | 15                    |       |                            |              |                                                                                          |

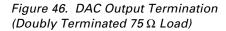

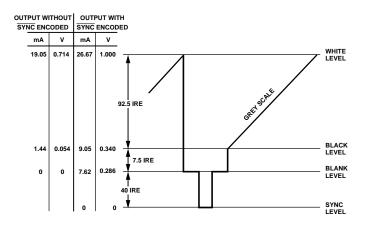

| White Level Relative to Blank                | 17.69                 | 19.05 | 20.40                      | mA           |                                                                                          |

| White Level Relative to Black                | 16.74                 | 17.62 | 18.50                      | mA           |                                                                                          |

| Black Level Relative to Black                | 0.95                  | 1.44  | 1.90                       | mA           |                                                                                          |

|                                              | 0.95                  |       |                            |              | Suma Disablad                                                                            |

| Blank Level                                  | -                     | 5     | 50                         | μΑ           | Sync Disabled                                                                            |

| Blank Level                                  | 6.29                  | 7.62  | 8.96                       | mA           | Sync Enabled                                                                             |

| Sync Level                                   | 0                     | 5     | 50                         | μA           |                                                                                          |

| Tri-Sync Level Relative to Blank             | 6.29                  | 7.62  | 8.96                       | mA           |                                                                                          |

| LSB Size                                     |                       | 17.22 | _                          | μA           |                                                                                          |

| DAC to DAC Matching                          |                       | 1     | 3                          | %            |                                                                                          |

| Output Compliance, V <sub>OC</sub>           | 0                     |       | +1.4                       | V            |                                                                                          |

| Output Impedance, R <sub>OUT</sub>           |                       | 30    |                            | kΩ           |                                                                                          |

| Output Capacitance, C <sub>OUT</sub>         |                       |       | 30                         | pF           | $I_{OUT} = 0 mA$                                                                         |

| VOLTAGE REFERENCE                            |                       |       |                            |              |                                                                                          |

| Voltage Reference Range, V <sub>REF</sub>    | 1.14                  | 1.235 | 1.26                       | V            | $V_{REF} = 1.235$ V for Specified Performance                                            |

| Input Current, I <sub>VREF</sub>             |                       | 5     |                            | μA           |                                                                                          |

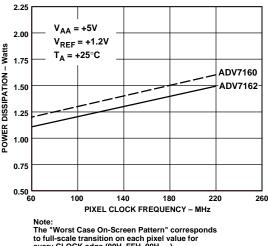

| POWER REQUIREMENTS                           |                       | -     |                            |              |                                                                                          |

|                                              |                       | 5     |                            | v            |                                                                                          |

| $V_{AA}$ $I_{AA}^{3}$                        |                       | )     | 475                        | mA           | For 220 MHz Operation (ADV7160)                                                          |

| $\mathbf{I}_{AA}$                            |                       |       |                            |              |                                                                                          |

|                                              |                       |       | 440                        | mA           | For 170 MHz Operation (ADV7160)                                                          |

| <b>T</b> 3                                   |                       |       | 410                        | mA           | For 140 MHz Operation (ADV7160)                                                          |

| $I_{AA}{}^3$                                 |                       |       | 450                        | mA           | For 220 MHz Operation (ADV7162)                                                          |

|                                              |                       |       | 400                        | mA           | For 170 MHz Operation (ADV7162)                                                          |

|                                              |                       | 0.1   | 360                        | mA           | For 140 MHz Operation (ADV7162)                                                          |

| Power Supply Rejection Ratio                 |                       | 0.1   |                            | %/%          | $COMP = 0.1 \ \mu F$                                                                     |

| DYNAMIC PERFORMANCE                          |                       |       |                            |              |                                                                                          |

| Clock and Data Feedthrough <sup>4, 5</sup>   |                       | -30   |                            | dB           |                                                                                          |

| Glitch Impulse                               |                       | 50    |                            | pV secs      |                                                                                          |

| DAC to DAC Crosstalk <sup>6</sup>            |                       | -23   |                            | dB           |                                                                                          |

| NOTES                                        | 1                     |       |                            | 1            | 1                                                                                        |

NOTES <sup>1</sup>±5% for all versions. <sup>2</sup>Temperature range ( $T_{MIN}$  to  $T_{MAX}$ ): 0°C to +70°C. <sup>3</sup>Pixel Port is continuously clocked with data corresponding to a linear ramp.  $T_J = 100$ °C. <sup>4</sup>Clock and data feedthrough is a function of the amount of overshoot and undershoot on the digital inputs. Glitch impulse includes clock and data feedthrough. <sup>5</sup>TTL input values are 0 V to 3 V, with input rise/fall times ≤3 ns, measured the 10% and 90% points. Timing reference points at 50% for inputs and outputs.

<sup>6</sup>DAC to DAC Crosstalk is measured by holding one DAC high while the other two are making low to high and high to low transitions.

Specifications subject to change without notice.

$\label{eq:timescale} \textbf{TIMING CHARACTERISTICS}^{1} \quad \begin{array}{l} (V_{AA}{}^2=+5 \ V; \ V_{REF}=+1.235 \ V; \ R_{SET}=280 \ \Omega. \ \ \text{IOR, IOG, IOB} \ (R_L=37.5 \ \Omega, \ C_L=10 \ \text{pF}). \ \ \text{All specifications } T_{MIN} \ \ \text{to } T_{MAX}{}^3 \ \ \text{unless otherwise noted.} \end{array}$

| Parameter                    | 220 MHz<br>Version | 170 MHz<br>Version | 140 MHz<br>Version | Units   | Conditions/Comments           |

|------------------------------|--------------------|--------------------|--------------------|---------|-------------------------------|

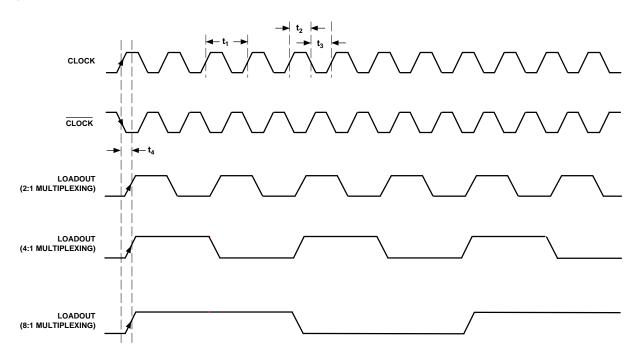

| f <sub>CLOCK</sub>           | 220                | 170                | 140                | MHz max | Pixel CLOCK Rate              |

| t <sub>1</sub>               | 4.5                | 5.88               | 7.14               | ns min  | Pixel CLOCK Cycle Time        |

| t <sub>2</sub>               | 2.0                | 2.5                | 2.86               | ns min  | Pixel CLOCK High Time         |

| t <sub>3</sub>               | 2.0                | 2.5                | 2.86               | ns min  | Pixel CLOCK Low Time          |

| t <sub>4</sub>               | 10                 | 10                 | 10                 | ns max  | Pixel CLOCK to LOADOUT Delay  |

| f <sub>LOADIN</sub>          |                    |                    |                    |         | LOADIN Clocking Rate          |

| 2:1 Multiplexing             | 110                | 85                 | 70                 | MHz max |                               |

| 4:1 Multiplexing             | 55                 | 42.5               | 35                 | MHz max |                               |

| 8:1 Multiplexing             | 27.5               | 21.25              | 17.5               | MHz max |                               |

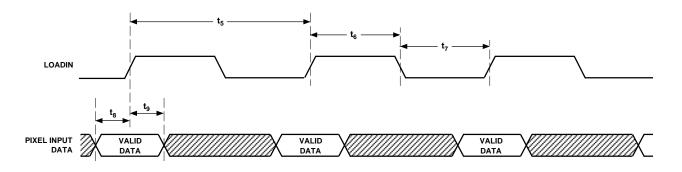

| t <sub>5</sub>               |                    |                    |                    |         | LOADIN Cycle Time             |

| 2:1 Multiplexing             | 9.1                | 11.77              | 14.29              | ns min  |                               |

| 4:1 Multiplexing             | 18.18              | 23.53              | 28.58              | ns min  |                               |

| 8:1 Multiplexing             | 36.36              | 47.1               | 57.16              | ns min  |                               |

| t <sub>6</sub>               |                    |                    |                    |         | LOADIN High Time              |

| 2:1 Multiplexing             | 4                  | 5                  | 6                  | ns min  |                               |

| 4:1 Multiplexing             | 8                  | 9                  | 12                 | ns min  |                               |

| 8:1 Multiplexing             | 15                 | 18                 | 23                 | ns min  |                               |

| t <sub>7</sub>               |                    |                    |                    |         | LOADIN Low Time               |

| 2:1 Multiplexing             | 4                  | 5                  | 6                  | ns min  |                               |

| 4:1 Multiplexing             | 8                  | 9                  | 12                 | ns min  |                               |

| 8:1 Multiplexing             | 15                 | 18                 | 23                 | ns min  |                               |

| t <sub>8</sub>               | 0                  | 0                  | 0                  | ns min  | Pixel Data Setup Time         |

| t <sub>9</sub>               | 5                  | 5                  | 5                  | ns min  | Pixel Data Hold Time          |

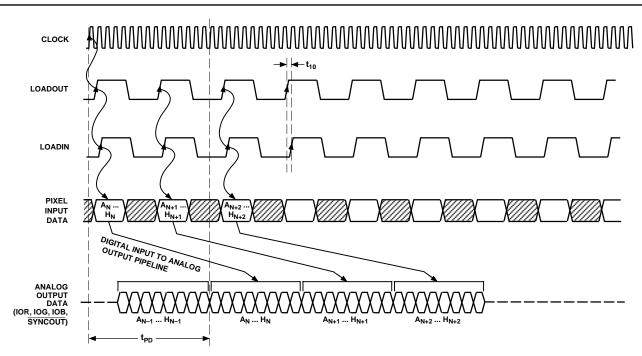

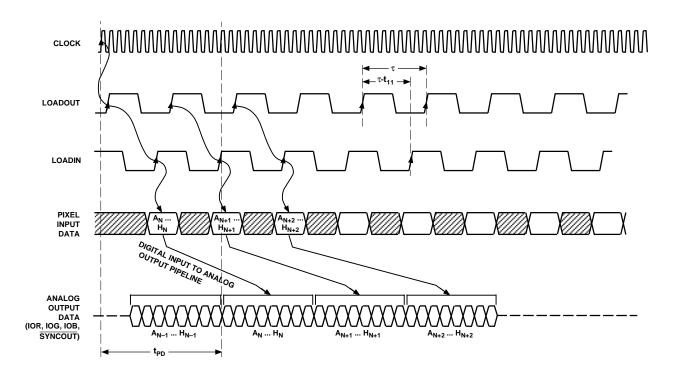

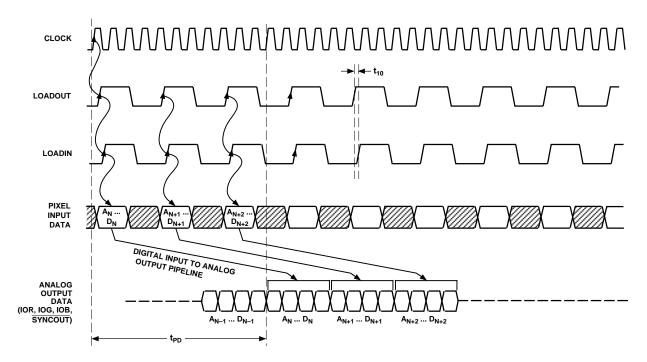

| t <sub>10</sub>              | 0                  | 0                  | 0                  | ns min  | LOADOUT to LOADIN Delay       |

| $\tau - t_{11}^{5}$          | τ-5                | τ-5                | τ-5                | ns max  | LOADOUT to LOADIN Delay       |

| t <sub>PD</sub> <sup>6</sup> |                    |                    |                    |         | Pipeline Delay                |

| 2:1 Multiplexing             | 9                  | 9                  | 9                  | CLOCKs  | $(1 \times CLOCK = t_1)$      |

| 4:1 Multiplexing             | 11                 | 11                 | 11                 | CLOCKs  |                               |

| 8:1 Multiplexing             | 15                 | 15                 | 15                 | CLOCKs  |                               |

| t <sub>12</sub>              | 10                 | 10                 | 10                 | ns max  | Pixel CLOCK to PRGCKOUT Delay |

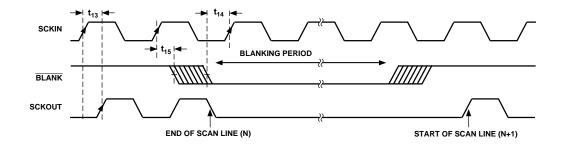

| t <sub>13</sub>              | 5                  | 5                  | 5                  | ns max  | SCKIN to SCKOUT Delay         |

| t <sub>14</sub>              | 5                  | 5                  | 5                  | ns min  | BLANK to SCKIN Setup Time     |

| t <sub>15</sub>              | 0                  | 0                  | 0                  | ns min  | BLANK to SCKIN Hold Time      |

#### **CLOCK CONTROL AND PIXEL PORT<sup>4</sup>**

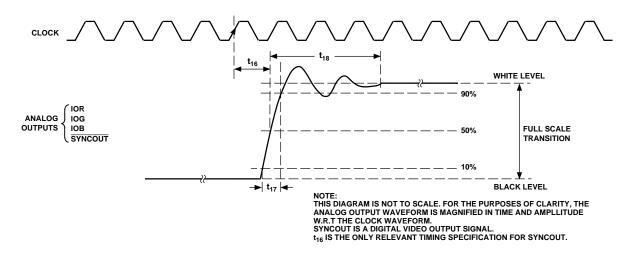

#### ANALOG OUTPUTS<sup>7</sup>

| Parameter                                                                | 220 MHz<br>Version      | 170 MHz<br>Version      | 140 MHz<br>Version      | Units                                          | Conditions/Comments                                                                                            |

|--------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| t <sub>16</sub><br>t <sub>17</sub><br>t <sub>18</sub><br>t <sub>SK</sub> | 25<br>1<br>25<br>2<br>0 | 25<br>1<br>25<br>2<br>0 | 25<br>1<br>25<br>2<br>0 | ns typ<br>ns typ<br>ns typ<br>ns max<br>ns typ | Analog Output Delay<br>Analog Output Rise/Fall Time<br>Analog Output Transition Time<br>RGB Analog Output Skew |

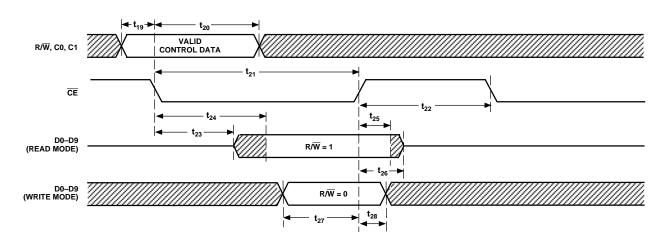

#### MPU PORT<sup>8,9</sup>

| Parameter                    | 220 MHz<br>Version | 170 MHz<br>Version | 140 MHz<br>Version | Units  | Conditions/Comments                                      |

|------------------------------|--------------------|--------------------|--------------------|--------|----------------------------------------------------------|

| t <sub>19</sub>              | 0                  | 0                  | 0                  | ns min | $R/\overline{W}$ , C0, C1 to $\overline{CE}$ Setup Time  |

| t <sub>20</sub>              | 10                 | 10                 | 10                 | ns min | $R/\overline{W}$ , C0, C1 to $\overline{CE}$ Hold Time   |

| t <sub>21</sub>              | 45                 | 45                 | 45                 | ns min | $\overline{\text{CE}}$ Low Time                          |

| t <sub>22</sub>              | 25                 | 25                 | 25                 | ns min | $\overline{\text{CE}}$ High Time                         |

| t <sub>23</sub> <sup>8</sup> | 5                  | 5                  | 5                  | ns min | $\overline{\text{CE}}$ Asserted to Data-Bus Driven       |

| $t_{24}^{9}$                 | 45                 | 45                 | 45                 | ns max | $\overline{\text{CE}}$ Asserted to Data Valid            |

| t <sub>25</sub> 9            | 20                 | 20                 | 20                 | ns max | $\overline{\text{CE}}$ Disabled to Data-Bus Three-Stated |

| $t_{26}^{9}$                 | 5                  | 5                  | 5                  | ns min | $\overline{\text{CE}}$ Disabled to Data Invalid          |

| t <sub>27</sub>              | 20                 | 20                 | 20                 | ns min | Write Data (D0–D9) Setup Time                            |

| t <sub>28</sub>              | 5                  | 5                  | 5                  | ns min | Write Data (D0–D9) Hold Time                             |

NOTES

General Notes

<sup>1</sup>TTL input values are 0 to 3 volts, with input rise/fall times  $\leq$  3 ns, measured between the 10% and 90% points.

ECL inputs (CLOCK,  $\overline{\text{CLOCK}}$ ) are  $V_{AA}$ -0.8 V to  $V_{AA}$ -1.8 V, with input rise/fall times  $\leq 2$  ns, measured between the 10% and 90% points.

Timing reference points at 50% for inputs and outputs.

Analog output load  $\leq 10 \text{ pF}$ .

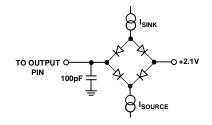

Data-Bus (D0-D9) loaded as shown in Figure 1.

Digital output load for LOADOUT, PRGCKOUT & SCKOUT ≤ 30 pF.

$^{2}\pm5\%$  for all versions

<sup>3</sup>Temperature range ( $T_{MIN}$  to  $T_{MAX}$ ); 0°C to +70°C. Notes on PIXEL PORT

<sup>4</sup>Pixel Port consists of the following inputs:

Pixel Inputs: RED [A, B, C, D] GREEN [A, B, C, D] BLUE [A, B, C, D]

Palette Selects:

PS0 [A, B, C, D];

PS1[A, B, C, D]

Pixel Controls:

SYNC, BLANK, TRISYNC, ODD/EVEN

Clock Inputs:

CLOCK, CLOCK, LOADIN, SCKIN

Clock Outputs:

LOADOUT, PRGCKOUT, SCKOUT

${}^{5}\tau$  is the LOADOUT Cycle Time and is a function of the Pixel CLOCK Rate and the Multiplexing Mode:

2:1 multiplexing;  $\tau = \text{CLOCK} \times 2$ =  $2 \times t_1$ ns

4:1 multiplexing;  $\tau = CLOCK \times 4$  $= 4 \times t_1$ ns

$\tau = CLOCK \times 8$ 8:1 multiplexing;  $= 8 \times t_1$ ns

<sup>6</sup>These fixed values for Pipeline Delay are valid under conditions where t<sub>10</sub> and τ-t<sub>11</sub> are met. If either t<sub>10</sub> or τ-t<sub>11</sub> are not met, the part will operate but the Pipeline Delay is increased.

Notes on ANALOG OUTPUTS

<sup>7</sup>Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of full-scale transition.

Output rise/fall time measured between the 10% and 90% points of full-scale transition.

Transition time measured from the 50% point of full scale transition to the output remaining within 2% of the final output value. (Transition time does not include clock and data feedthrough).

Notes on MPU PORT

<sup>8</sup>t<sub>23</sub> and t<sub>24</sub> are measured with the load circuit of Figure 1 and defined as the time required for an output to cross 0.4 V or 2.4 V.

<sup>9</sup>t<sub>25</sub> and t<sub>26</sub> are derived from the measured time taken by the data outputs to change by 0.5 V when loaded with the circuit of Figure 1. The measured numbers are then extrapolated back to remove the effects of charging the 100 pF capacitor. This means that the times t<sub>25</sub> and t<sub>26</sub>, quoted in the Timing Characteristics are the true values for the device and as such are independent of external loading capacitances.

Specifications subject to change without notice.

Figure 1. Load Circuit for Databus Access and Relinquish Times

# $\label{eq:timescale} \textbf{TIMING CHARACTERISTICS (Cont.)}^1 \quad (V_{AA}{}^2 = +5 \text{ V}; \ V_{REF} = +1.235 \text{ V}; \ R_{SET} = 280 \ \Omega. \ \text{IOR, IOG, IOB (R}{}_{L} = 37.5 \ \Omega, \ C_{L} = 10 \ \text{pF}). \\ \text{All specifications T}_{\text{MIN}} \ \text{to T}_{\text{MAX}}{}^3 \ \text{unless otherwise noted.)}$

#### JTAG PORT

| Parameter                                        | All Versions | Units   | Conditions/Comments |

|--------------------------------------------------|--------------|---------|---------------------|

| PLL PERFORMANCE <sup>4</sup>                     |              |         |                     |

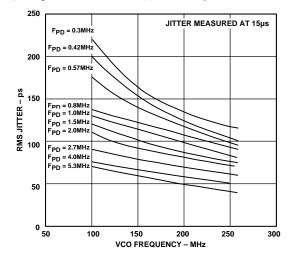

| Jitter                                           | 250          | ps rms  | 1σ                  |

| PLL REFERENCE INPUT                              |              |         |                     |

| PLL <sub>REF</sub> Frequency                     | 900          | kHz min |                     |

|                                                  | 40           | MHz max |                     |

| $V_{IH}$                                         | 2.0          | V max   |                     |

| V <sub>IL</sub>                                  | 0.8          | V min   |                     |

| PLL <sub>REF</sub> Period                        | 25           | ns min  |                     |

|                                                  | 1.67         | µs max  |                     |

| PLL <sub>REF</sub> Duty Cycle                    | 40           | % min   |                     |

|                                                  | 60           | % max   |                     |

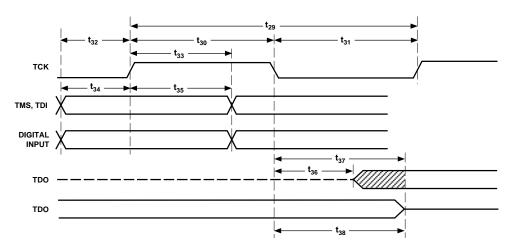

| JTAG PERFORMANCE                                 |              |         |                     |

| TCK Frequency, t <sub>29</sub>                   | 20           | MHz max |                     |

| TCK High Time, t <sub>30</sub>                   | 15           | ns min  |                     |

| $\overline{\text{TCK}}$ Low Time, $t_{31}$       | 15           | ns min  |                     |

| TDI, TMS Setup Time, t <sub>32</sub>             | 15           | ns max  |                     |

| TDI, TMS Hold Time, t <sub>33</sub>              | 15           | ns max  |                     |

| Digital Input to TCK Setup Time, t <sub>34</sub> | 15           | ns max  |                     |

| Digital Input to TCK Hold Time, t <sub>35</sub>  | 15           | ns max  |                     |

| TCLK to TDO Drive, t <sub>36</sub>               | 0            | ns min  |                     |

| TCLK to TDO Valid, t <sub>37</sub>               | 20           | ns min  |                     |

| TCLK to TDO Three-State, t <sub>38</sub>         | 5            | ns min  |                     |

|                                                  | 15           | ns max  |                     |

NOTES  $^{1}$ TTL input values are 0 to 3 volts, with input rise/fall times  $\leq$  3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs.  $^{2}\pm5\%$  for all versions.

<sup>3</sup>Temperature range ( $T_{MIN}$  to  $T_{MAX}$ ); 0°C to +70°C. <sup>4</sup>Jitter is measured by triggering on the output clock, delayed by 15 µs and then measuring the time period from the trigger edge to the next edge of the output clock after the delay. This measurement is repeated multiple times and the RMS value is determined.

Specifications subject to change without notice.

Figure 2. JTAG Timing

## **Timing Waveforms**

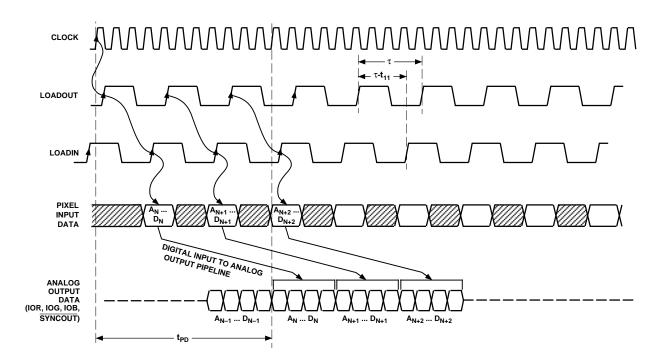

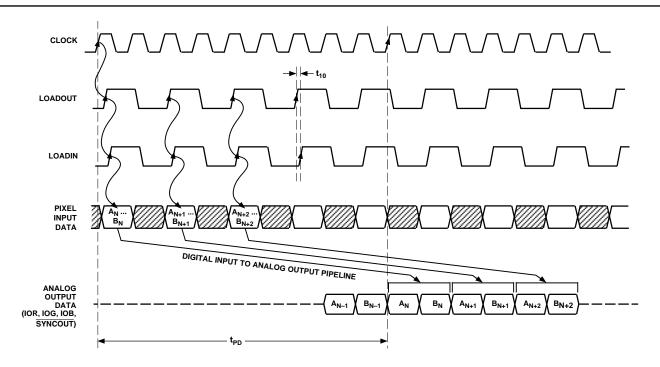

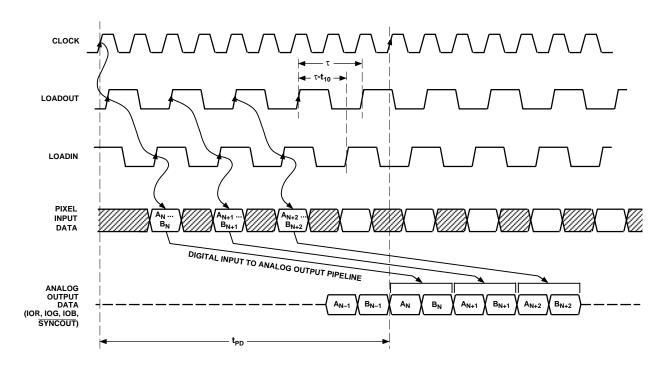

Figure 3. LOADOUT vs. Pixel Clock Input (CLOCK, CLOCK)

Figure 4. LOADIN vs. Pixel Input Data

Figure 5. Pixel Input to Analog Output Pipeline with Minimum LOADOUT to LOADIN Delay (8:1 Multiplex Mode)

Figure 6. Pixel Input to Analog Output Pipeline with Maximum LOADOUT to LOADIN Delay (8:1 Multiplex Mode)

Figure 7. Pixel Input to Analog Output Pipeline with Minimum LOADOUT to LOADIN Delay (4:1 Multiplex Mode)

Figure 8. Pixel Input to Analog Output Pipeline with Maximum LOADOUT to LOADIN Delay (4:1 Multiplex Mode)

Figure 9. Pixel Input to Analog Output Pipeline with Minimum LOADOUT to LOADIN Delay (2:1 Multiplex Mode)

Figure 10. Pixel Input to Analog Output Pipeline with Maximum LOADOUT to LOADIN Delay (2:1 Multiplex Mode)

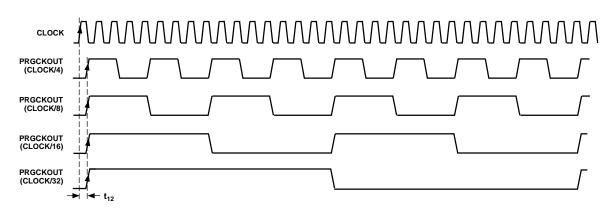

Figure 11. Pixel Clock Input vs. Programmable Clock Output (PRGCKOUT)

Figure 12. Video Data Shift Clock Input (SCKIN) & BLANK vs. Video Data Shift Clock Output (SCKOUT)

Figure 13. Analog Output Response vs. CLOCK

Figure 14. Microprocessor Port (MPU) Interface Timing

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| V <sub>AA</sub> to GND                                                     |

|----------------------------------------------------------------------------|

| Voltage on Any Digital Pin $\ldots$ GND – 0.5 V to V <sub>AA</sub> + 0.5 V |

| Ambient Operating Temperature $(T_A) \dots 0^{\circ}C$ to $+70^{\circ}C$   |

| Storage Temperature $(T_S)$ 65°C to +150°C                                 |

| Junction Temperature $(T_J)$ +150°C                                        |

| Lead Temperature (Soldering, 10 secs) +260°C                               |

| Vapor Phase Soldering (1 minute) +220°C                                    |

| Analog Outputs to $GND^2$ $GND - 0.5 V$ to $V_{AA}$                        |

#### NOTES

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. <sup>2</sup>Analog Output Short Circuit to any Power Supply or Common can be of an indefinite duration.

#### **ORDERING INFORMATION<sup>1, 2, 3</sup>**

| Dot Clock Speed                                        |                                                        |                                                        |  |  |

|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|--|

| 220 MHz                                                | 170 MHz                                                | 140 MHz                                                |  |  |

| ADV7160KS220 <sup>3</sup><br>ADV7162KS220 <sup>4</sup> | ADV7160KS170 <sup>3</sup><br>ADV7162KS170 <sup>4</sup> | ADV7160KS140 <sup>3</sup><br>ADV7162KS140 <sup>4</sup> |  |  |

NOTES

<sup>1</sup>All devices are specified for 0°C to +70°C operation.

<sup>2</sup>Contact Sales Office for latest information on package design.

<sup>3</sup>ADV7160 is packaged in a 160-pin plastic power quad flatpack, QFP with heatsink embedded.

<sup>4</sup>ADV7162 is packaged in a standard 160-pin plastic quad flatpack, QFP.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADV7160/ADV7162 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

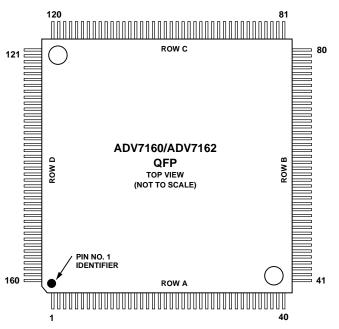

#### 160-Lead QFP Configuration

| Pin No. | Mnemonic           | Pin No. | Mnemonic        | Pin No. | Mnemonic         | Pin No. | Mnemonic        |

|---------|--------------------|---------|-----------------|---------|------------------|---------|-----------------|

| 1       | G2 <sub>A</sub>    | 41      | CLOCK           | 81      | D9               | 121     | R1 <sub>C</sub> |

| 2       | G2 <sub>B</sub>    | 42      | SCKIN           | 82      | D8               | 122     | R1 <sub>D</sub> |

| 3       | G2 <sub>C</sub>    | 43      | SCKOUT          | 83      | D7               | 123     | R2 <sub>A</sub> |

| 4       | G2 <sub>D</sub>    | 44      | $V_{AA}$        | 84      | D6               | 124     | R2 <sub>B</sub> |

| 5       | G3 <sub>A</sub>    | 45      | PRGCKOUT        | 85      | D5               | 125     | R2 <sub>C</sub> |

| 6       | G3 <sub>B</sub>    | 46      | GND             | 86      | D4               | 126     | R2 <sub>D</sub> |

| 7       | G3 <sub>C</sub>    | 47      | LOADOUT         | 87      | D3               | 127     | R3 <sub>A</sub> |

| 8       | G3 <sub>D</sub>    | 48      | LOADIN          | 88      | D2               | 128     | R3 <sub>B</sub> |

| 9       | G4 <sub>A</sub>    | 49      | $B0_A$          | 89      | D1               | 129     | R3 <sub>C</sub> |

| 10      | G4 <sub>B</sub>    | 50      | $B0_B$          | 90      | D0               | 130     | R3 <sub>D</sub> |

| 11      | G4 <sub>C</sub>    | 51      | B0 <sub>C</sub> | 91      | C1               | 131     | R4 <sub>A</sub> |

| 12      | G4 <sub>D</sub>    | 52      | B0 <sub>D</sub> | 92      | C0               | 132     | V <sub>AA</sub> |

| 13      | G5 <sub>A</sub>    | 53      | B1 <sub>A</sub> | 93      | $R/\overline{W}$ | 133     | V <sub>AA</sub> |

| 14      | G5 <sub>B</sub>    | 54      | B1 <sub>B</sub> | 94      | CE               | 134     | GND             |

| 15      | G5 <sub>C</sub>    | 55      | B1 <sub>C</sub> | 95      | TCK              | 135     | GND             |

| 16      | G5 <sub>D</sub>    | 56      | B1 <sub>D</sub> | 96      | TMS              | 136     | R4 <sub>B</sub> |

| 17      | G6 <sub>A</sub>    | 57      | $B2_A$          | 97      | GND              | 137     | R4 <sub>C</sub> |

| 18      | G6 <sub>B</sub>    | 58      | $B2_B$          | 98      | V <sub>AA</sub>  | 138     | R4 <sub>D</sub> |

| 19      | G6 <sub>C</sub>    | 59      | B2 <sub>C</sub> | 99      | TDO              | 139     | R5 <sub>A</sub> |

| 20      | G6 <sub>D</sub>    | 60      | B2 <sub>D</sub> | 100     | TDI              | 140     | R5 <sub>B</sub> |

| 21      | G7 <sub>A</sub>    | 61      | B3 <sub>A</sub> | 101     | SYNCOUT          | 141     | R5 <sub>C</sub> |

| 22      | V <sub>AA</sub>    | 62      | B3 <sub>B</sub> | 102     | TRISYNC          | 142     | R5 <sub>D</sub> |

| 23      | V <sub>AA</sub>    | 63      | B3 <sub>C</sub> | 103     | ODD/EVEN         | 143     | R6 <sub>A</sub> |

| 24      | GND                | 64      | B3 <sub>D</sub> | 104     | SYNC             | 144     | R6 <sub>B</sub> |

| 25      | GND                | 65      | $B4_A$          | 105     | BLANK            | 145     | R6 <sub>C</sub> |

| 26      | V <sub>AA</sub>    | 66      | $B4_B$          | 106     | V <sub>REF</sub> | 146     | R6 <sub>D</sub> |

| 27      | GND                | 67      | $B4_C$          | 107     | IOB              | 147     | R7 <sub>A</sub> |

| 28      | PLL <sub>REF</sub> | 68      | $B4_D$          | 108     | COMP             | 148     | R7 <sub>B</sub> |

| 29      | G7 <sub>B</sub>    | 69      | B5 <sub>A</sub> | 109     | R <sub>SET</sub> | 149     | R7 <sub>C</sub> |

| 30      | G7 <sub>C</sub>    | 70      | $B5_B$          | 110     | V <sub>AA</sub>  | 150     | GND             |

| 31      | G7 <sub>D</sub>    | 71      | B5 <sub>C</sub> | 111     | V <sub>AA</sub>  | 151     | V <sub>AA</sub> |

| 32      | PS0 <sub>A</sub>   | 72      | B5 <sub>D</sub> | 112     | GND              | 152     | R7 <sub>D</sub> |

| 33      | PS0 <sub>B</sub>   | 73      | $B6_A$          | 113     | IOG              | 153     | G0 <sub>A</sub> |

| 34      | PS0 <sub>C</sub>   | 74      | B6 <sub>B</sub> | 114     | IOR              | 154     | G0 <sub>B</sub> |

| 35      | PS0 <sub>D</sub>   | 75      | B6 <sub>C</sub> | 115     | R0 <sub>A</sub>  | 155     | G0 <sub>C</sub> |

| 36      | PS1 <sub>A</sub>   | 76      | B6 <sub>D</sub> | 116     | R0 <sub>B</sub>  | 156     | G0 <sub>D</sub> |

| 37      | PS1 <sub>B</sub>   | 77      | B7 <sub>A</sub> | 117     | R0 <sub>C</sub>  | 157     | G1 <sub>A</sub> |

| 38      | PS1 <sub>C</sub>   | 78      | $B7_B$          | 118     | R0 <sub>D</sub>  | 158     | G1 <sub>B</sub> |

| 39      | PS1 <sub>D</sub>   | 79      | B7 <sub>C</sub> | 119     | R1 <sub>A</sub>  | 159     | G1 <sub>C</sub> |

| 40      | CLOCK              | 80      | B7 <sub>D</sub> | 120     | R1 <sub>B</sub>  | 160     | G1 <sub>D</sub> |

#### ADV7160/ADV7162 PIN ASSIGNMENTS

#### PIN FUNCTION DESCRIPTION

| Mnemonic                                                                                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\operatorname{RED} (\operatorname{R0}_{A} \dots \operatorname{R0}_{B} - \operatorname{R7}$ | <ul> <li><sup>7</sup>A R7<sub>D</sub>), GREEN (G0<sub>A</sub> G0<sub>D</sub> - G7<sub>A</sub> G7<sub>D</sub>), BLUE (B0<sub>A</sub> B0<sub>D</sub> - B7<sub>A</sub> B7<sub>D</sub>):<br/>Pixel Port (TTL Compatible Inputs): 96 pixel select inputs, with 8 bits each for Red, Green and Blue.<br/>Each bit is multiplexed [A-D] 4:1 or 2:1. It can be configured for 24-Bit True-Color Data, 8-Bit<br/>Pseudo-Color Data, 16-Bit True-Color and 15-Bit True-Color Data formats. In 8-Bit Pseudo-Color<br/>Mode, there is a special case whereby 8:1 multiplexing is also available. It will be explained in more<br/>detail later. Pixel Data is latched into the device on the rising edge of LOADIN.</li> </ul> |

| $PS0_A \dots PS0_D$ , $PS1_A$ .                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LOADIN                                                                                      | Pixel Data Load Input (TTL Compatible Input): This input latches the multiplexed pixel data, in-<br>cluding PS0-PS1, BLANK, TRISYNC, SYNC and ODD/EVEN into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LOADOUT                                                                                     | Pixel Data Load Output (TTL Compatible Output): This output control signal runs at a divided down frequency of the pixel clock. Its frequency is a function of the multiplex rate. It can be used to directly or indirectly drive LOADIN.<br>$f_{LOADOUT} = f_{CLOCK}/M$                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                             | where<br>(M = 2 for 2:1 Multiplex Mode)<br>(M = 4 for 4:1 Multiplex Mode)<br>(M = 8 for 8:1 Multiplex Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PRGCKOUT                                                                                    | Programmable Clock Output (TTL Compatible Output): This output control signal runs at a divided down frequency of the pixel Clock. Its frequency is user programmable and is determined by bits CR30 and CR31 of Command Register 3.<br>$f_{PRGCKOUT} = f_{CLOCK}/N$<br>where N = 4, 8, 16 & 32                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCKIN                                                                                       | Video Shift Clock Input (TTL Compatible Input): The signal on this input is internally gated syn-<br>chronously with the BLANK signal. The resultant output, SCKOUT, is a video clocking signal that<br>is stopped during video blanking periods. It is normally driven by a divided down version of the<br>CLOCK frequency.                                                                                                                                                                                                                                                                                                                                                                                       |

| SCKOUT                                                                                      | Video Shift Clock Output (TTL Compatible Output): This output is a synchronously gated version of SCKIN and BLANK. SCKOUT is a video clocking signal that is stopped during video blanking periods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLOCK, CLOCK                                                                                | Clock Inputs (ECL Compatible Inputs): These differential clock inputs are designed to be driven by ECL logic levels configured for single supply (+5 V) operation. The clock rate is normally the pixel clock rate of the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PLL <sub>REF</sub>                                                                          | PLL Clock Input (TTL Compatible Input): This clock input is designed to be driven by TTL logic levels. The PLL is then configured to output a specific frequency depending on the PLL Registers. See PLL section for more detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BLANK                                                                                       | Composite Blank (TTL Compatible Input): This video control signal drives the analog outputs to the blanking level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

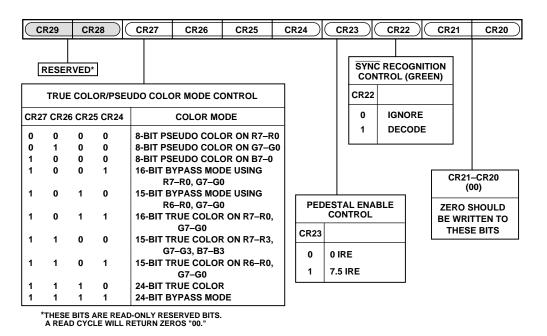

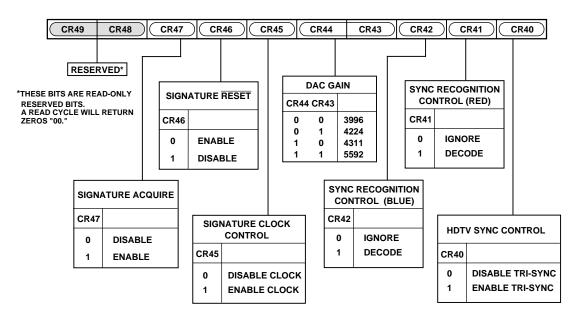

| SYNC                                                                                        | Composite-Sync Input (TTL Compatible Input): This video control signal drives any of the analog outputs to the SYNC level. It is only asserted during the blanking period. CR22 in Command Register 2 must be set if <u>SYNC</u> is to be decoded onto the IOG analog output, CR41 in Command Register 4 must be set if <u>SYNC</u> is to be decoded onto the IOR analog output, CR42 in Command Register 4 must be set if <u>SYNC</u> is to be decoded onto the IOB analog output, otherwise the <u>SYNC</u> input is ignored.                                                                                                                                                                                    |

| Mnemonic                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| SYNCOUT                 | Composite-Sync Output (TTL Compatible Output). This video output is a delayed version of $\overline{\text{SYNC}}$ . The delay corresponds to the number of pipeline stages of the device.                                                                                                                                                                                                                                                                                                          |                |  |  |  |  |  |

| TRISYNC                 | Composite-Sync HDTV Control (TTL Compatible Output). This video input is enabled using Bit CR17 in Command Register 1. When $\overline{\text{TRISYNC}}$ is low, any DAC output which has Sync enabled goes to the tri-sync level. As with the $\overline{\text{SYNC}}$ input, it should only be activated while $\overline{\text{BLANK}}$ is low.                                                                                                                                                  |                |  |  |  |  |  |

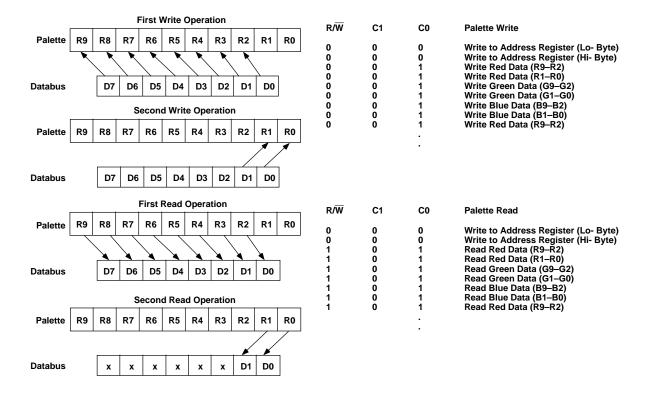

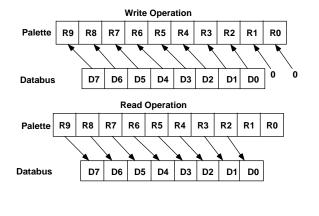

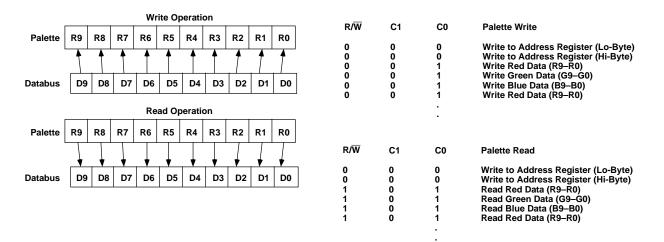

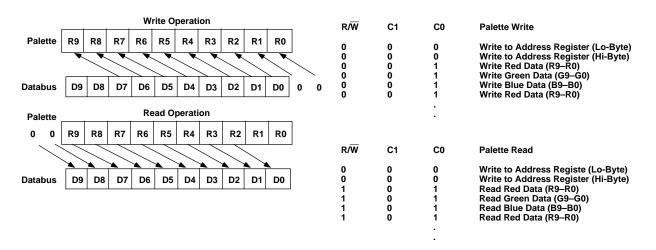

| D9-D0                   | Data Bus (TTL Compatible Input/Output Bus). Data, including color palette values and device co<br>trol information is written to and read from the device over this 10-bit, bidirectional databus. 10-bit<br>data or 8-bit data can be used. The databus can be configured for either 10-bit parallel data or byte<br>data (8+2) as well as standard 8-bit data. Any unused bits of the data bus should be terminated<br>through a resistor to either the digital power plane ( $V_{CC}$ ) or GND. |                |  |  |  |  |  |

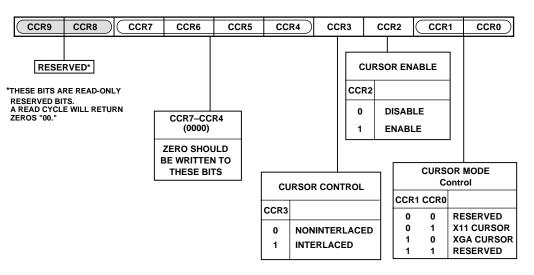

| ODD/EVEN                | Odd/Even Control (TTL Compatible Input). This input indicates which field of the frame is being displayed. It is required to ensure proper operation of the ADV7160/ADV7162 cursor when inter-<br>laced display mode is selected. It is ignored when noninterlaced display mode is selected. This input should change only during the vertical blank period. It is assumed that an odd field will always follow an even field and vice versa.                                                      |                |  |  |  |  |  |

| CE                      | Chip Enable (TTL Compatible Input). This input must be at Logic "0" when writing to or readin from the device over the data bus (D0–D9). Internally, data is latched on the rising edge of $\overline{CE}$ .                                                                                                                                                                                                                                                                                       | ıg             |  |  |  |  |  |

| $R/\overline{W}$        | Read/Write Control (TTL Compatible Input). This input determines whether data is written to or read from the device's registers and color palette RAM. $R/\overline{W}$ and $\overline{CE}$ must be at Logic "0" to write data to the part. $R/\overline{W}$ must be at Logic "1" and $\overline{CE}$ at Logic "0" to read from the device.                                                                                                                                                        |                |  |  |  |  |  |

| C0, C1                  | Command Controls (TTL Compatible Inputs). These inputs determine the type of read or write operation being performed on the device over the data bus, (see Interface Truth Table). Data on these inputs is latched on the falling edge of $\overline{CE}$ .                                                                                                                                                                                                                                        |                |  |  |  |  |  |

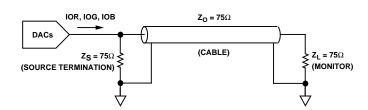

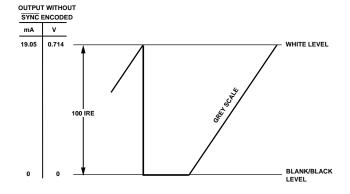

| IOR, IOG, IOB           | Red, Green & Blue Current Outputs (High Impedance Current Sources). These RGB video outp<br>are specified to directly drive RS-343A and RS-170 video levels into doubly terminated 75 $\Omega$ loads                                                                                                                                                                                                                                                                                               |                |  |  |  |  |  |

| V <sub>REF</sub>        | Voltage Reference Input (Analog Input): An external 1.235 V voltage reference is required to driv<br>this input. An AD589 (2-terminal voltage reference) or equivalent is recommended. (Note: It is n<br>recommended to use a resistor network to generate the voltage reference.)                                                                                                                                                                                                                 |                |  |  |  |  |  |

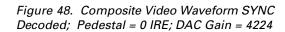

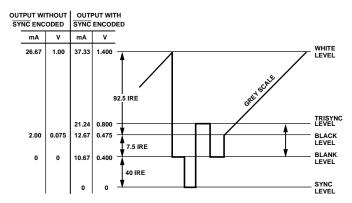

| R <sub>SET</sub>        | Output Full Scale Adjust Control (Analog Input). A resistor connected between this pin and anal ground controls the absolute amplitude of the output video signal. For a value of $R_{SET}$ of nominal 280 $\Omega$ , with 37.5 $\Omega$ termination and using CR43 and CR44 of Command Register 4 to set the DA Gain as shown, the required Video Standard can be achieved.                                                                                                                       | lly            |  |  |  |  |  |

|                         | CR44CR43Video StandardDAC GainBlack to White00RS343A, Sync & Pedestal3996660 mV 17.62 m01RS343A, Sync & No Pedestal4224699 mV 18.63 m10RS343A, No Sync & No Pedestal4311714 mV 19.05 m11RS170, Sync & Pedestal5592925 mV 24.67 m                                                                                                                                                                                                                                                                   | nA<br>nA<br>nA |  |  |  |  |  |

|                         | Alternatively, $R_{SET}$ can be calculated by the following equation:                                                                                                                                                                                                                                                                                                                                                                                                                              |                |  |  |  |  |  |

|                         | $R_{SET} rac{DAC \ Gain 	imes V_{REF}}{Black \ to \ White \ Current}$                                                                                                                                                                                                                                                                                                                                                                                                                             |                |  |  |  |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |  |  |  |  |  |

| COMP<br>V <sub>AA</sub> | Compensation Pin. A 0.1 $\mu$ F capacitor should be connected between this pin and V <sub>AA</sub> .<br>Power Supply (+5 V ± 5%). The part contains multiple power supply pins, all should be connected                                                                                                                                                                                                                                                                                            |                |  |  |  |  |  |

| GND:                    | together to one common +5 V filtered analog power supply.<br>Analog Ground. The part contains multiple ground pins, all should be connected together to the system's ground plane.                                                                                                                                                                                                                                                                                                                 | ;              |  |  |  |  |  |

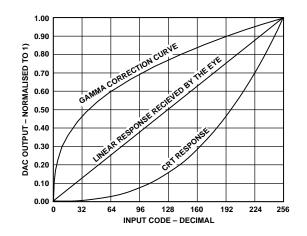

| TMS, TCK,<br>TDI, TDO   | These four pins control the JTAG test access port.<br>See Appendix 6 for more detail                                                                                                                                                                                                                                                                                                                                                                                                               |                |  |  |  |  |  |

#### (Continued from page 1)

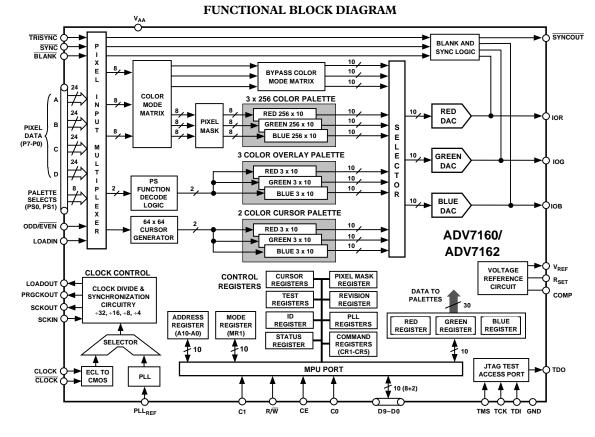

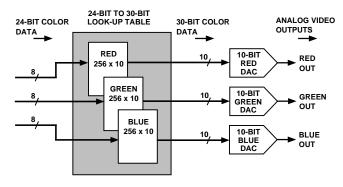

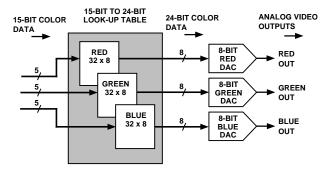

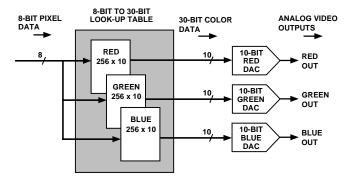

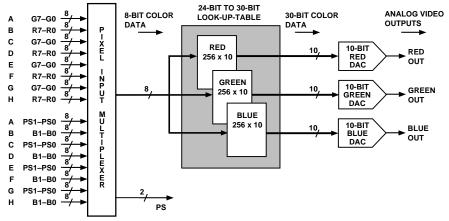

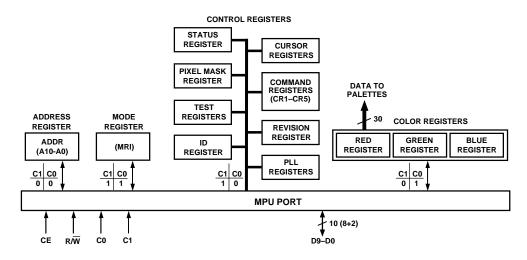

The ADV7160/ADV7162 integrates a number of graphic functions onto one device allowing 24-bit direct True-Color (30-bit Corrected-Color) operation at the maximum screen resolution of 1600 × 1280 at a refresh rate of 85 Hz. The ADV7160/ ADV7162 integrates a 256 × 30 Color Palette RAM with three high speed, 10-bit, digital-to analog converters (RGB DACs). It also contains a user-definable, X-Windows compatible,  $64 \times$  $64 \times 2$  cursor generator and associated RAM. An on-board Overlay Palette RAM is also included. The device's 96-bit Programmable Pixel Port enables various data formats to be input to the part. An on-board clock and synchronization circuit controls all clocking functions for both the part and graphics subsystem.

There are two video data paths through the ADV7160/ADV7162. One routes the data from the pixel port through the RAM to the DACs, the other bypasses the RAM and routes data direct from the pixel port to the DACs. Either path can be selected on a pixel by pixel basis. This allows for the overlay of an active video window on a graphics background.

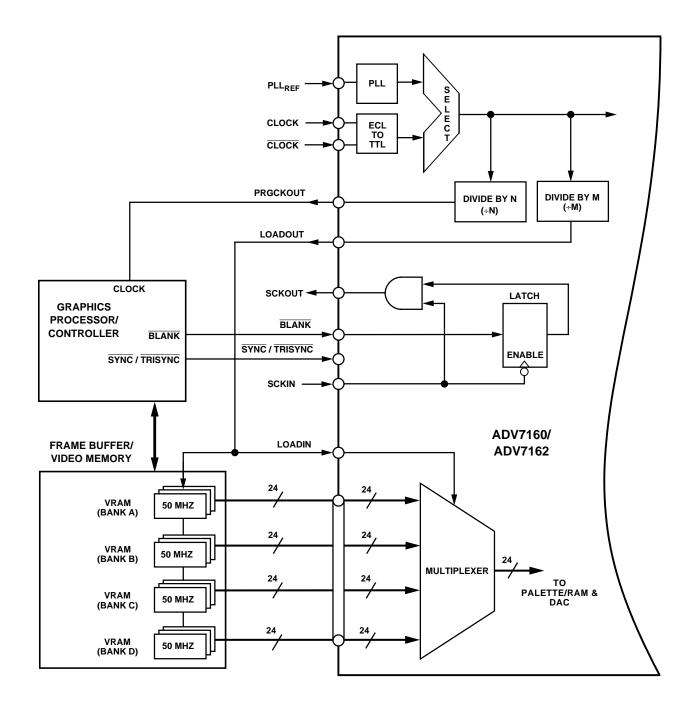

The on-board palette priority select inputs enable multiple palette devices to be connected together for use in multipalette and window applications. The part is controlled and programmed through the microprocessor (MPU) port. The 30 bits of resolution, associated with the color look-up table and triple 10-bit DAC, realizes 24-bit True-Color resolution, while also allowing for the on-board implementation of linearization algorithms, such as Gamma-Correction and Monitor Callibration. This allows effective 30-bit True-Color operation.

The on-chip video clock controller circuit generates all the internal clocking and some additional external clocking signals. The high accuracy, low jitter on board PLL eliminates the need for an external high speed clock generator. The PLL can be programmed to produce a pixel clock that is a multiple of the PLL reference clock.

The ADV7162 is packaged in a standard plastic 160-pin quad flatpack (QFP).

The ADV7160 is packaged in a plastic 160-pin power quad flatpack (PQUAD). Superior thermal distribution is achieved by the inclusion of a copper heatslug, within the standard package outline, to which the die is attached. This part is ideally suited for high performance applications where external environmental conditions are unpredictable and uncontrollable.

### CIRCUIT DETAILS AND OPERATION

#### **OVERVIEW**

Digital video or pixel data is latched into the ADV7160/ADV7162 over the devices Pixel Port. This data acts as a pointer to onboard Color Palette RAM. The data at the RAM address pointed to is latched to the digital-to-analog converters (DACs) and output as an RGB analog video signal.

For the purposes of clarity of description, the ADV7160/ADV7162 is broken down into three separate functional blocks. These are:

- 1. Pixel Port and Clock Control Circuit

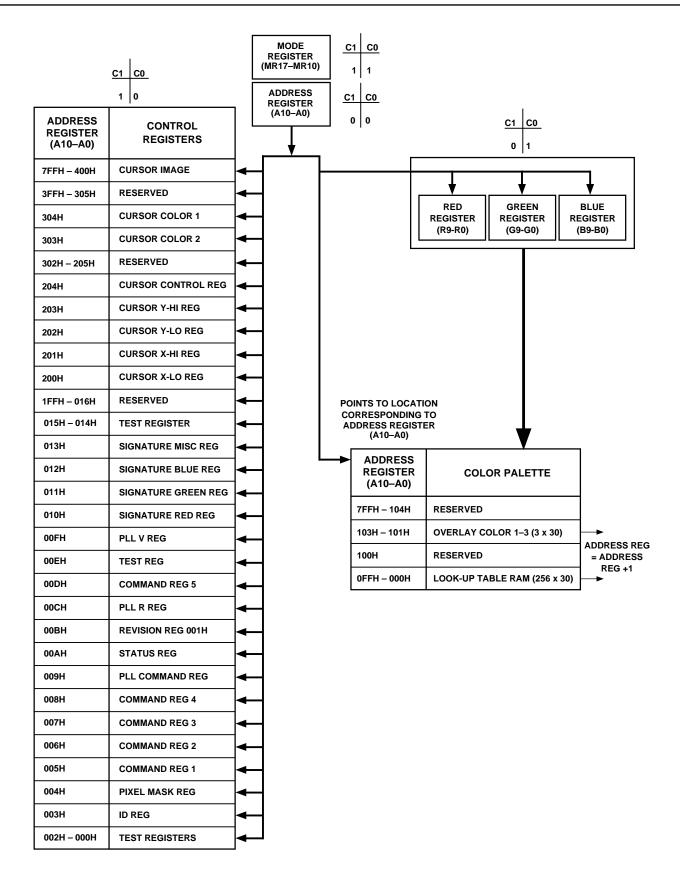

- 2. MPU Port, Registers and Color Palette

3. Digital-to-Analog Converters and Video Outputs

#### Pixel Port & Clock Control Circuit

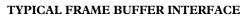

The Pixel Port of the ADV7160/ADV7162 is directly interfaced to the video/graphics pipeline of a computer graphics subsystem. It is connected directly or through a gate array to the video RAM of the systems Frame-Buffer (video memory). The pixel port on the device consists of:

| Color Data      | RED, GREEN, BLUE                        |  |

|-----------------|-----------------------------------------|--|

| Pixel Controls  | <u>SYNC, BLANK, TRISYNC</u>             |  |

| Palette Selects | PS0 <sub>A-D</sub> , PS1 <sub>A-D</sub> |  |

The associated clocking signals for the pixel port include:

| Clock Inputs  | CLOCK, $\overline{\text{CLOCK}}$ , $\text{PLL}_{\text{REF}}$ , LOADIN, SCKIN |

|---------------|------------------------------------------------------------------------------|

| Clock Outputs | LOADOUT, PRGCKOUT,<br>SCKOUT                                                 |

These on-board clock control signals are included to simplify interfacing between the part and the frame buffer. Either two control input signals CLOCK and  $\overline{\text{CLOCK}}$  (ECL Levels) or

one TTL input signal  $PLL_{REF}$  are required to get the part operational. No additional signals or external glue logic are required to get the Pixel Port and Clock Control Circuit of the part operational.

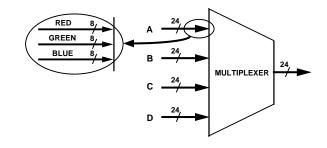

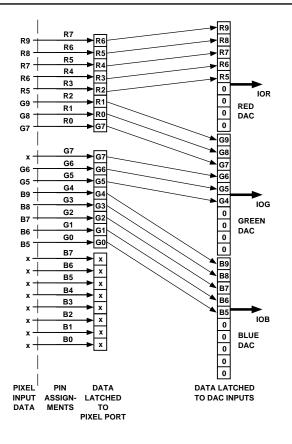

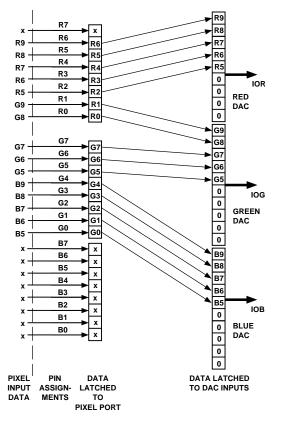

#### Pixel Port (Color Data)

The ADV7160/ADV7162 has 96 color data inputs. The part has four (for 4:1 multiplexing) 24-bit wide direct color data inputs. These are user programmed to support a number of color data formats including 24-bit True-Color, 16-bit True-Color, 15-bit True-Color in 4:1 and 2:1 multiplex modes, and 8-bit Pseudo-Color (see "Multiplexing" section) in 8:1, 4:1 and 2:1 multiplex modes.

Color data is latched into the parts pixel port on every rising edge of LOADIN (see Timing Waveform, Figure 4). The required frequency of LOADIN is determined by the multiplex rate, where

| $f_{LOADIN} = f_{CLOCK}/8$ | 8:1 multiplex mode |

|----------------------------|--------------------|

| $f_{LOADIN} = f_{CLOCK}/4$ | 4:1 multiplex mode |

| $f_{LOADIN} = f_{CLOCK}/2$ | 2:1 multiplex mode |

Other pixel data signals latched into the device by LOADIN include  $\overline{SYNC}$ ,  $\overline{BLANK}$ ,  $\overline{TRISYNC}$  and  $PSO_{A-D} - PS1_{A-D}$ .

Internally, data is pipelined through the part by the differential pixel clock inputs, CLOCK and CLOCK or by the internal pixel clock generated by the PLL on-board. The LOADIN control signal need only have a frequency synchronous relationship to the pixel CLOCK (see "Pipeline Delay & On-Board Calibration" section). A completely phase independent LOADIN signal can be used with the ADV7160/ADV7162, allowing the CLOCK to occur anywhere during the LOADIN cycle.

Alternatively, the LOADOUT signal of the ADV7160/ADV7162 can be used. LOADOUT can be connected either directly or indirectly to LOADIN. Its frequency is automatically set to the correct LOADIN requirement.

#### **SYNC**, **BLANK**

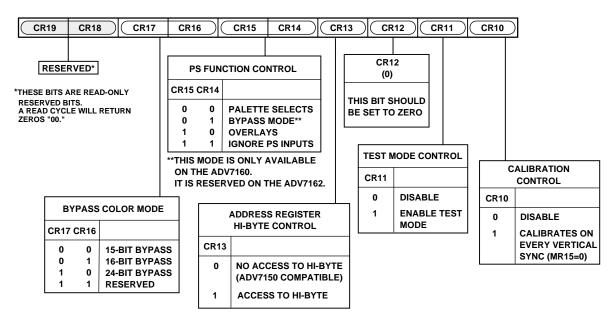

The BLANK and SYNC video control signals drive the analog outputs to the Blank and Sync levels respectively. These signals are latched into the part on the rising edge of LOADIN. The SYNC information is encoded onto the IOG analog signal when Bit CR22 of Command Register 2 is set to "1," the IOR analog signal when Bit CR41 of Command Register 4 is set to "1" and the IOB analog signal when Bit CR42 of Command Register 4 is set to "1." The SYNC input is ignored if CR22, CR41 and CR42 are set to logic "0."

#### SYNCOUT

In some applications where it is not permissible to encode <u>SYNC</u> on green (IOG), blue (IOB), or red (IOR), <u>SYNCOUT</u> can be used as a separate TTL digital <u>SYNC</u> output. This has the advantage over an independent (of the ADV7160/ADV7162) <u>SYNC</u> in that it does not necessitate knowing the absolute pipeline delay of the part. This allows complete independence between LOADIN/Pixel Data and CLOCK. The <u>SYNC</u> input is connected to the device as normal with Bit CR22 of Command Register 2, Bit CR41 of Command Register 4 and Bit <u>CR42</u> of Command Register 4 are set to "0" thereby preventing <u>SYNC</u> from being encoded <u>onto IOG</u>, IOR and IOB. The output signal generates a TTL <u>SYNCOUT</u> with correct pipeline delay which is capable of directly driving the composite <u>SYNC</u> signal of a computer monitor.

#### TRISYNC

This input is used to generate a HDTV Sync on any of the DAC outputs. Bit CR17 of Command Register 1 is set to "1", enabling TRISYNC. When TRISYNC is low, the analog output which has Sync enabled goes to the tri-sync level.

#### PS0<sub>A-D</sub>-PS1<sub>A-D</sub> (Palette Priority Select Inputs)

These multifunctional TTL compatible inputs can be configured for three separate functions. The eight PS inputs are multiplexed to provide two bits which are used to provide one of three different functions. The function is selected by Bit CR14 and Bit CR15 of Command Register 1.

| CR15 | CR14 | Color Mode                         |

|------|------|------------------------------------|

| 0    | 0    | Palette Select Mode                |

| 0    | 1    | Bypass Mode Control (ADV7160 Only) |

| 1    | 0    | Overlay Color Mode                 |

| 1    | 1    | Ignore PS Inputs                   |

However, in 8:1 Mode, for 8-Bit Pseudo Color, the unused Blue Pixel Inputs are used to provide 8 extra PS inputs. The bypass mode is unavailable in this case.

#### Palette Select Mode

These pixel port select inputs effectively determine whether the devices RGB analog outputs are turned-on or shut down. When the analog outputs are shut down, IOR, IOG and IOB are forced to 0 mA regardless of the state of the pixel and control data inputs. This state is determined on a pixel by pixel basis as the PS0–PS1 inputs are multiplexed in exactly the same format as the pixel port color data. These controls allow for switching between multiple palette devices. If the values of PS0 and PS1 match the values programmed into bits MR16 and MR17 of the Mode Register, then the device is selected, if there is no match the device is effectively shut down.

#### Bypass Mode Control (ADV7160 Only)

In this mode PS1 is used to switch between one of the color modes through the Color Palette and one of the Palette Bypass modes on a pixel by pixel basis. The color mode through the palette is selected using Bits CR27–CR24 of Command Register 2. The Bypass Color Mode is selected using Bits CR17 and CR16 of Command Register 1. PS1 then switches between the Palette Color Mode, and the Bypass Color Mode. The PS0 input continues to act as an overlay input, allowing Overlay Color 1 to be displayed.

| PS0 | PS1 | Color Mode                     |

|-----|-----|--------------------------------|

| 0   | 0   | Palette Color Mode (CR27–CR24) |

| 0   | 1   | Bypass Color Mode (CR17-CR16)  |

| 1   | х   | Overlay Color 1                |

This mode is not available if using the ADV7162.

#### **Overlay Color Mode**

In this mode, the PS inputs provide control for a three color overlay. Whenever the value other than "00" is placed on the overlay inputs, the corresponding overlay color is displayed. When the overlay inputs contain "00" the color is specified by the main pixel inputs.

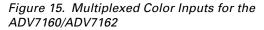

#### CLOCK CONTROL CIRCUIT

The ADV7160/ADV7162 has an integrated Clock Control Circuit (Figure 16). This circuit is capable of both generating the ADV7160/ADV7162's internal clocking signals as well as external graphics subsystem clocking signals. Total system synchronization can be attained by using the parts output clocking signals to drive the controlling graphics processor's master clock as well as the video frame buffers shift clock signals.

#### CLOCK, CLOCK Inputs

The Clock Control Circuit is driven by the pixel clock inputs, CLOCK and  $\overline{\text{CLOCK}}$ . These inputs can be driven by a differential ECL oscillator running from a +5 V supply.

*Figure 16. Clock Control Circuit of the ADV7160/ADV7162*

## CLOCK CONTROL SIGNALS LOADOUT

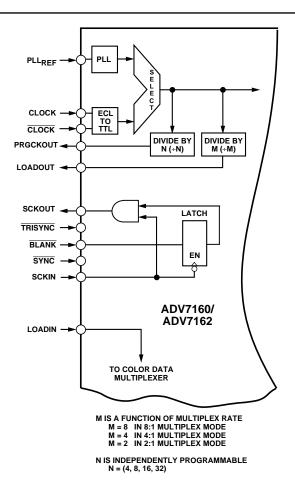

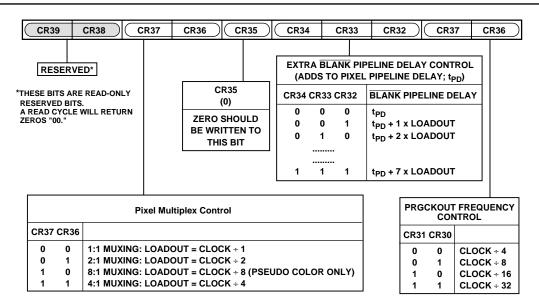

The ADV7160/ADV7162 generates a LOADOUT control signal which runs at a divided down frequency of the pixel CLOCK. The frequency is automatically set to the programmed multiplex rate, controlled by CR37 and CR36 of Command Register 3.

| $f_{LOADOUT} = f_{CLOCK}/8$ | 8:1 multiplex mode |

|-----------------------------|--------------------|

| $f_{LOADOUT} = f_{CLOCK}/4$ | 4:1 multiplex mode |

| $f_{LOADOUT} = f_{CLOCK}/2$ | 2:1 multiplex mode |

The LOADOUT signal is used to directly drive the LOADIN pixel latch signal of the ADV7160/ADV7162. This is most simply achieved by tying the LOADOUT and LOADIN pins together. Alternatively, the LOADOUT signal can be used to drive the frame buffer's shift clock signals, returning to the LOADIN input delayed with respect to LOADOUT.

If it is not necessary to have a known fixed number of pipeline delays, then there is no limitation on the delay between LOADOUT and LOADIN (LOADOUT(1) and LOADOUT(2)). LOADIN and Pixel Data must conform to the setup and hold times ( $t_8$  and  $t_9$ ).

If however, it is required that the ADV7160/ADV7162 has a fixed number of pipeline delays ( $t_{PD}$ ) LOADOUT and LOADIN must conform to timing specifications  $t_{10}$  and  $\tau$ - $t_{11}$  as illustrated in Figures 5 to 10.

### ADV7160/ADV7162

#### Figure 17. LOADOOUT vs Pixel Clock

#### Pipeline Delay and Onboard Calibration

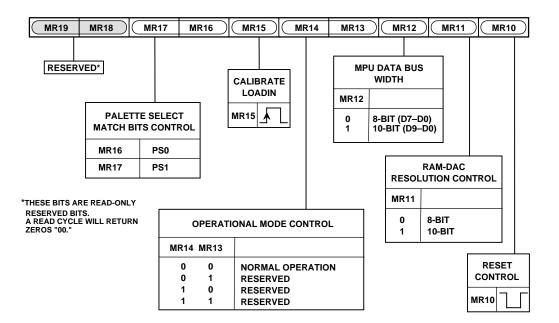

The ADV7160/ADV7162 has a fixed number of pipeline delays ( $t_{PD}$ ), so long as timings  $t_{10}$  and  $\tau$ - $t_{11}$  are met. However, if a fixed number of pipeline delays is not a requirement, timings  $t_{10}$  and  $\tau$ - $t_{11}$  can be ignored, a calibration cycle must be run and there is no restriction on LOADIN to LOADOUT timing. If timings  $t_{10}$  and  $\tau$ - $t_{11}$  are not met, the part will function correctly though with an increased number of pipeline delays. The ADV7160/ADV7162 has on-board calibration circuitry which synchronizes pixel data and LOADIN with the internal ADV7160/ADV7162 clocking signals. Calibration can be performed in two ways. During the device's initialization sequence by toggling two bits of the Mode Register, MR10 followed by MR15 or by writing a "1" to Bit CR10 of Command Register 1 and a "0" to MR15 which executes a calibration on every Vertical Sync.

#### PRGCKOUT

The PRGCKOUT control signal outputs a user programmable clock frequency. It is a divided down frequency of the pixel CLOCK (see Figure 11). The rising edge of PRGCKOUT is synchronous to the rising edge of LOADOUT.

$$f_{PRGCKOUT} = f_{CLOCK}/N$$

where N = 4, 8, 16 or 32.

One application of the PRGCKOUT is to use it as the master clock frequency of the graphics subsystems processor or controller.

#### SCKIN, SCKOUT

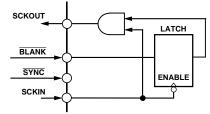

These video memory signals are used to minimize external support chips. Figure 18 illustrates the function that is provided. An input signal applied to SCKIN is synchronously AND-ed with the video blanking signal ( $\overline{BLANK}$ ). The resulting signal is output on SCKOUT. Figure 12 of the Timing Waveform section shows the relationship between SCKOUT, SCKIN and  $\overline{BLANK}$ .

Figure 18. SCKOUT Generation Circuit

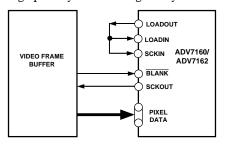

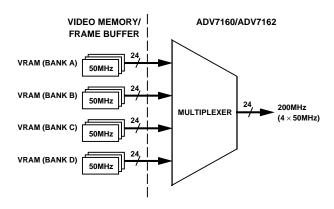

The SCKOUT signal is essentially the video memory shift control signal. It is stopped during the screen retrace. Figure 19 shows a suggested frame buffer to ADV7160/ADV7162 interface. This is a minimum chip solution and allows the ADV7160/ADV7162 control the overall graphics system clocking and synchronization.

Figure 19. ADV7160/ADV7162 Interface Using SCKIN and SCKOUT

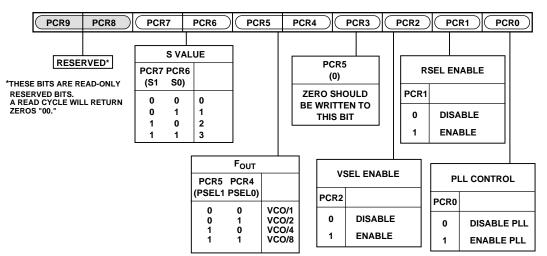

#### PLL

The on-board PLL can be used as an alternative clock source. This eliminates the need for an external high speed clock generator such as a crystal oscillator. With the PLL, it is possible to generate an internal clock whose frequency is a multiple of the PLL reference frequency (PLL<sub>REF</sub>). Internal PLL operation is selected by setting CR56 of Command Register 5 to Logic "1." The PLL registers can be programmed to set up the frequency required.

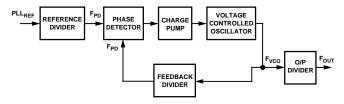

The block diagram of the Phase Locked Loop is shown in Figure 20. The blocks consist of a phase frequency detector, a charge pump, a loop filter, a voltage controlled oscillator and a programmable divider.

#### Figure 20. PLL Block Diagram

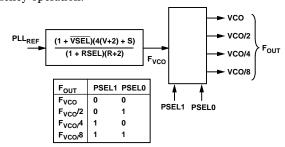

The phase frequency detector drives the voltage controlled oscillator (VCO), to a frequency that will cause the two inputs to the phase frequency detector to be matched in frequency and phase. The corresponding output of the VCO can be calculated as:

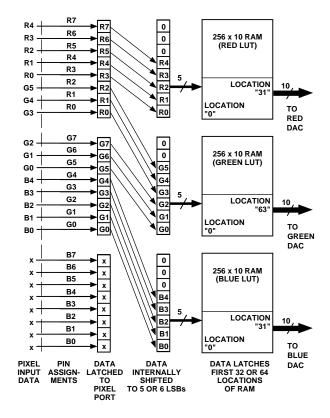

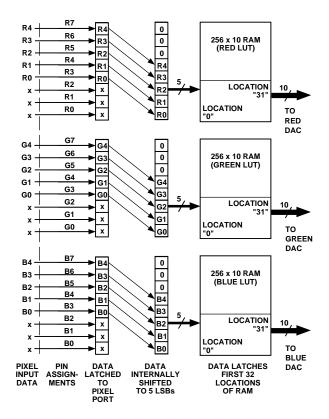

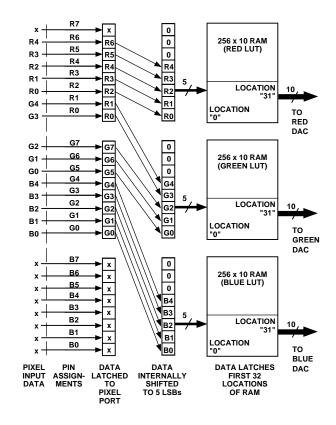

#### $VCO = PLL_{REF}$ <u>Feedback Divider</u> Reference Divider