# ADSP-2136x SHARC® Processor Hardware Reference

Includes ADSP-21362, ADSP-21363, ADSP-21364, ADSP-21365, ADSP-21366

Revision 1.0, October 2005

Part Number 82-000501-01

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

## Copyright Information

© 2005 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### **Disclaimer**

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

### Trademark and Service Mark Notice

The Analog Devices logo, Blackfin, EZ-KIT Lite, SHARC, the SHARC logo, TigerSHARC, and VisualDSP++ are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

# **Contents**

## **PREFACE**

| Purpose of This Manual xxiii                  |

|-----------------------------------------------|

| Intended Audience xxiii                       |

| Manual Contents                               |

| What's New in This Manual                     |

| Technical or Customer Support                 |

| Supported Processorsxxvii                     |

| Product Information                           |

| MyAnalog.com xxviii                           |

| Processor Product Information                 |

| Related Documents xxix                        |

| Online Technical Documentation                |

| Accessing Documentation From VisualDSP++ xxxi |

| Accessing Documentation From Windows xxxi     |

| Accessing Documentation From the Web xxxii    |

| Printed Manuals xxxii                         |

| VisualDSP++ Documentation Set xxxii           |

| Hardware Tools Manuals xxxiii                 |

| Processor Manuals xxxiii                      |

| Data Sheets                                | xxxiii |

|--------------------------------------------|--------|

| Conventions                                | xxxiv  |

| INTRODUCTION                               |        |

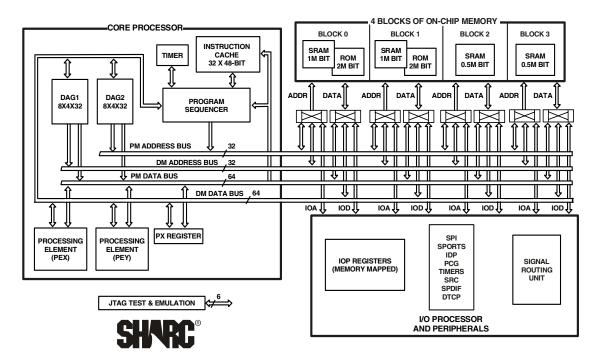

| ADSP-2136x SHARC Design Advantages         | 1-1    |

| Processor Architectural Overview           | 1-8    |

| Processor Core                             | 1-9    |

| Processor Peripherals                      | 1-9    |

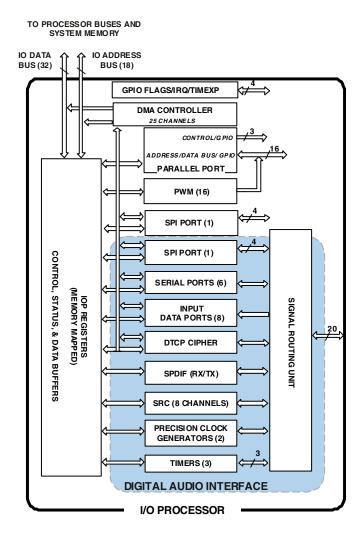

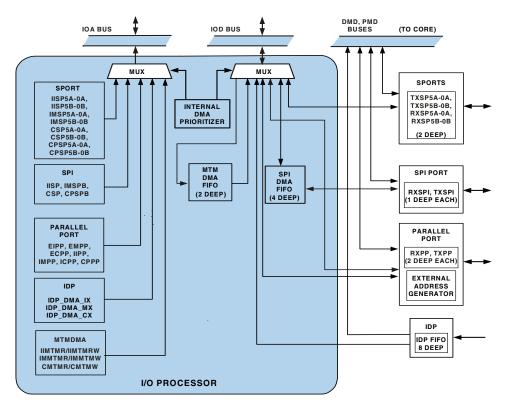

| I/O Processor                              | 1-9    |

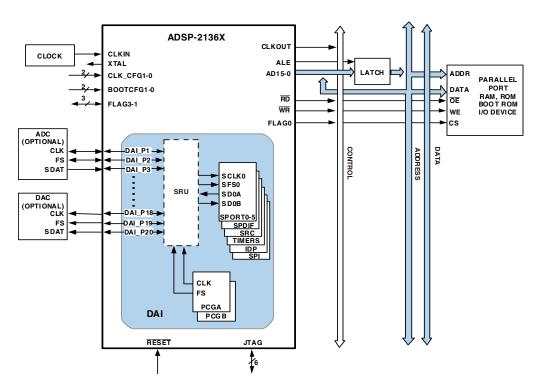

| Digital Audio Interface (DAI)              | 1-11   |

| Development Tools                          | 1-12   |

| Architecture Enhancements                  | 1-12   |

| Parallel Port Enhancements                 | 1-12   |

| I/O Architecture Enhancements              | 1-13   |

| Instruction Set Enhancements               | 1-13   |

| I/O PROCESSOR                              |        |

| General Procedure for Configuring DMA      | 2-2    |

| Core Access to IOP Registers               | 2-3    |

| Choosing IOP/Core Interaction Options      | 2-6    |

| Interrupt-Driven I/O                       | 2-6    |

| Polling/Status-Driven I/O                  | 2-10   |

| DMA Controller Operation                   | 2-11   |

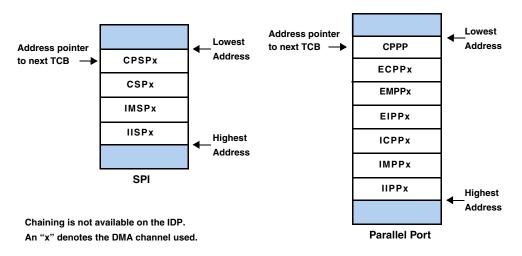

| Chaining DMA Processes                     | 2-13   |

| Transfer Control Block (TCB) Chain Loading | 2-16   |

| Setting Up and Starting Chained DMA on           |        |

|--------------------------------------------------|--------|

| Serial/Parallel Ports                            | 2-18   |

| Setting Up and Starting Chained DMA over the SPI | I 2-18 |

| Inserting a TCB in an Active Chain               | 2-20   |

| Memory-to-Memory DMA                             | 2-21   |

| Setting Up DMA Channel Allocation and Priorities | 2-21   |

| Managing DMA Channel Priority                    | 2-22   |

| DMA Bus Arbitration                              | 2-23   |

| Setting Up DMA Parameter Registers               | 2-26   |

| DMA Transfer Direction                           | 2-26   |

| Data Buffer Registers                            | 2-28   |

| Port, Buffer, and DMA Control Registers          | 2-29   |

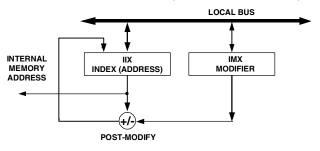

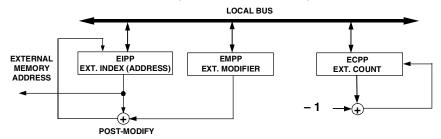

| Addressing                                       | 2-31   |

| Setting Up DMA                                   | 2-36   |

| Programming Example                              | 2-37   |

| PARALLEL PORT                                    |        |

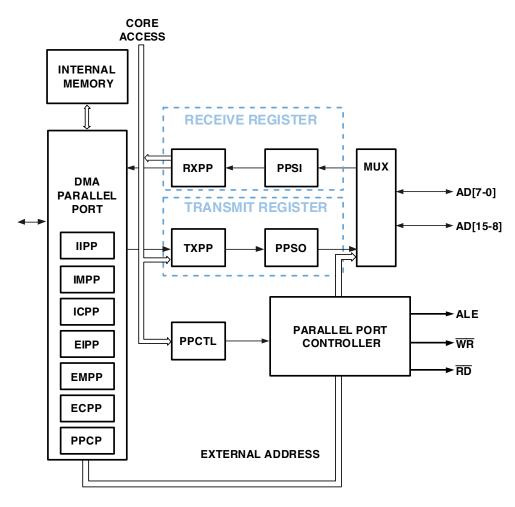

| Parallel Port Pins                               | 3-3    |

| Alternate Pin Functions                          | 3-4    |

| Parallel Port Pins as FLAG Pins                  | 3-4    |

| Parallel Data Acquisition Port as AD Pins        | 3-5    |

| Parallel Port Operation                          | 3-5    |

| Basic Parallel Port External Transaction         | 3-5    |

| Data Cycles                                      | 3-6    |

| Reading From an External Device or Memory        | 3-7    |

|                                                  |        |

| Writing to an External Device or Memory | 3-8  |

|-----------------------------------------|------|

| Transfer Protocol                       | 3-9  |

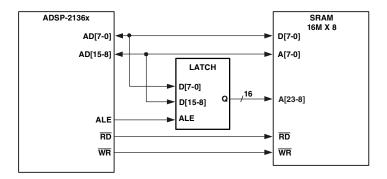

| 8-Bit Mode                              | 3-9  |

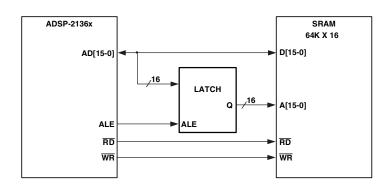

| 16-Bit Mode                             | 3-10 |

| Comparison of 8- and 16-Bit SRAM Modes  | 3-11 |

| Parallel Port Interrupts                | 3-12 |

| Parallel Port Throughput                | 3-13 |

| 8-Bit Access                            | 3-14 |

| 16-Bit Access                           | 3-15 |

| Conclusion                              | 3-16 |

| Parallel Port Registers                 | 3-16 |

| Parallel Port Control Register (PPCTL)  | 3-17 |

| Parallel Port DMA Registers             | 3-17 |

| Parallel Port External Setup Registers  | 3-19 |

| Using the Parallel Port                 | 3-19 |

| DMA Transfers                           | 3-20 |

| Configuring the Parallel Port for DMA   | 3-21 |

| Configuring a Chained DMA               | 3-21 |

| Core-Driven Transfers                   | 3-23 |

| Known-Duration Accesses                 | 3-25 |

| Status-Driven Transfers (Polling)       | 3-26 |

| Core-Stall Driven Transfers             | 3-26 |

| Interrupt Driven Accesses               | 3-27 |

| Programming Examples                    | 3-27 |

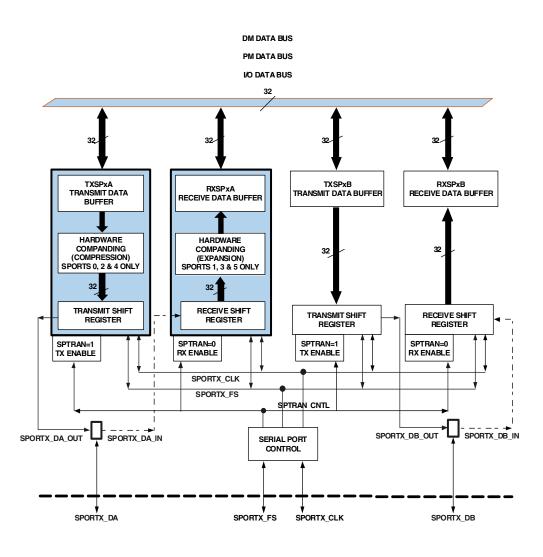

## **SERIAL PORTS**

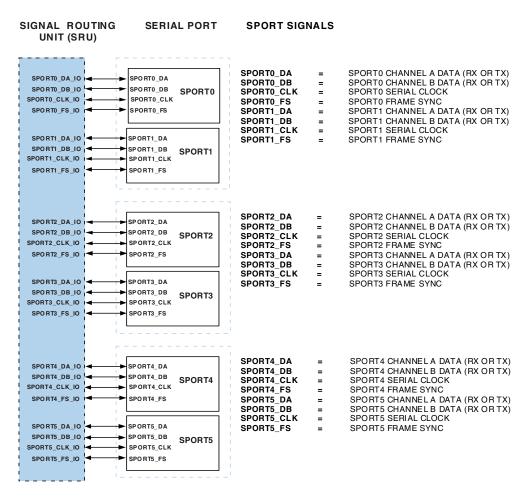

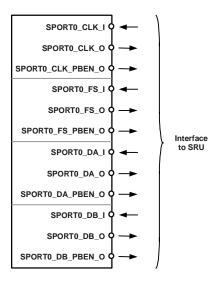

| Serial Port Signals                                         |

|-------------------------------------------------------------|

| Serial Port Signal Sensitivity                              |

| SPORT Operation Modes                                       |

| Standard DSP Serial Mode 4-12                               |

| Standard DSP Serial Mode Control Bits 4-12                  |

| Clocking Options                                            |

| Frame Sync Options                                          |

| Data Formatting                                             |

| Data Transfers                                              |

| Status Information                                          |

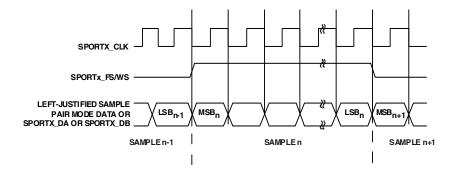

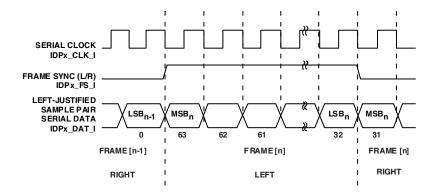

| Left-Justified Sample Pair Mode                             |

| Setting the Internal Serial Clock and Frame Sync Rates 4-16 |

| Left-Justified Sample Pair Mode Control Bits 4-16           |

| Setting Word Length (SLEN)                                  |

| Enabling SPORT Master Mode (MSTR) 4-17                      |

| Selecting Transmit and Receive Channel Order (FRFS) 4-17    |

| Selecting Frame Sync Options (DIFS)                         |

| Enabling SPORT DMA (SDEN)                                   |

| Interrupt-Driven Data Transfer Mode 4-18                    |

| DMA-Driven Data Transfer Mode                               |

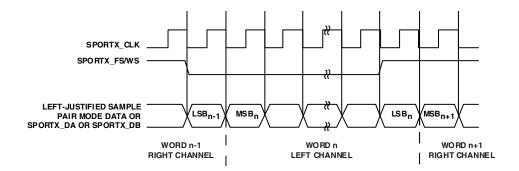

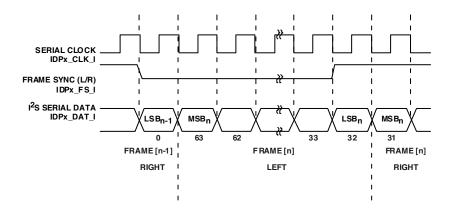

| I2S Mode                                                    |

| I2S Mode Control Bits                                       |

| Setting the Internal Serial Clock and Frame Sync Rates 4-21 |

| I2S Control Bits                                    | 4-21 |

|-----------------------------------------------------|------|

| Setting Word Length (SLEN)                          | 4-22 |

| Enabling SPORT Master Mode (MSTR)                   | 4-22 |

| Selecting Transmit and Receive Channel Order (FRFS) | 4-22 |

| Selecting Frame Sync Options (DIFS)                 | 4-23 |

| Enabling SPORT DMA (SDEN)                           | 4-23 |

| Interrupt-Driven Data Transfer Mode                 | 4-24 |

| DMA-Driven Data Transfer Mode                       | 4-24 |

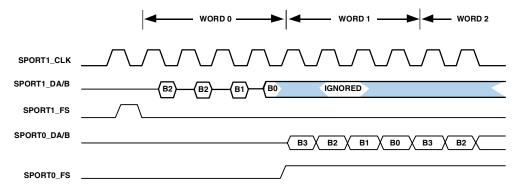

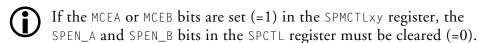

| Multichannel Operation                              | 4-24 |

| Frame Syncs in Multichannel Mode                    | 4-27 |

| Active State Multichannel Receive Frame Sync Select | 4-28 |

| Multichannel Mode Control Bits                      | 4-28 |

| Receive Multichannel Frame Sync Source              | 4-30 |

| Active State Transmit Data Valid                    | 4-30 |

| Multichannel Status Bits                            | 4-30 |

| Channel Selection Registers                         | 4-31 |

| SPORT Loopback                                      | 4-32 |

| Clock Signal Options                                | 4-34 |

| Frame Sync Options                                  | 4-34 |

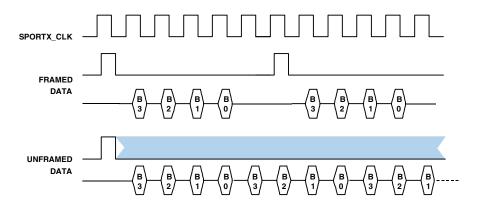

| Framed Versus Unframed Frame Syncs                  | 4-35 |

| Internal Versus External Frame Syncs                | 4-36 |

| Active Low Versus Active High Frame Syncs           | 4-36 |

| Sampling Edge for Data and Frame Syncs              | 4-37 |

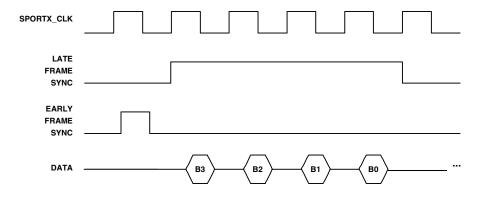

| Early Versus Late Frame Syncs                       | 4-37 |

|                                                     |      |

| Data-Independent Frame Sync                            | 4-38 |

|--------------------------------------------------------|------|

| Data Word Formats                                      | 4-40 |

| Word Length                                            | 4-40 |

| Endian Format                                          | 4-41 |

| Data Packing and Unpacking                             | 4-41 |

| Data Type                                              | 4-42 |

| Companding                                             | 4-43 |

| SPORT Control Registers and Data Buffers               | 4-45 |

| Register Writes and Effect Latency                     | 4-51 |

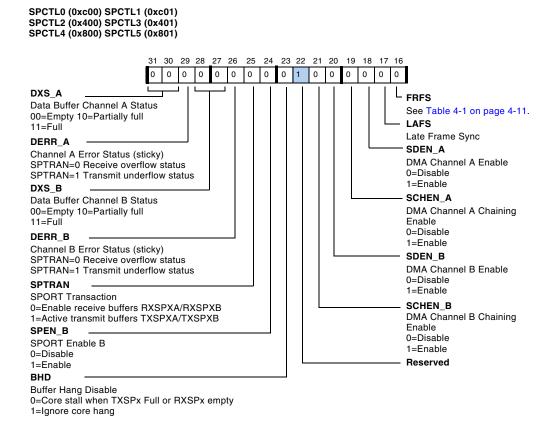

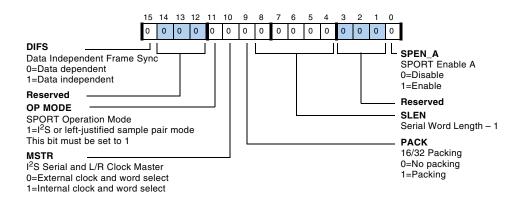

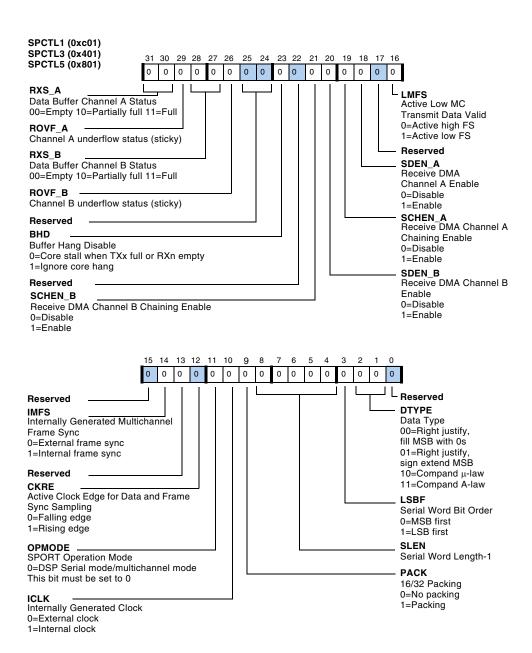

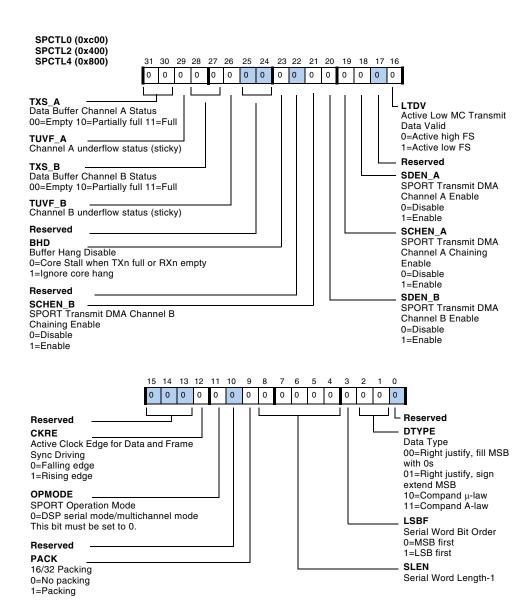

| Serial Port Control Registers (SPCTLx)                 | 4-51 |

| Transmit and Receive Data Buffers (TXSPxA/B, RXSPxA/B) | 4-60 |

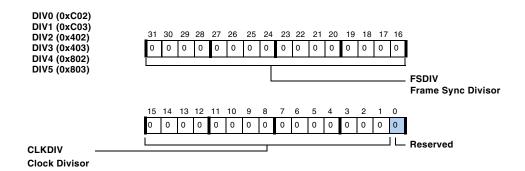

| Clock and Frame Sync Frequency Registers (DIVx)        | 4-63 |

| SPORT Reset                                            | 4-65 |

| SPORT Interrupts                                       | 4-66 |

| Moving Data Between SPORTS and Internal Memory         | 4-67 |

| DMA Block Transfers                                    | 4-67 |

| Setting Up DMA on SPORT Channels                       | 4-69 |

| SPORT DMA Parameter Registers                          | 4-70 |

| SPORT DMA Chaining                                     | 4-74 |

| Single Word Transfers                                  | 4-74 |

| SPORT Programming Examples                             | 4-76 |

#### SERIAL PERIPHERAL INTERFACE PORTS

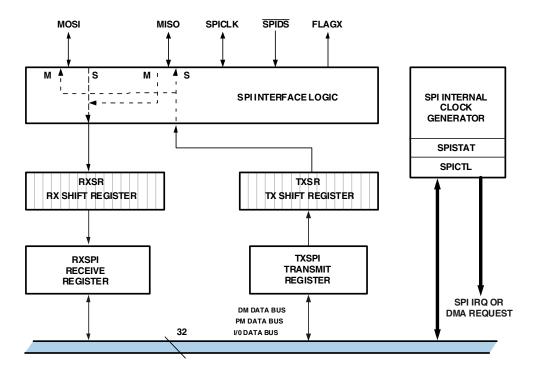

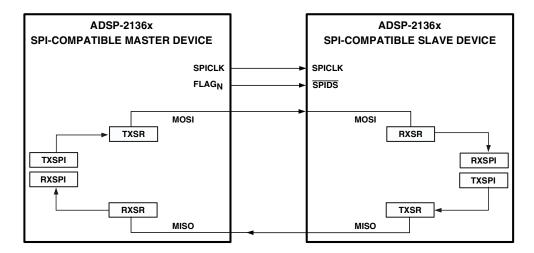

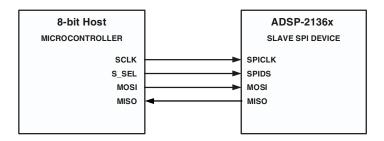

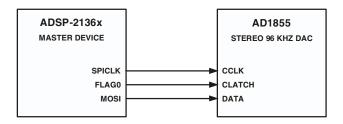

| Functional Description                      |

|---------------------------------------------|

| SPI Interface Signals 5-4                   |

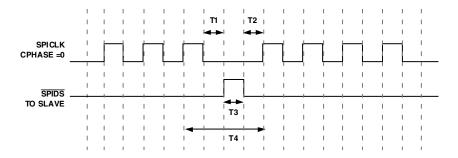

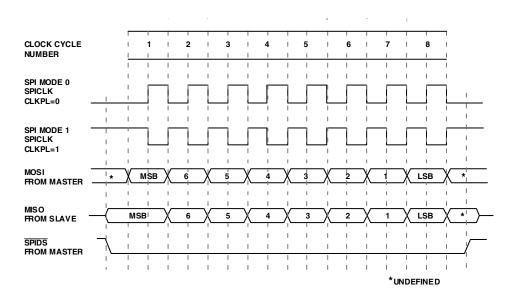

| SPI Clock Signal (SPICLK)                   |

| SPICLK Timing                               |

| SPI Slave Select Outputs (SPIDS0-3)         |

| SPI Device Select Signal                    |

| Master Out Slave In (MOSI)                  |

| Master In Slave Out (MISO)                  |

| SPI General Operations 5-8                  |

| SPI Enable                                  |

| Open Drain Mode (OPD)                       |

| Master Mode Operation                       |

| Slave Mode Operation                        |

| Multimaster Conditions                      |

| SPI Data Transfer Operations                |

| Core Transmit/Receive Operations            |

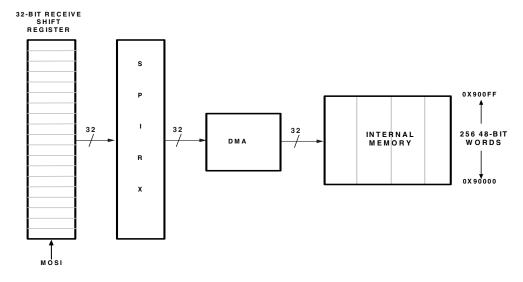

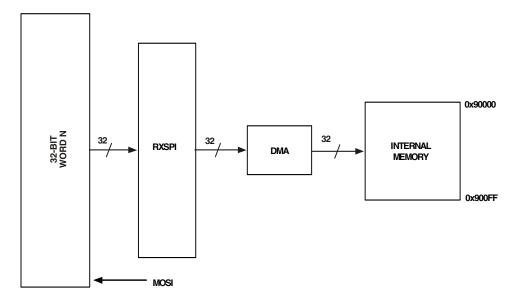

| SPI DMA 5-14                                |

| Master Mode DMA Operation                   |

| Master Transfer Preparation                 |

| Slave Mode DMA Operation                    |

| Slave Transfer Preparation                  |

| Changing SPI Configuration                  |

| Switching From Transmit To Receive DMA 5-23 |

| Switching From Receive to Transmit DMA 5-24 |

|---------------------------------------------|

| DMA Error Interrupts                        |

| DMA Chaining                                |

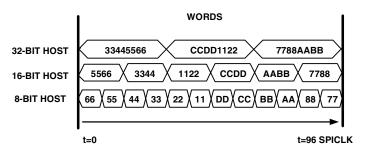

| SPI Transfer Formats                        |

| Beginning and Ending an SPI Transfer 5-29   |

| SPI Word Lengths                            |

| 8-Bit Word Lengths                          |

| 16-Bit Word Lengths                         |

| 32-Bit Word Lengths                         |

| Packing                                     |

| SPI Interrupts                              |

| Error Signals and Flags                     |

| Mode Fault Error (MME) 5-35                 |

| Transmission Error Bit (TUNF)               |

| Reception Error Bit (ROVF)                  |

| Transmit Collision Error Bit (TXCOL)        |

| SPI Programming Examples                    |

| INPUT DATA PORT                             |

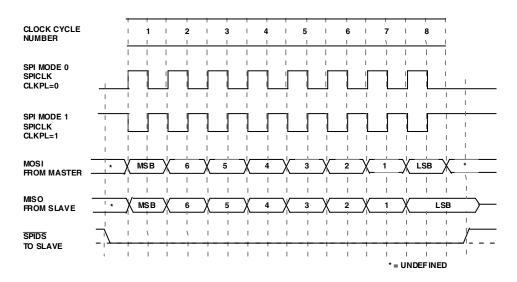

| Serial Inputs                               |

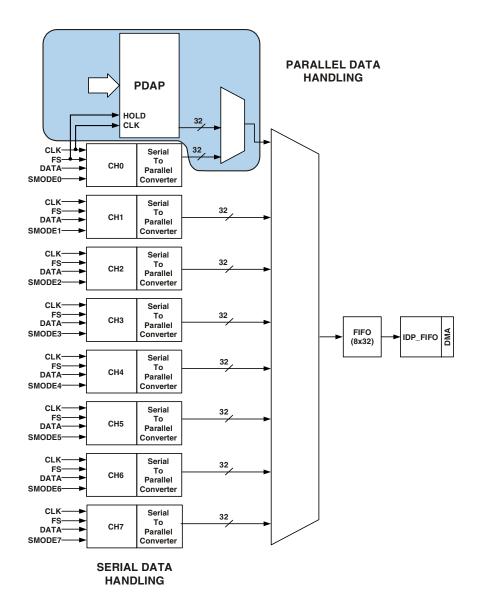

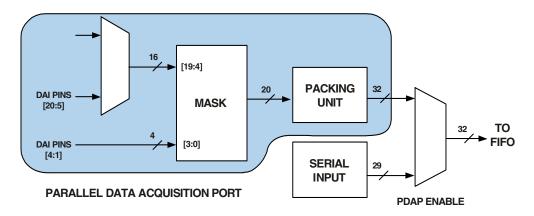

| Parallel Data Acquisition Port (PDAP)       |

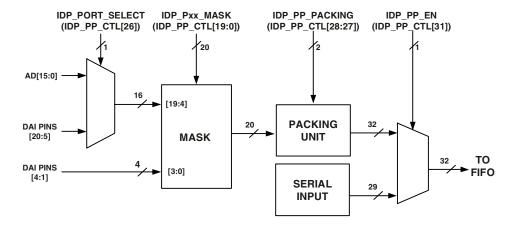

| Masking 6-9                                 |

| Packing Unit                                |

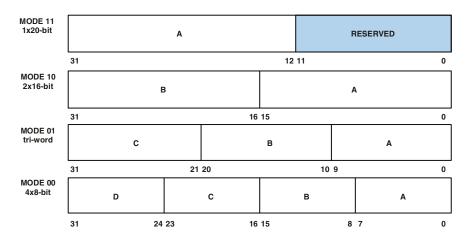

| Packing Mode 11                             |

| Packing Mode 10 6-11                        |

| Packing Mode 01                               | 6-11  |

|-----------------------------------------------|-------|

| Packing Mode 00                               | 6-11  |

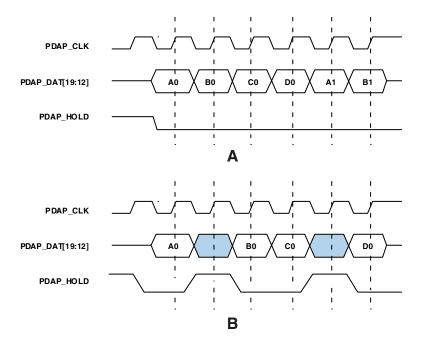

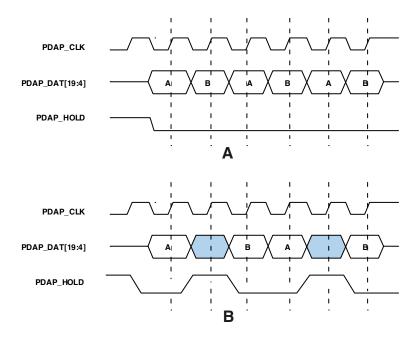

| Clocking Edge Selection                       | 6-12  |

| Hold Input                                    | 6-12  |

| PDAP Strobe                                   | 6-14  |

| FIFO Control and Status                       | 6-15  |

| FIFO to Memory Data Transfer                  | 6-16  |

| Interrupt-Driven Transfers                    | 6-17  |

| Starting an Interrupt-Driven Transfer         | 6-18  |

| Interrupt-Driven Transfer Notes               | 6-19  |

| DMA Transfers                                 | 6-20  |

| Simple DMA                                    | 6-20  |

| Starting A Simple DMA Transfer                | 6-21  |

| Ping-Pong DMA                                 | 6-22  |

| Starting Ping-Pong DMA Transfers              | 6-23  |

| DMA Transfer Notes                            | 6-25  |

| DMA Channel Parameter Registers               | 6-27  |

| IDP (DAI) Interrupt Service Routines for DMAs | 6-28  |

| FIFO Overflow                                 | 6-30  |

| Input Data Port Programming Example           | 6-31  |

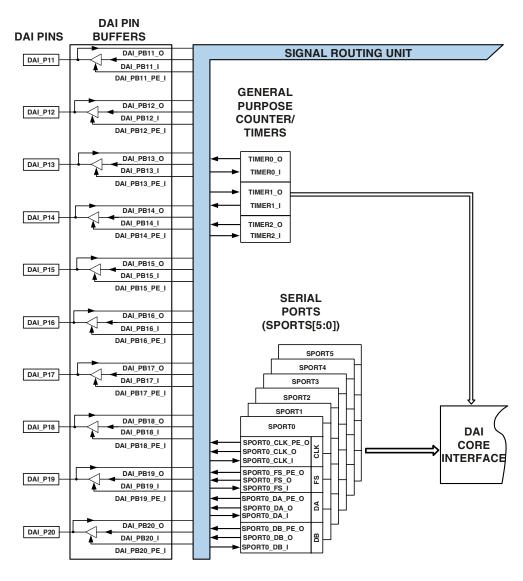

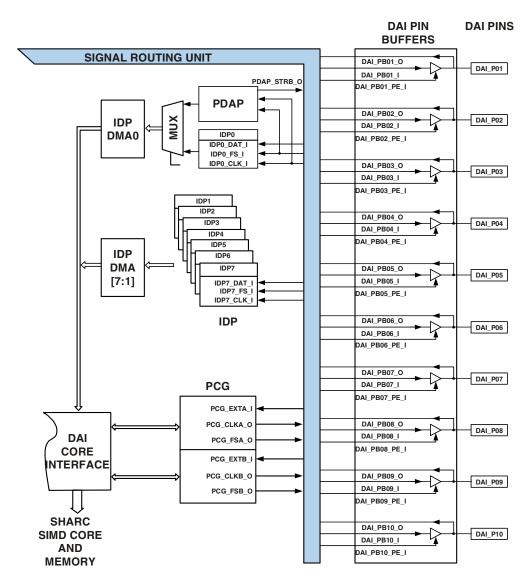

| DIGITAL AUDIO INTERFACE                       |       |

| Structure of the DAI                          | . 7-1 |

| DAI System Design                             | . 7-2 |

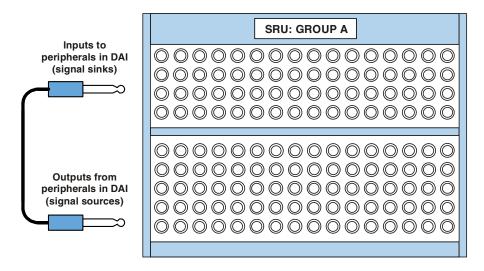

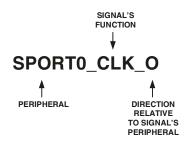

| Signal Routing Unit                           | . 7-6 |

| Connecting Peripherals                         | 7 |

|------------------------------------------------|---|

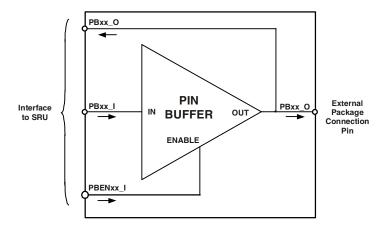

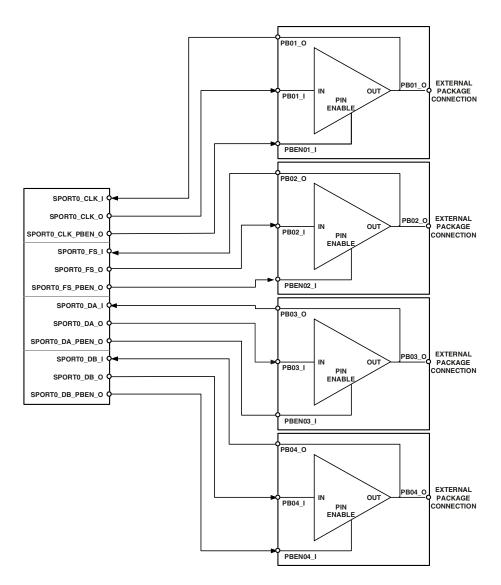

| Pins Interface                                 | 8 |

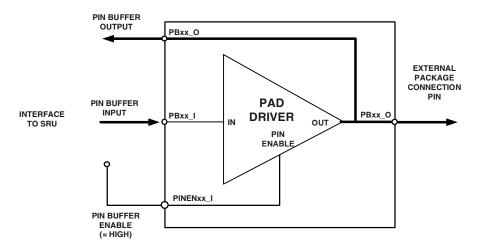

| Pin Buffers as Signal Output Pins              | 9 |

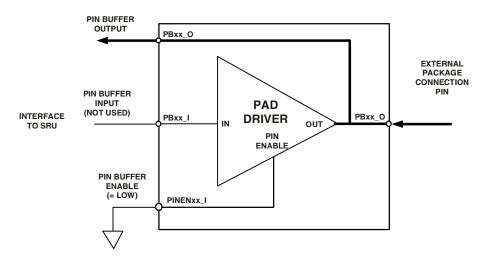

| Pin Buffers as Signal Input Pins               | 1 |

| Bidirectional Pin Buffers                      | 2 |

| Making Connections in the SRU                  | 3 |

| SRU Connection Groups                          | 6 |

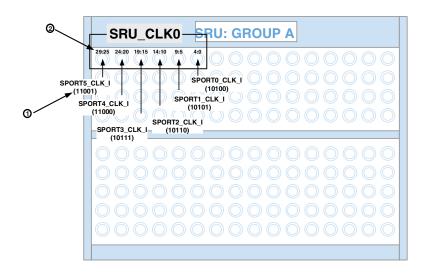

| Group A Connections—Clock Signals              | 6 |

| Group B Connections—Data Signals               | 8 |

| Group C Connections—Frame Sync Signals         | 0 |

| Group D Connections—Pin Signal Assignments 7-2 | 2 |

| Group E Connections—Miscellaneous Signals      | 4 |

| Group F Connections—Pin Enable Signals         | 6 |

| General-Purpose I/O (GPIO) and Flags           | 7 |

| Miscellaneous Signals                          | 7 |

| DAI Interrupt Controller                       | 7 |

| Relationship to the Core                       | 7 |

| DAI Interrupts                                 | 9 |

| High and Low Priority Latches                  | 0 |

| Rising and Falling Edge Masks                  | 1 |

| Using the SRU() Macro                          | 2 |

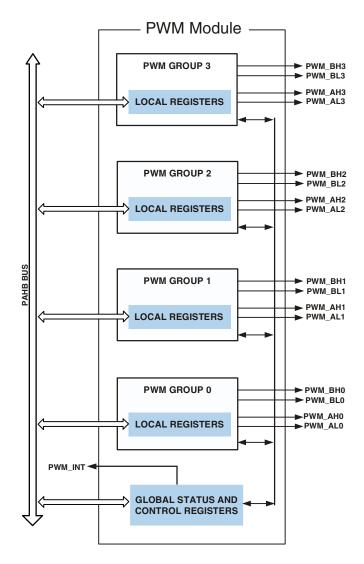

## PULSE WIDTH MODULATION

| PWM Implementation 8-1        |

|-------------------------------|

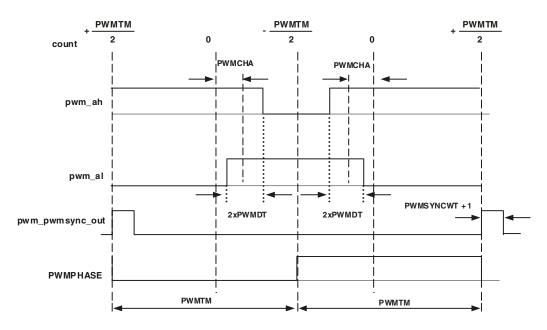

| PWM Waveforms 8-3             |

| Edge-Aligned Mode 8-3         |

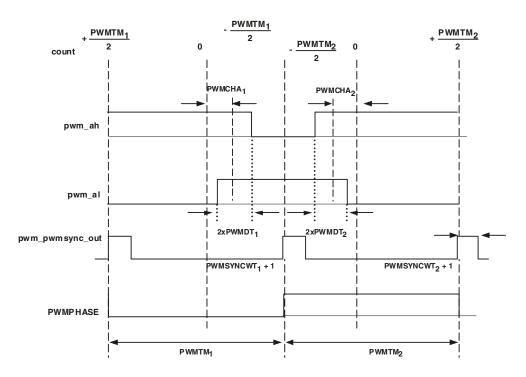

| Center-Aligned Mode           |

| Switching Frequencies         |

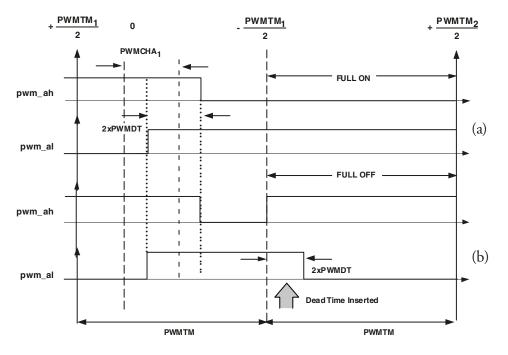

| Dead Time 8-6                 |

| Duty Cycles 8-7               |

| Duty Cycles and Dead Time 8-7 |

| Over-Modulation 8-11          |

| Update Modes 8-14             |

| Single-Update 8-14            |

| Double-Update 8-14            |

| Configurable Polarity 8-14    |

| PWM Pins and Signals 8-14     |

| Crossover 8-15                |

| PWM Accuracy 8-16             |

| PWM Registers 8-17            |

| Duty Cycle 8-18               |

| Output Enable 8-19            |

| Programming Example 8-19      |

## SONY/PHILLIPS DIGITAL INTERFACE

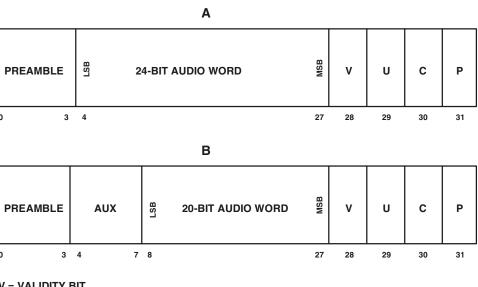

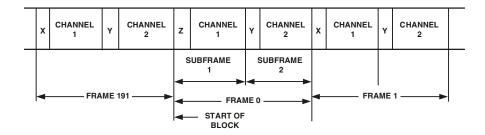

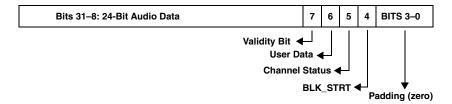

| AES3, S/PDIF Stream Format                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

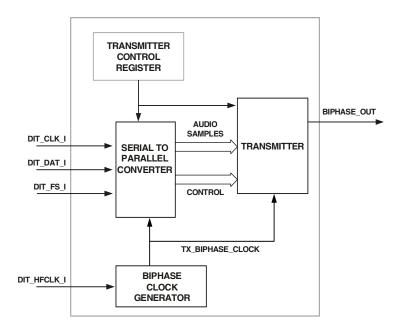

| S/PDIF Transmitter                                                                                                                                                                                                            |

| Channel Status                                                                                                                                                                                                                |

| SRU Control Registers for the S/PDIF Transmitter 9-7                                                                                                                                                                          |

| S/PDIF Control Registers                                                                                                                                                                                                      |

| S/PDIF Transmitter Programming Guidelines 9-9                                                                                                                                                                                 |

| Control Register                                                                                                                                                                                                              |

| SRU Programming for Input and Output Streams 9-10                                                                                                                                                                             |

| Control Register Programming and Enable 9-11                                                                                                                                                                                  |

| Programming Summary 9-11                                                                                                                                                                                                      |

| Structure of the S/PDIF and AES3 Format                                                                                                                                                                                       |

| S/PDIF Receiver                                                                                                                                                                                                               |

| S/PDIF Receiver Registers                                                                                                                                                                                                     |

| SRU Control Registers                                                                                                                                                                                                         |

| SKO Colition Registers                                                                                                                                                                                                        |

| S/PDIF Receiver Control Registers                                                                                                                                                                                             |

|                                                                                                                                                                                                                               |

| S/PDIF Receiver Control Registers                                                                                                                                                                                             |

| S/PDIF Receiver Control Registers                                                                                                                                                                                             |

| S/PDIF Receiver Control Registers                                                                                                                                                                                             |

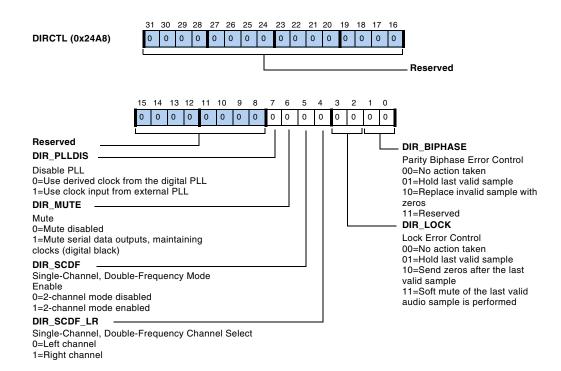

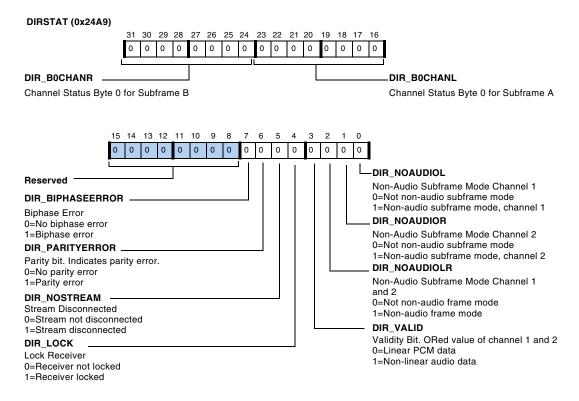

| S/PDIF Receiver Control Registers9-15S/PDIF Receiver Control Register (DIRCTL)9-15S/PDIF Receiver Status Register (DIRSTAT)9-15Channel Status for Subframes9-16                                                               |

| S/PDIF Receiver Control Registers9-15S/PDIF Receiver Control Register (DIRCTL)9-15S/PDIF Receiver Status Register (DIRSTAT)9-15Channel Status for Subframes9-16S/PDIF Receiver Programming Guidelines9-16                     |

| S/PDIF Receiver Control Registers9-15S/PDIF Receiver Control Register (DIRCTL)9-15S/PDIF Receiver Status Register (DIRSTAT)9-15Channel Status for Subframes9-16S/PDIF Receiver Programming Guidelines9-16Control Register9-16 |

| Status Bits                          | 9-17  |

|--------------------------------------|-------|

| Programming Summary                  | 9-17  |

| Phased-Locked Loop                   | 9-18  |

| Channel Status Decoding              | 9-19  |

| Compressed or Non-linear Audio Data  | 9-19  |

| Emphasized Audio Data                | 9-20  |

| Single-Channel Double-Frequency Mode | 9-20  |

| Error Handling                       | 9-21  |

| Interrupts                           | 9-23  |

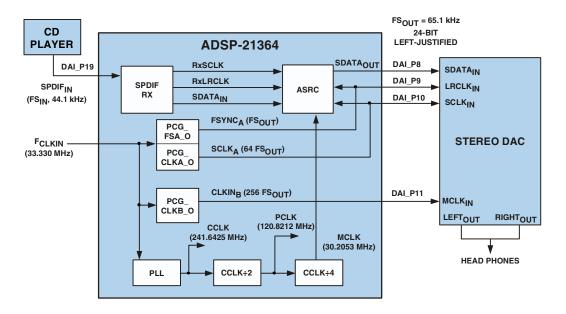

| ASYNCHRONOUS SAMPLE RATE CONVERTE    | R     |

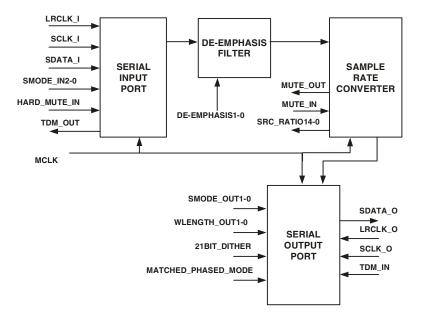

| Introduction                         | 10-1  |

| Overview                             | 10-1  |

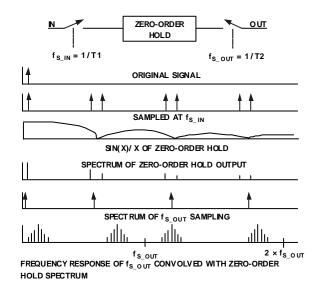

| Theory of Operation                  | 10-4  |

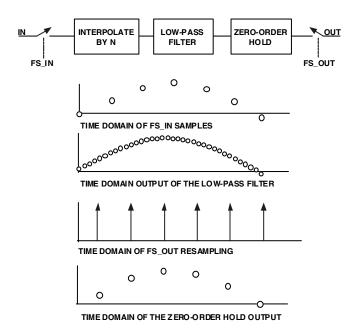

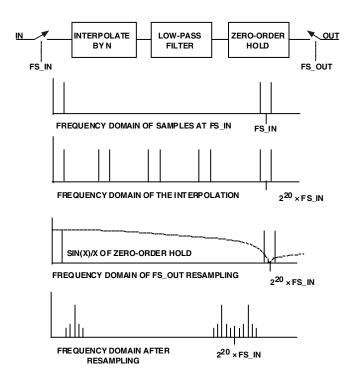

| Conceptual Model                     | 10-5  |

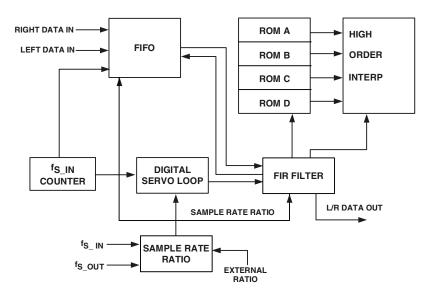

| Hardware Model                       | 10-7  |

| Sample Rate Converter Architecture   | 10-9  |

| Group Delay                          | 10-12 |

| SRC Operation                        | 10-12 |

| SRC Enable                           | 10-12 |

| Serial Data Ports                    | 10-13 |

| Data Format                          | 10-13 |

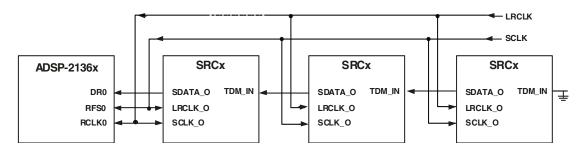

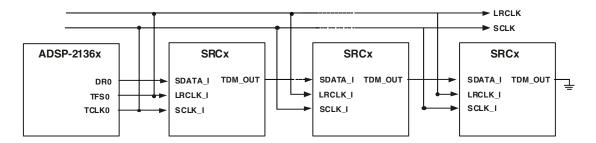

| TDM Output Mode                      | 10-14 |

| TDM Input Mode                       | 10-15 |

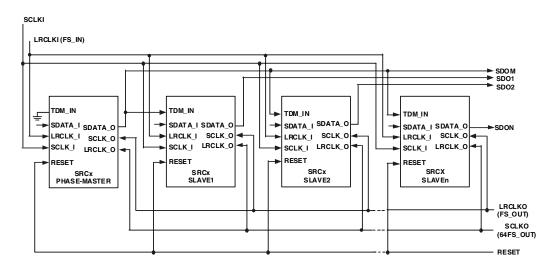

| Matched-Phase Mode                   | 10-16 |

| Bypass Mode 10-18                        |

|------------------------------------------|

| De-Emphasis Filter                       |

| Mute Control                             |

| Soft Mute                                |

| Hard Mute                                |

| Auto Mute                                |

| SRC Registers                            |

| Programming the SRC Module               |

| SRC Control Register Programming         |

| SRU Programming                          |

| SRC Mute-Out Interrupt                   |

| Sample Rate Ratio                        |

|                                          |

| Programming Summary                      |

|                                          |

|                                          |

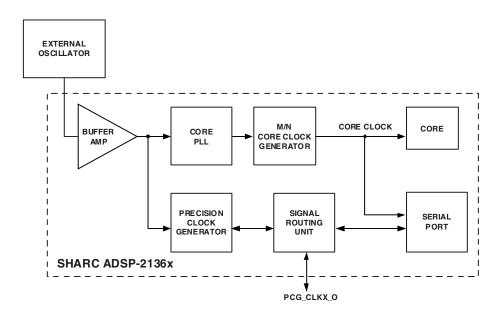

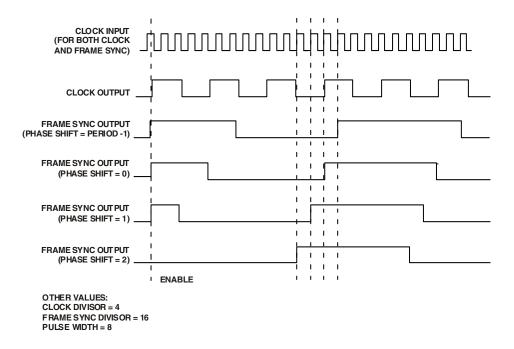

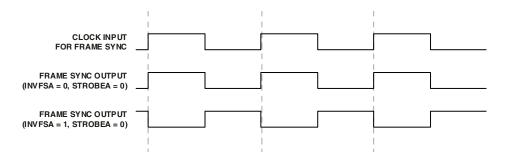

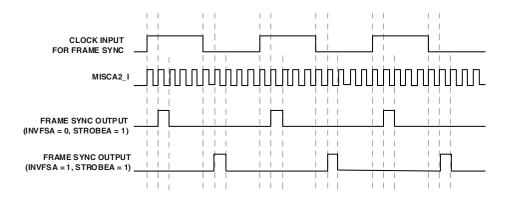

| PRECISION CLOCK GENERATOR                |

| PRECISION CLOCK GENERATOR  Clock Outputs |

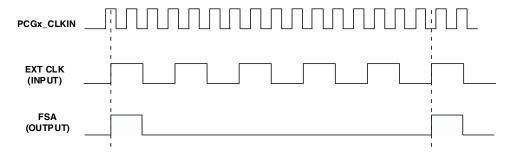

| Bypass as a Pass Through                            | 11-12  |

|-----------------------------------------------------|--------|

| Bypass as a One Shot                                | 11-12  |

| Programming Examples                                | 11-14  |

| PCG Setup for I2S or Left-Justified Formats         | 11-14  |

| Clock and Frame Sync Divisors PCG Channel B         | 11-19  |

| PCG Channel A and B Output Example                  | 11-22  |

| SYSTEM DESIGN                                       |        |

| Processor Pin Descriptions                          | . 12-2 |

| Pin Multiplexing                                    | . 12-2 |

| Address/Data Pins as FLAGs                          | 12-12  |

| Input Synchronization Delay                         | 12-12  |

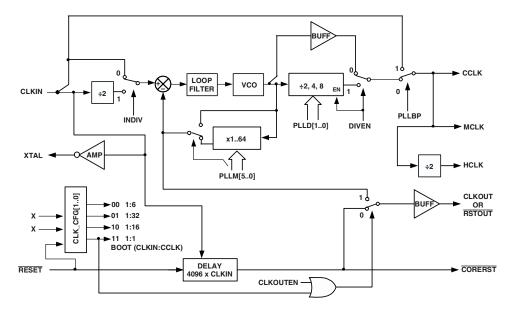

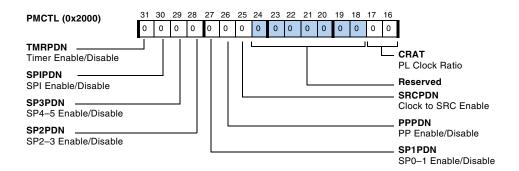

| Clock Derivation                                    | 12-13  |

| Using the Power Management Control Register (PMCTL) | 12-13  |

| PLL Programming Example 1                           | 12-16  |

| PLL Programming Example 2                           | 12-17  |

| Timing Specifications                               | 12-18  |

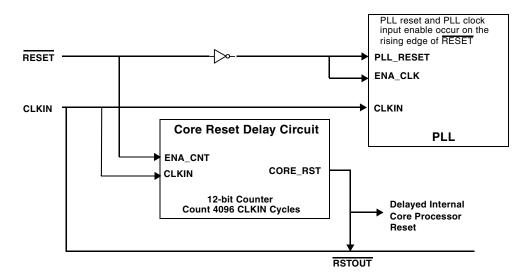

| RESET and CLKIN                                     | 12-21  |

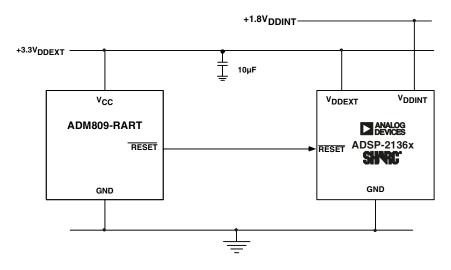

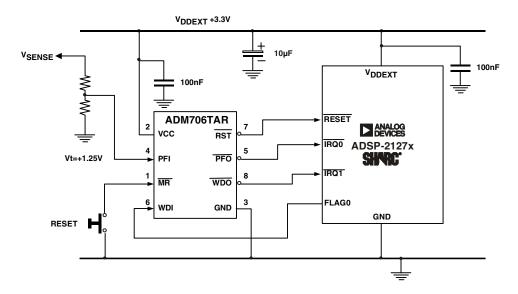

| Reset Generators                                    | 12-23  |

| Interrupt and Timer Pins                            | 12-25  |

| Core-Based Flag Pins                                | 12-26  |

| JTAG Interface Pins                                 | 12-26  |

| Phase-Locked Loop Start Up                          | 12-27  |

| Conditioning Input Signals                          | 12-28  |

| Reset Input Hysteresis                          | 8            |

|-------------------------------------------------|--------------|

| Designing for High Frequency Operation          | 9            |

| Clock Specifications and Jitter                 | 9            |

| Other Recommendations and Suggestions           | 0            |

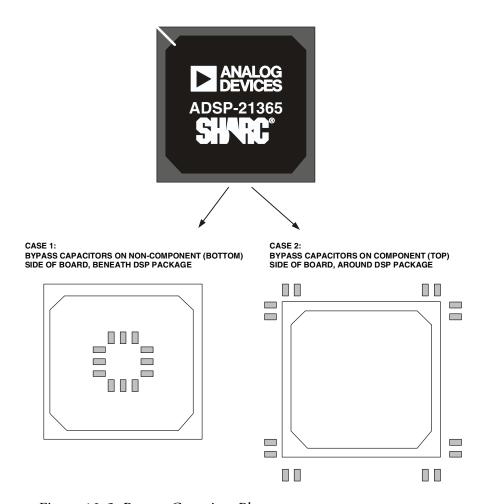

| Decoupling Capacitors and Ground Planes         | $\mathbf{C}$ |

| Oscilloscope Probes                             | 1            |

| Recommended Reading                             | 3            |

| Booting                                         | 4            |

| Parallel Port Booting                           | 5            |

| SPI Port Booting                                | 7            |

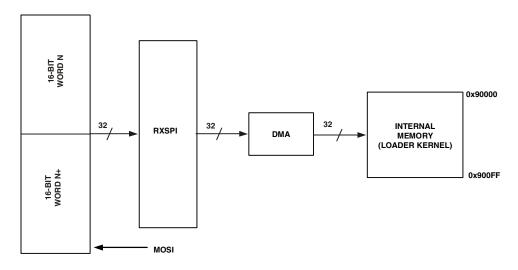

| 32-bit SPI Host Boot                            | 9            |

| 16-bit SPI Host Boot                            | 0            |

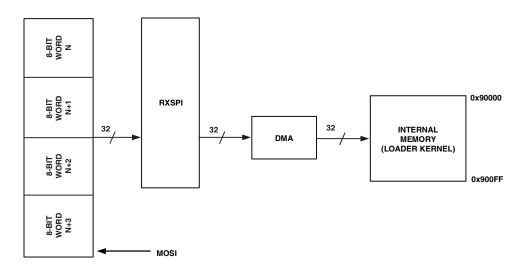

| 8-bit SPI Host Boot                             | 2            |

| Slave Boot Mode                                 | 3            |

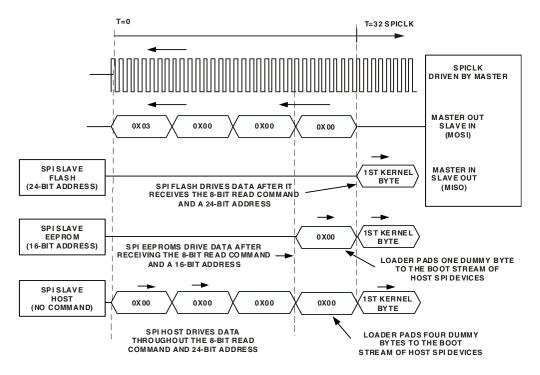

| Master Boot                                     | 5            |

| Booting From an SPI Flash                       | 8            |

| Booting From an SPI PROM (16-bit address) 12-48 | 8            |

| Booting From an SPI Host Processor              | 8            |

| Data Delays, Latencies, and Throughput          | 9            |

| Execution Stalls                                | 9            |

| DAG Stalls                                      | $\mathbf{c}$ |

| Memory Stalls                                   | $\mathbf{C}$ |

| IOP Register Stalls                             | 0            |

| DMA Stalls                                      | 1            |

| IOP Buffer Stalls                                              | -51 |

|----------------------------------------------------------------|-----|

| REGISTERS REFERENCE                                            |     |

| I/O Processor Registers                                        | 1-2 |

| Notes on Reading Register Drawings                             | 1-6 |

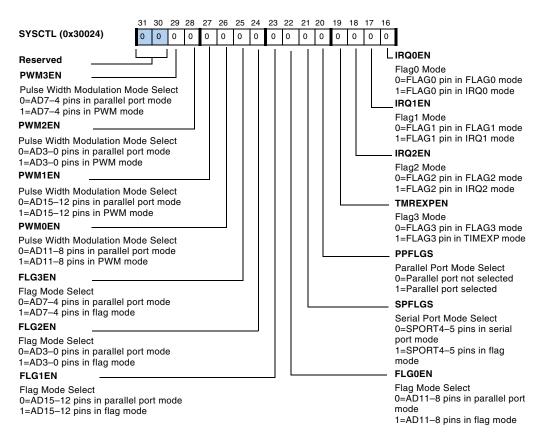

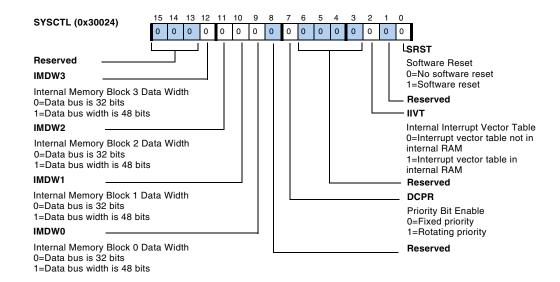

| System Control Register (SYSCTL)                               | 1-7 |

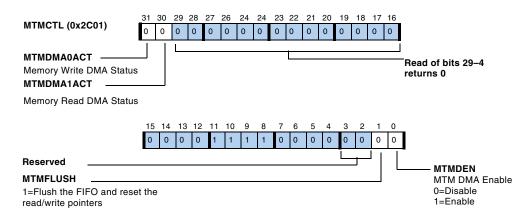

| Memory-to-Memory DMA Register                                  | 11  |

| Parallel Port Registers                                        | 12  |

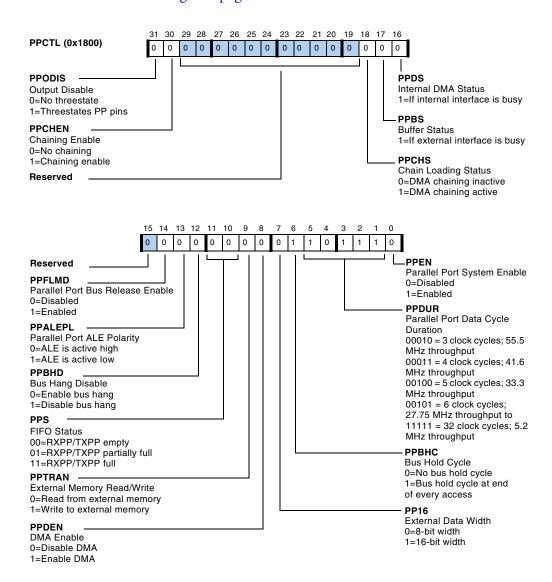

| Parallel Port Control Register (PPCTL)                         | 12  |

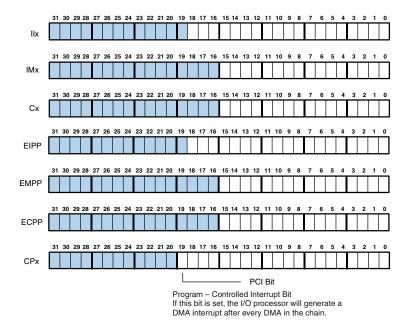

| Parallel Port DMA Registers                                    | 16  |

| Parallel Port DMA Transmit Register (TXPP) A-                  | 16  |

| Parallel Port DMA Receive Register (RXPP) A-                   | 17  |

| Parallel Port DMA Start Internal Index Address Register (IIPP) | 17  |

| Parallel Port DMA Internal Modifier Address Register (IMPP)    | -17 |

| Parallel Port DMA Internal Word Count Register (ICPP)          | -17 |

| Parallel Port DMA External Index Address Register (EIPP)       | -18 |

| Parallel Port DMA External Modifier Address Register (EMPP)    | -18 |

| Parallel Port DMA External Word Count Register (ECPP)          | -18 |

| Parallel Port DMA Chain Pointer Register (CPPP) A-             | 18  |

| Serial Port Registers                                          | 19  |

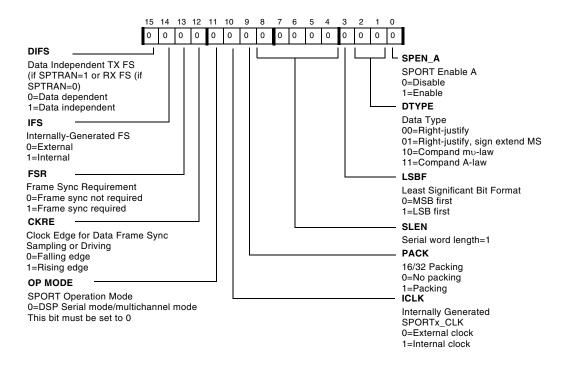

| SPORT Serial Control Registers (SPCTLx)                        |     |

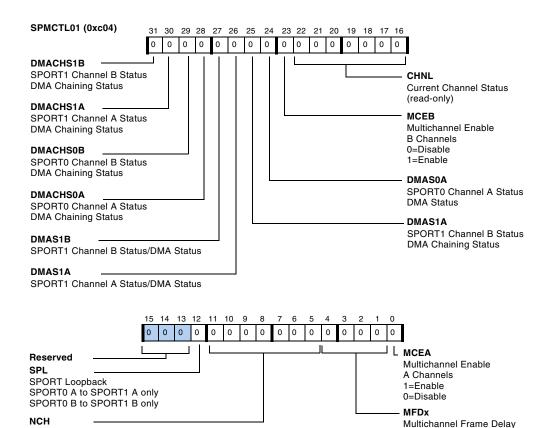

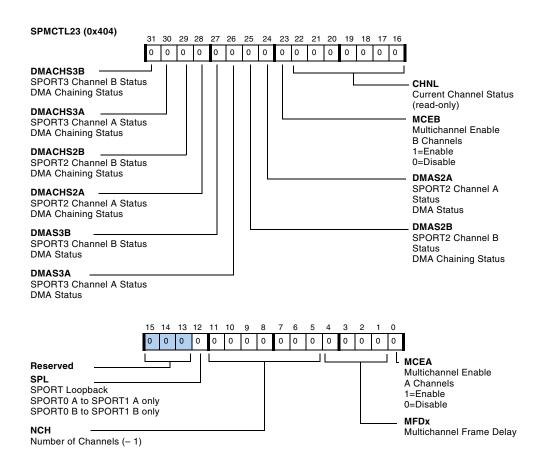

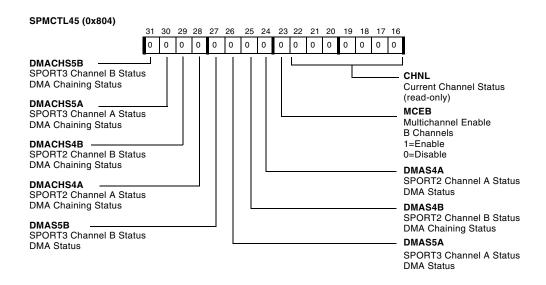

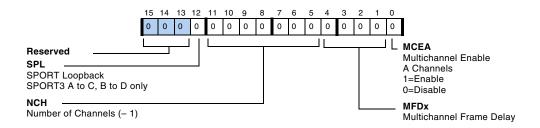

| SPORT Multichannel Control Registers (SPMCTLxy)      | A-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPORT Transmit Buffer Registers (TXSPx)              | A-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Receive Buffer Registers (RXSPx)               | A-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

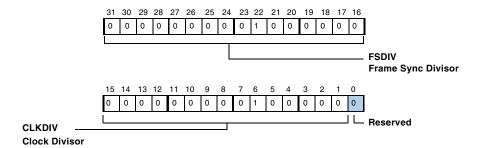

| SPORT Divisor Registers (DIVx)                       | A-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Count Registers (SPCNTx)                       | A-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Transmit Select Registers (MTxCSy)             | A-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Transmit Compand Registers (MTxCCSy)           | A-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Receive Select Registers (MRxCSx)              | A-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Receive Compand Registers (MRxCCSx)            | A-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT DMA Index Registers (IISPx)                    | A-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT DMA Modifier Registers (IMSPx)                 | A-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT DMA Count Registers (CSPx)                     | A-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPORT Chain Pointer Registers (CPSPx)                | A-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ial Peripheral Interface Registers                   | A-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

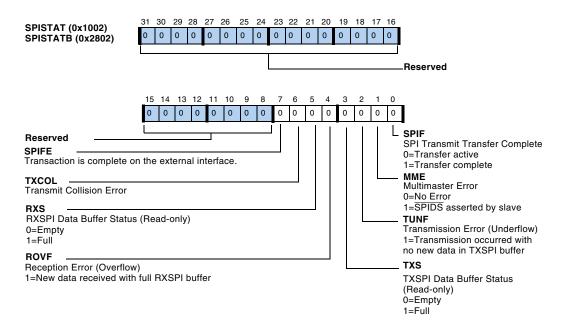

| SPI Port Status (SPISTAT, SPISTATB) Registers        | A-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

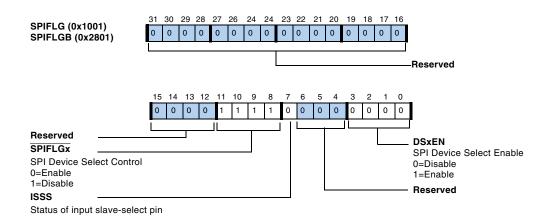

| SPI Port Flags Registers (SPIFLG, SPIFLGB)           | A-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

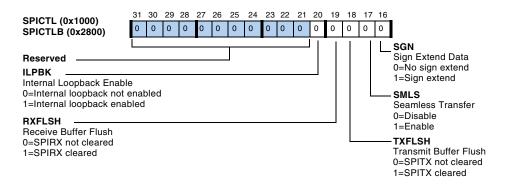

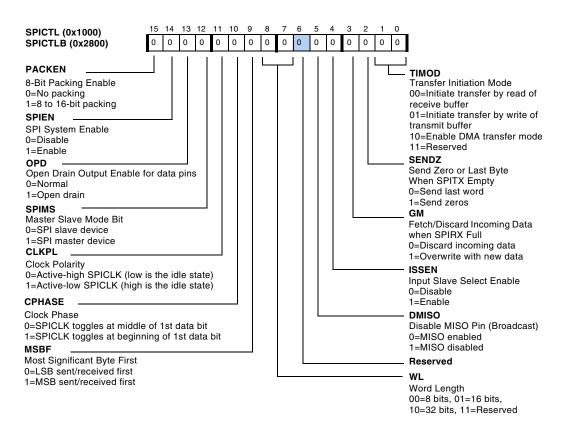

| SPI Control Registers (SPICTL, SPICTLB)              | A-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPI Receive Buffer Registers (RXSPI, RXSPIB)         | A-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXSPI Shadow Registers (RXSPI_SHADOW, RXSPIB_SHADOW) | A-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPI Transmit Buffer Registers (TXSPI, TXSPIB)        | A-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

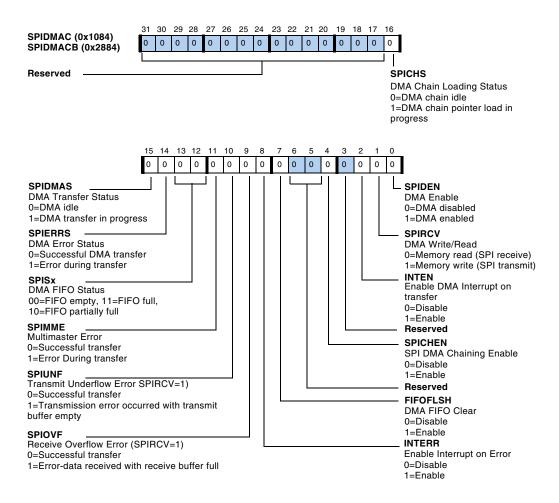

| SPI DMA Configuration Registers (SPIDMAC, SPIDMACB)  | A-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                      | SPORT Transmit Buffer Registers (TXSPx)  SPORT Receive Buffer Registers (RXSPx)  SPORT Divisor Registers (DIVx)  SPORT Count Registers (SPCNTx)  SPORT Transmit Select Registers (MTxCSy)  SPORT Transmit Compand Registers (MTxCSy)  SPORT Receive Select Registers (MRxCSx)  SPORT Receive Compand Registers (MRxCSx)  SPORT DMA Index Registers (IISPx)  SPORT DMA Modifier Registers (IMSPx)  SPORT DMA Count Registers (CSPx)  SPORT DMA Count Registers (CSPx)  SPORT Chain Pointer Registers (CPSPx)  ial Peripheral Interface Registers  SPI Port Status (SPISTAT, SPISTATB) Registers  SPI Port Flags Registers (SPIFLG, SPIFLGB)  SPI Control Registers (SPICTL, SPICTLB)  SPI Receive Buffer Registers (RXSPI, RXSPIB)  RXSPI Shadow Registers  (RXSPI_SHADOW, RXSPIB_SHADOW)  SPI Transmit Buffer Registers (TXSPI, TXSPIB)  SPI Baud Rate Registers (SPIBAUD, SPIBAUDB) |

| SPI DMA Start Address Registers (IISPI, IISPIB)                | . A-54 |

|----------------------------------------------------------------|--------|

| SPI DMA Address Modify Registers (IMSPI, IMSPIB)               | . A-54 |

| SPI DMA Word Count Registers (CSPI, CSPIB)                     | . A-54 |

| SPI DMA Chain Pointer Registers (CPSPI, CPSPIB)                | . A-55 |

| Input Data Port Registers                                      | . A-55 |

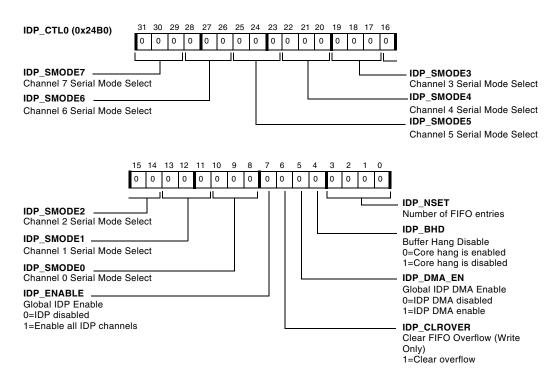

| Input Data Port Control Register 0 (IDP_CTL0)                  | . A-56 |

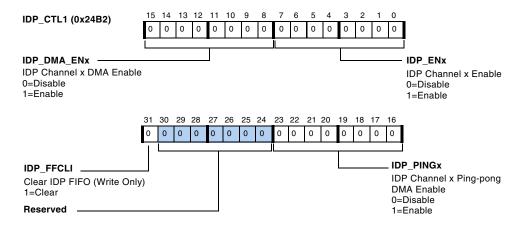

| Input Data Port Control Register 1 (IDP_CTL1)                  | . A-58 |

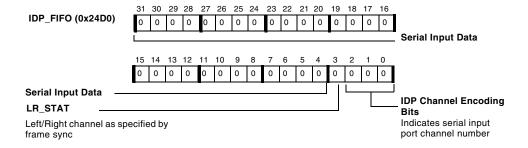

| Input Data Port FIFO Register (IDP_FIFO)                       | . A-59 |

| Input Data Port DMA Control Registers                          | . A-60 |

| Index (IDP_DMA_Ix)                                             | . A-60 |

| Modifier (IDP_DMA_Mx)                                          | . A-61 |

| Counter (IDP_DMA_Cx)                                           | . A-61 |

| Input Data Port Ping-pong DMA Registers                        | . A-62 |

| IDP Ping-pong Index Registers (IDP_DMA_IxA)                    | . A-62 |

| IDP Ping-pong Count Registers (IDP_DMA_PCx)                    | . A-63 |

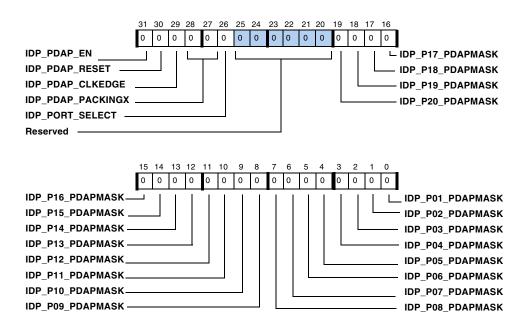

| Parallel Data Acquisition Port Control Register (IDP_PDAP_CTL) | A-64   |

| Sample Rate Converter Registers                                |        |

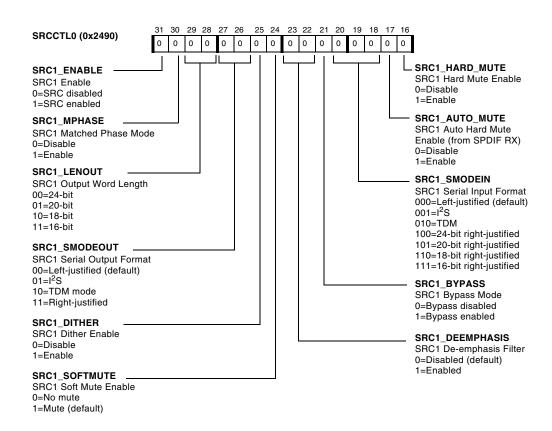

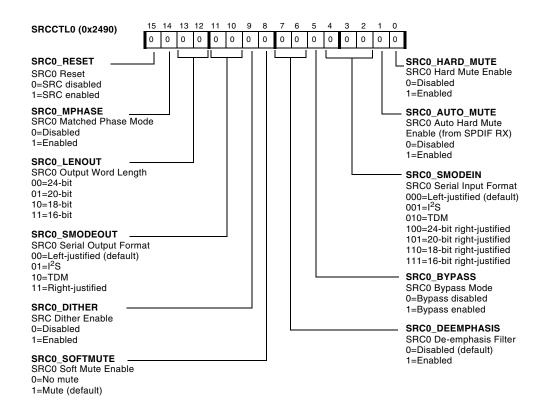

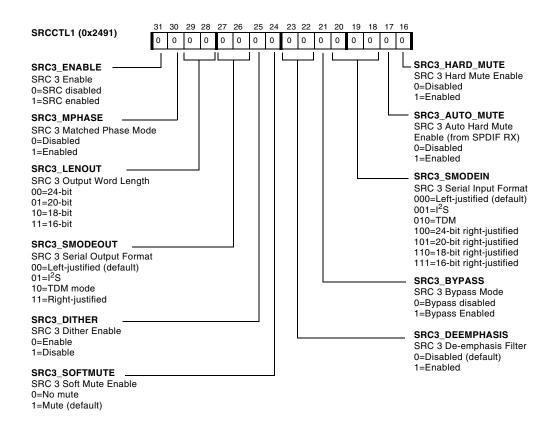

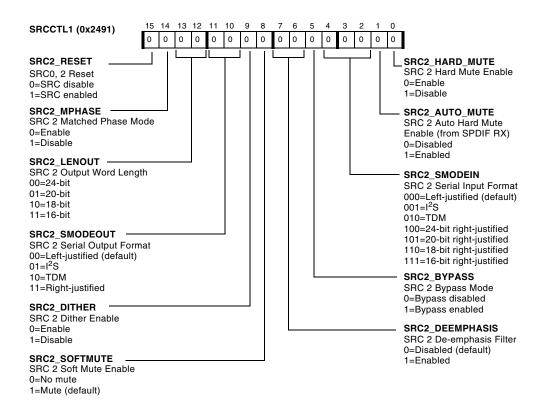

| SRC Control Registers (SRCCTLx)                                |        |

| SRC Mute Register (SRCMUTE)                                    |        |

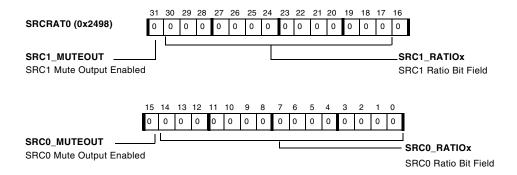

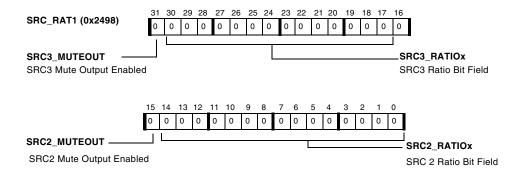

| SRC Ratio Registers (SRCRATx)                                  |        |

| Signal Routing Unit Registers                                  | . A-80 |

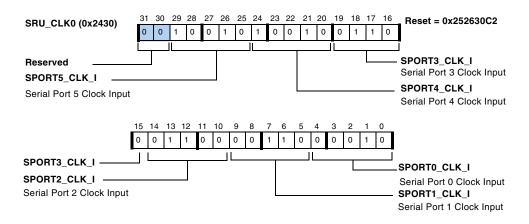

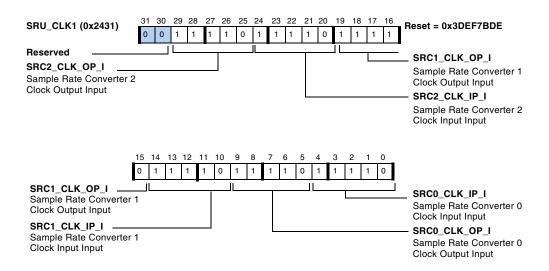

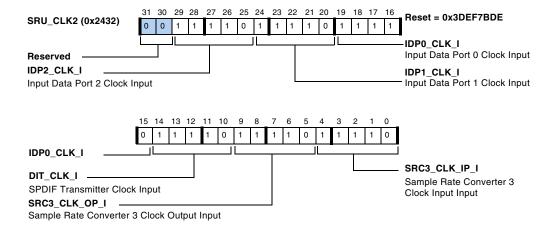

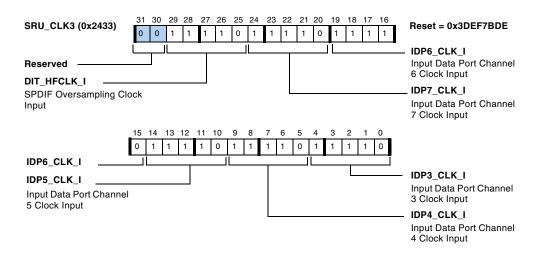

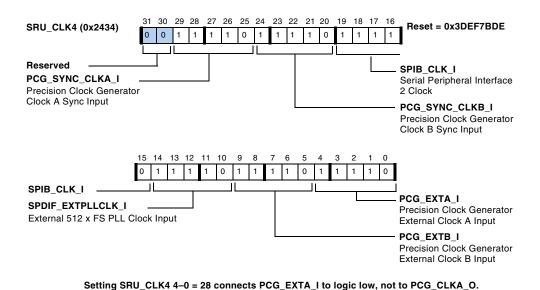

| Clock Routing Control Registers (SRU_CLKx, Group A)            | A-81   |

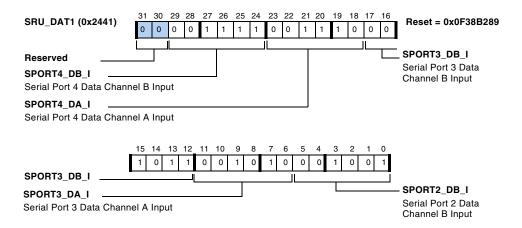

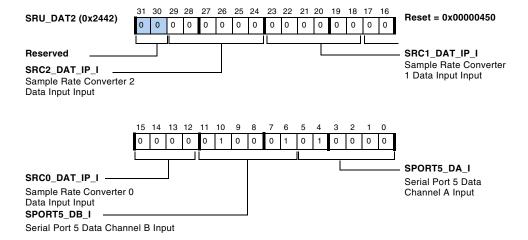

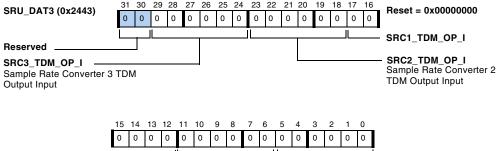

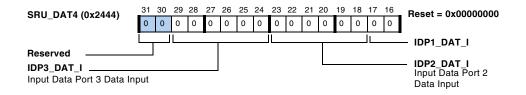

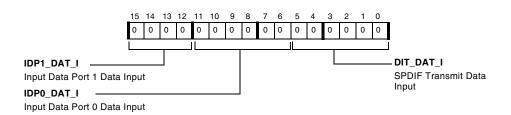

| Serial Data Routing Registers (SRU_DATx, Group B)              |        |

| Serial Data Routing Registers (SRU_DATX, Group b)              | . A-0) |

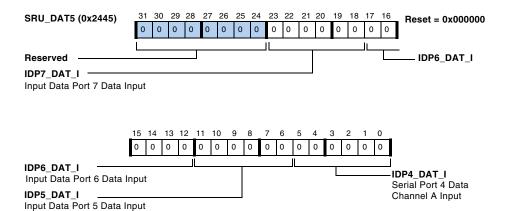

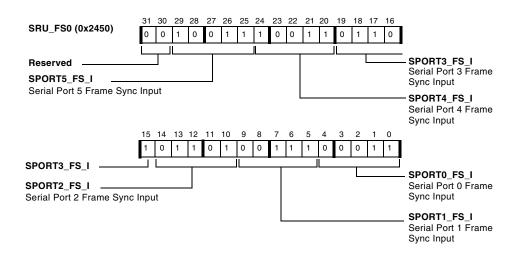

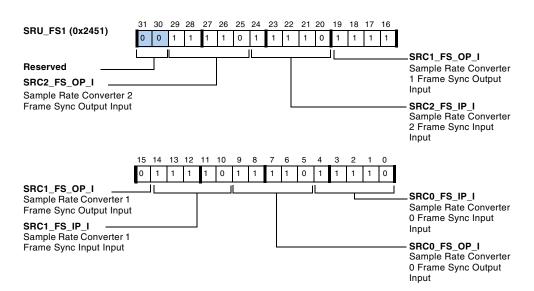

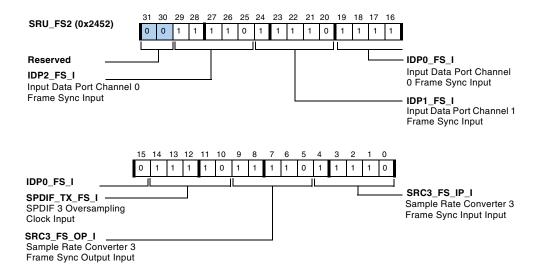

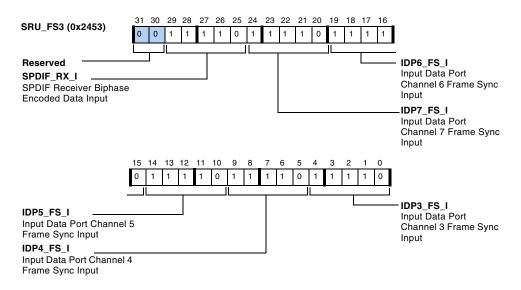

| Frame Sync Routing Control Registers (SRU_FSx, Group C)     | A-90         |

|-------------------------------------------------------------|--------------|

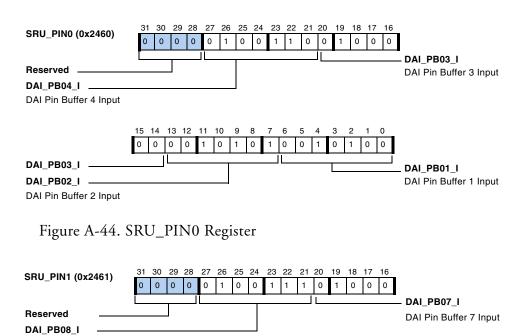

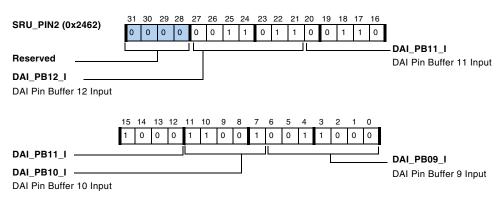

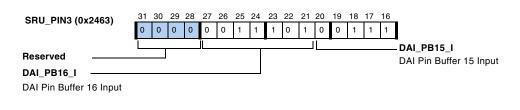

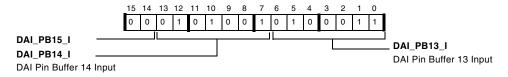

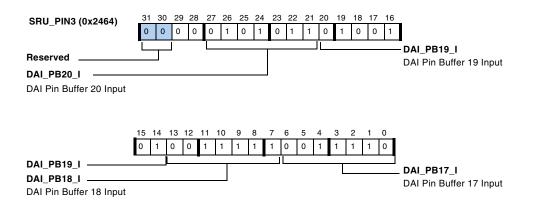

| Pin Signal Assignment Registers (SRU_PINx, Group D)         | A-94         |

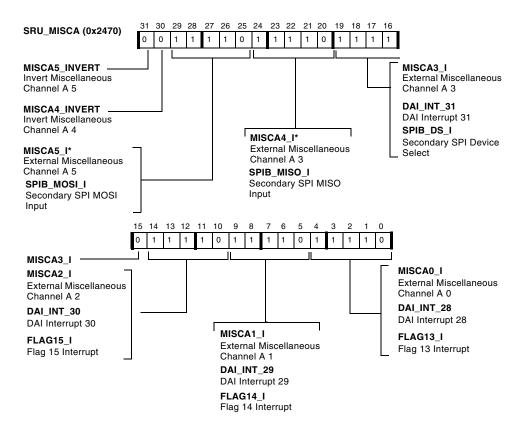

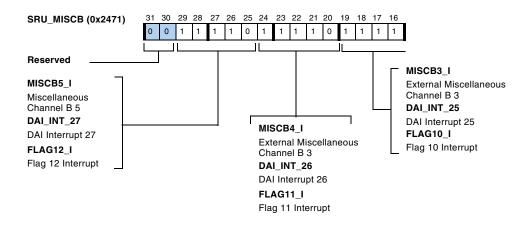

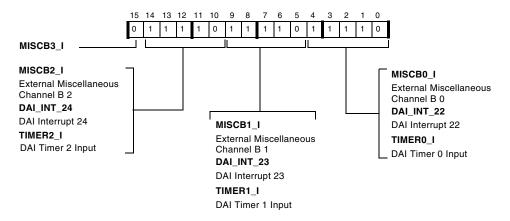

| Miscellaneous Signal Routing Registers (SRU_MISCx, Group E) | <b>L-101</b> |

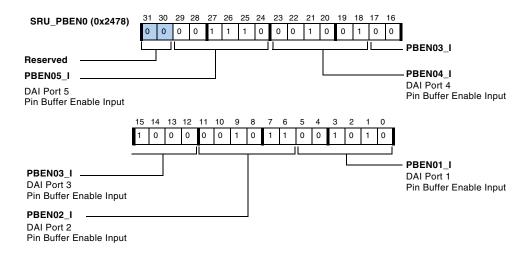

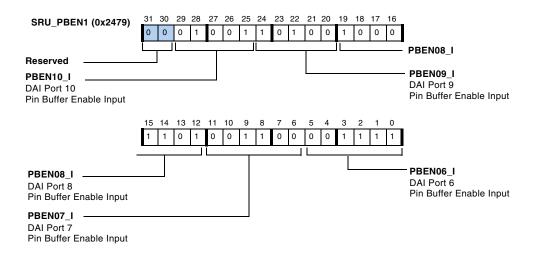

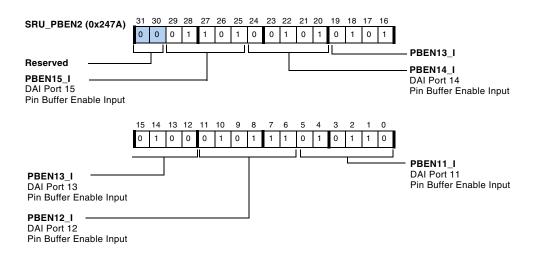

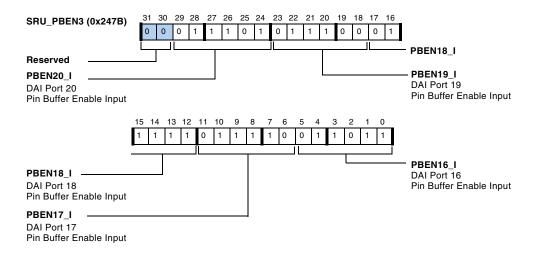

| DAI Pin Buffer Enable Registers (SRU_PBENx, Group F)        | L-105        |

| Special IDP Registers A                                     | -110         |

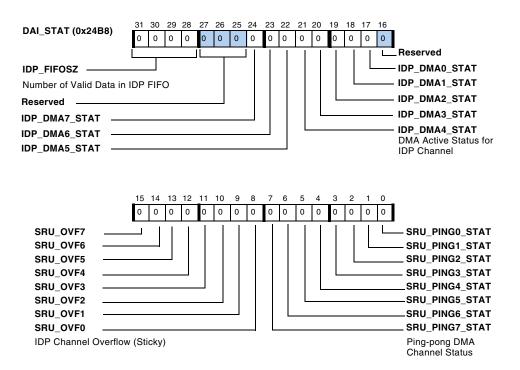

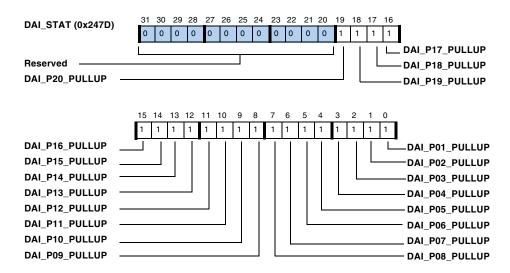

| Digital Audio Interface Status Register (DAI_STAT) A        | -110         |

| DAI Resistor Pull-up Enable Register (DAI_PIN_PULLUP)       | <u>113</u>   |

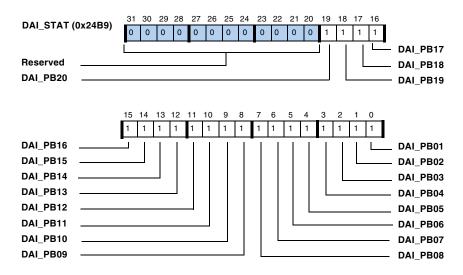

| DAI Pin Buffer Status Register (DAI_PBIN_STAT) A            | -114         |

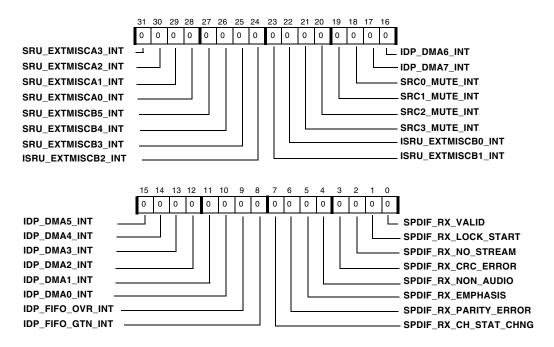

| DAI Interrupt Controller Registers A                        | -115         |

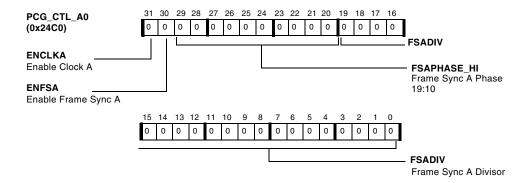

| Precision Clock Generator Registers A                       | -117         |

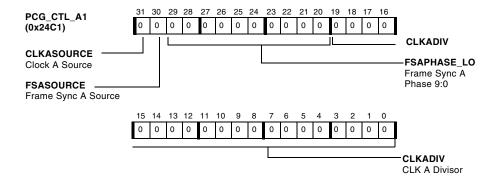

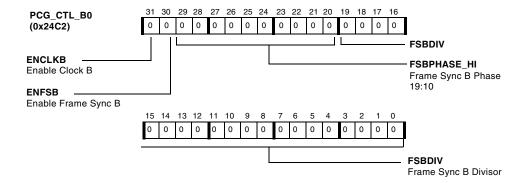

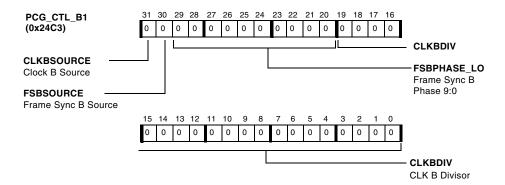

| Control Registers (PCG_CTLxx)                               | -118         |

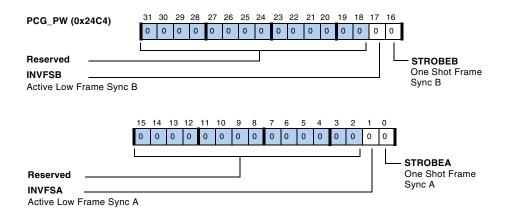

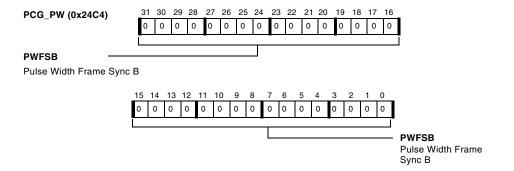

| Pulse Width Register (PCG_PW) A                             | -122         |

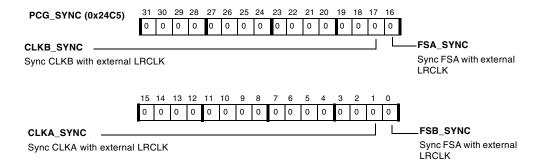

| Synchronization Register (PCG_SYNC) A                       | -124         |

| Pulse Width Modulation Registers A                          | -125         |

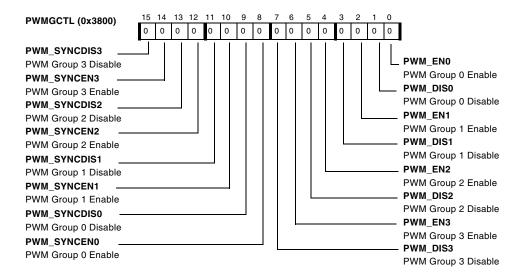

| PWM Global Control Register (PWMGCTL) A                     | -125         |

| PWM Global Status Register (PWMGSTAT) A                     | -126         |

| PWM Control Register (PWMCTLx) A                            | -126         |

| PWM Status Registers (PWMSTATx) A                           | -127         |

| PWM Period Registers (PWMPERIODx) A                         | -128         |

| PWM Output Disable Registers (PWMSEGx) A                    | -128         |

| PWM Polarity Select Registers (PWMPOLx) A                   | -129         |

|                                                             |              |

| PWM Channel Duty Control Registers (PWMAx, PWMBx)            | 30 |

|--------------------------------------------------------------|----|

| PWM Channel Low Duty Control Registers (PWMALx, PWMBLx)      | 31 |

| PWM Dead Time Registers (PWMDTx) A-13                        | 31 |

| Sony/Philips Digital Interface Registers                     | 32 |

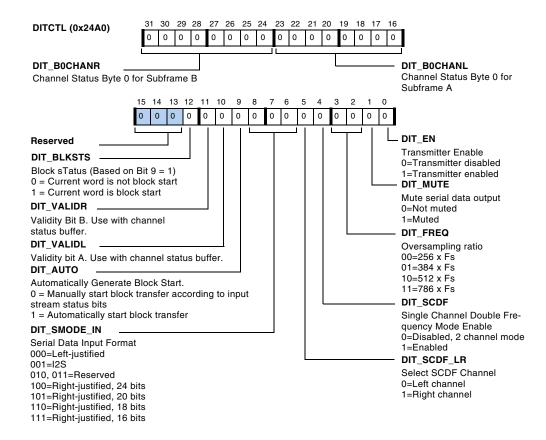

| Transmitter Control Register (DITCTL)                        | 32 |

| Left Channel Status for Subframe A Register (DITCHANL)       | 34 |

| Right Channel Status for Subframe B Register (DITCHANR)      | 35 |

| Receiver Control Register (DIRCTL)                           | 35 |

| Receiver Status Register (DIRSTAT)                           | 38 |

| Left Channel Status for Subframe A Register (DIRCHANL)       | 40 |

| Right Channel Status for Subframe B Register (DIRCHANR)      | 40 |

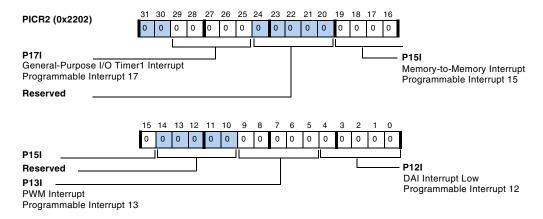

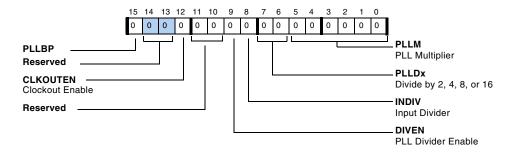

| Peripheral Interrupt Priority Control Registers (PICRx) A-14 | 41 |

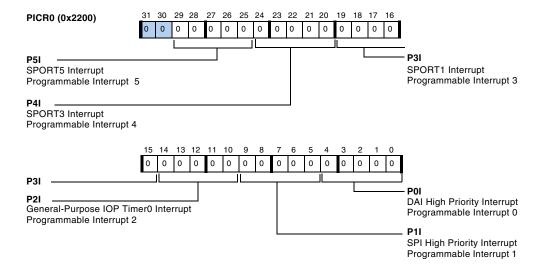

| Peripheral Interrupt Priority0 Control Register (PICR0) A-14 | 43 |

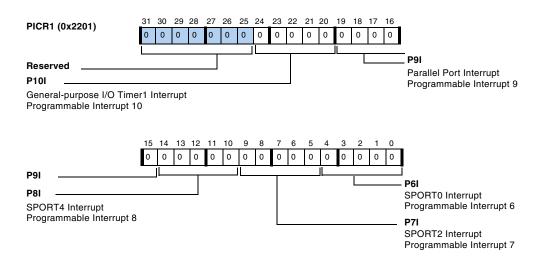

| Peripheral Interrupt Priority1 Control Register (PICR1) A-14 | 44 |

| Peripheral Interrupt Priority2 Control Register (PICR2) A-14 | 45 |

| Peripheral Interrupt Priority3 Control Register (PICR3) A-14 | 46 |

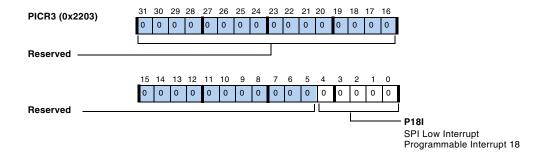

| Power Management Control Register (PMCTL)                    | 46 |

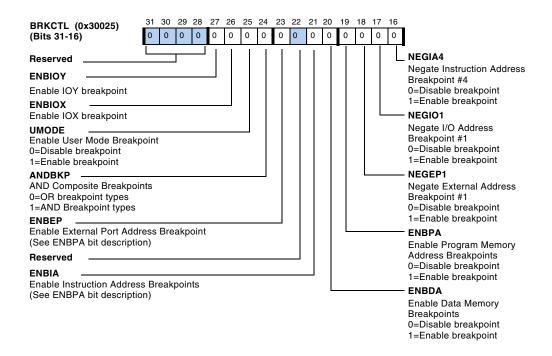

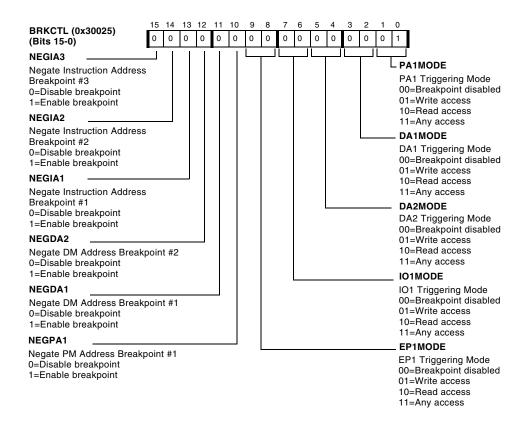

| Hardware Breakpoint Control Register (BRKCTL) A-15           |    |

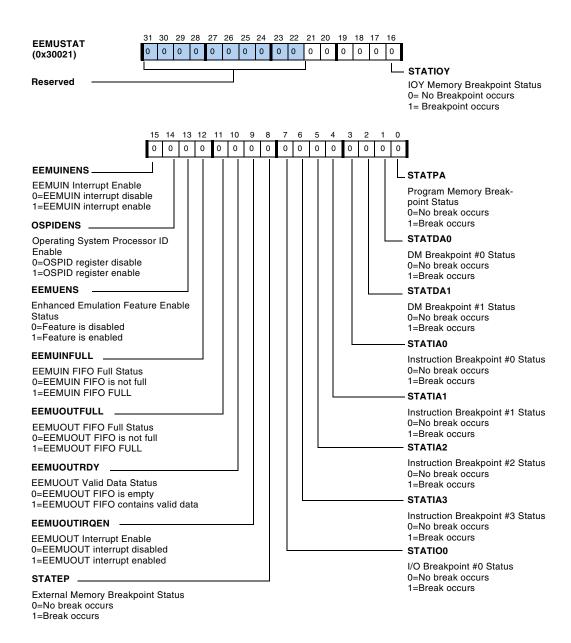

| Enhanced Emulation Status Register (EEMUSTAT) A-1            |    |

|                                                              |    |

## **INTERRUPTS**

| Interrupt Vector Tables                  | B-1  |

|------------------------------------------|------|

| Interrupt Priorities                     | B-4  |

| Interrupt Registers                      | В-6  |

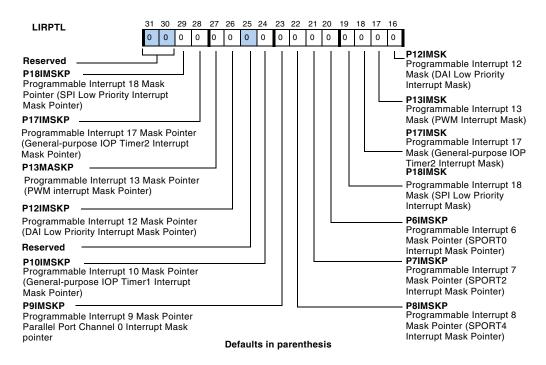

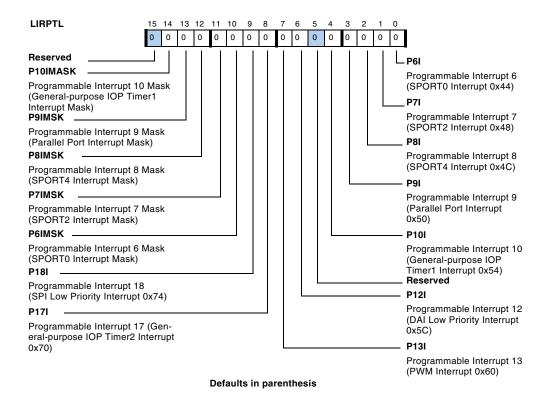

| Interrupt Register (LIRPTL)              | В-6  |

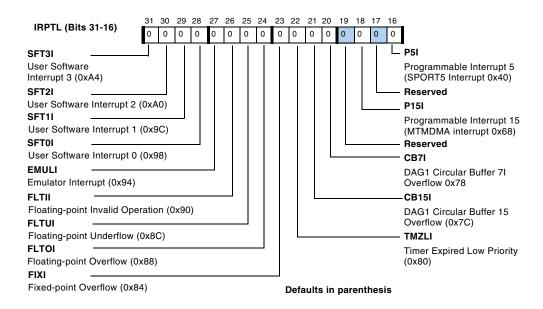

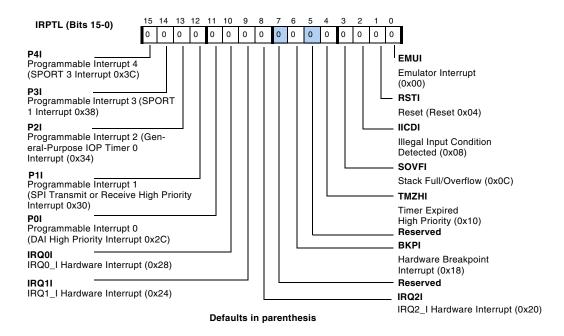

| Interrupt Latch Register (IRPTL)         | В-13 |

| Interrupt Mask Register (IMASK)          | В-18 |

| Interrupt Mask Pointer Register (IMASKP) | B-21 |

|                                          |      |

## **INDEX**

## **PREFACE**

Thank you for purchasing and developing systems using ADSP-2136x SHARC® processors from Analog Devices.

## **Purpose of This Manual**

The ADSP-2136x SHARC Processor Hardware Reference for the ADSP-21362/3/4/5/6 Processors contains information about the DSP architecture and DSP assembly language for these processors. These are 32-bit, fixed- and floating-point digital signal processors from Analog Devices for use in computing, communications, and consumer applications.

The manual provides information on how assembly instructions execute on the ADSP-2136x SHARC processor's architecture along with reference information about DSP operations.

## Intended Audience

The primary audience for this manual is a programmer who is familiar with Analog Devices processors. This manual assumes that the audience has a working knowledge of the appropriate processor architecture and instruction set. Programmers who are unfamiliar with Analog Devices processors can use this manual, but should supplement it with other texts (such as the appropriate hardware reference manuals and data sheets) that describe your target architecture.

## **Manual Contents**

This manual provides detailed information about the ADSP-2136x SHARC processors in the following chapters:

- Chapter 1, "Introduction"

Provides an architectural overview of the ADSP-2136x SHARC processor.

- Chapter 2, "I/O Processor"

Describes ADSP-2136x input/output processor architecture, and provides direct memory access (DMA) procedures for the processor peripherals.

- Chapter 3, "Parallel Port"

Describes how the ADSP-2136x processor's on-chip DMA controller acts as a machine for transferring data without core interruption.

- Chapter 4, "Serial Ports"

Describes the six dual data line serial ports. Each SPORT contains a clock, a frame sync, and two data lines that can be configured as either a receiver or transmitter pair.

- Chapter 5, "Serial Peripheral Interface Ports"

Describes the operation of the serial peripheral interface (SPI) port.

SPI devices communicate using a master-slave relationship and can achieve high data transfer rate because they can operate in full-duplex mode.

- Chapter 6, "Input Data Port"

Discusses the function of the input data port (IDP) which provides a low overhead method of routing signal routing unit (SRU) signals back to the core's memory.

- Chapter 7, "Digital Audio Interface"

Provides information about the digital applications interface (DAI) which allows you to attach an arbitrary number and variety of peripherals to the ADSP-2136x SHARC processor while retaining high levels of compatibility.

- Chapter 8, "Pulse Width Modulation"

Describes the implementation and use of the pulse width modulation module which provides a technique for controlling analog circuits with the microprocessor's digital outputs.

- Chapter 9, "Sony/Phillips Digital Interface"

Provides information on the use of the Sony/Phillips Digital Interface which is a standard audio file transfer format that allows the transfer of digital audio signals from one device to another without having to be converted to an analog signal.

- Chapter 10, "Asynchronous Sample Rate Converter"

Provides information on the sample rate converter (SRC) module.

This module performs synchronous or asynchronous sample rate conversion across independent stereo channels, without using any internal processor resources.

- Chapter 11, "Precision Clock Generator"

Details the precision clock generators (PCG), each of which generates a pair of signals derived from a clock input signal.

- Chapter 12, "System Design"

Describes system design features of the ADSP-2136x SHARC processor. These include power, reset, clock, JTAG, and booting, as well as pin descriptions and other system-level information.

- Appendix A, "Registers Reference"

Provides a graphical presentation of all registers and describes the bit usage in each register.

#### What's New in This Manual

- Appendix B "Interrupts",

Provides a complete listing of the registers that are used to configure and control interrupts.

- This hardware reference is a companion document to the ADSP-2136x SHARC Processor Programming Reference.

## What's New in This Manual

This is the first edition (Revision 1.0) of the ADSP-2136x SHARC Processor Hardware Reference. In future revisions this section will document additions and corrections from previous editions of the book.

## **Technical or Customer Support**

You can reach Analog Devices, Inc. Customer Support in the following ways:

- Visit the Embedded Processing and DSP products Web site at http://www.analog.com/processors/technicalSupport

- E-mail tools questions to processor.tools.support@analog.com

- E-mail processor questions to processor.support@analog.com (World wide support) processor.europe@analog.com (Europe support) processor.china@analog.com (China support)

- Phone questions to 1-800-ANALOGD

- Contact your Analog Devices, Inc. local sales office or authorized distributor

#### Send questions by mail to:

Analog Devices, Inc. One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

## **Supported Processors**

The following is the list of Analog Devices, Inc. processors supported in VisualDSP++®.

#### TigerSHARC® (ADSP-TSxxx) Processors

The name *TigerSHARC* refers to a family of floating-point and fixed-point [8-bit, 16-bit, and 32-bit] processors. VisualDSP++ currently supports the following TigerSHARC families: ADSP-TS101 and ADSP-TS20x.

#### SHARC (ADSP-21xxx) Processors

The name *SHARC* refers to a family of high-performance, 32-bit, floating-point processors that can be used in speech, sound, graphics, and imaging applications. VisualDSP++ currently supports the following SHARC families: ADSP-2106x, ADSP-2116x, ADSP-2126x, and ADSP-2136x.

#### Blackfin® (ADSP-BFxxx) Processors

The name *Blackfin* refers to a family of 16-bit, embedded processors. VisualDSP++ currently supports the following Blackfin families: ADSP-BF53x and ADSP-BF56x.

## **Product Information**

You can obtain product information from the Analog Devices web site, from the product CD-ROM, or from the printed publications (manuals).

Analog Devices is online at www.analog.com. Our Web site provides information about a broad range of products—analog integrated circuits, amplifiers, converters, and digital signal processors.

## MyAnalog.com

MyAnalog.com is a free feature of the Analog Devices Web site that allows customization of a Web page to display only the latest information on products you are interested in. You can also choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests. MyAnalog.com provides access to books, application notes, data sheets, code examples, and more.

#### Registration

Visit www.myanalog.com to sign up. Click **Register** to use MyAnalog.com. Registration takes about five minutes and serves as a means to select the information you want to receive.

If you are already a registered user, just log on. Your user name is your e-mail address.

#### **Processor Product Information**

For information on embedded processors and DSPs, visit our Web site at www.analog.com/processors, which provides access to technical publications, data sheets, application notes, product overviews, and product announcements.

You may also obtain additional information about Analog Devices and its products in any of the following ways.

- E-mail questions or requests for information to processor.support@analog.com (World wide support) processor.europe@analog.com (Europe support) processor.china@analog.com (China support)

- Fax questions or requests for information to 1-781-461-3010 (North America) +49-89-76903-157 (Europe)

- Access the FTP Web site at ftp ftp.analog.com (or ftp 137.71.25.69) ftp://ftp.analog.com

#### **Related Documents**

The following publications that describe the ADSP-2136x SHARC processors (and related processors) can be ordered from any Analog Devices sales office:

- ADSP-21362 SHARC Processor Data Sheet

- ADSP-21363 SHARC Processor Data Sheet

- ADSP-21364 SHARC Processor Data Sheet

- ADSP-21365/ADSP-21366 SHARC Processor Data Sheet

- ADSP-21367 SHARC Processor Data Sheet

- ADSP-21368 SHARC Processor Data Sheet

- ADSP-21369 SHARC Processor Data Sheet

- ADSP-2136x SHARC Processor Programming Reference

#### **Product Information**

For information on product related development software and Analog Devices processors, see these publications:

- VisualDSP++ User's Guide

- VisualDSP++ C/C++ Compiler and Library Manual

- VisualDSP++ Assembler and Preprocessor Manual

- VisualDSP++ Linker and Utilities Manual

- VisualDSP++ Kernel (VDK) User's Guide

Visit the Technical Library Web site to access all processor and tools manuals and data sheets:

http://www.analog.com/processors/technical\_library

#### Online Technical Documentation

Online documentation comprises the VisualDSP++ Help system, software tools manuals, hardware tools manuals, processor manuals, the Dinkum Abridged C++ library, and Flexible License Manager (FlexLM) network license manager software documentation. You can easily search across the entire VisualDSP++ documentation set for any topic of interest. For easy printing, supplementary .PDF files of most manuals are also provided.

Each documentation file type is described as follows.

| File             | Description                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .CHM             | Help system files and manuals in Help format                                                                                                                                               |

| .HTM or<br>.HTML | Dinkum Abridged C++ library and FlexLM network license manager software documentation. Viewing and printing the .HTML files requires a browser, such as Internet Explorer 4.0 (or higher). |

| .PDF             | VisualDSP++ and processor manuals in Portable Documentation Format (PDF). Viewing and printing the .PDF files requires a PDF reader, such as Adobe Acrobat Reader (4.0 or higher).         |

If documentation is not installed on your system as part of the software installation, you can add it from the VisualDSP++ CD-ROM at any time by running the tools installation. Access the online documentation from the VisualDSP++ environment, Windows® Explorer, or the Analog Devices web site.

#### Accessing Documentation From VisualDSP++

From the VisualDSP++ environment:

- Access VisualDSP++ online Help from the Help menu's Contents,

Search, and Index commands.

- Open online Help from context-sensitive user interface items (toolbar buttons, menu commands, and windows).

#### **Accessing Documentation From Windows**

In addition to any shortcuts you may have constructed, there are many ways to open VisualDSP++ online Help or the supplementary documentation from Windows.

Help system files (.CHM) are located in the Help folder, and PDF files are located in the Docs folder of your VisualDSP++ installation CD-ROM. The Docs folder also contains the Dinkum Abridged C++ library and the FlexLM network license manager software documentation.

#### Using Windows Explorer

- Double-click the vdsp-help.chm file, which is the master Help system, to access all the other .CHM files.

- Double-click any file that is part of the VisualDSP++ documentation set.

#### **Product Information**

#### Using the Windows Start Button

- Access VisualDSP++ online Help by clicking the Start button and choosing Programs, Analog Devices, VisualDSP++, and VisualDSP++ Documentation.

- Access the .PDF files by clicking the Start button and choosing Programs, Analog Devices, VisualDSP++, Documentation for Printing, and the name of the book.

#### Accessing Documentation From the Web

Download manuals at the following Web site: http://www.analog.com/processors/technical\_library

Select a processor family and book title. Download archive (.ZIP) files, one for each manual. Use any archive management software, such as WinZip, to decompress downloaded files.

#### **Printed Manuals**

For general questions regarding literature ordering, call the Literature Center at 1-800-ANALOGD (1-800-262-5643) and follow the prompts.

#### VisualDSP++ Documentation Set

To purchase VisualDSP++ manuals, call 1-603-883-2430. The manuals may be purchased only as a kit.

If you do not have an account with Analog Devices, you are referred to Analog Devices distributors. For information on our distributors, log onto http://www.analog.com/salesdir.

### Hardware Tools Manuals

To purchase EZ-KIT Lite® and In-Circuit Emulator (ICE) manuals, call 1-603-883-2430. The manuals may be ordered by title or by product number located on the back cover of each manual.

### **Processor Manuals**

Hardware reference and instruction set reference manuals may be ordered through the Literature Center at 1-800-ANALOGD (1-800-262-5643), or downloaded from the Analog Devices Web site. Manuals may be ordered by title or by product number located on the back cover of each manual.

### **Data Sheets**

All data sheets (preliminary and production) may be downloaded from the Analog Devices Web site. Only production (final) data sheets (Rev. 0, A, B, C, and so on) can be obtained from the Literature Center at 1-800-ANALOGD (1-800-262-5643); they also can be downloaded from the Web site.

To have a data sheet faxed to you, call the Analog Devices Faxback System at 1-800-446-6212. Follow the prompts and a list of data sheet code numbers will be faxed to you. If the data sheet you want is not listed, check for it on the Web site.

# Conventions

Text conventions used in this manual are identified and described as follows.

| Example                      | Description                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Close command<br>(File menu) | Titles in reference sections indicate the location of an item within the VisualDSP++ environment's menu system (for example, the Close command appears on the File menu).                                                                                                                                      |  |  |  |  |

| {this   that}                | Alternative items in syntax descriptions appear within curly brackets and separated by vertical bars; read the example as this or that. One or the other is required.                                                                                                                                          |  |  |  |  |

| [this   that]                | Optional items in syntax descriptions appear within brackets and separated by vertical bars; read the example as an optional this or that.                                                                                                                                                                     |  |  |  |  |

| [this,]                      | Optional item lists in syntax descriptions appear within brackets delimited by commas and terminated with an ellipse; read the example as an optional comma-separated list of this.                                                                                                                            |  |  |  |  |

| .SECTION                     | Commands, directives, keywords, and feature names are in text with letter gothic font.                                                                                                                                                                                                                         |  |  |  |  |

| filename                     | Non-keyword placeholders appear in text with italic style format.                                                                                                                                                                                                                                              |  |  |  |  |

| <b>(i)</b>                   | Note: For correct operation, A Note: provides supplementary information on a related topic. In the online version of this book, the word Note appears instead of this symbol.                                                                                                                                  |  |  |  |  |

| ×                            | Caution: Incorrect device operation may result if  Caution: Device damage may result if  A Caution: identifies conditions or inappropriate usage of the product that could lead to undesirable results or product damage. In the online version of this book, the word Caution appears instead of this symbol. |  |  |  |  |

| $\Diamond$                   | Warning: Injury to device users may result if A Warning: identifies conditions or inappropriate usage of the product that could lead to conditions that are potentially hazardous for devices users. In the online version of this book, the word Warning appears instead of this symbol.                      |  |  |  |  |

Additional conventions, which apply only to specific chapters, may appear throughout this document.

# Conventions

# 1 INTRODUCTION