# **Class-D Audio Power Amplifier**

**ADAU1590**

#### **FEATURES**

Integrated stereo modulator and power stage 0.005% THD + N 101 dB dynamic range PSRR >55 dB R<sub>DS-ON</sub> < 0.3  $\Omega$  (per transistor) Efficiency > 90% (8  $\Omega$ ) EMI-optimized modulator On/off-mute pop-noise suppression Short-circuit protection Overtemperature protection

#### **APPLICATIONS**

Flat panel televisions PC audio systems Mini-components

#### **GENERAL DESCRIPTION**

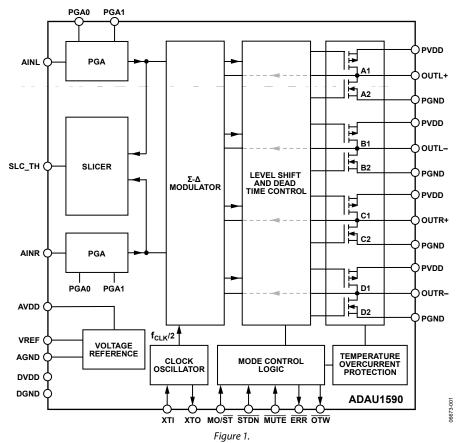

The ADAU1590 is a 2-channel, bridge-tied load (BTL) switching audio power amplifier with an integrated  $\Sigma$ - $\Delta$  modulator.

The modulator accepts an analog input signal and generates a switching output to drive speakers directly. A digital, microcontroller-compatible interface provides control of reset, mute and PGA gain as well as output signals for thermal and overcurrent error conditions. The output stage can operate from supply voltages ranging from 9 V to 15 V. The analog modulator and digital logic operate from a 3.3 V supply.

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                     | Slicer                              | 1  |

|----------------------------------------------|-------------------------------------|----|

| Applications1                                | Power Stage                         | 10 |

| General Description                          | Gain                                | 10 |

| Functional Block Diagram                     | Protection Circuits                 | 10 |

| Revision History                             | Thermal Protection                  | 10 |

| Specifications                               | Overcurrent Protection              | 10 |

| Audio Performance                            | Undervoltage Protection             | 12 |

| DC Specifications4                           | Clock Loss Detection                | 12 |

| Power Supplies4                              | Automatic Recovery from Protections | 12 |

| Digital I/O 4                                | MUTE and STDN                       | 12 |

| Digital Timing5                              | Power-Up/Power-Down Sequence        | 18 |

| Absolute Maximum Ratings                     | DC Offset and Pop Noise             | 19 |

| Thermal Resistance                           | Selecting Value for CREF and CIN    | 19 |

| ESD Caution6                                 | Mono Mode                           | 19 |

| Pin Configuration and Function Descriptions7 | Power Supply Bypassing              | 19 |

| Typical Performance Characteristics          | Clock                               | 20 |

| Theory of Operation                          | Applications Information            | 2  |

| Overview                                     | Outline Dimensions                  | 2  |

| Modulator                                    | Ordering Guide                      | 2: |

|                                              |                                     |    |

## **REVISION HISTORY**

5/07—Revision 0: Initial Version

## **SPECIFICATIONS**

AVDD = DVDD = 3.3 V, PVDD = 12 V, ambient temperature = 25°C, load impedance = 6  $\Omega$ , clock frequency = 24.576 MHz, measurement bandwidth = 20 Hz to 20 kHz, unless otherwise noted.

### **AUDIO PERFORMANCE**

Table 1

| Parameter                                  | Min | Тур    | Max | Unit      | Test Conditions/Comments                                    |

|--------------------------------------------|-----|--------|-----|-----------|-------------------------------------------------------------|

| OUTPUT POWER <sup>1</sup>                  |     |        |     |           | 1 kHz                                                       |

|                                            |     | 7      |     | W         | 1% THD + N, 8 Ω                                             |

|                                            |     | 9      |     | W         | 10% THD + N , 8 Ω                                           |

|                                            |     | 9      |     | W         | 1% THD + N, 6 Ω                                             |

|                                            |     | 11.5   |     | W         | 10% THD + N, 6 Ω                                            |

|                                            |     | 12.5   |     | W         | 1% THD + N , 4 Ω                                            |

|                                            |     | 15.5   |     | W         | 10% THD + N , 4 Ω                                           |

| EFFICIENCY                                 |     | 87     |     | %         | @ 12 W, 6 Ω                                                 |

| R <sub>DS-ON</sub>                         |     |        |     |           | @ T <sub>CASE</sub> = 25°C                                  |

| Per High-Side Transistor                   |     | 0.28   |     | Ω         | @ 100 mA                                                    |

| Per Low-Side Transistor                    |     | 0.25   |     | Ω         | @ 100 mA                                                    |

| THERMAL CHARACTERISTICS                    |     |        |     |           |                                                             |

| Thermal Warning Active <sup>2</sup>        |     | 135    |     | °C        | Die temperature                                             |

| Thermal Shutdown Active                    |     | 150    |     | °C        | Die temperature                                             |

| OVERCURRENT SHUTDOWN ACTIVE                | 5   | 6      |     | Α         | Peak current                                                |

| PVDD UNDERVOLTAGE SHUTDOWN                 |     | 5.1    |     | V         |                                                             |

| INPUT LEVEL FOR FULL-SCALE OUTPUT          |     |        |     |           | Full-scale output @ 1% THD + N                              |

|                                            |     | 1.0    |     | $V_{RMS}$ | PGA gain = 0 dB                                             |

|                                            |     | _0.5 _ |     | $V_{RMS}$ | PGA gain = 6 dB                                             |

|                                            |     | 0.25   |     | $V_{RMS}$ | PGA gain = 12 dB                                            |

|                                            |     | 0.125  |     | $V_{RMS}$ | PGA gain = 18 dB                                            |

| TOTAL HARMONIC DISTORTION + NOISE (THD+N)  |     | 0.005  |     | %         | 1 kHz, Pout = 1 W, PGA gain = 0 dB                          |

| SIGNAL-TO-NOISE RATIO (SNR)                | 99  | 101    |     | dB        | A-weighted, referred to 1% THD + N output                   |

| DYNAMIC RANGE (DNR)                        | 99  | 101    |     | dB        | A-weighted, measured with -60 dBFS input                    |

| CROSSTALK (LEFT TO RIGHT OR RIGHT TO LEFT) |     | -90    |     | dB        | @ full-scale output voltage, 1% THD + N, 1 kHz              |

| AMPLIFIER GAIN                             |     |        |     |           | PVDD = 12 V, 6 Ω                                            |

| PGA = 0 dB                                 |     | 17     |     | dB        |                                                             |

| PGA = 6 dB                                 |     | 23     |     | dB        |                                                             |

| PGA = 12 dB                                |     | 29     |     | dB        |                                                             |

| PGA = 18 dB                                |     | 35     |     | dB        |                                                             |

| OUTPUT NOISE VOLTAGE                       |     |        |     |           | PVDD = 12 V, 6 Ω                                            |

| PGA = 0 dB                                 |     | 65     |     | μV        |                                                             |

| PGA = 6 dB                                 |     | 83     |     | μV        |                                                             |

| PGA = 12 dB                                |     | 130    |     | μV        |                                                             |

| PGA = 18 dB                                |     | 230    |     | μV        |                                                             |

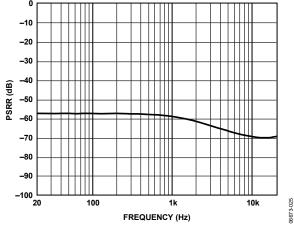

| POWER SUPPLY REJECTION RATIO (PSRR)        |     | 57     |     | dB        | 20 Hz to 20 kHz, 1.2 V p-p ripple, inputs accoupled to AGND |

$<sup>^1</sup>$  Output powers above 12 W at 4  $\Omega$  and above 18 W at 6  $\Omega$  are not continuous and are thermally limited by the package dissipation.  $^2$  Thermal warning flag is for indication of device T<sub>J</sub> reaching close to shutdown temperature.

## **DC SPECIFICATIONS**

### Table 2.

| Parameter                | Min Typ Max |    | Unit | Test Conditions/Comments |           |

|--------------------------|-------------|----|------|--------------------------|-----------|

| INPUT IMPEDANCE          |             | 20 |      | kΩ                       | AINL/AINR |

| OUTPUT DC OFFSET VOLTAGE |             | ±3 |      | mV                       |           |

## **POWER SUPPLIES**

### Table 3.

| Parameter                              | Min | Тур  | Max  | Unit | Test Conditions/Comments          |

|----------------------------------------|-----|------|------|------|-----------------------------------|

| ANALOG SUPPLY VOLTAGE (AVDD)           | 3.0 | 3.3  | 3.6  | V    |                                   |

| DIGITAL SUPPLY VOLTAGE (DVDD)          | 3.0 | 3.3  | 3.6  | V    |                                   |

| POWER TRANSISTOR SUPPLY VOLTAGE (PVDD) | 9   | 12   | 15   | V    |                                   |

| POWER-DOWN CURRENT                     |     |      |      |      | STDN held low                     |

| AVDD                                   |     | 6    | 60   | μΑ   |                                   |

| DVDD                                   |     | 0.14 | 0.24 | mA   |                                   |

| PVDD                                   |     | 0.06 | 0.25 | mA   |                                   |

| MUTE CURRENT                           |     |      |      |      | MUTE held low                     |

| AVDD                                   |     | 13   | 20   | mA   |                                   |

| DVDD                                   |     | 1.8  | 3.2  | mA   |                                   |

| PVDD                                   |     | 4.5  | 8    | mA   |                                   |

| OPERATING CURRENT                      |     |      |      |      | STDN and MUTE held high, no input |

| AVDD                                   |     | 13   | 30   | mA   |                                   |

| DVDD                                   |     | 2.7  | 4    | mA   |                                   |

| PVDD                                   |     | 34   | 65   | mA   |                                   |

## **DIGITAL I/O**

### Table 4.

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments |

|-----------------------------------|-----|-----|-----|------|--------------------------|

| INPUT VOLTAGE                     |     |     |     |      |                          |

| Input Voltage High                | 2   |     |     | V    |                          |

| Input Voltage Low                 |     |     | 0.8 | V    |                          |

| OUTPUT VOLTAGE                    |     |     |     |      |                          |

| Output Voltage High               | 2   |     |     | V    | @ 2 mA                   |

| Output Voltage Low                |     |     | 0.4 | V    | @ 2 mA                   |

| LEAKAGE CURRENT ON DIGITAL INPUTS |     |     | 10  | μΑ   |                          |

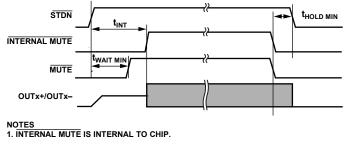

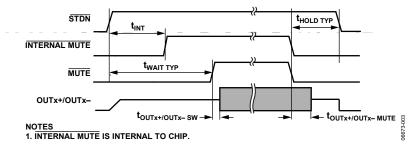

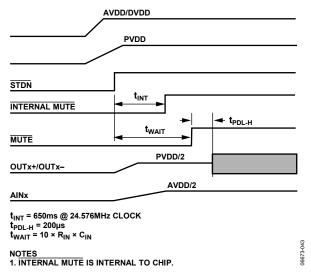

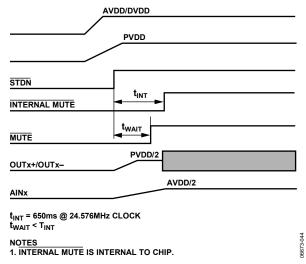

## **DIGITAL TIMING**

Table 5.

| Parameter                           | Min               | Тур              | Unit | Test Conditions/Comments                                      |

|-------------------------------------|-------------------|------------------|------|---------------------------------------------------------------|

| twait                               | 0.01 <sup>1</sup> | 1000²            | ms   | Wait time for unmute                                          |

| t <sub>INT</sub>                    |                   | 650              | ms   | Internal mute time                                            |

| t <sub>HOLD</sub>                   | 10 <sup>1</sup>   | 250 <sup>3</sup> | μs   | Wait time for shutdown                                        |

| $t_{\text{OUTx+/OUTx-}\text{SW}}$   |                   | 200              | μs   | Time delay after MUTE held high until output starts switching |

| $t_{\text{OUTx+/OUTx-}\text{MUTE}}$ |                   | 200              | μs   | Time delay after MUTE held low until output stops switching   |

<sup>&</sup>lt;sup>1</sup> twart min and thold min are the minimum times for fast turn-on and do not guarantee pop-and-click suppression.

<sup>&</sup>lt;sup>3</sup> t<sub>HOLD TYP</sub> is the recommended value for minimum pop and click during the mute of the amplifier.

Figure 2.Timing Diagram (Minimum)

Figure 3. Timing Diagram (Typical)

<sup>&</sup>lt;sup>2</sup> t<sub>WAIT TYP</sub> is the recommended value for minimum pop and click during the unmute of the amplifier. The recommended value is 1 sec. It is calculated using the input coupling capacitor value and the input resistance of the device. See the Power-Up/Power-Down Sequence section.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                   | Rating                       |

|-----------------------------|------------------------------|

| DVDD to DGND                | -0.3 V to +3.6 V             |

| AVDD to AGND                | −0.3 V to +3.6 V             |

| PVDD to PGND <sup>1</sup>   | −0.3 V to +20.0 V            |

| MUTE/STDN Inputs            | DGND - 0.3 V to DVDD + 0.3 V |

| Operating Temperature Range | –40°C to +85°C               |

| Storage Temperature Range   | −65°C to +150°C              |

| Maximum Junction            | 150°C                        |

| Temperature                 |                              |

| Lead Temperature            |                              |

| Soldering (10 sec)          | 260°C                        |

| Vapor Phase (60 sec)        | 215°C                        |

| Infrared (15 sec)           | 220°C                        |

<sup>&</sup>lt;sup>1</sup> Includes any induced voltage due to inductive load.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 7. Thermal Resistance

| Package Type | $\theta_{JA}^1$ | <b>θ</b> <sub>JC</sub> <sup>1, 2</sup> | Ψјβ  | Ψл   | Unit |

|--------------|-----------------|----------------------------------------|------|------|------|

| LFCSP-48     | 24.6            | 2.0                                    | 8.05 | 0.18 | °C/W |

| TQFP-48      | 24.7            | 1.63                                   | 11   | 0.8  | °C/W |

<sup>&</sup>lt;sup>1</sup> With exposed pad (ePAD) soldered to 4-layer JEDEC standard PCB.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Through the bottom (ePAD) surface.

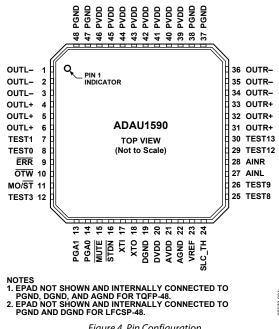

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin. Number | Mnemonic | Type <sup>1</sup> | Description                                                                                |

|-------------|----------|-------------------|--------------------------------------------------------------------------------------------|

| 1, 2, 3     | OUTL-    | . 0               | Output of High Power Transistors, Left Channel Negative Polarity.                          |

| 4, 5, 6     | OUTL+    | 0                 | Output of High Power Transistors, Left Channel Positive Polarity.                          |

| 7           | TEST1    | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 8           | TEST0    | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 9           | ERR      | 0                 | Error Indicator (Active Low, Open-Drain Output).                                           |

| 10          | OTW      | 0                 | Overtemperature Warning Indicator (Active Low Open-Drain Output).                          |

| 11          | MO/ST    | 1                 | Mono/Stereo Mode Setting Pin for Stereo. Connect to DGND (for mono mode, connect to DVDD). |

| 12          | TEST3    | 1                 | Reserved for Internal Use. Connect to DVDD.                                                |

| 13          | PGA1     | 1                 | Programmable Gain Amplifier Select, MSB.                                                   |

| 14          | PGA0     | 1                 | Programmable Gain Amplifier Select, LSB.                                                   |

| 15          | MUTE     | 1                 | Mute (Active Low Input).                                                                   |

| 16          | STDN     | 1                 | Shutdown/Reset Input (Active Low Input).                                                   |

| 17          | XTI      | 1                 | Quartz Crystal Connection/External Clock Input.                                            |

| 18          | XTO      | 0                 | Quartz Crystal Connection/Clock Output.                                                    |

| 19          | DGND     | Р                 | Digital Ground for Digital Circuitry. Internally connected to exposed pad (ePAD).          |

| 20          | DVDD     | Р                 | Positive Supply for Digital Circuitry.                                                     |

| 21          | AVDD     | Р                 | Positive Supply for Analog Circuitry. (Can be tied to DVDD.)                               |

| 22          | AGND     | Р                 | Analog Ground for Analog Circuitry. (See the notes in Figure 4 for connection to ePAD.)    |

| 23          | VREF     | 1                 | AVDD/2 Voltage Reference Connection for External Filter.                                   |

| 24          | SLC_TH   | 1                 | Slicer Threshold Adjust. (Connect to AGND via a resistor for slicer operation.)            |

| 25          | TEST8    | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 26          | TEST9    | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 27          | AINL     | 1                 | Analog Input Left Channel.                                                                 |

| 28          | AINR     | 1                 | Analog Input Right Channel.                                                                |

| 29          | TEST12   | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 30          | TEST13   | 1                 | Reserved for Internal Use. Connect to DGND.                                                |

| 31, 32, 33  | OUTR+    | 0                 | Output of High Power Transistors, Right Channel Positive Polarity.                         |

| Pin. Number     | Mnemonic | Type <sup>1</sup> | Description                                                            |

|-----------------|----------|-------------------|------------------------------------------------------------------------|

| 34, 35, 36      | OUTR-    | 0                 | Output of High Power Transistors, Right Channel Negative Polarity.     |

| 37, 38, 47, 48  | PGND     | Р                 | Power Ground for High Power Transistors. Internally connected to EPAD. |

| 39, 40, 41, 42, | PVDD     | Р                 | Positive Power Supply for High Power Transistors.                      |

| 43, 44, 45, 46  |          |                   |                                                                        |

$<sup>^{1}</sup>$  I = input, O = output, P = power.

## TYPICAL PERFORMANCE CHARACTERISTICS

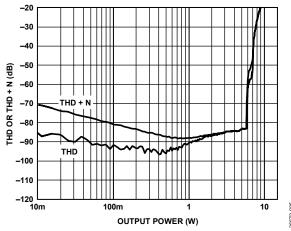

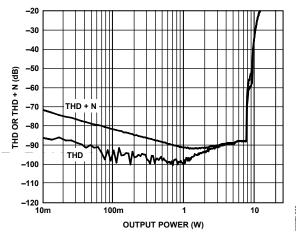

Figure 5. THD or THD + N vs. Output Power,  $4\Omega$ , PVDD = 9V

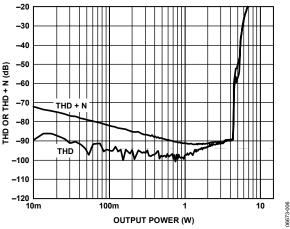

Figure 6. THD or THD + N vs. Output Power,  $6 \Omega$ , PVDD = 9 V

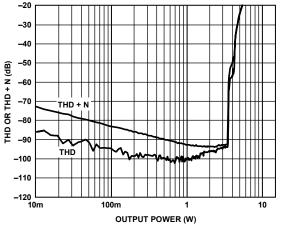

Figure 7. THD or THD + N vs. Output Power,  $8 \Omega$ , PVDD = 9 V

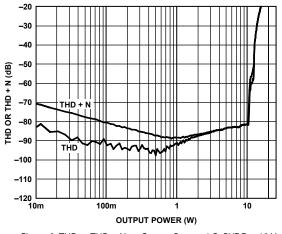

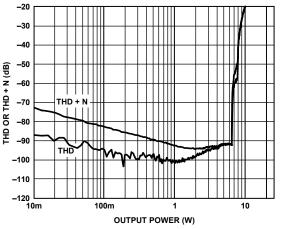

Figure 8. THD or THD + N vs. Output Power, 4  $\Omega$ , PVDD = 12 V

Figure 9. THD or THD + N vs. Output Power, 6  $\Omega$ , PVDD = 12 V

Figure 10. THD or THD + N vs. Output Power, 8  $\Omega$ , PVDD = 12 V

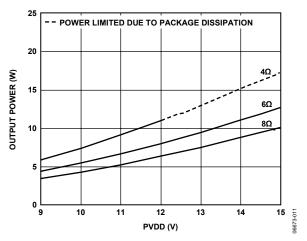

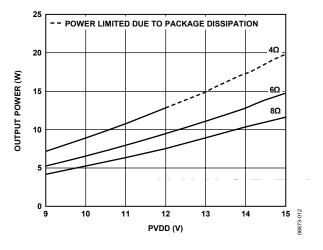

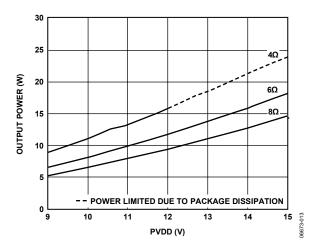

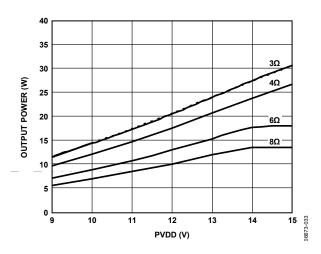

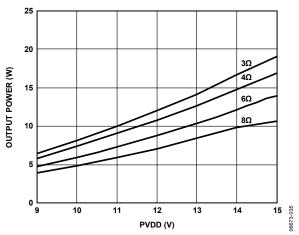

Figure 11. Output Power vs. PVDD @ 0.1% THD + N

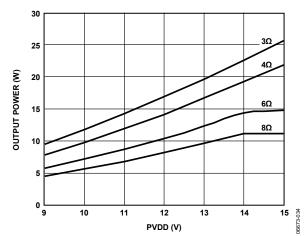

Figure 12. Output Power vs. PVDD @ 1% THD + N

Figure 13. Output Power vs. PVDD @ 10% THD + N

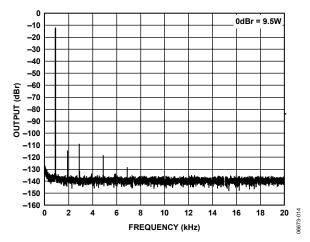

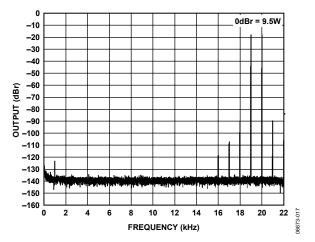

Figure 14. FFT @ 1W, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB, 1 kHz Sine

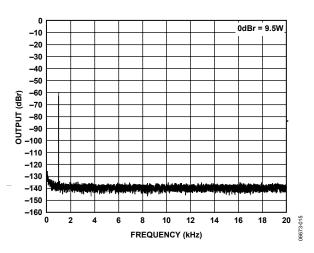

Figure 15. FFT @ -60 dBFS,  $6\Omega$ , PVDD = 12 V, PGA = 0 dB, 1 kHz Sine

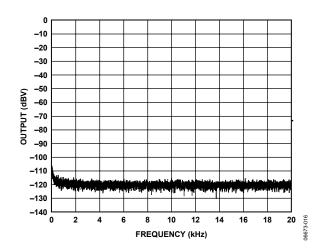

Figure 16. FFT No Input, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB

Figure 17. FFT @ 1 W, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB, 19 kHz and 20 kHz Sine

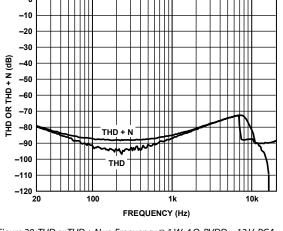

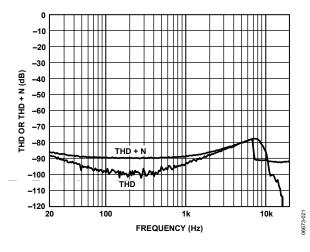

Figure 20. THD or THD + N vs. Frequency @ 1 W, 4  $\Omega$ , PVDD = 12 V, PGA = 0 dB

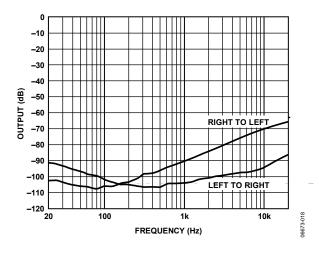

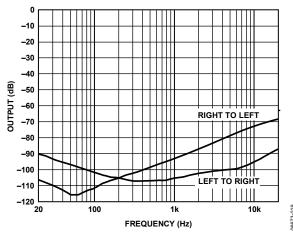

Figure 18. Crosstalk @ 1 W, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB

Figure 21. THD or THD + N vs. Frequency @ 1 W, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB

Figure 19. Crosstalk @ Full Scale, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB

Figure 22. THD or THD + N vs. Frequency @ 1 W, 8  $\Omega$ , PVDD = 12 V, PGA = 0 dB

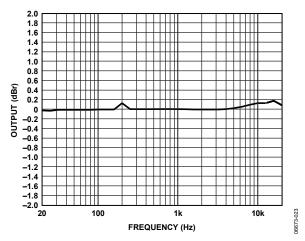

Figure 23. Frequency Response @ 1 W, 6  $\Omega$ , PVDD = 12 V, PGA = 0 dB

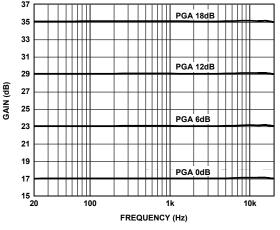

Figure 24. Gain vs. Frequency @ 1 W, 6  $\Omega$ , PVDD = 12 V, 6  $\Omega$

Figure 25. PSRR vs. Frequency, No Input Signal Ripple = 1.2 V p-p, PVDD = 12 V, 6  $\Omega$

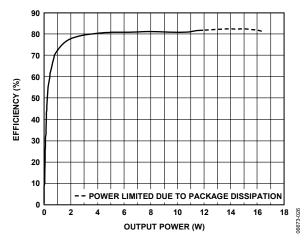

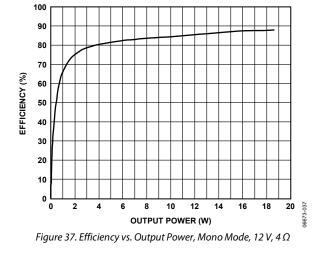

Figure 26. Efficiency vs. Output Power, 12 V,  $4\Omega$

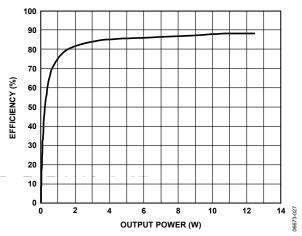

Figure 27. Efficiency vs. Output Power, 12 V,  $6\Omega$

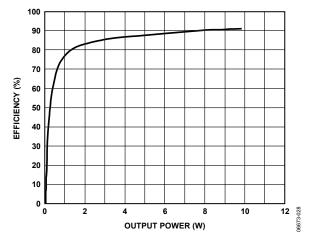

Figure 28. Efficiency vs. Output Power, 12 V, 8  $\Omega$

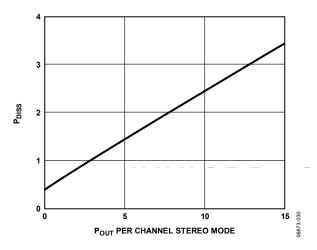

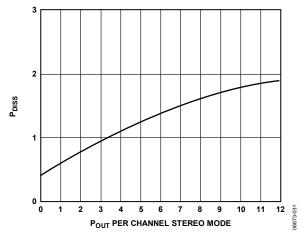

Figure 29. Power Dissipation vs. Output Power, 12 V, 4  $\Omega$ , Stereo Mode, Both Channels Driven

Figure 30. Power Dissipation vs. Output Power, 12 V, 6  $\Omega$ , Stereo Mode, Both Channels Driven

Figure 31. Power Dissipation vs. Output Power, 12 V, 8 Ω, Stereo Mode, Both Channels Driven

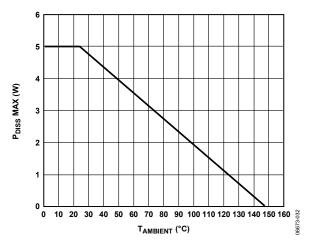

Figure 32. Power Dissipation Derating vs. Ambient Temperature

Figure 33. Output Power vs. PVDD, Mono Mode, THD + N, 20 dB

Figure 34. Output Power vs. PVDD, Mono Mode, THD + N, 40 dB

Figure 35. Output Power vs. PVDD, Mono Mode, THD + N, 60 dB

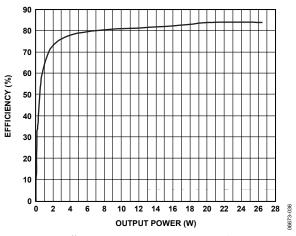

Figure 36. Efficiency vs. Output Power, Mono Mode, 12 V, 3  $\Omega$

## THEORY OF OPERATION

#### **OVERVIEW**

The ADAU1590 is a 2-channel high performance switching audio power amplifier. Each of the two  $\Sigma$ - $\Delta$  modulators converts a single-ended analog input into a 2-level PDM output. This PDM pulse stream is output from the internal full differential power stage. The ADAU1590 has built-in circuits to suppress the turn-on and turn off pop and click. The ADAU1590 also offers extensive thermal and overcurrent protection circuits.

#### **MODULATOR**

The modulator is a 5<sup>th</sup>-order  $\Sigma$ - $\Delta$  with feedback from the power stage connected internally. This helps reduce the external connections. The 5<sup>th</sup>-order modulator switches to a lower order near full-scale inputs. The modulator gain is optimized at 19 dB for 15 V operation. The  $\Sigma$ - $\Delta$  modulator outputs a pulse density modulation (PDM) 1-bit stream, which does not produce distinct sharp peaks and harmonics in the AM band like conventional fixed-frequency PWM.

The  $\Sigma\text{-}\Delta$  modulators require feedback to generate PDM stream with respect to the input. The feedback for the modulators comes from the power stage. This helps reduce the nonlinearity in the power stages and achieve excellent THD + N performance. The feedback also helps in achieving good PSRR. In the ADAU1590, the feedback from the power stage is internally connected. This helps reduce the external connections for ease in PCB layout.

The  $\Sigma$ - $\Delta$  modulators operate in a discrete time domain and Nyquist frequency limit, which is half the sampling frequency. The modulator uses the master clock of 12.288 MHz. This is generated by dividing the external clock input by 2. This sets the f<sub>S</sub>/2 around 6.144 MHz. This is sufficient for the audio bandwidth of 22 kHz. The modulator shapes the quantization noise and transfers it outside the audio band. The noise floor rises sharply above 20 kHz. This ensures very good signal-tonoise ratio (SNR) in the audio band of 20 kHz. The 6.144 MHz bandwidth allows the modulator order to be set around the 5th order. The modulator uses proprietary dynamic hysteresis to reduce the switching rate or frequency to around 700 kHz. This reduces the switching losses and achieves good efficiency. The dynamic hysteresis helps the modulator to continuously track the change in PVDD and the input level to keep the modulator stable.

#### **SLICER**

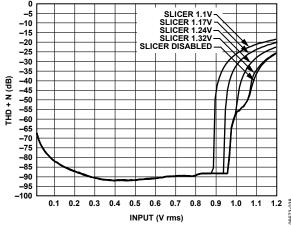

The ADAU1590 has a built-in slicer block following the PGA and before the modulator. The slicer block is essentially a hard limiter included for limiting the input signal to the modulator. This, in turn, limits the output power at a given supply voltage. The slicer in the ADAU1590 is normally inactive at lower input levels but is activated as soon as the peak input voltage exceeds the set threshold. The threshold can be set externally by connecting a resistor from SLC\_TH (Pin 24) to ground. This

feature allows the user to adjust the slicer to the desired value and to limit the output power. For input signals higher than the set threshold, the slicer clips the input signal to the modulator. This adds distortion due to clipping of the signal input to the modulator. This is especially helpful in applications where the output power available needs to be reduced instead of reducing the supply voltage.

Figure 38 is a plot showing THD + N vs. the input level at 0 dB PGA, 12 V, and 6  $\Omega$ , and demonstrates the difference between a device with and without the slicer.

Figure 38. THD + N vs. Input Level @ PGA = 0 dB, 12 V

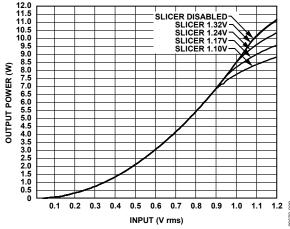

Figure 39 depicts the typical output power vs. input at different slicer settings.

Figure 39. Typical Output Power vs. Input, at Different Slicer Settings

From Figure 39, it can be seen that the slicer effectively reduces the output power depending on its setting.

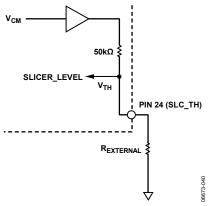

Internally, the slicer block receives the input from the PGA. Figure 40 shows the block for slicer threshold adjust, SLC\_TH (Pin 24).

Figure 40. Block for Slicer Threshold Adjust, SLC\_TH

The slicer threshold can be set externally using a resistor as follows:

$$V_{TH} = (AVDD/2) \times (50 \text{ k}\Omega/50 \text{ k}\Omega + R_{EXTERNAL})$$

where:

AVDD = 3.3 V typical.

$V_{TH}$  is the voltage threshold at which the slicer is activated.

The following equation can be used to calculate the input signal at which the slicer becomes active:

$$V_{\mathit{IN\,RMS}} = \frac{V_{\mathit{TH}}}{1.414 \times 0.9}$$

Therefore, for AVDD = 3.3 V typical and  $V_{TH} = 1.1 \text{ V}$ ,

$$R_{EXTERNAL} = 24.9 \text{ k}\Omega$$

$V_{INRMS} = 0.864 \text{ V}$

Thus, the slicer is activated at and above  $0.864 \ V_{IN RMS}$ .

This feature allows the user to set the slicer and, in turn, reduces the output power at a given supply voltage. To disable the slicer, SLC\_TH should be connected to AGND. Table 9 shows the typical values for  $R_{\rm EXTERNAL}$ .

Table 9. Typical Rexternal Values

| V <sub>TH</sub> (V) | R <sub>EXTERNAL</sub> (kΩ) | V <sub>IN RMS</sub> (V) |

|---------------------|----------------------------|-------------------------|

| 1.1                 | 24.9                       | 0.864                   |

| 1.17                | 20.5                       | 0.919                   |

| 1.24                | 16.5                       | 0.974                   |

| 1.32                | 12.4                       | 1.037                   |

#### **POWER STAGE**

The ADAU1590 power stage comprises a high-side PMOS and a low-side NMOS. The typical  $R_{DS-ON}$  is ~300 m $\Omega$ . The PMOS-NMOS stage does not need an external bootstrap capacitor and simplifies the high-side driver design. The power stage also has comprehensive protection circuits to detect the faults in typical applications. See the Protection Circuits section for further details.

#### **GAIN**

The gain of the amplifier is set internally using feedback resistors optimized for 12 V nominal operation. The typical gain values are tabulated in Table 1. The typical gain is 17 dB with PGA set to 0 dB. PGA0 (Pin 14) and PGA1 (Pin 13) are used for setting the desired gain.

The gain can be set according to Table 10. Note that the amplifier full-scale input level changes as per the PGA gain setting.

**Table 10. Gain Settings**

| PGA1<br>(Pin 13) | PGA0<br>(Pin14) | PGA<br>Gain (dB) | Amplifier<br>Gain (dB) | Full-Scale<br>Input Level<br>(V <sub>RMS</sub> ) |

|------------------|-----------------|------------------|------------------------|--------------------------------------------------|

| 0                | 0               | 0                | 17                     | 1                                                |

| 0                | 1               | 6                | 23                     | 0.5                                              |

| 1                | 0               | 12               | 29                     | 0.25                                             |

| 1                | 1               | 18               | 35                     | 0.125                                            |

#### **PROTECTION CIRCUITS**

The ADAU1590 includes comprehensive protection circuits. It includes thermal warning, thermal overheat, and overcurrent or short-circuit protection on the outputs. The ERR and OTW outputs are open drain and require external pull-up resistors. The outputs are capable of sinking 10 mA. The open-drain outputs are useful in multichannel applications where more than one ADAU1590 is used. The error outputs of multiple ADAU1590s can be OR'ed to simplify the system design. The logic outputs of the error flags ease the system design of using a microcontroller.

#### THERMAL PROTECTION

Thermal protection in the ADAU1590 is categorized into two error flags: one as thermal warning and the other as thermal shutdown. When the device junction temperature reaches near 135°C ( $\pm$ 5°C), the ADAU1590 outputs a thermal warning error flag by pulling  $\overline{OTW}$  (Pin 10) low. This flag can be used by the microcontroller in the system for indication to the user or can be used to lower the input level to the amplifier to prevent thermal shutdown. The device continues operation until shutdown temperature is reached.

When the device junction temperature exceeds 150°C, the device outputs an error flag by pulling  $\overline{ERR}$  (Pin 9) low. This error flag is latched. To restore the operation,  $\overline{MUTE}$  (Pin 15) needs to be toggled to low and then to high again.

#### **OVERCURRENT PROTECTION**

The overcurrent protection in the ADAU1590 is set internally at a 5 A peak output current. The device protects the output devices against excessive output current by pulling  $\overline{\text{ERR}}$  (Pin 9) low. This error flag is latched. To restore the normal operation,  $\overline{\text{MUTE}}$  (Pin 15) needs to be toggled to low and then to high again. The error flag is useful for the microcontroller in the system to indicate abnormal operation and to initiate the audio  $\overline{\text{MUTE}}$  sequence. The device senses the short-circuit condition

on the outputs after the LC filter. Typical short-circuit conditions include shorting of the output load, and shorting to either PVDD or PGND.

#### UNDERVOLTAGE PROTECTION

The ADAU1590 is also comprised of an undervoltage protection circuit, which senses the undervoltage on PVDD. When the PVDD supply goes below the operating threshold, the output FETs are turned to a high-Z condition. In addition, the device issues an error flag by pulling  $\overline{ERR}$  low. This condition is latched. To restore the operation,  $\overline{MUTE}$  (Pin 15) needs to be toggled to low and then to high again.

#### **CLOCK LOSS DETECTION**

The ADAU1590 includes a clock loss detection circuit. In case the master clock to the part is lost, the  $\overline{ERR}$  flag is set. This condition is latched. To restore operation,  $\overline{MUTE}$  needs to be toggled low and high again.

#### **AUTOMATIC RECOVERY FROM PROTECTIONS**

In certain applications, it is desired for the amplifier to recover itself from thermal protection without the need for system microcontroller intervention.

The ADAU1590 thermal protection circuit issues two error signals for this purpose: one a thermal warning  $(\overline{OTW})$  and the other a thermal shutdown  $(\overline{ERR})$ .

With the two error signals, there are two options available for using the protections:

- Option 1: Using OTW

- Option 2: Using ERR

The following sections provide further details of these two options.

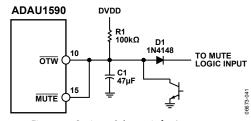

#### Option 1: Using OTW

The  $\overline{\text{OTW}}$  pin is pulled low when the die temperature reaches 130°C to 135°C. This pin can be wired to  $\overline{\text{MUTE}}$  as shown in Figure 41, using an RC circuit.

Figure 41. Option 1 Schematic for Autorecovery

The low logic level on  $\overline{OTW}$  also pulls down the  $\overline{MUTE}$  pin. The bridge is shut down and starts cooling or the die temperature starts reducing. When it reaches around 120°C, the  $\overline{OTW}$  signal starts going high. While this pin is tied to a capacitor with a resistor pulled to DVDD, the voltage on this pin starts rising slowly towards DVDD. When it reaches the CMOS threshold,  $\overline{MUTE}$  is deasserted and the amplifier starts functioning again. This cycle repeats itself depending on the input signal conditions and the temperature of the die. This option allows

device operation that is safely below the shutdown temperature of 150°C and allows the amplifier to recover itself without the need for microcontroller intervention.

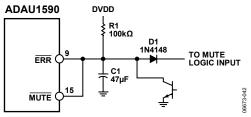

### Option 2: Using ERR

Option 2 is similar to Option 1 except the  $\overline{ERR}$  pin is tied to  $\overline{MUTE}$  instead of  $\overline{OTW}$ . See the circuit in Figure 42.

Figure 42. Option 2 Schematic for Autorecovery

In this case, the part goes into shutdown mode due to any of the error generating events like output overcurrent, overtemperature, missing PVDD or DVDD, or clock loss. The part recovers itself based on the same circuit operation in Figure 41.

However, if the part goes into error mode due to overtemperature, then the device would have reached its maximum limit of 150°C (15°C to 20°C higher than Option 1). If it goes into error mode due to an overcurrent from a short circuit on the speaker outputs, then the part keeps itself recycling on and off until the short circuit is removed.

It is possible that, with this operation, the part is subjected to a much higher temperature and current stress continuously. This, in turn, reduces the part's reliability in the long term. Therefore, using Option 1 for autorecovery from thermal protection and using the system microcontroller to indicate to the user of an error condition is recommended.

#### MUTE AND STDN

The MUTE and STDN pins are 3.3 V logic-compatible inputs used to control the turn-on/turn-off for ADAU1590.

The STDN input is active low when the STDN pin is pulled low and the device is in its energy saving mode. The modulator is inactive and the power stage is in high-Z state. The high logic level input on the STDN pin wakes up the device. The modulator is running internally but the power stage is still in high-Z state.

When the  $\overline{\text{MUTE}}$  pin is pulled high, the power stage becomes active with a soft turn-on to avoid the pop and clicks. The low level on the  $\overline{\text{MUTE}}$  pin disables the power stage and is recommended to be used to mute the audio output. See the Power-Up/Power-Down Sequence section for more details.

#### POWER-UP/POWER-DOWN SEQUENCE

Figure 43 shows the recommended power-up sequence for the ADAU1590.

Figure 43. Recommended Power-Up Sequence

The ADAU1590 has a special turn-on sequence that consists of a fixed internal mute time during which the power stage does not start switching. This internal mute time depends on the master clock frequency and is 650 ms for a 24.576 MHz clock. Also, the internal mute overrides the external MUTE and ensures that the power stage does not switch on immediately even if the external MUTE signal is pulled high in less than 650 ms after STDN. The power stage starts switching only after 650 ms plus a small propagation delay of 200  $\mu$ s has elapsed and after MUTE is deasserted. Therefore, it is recommended to ensure that  $t_{\rm WAIT} > t_{\rm INT}$  to prevent the pop and click during power-on.

Ensure that the  $\overline{MUTE}$  signal is delayed by at least  $t_{WAIT}$  seconds after  $\overline{STDN}$ . This time is approximately 10 times the charging time constant of the input coupling capacitor.

For example, if the input coupling capacitor is 4.7  $\mu\text{F},$  the time constant is

$$T = R \times C = 20 \text{ k}\Omega \times 4.7 \text{ }\mu\text{F} = 94 \text{ ms}$$

Therefore,  $t_{WAIT} = 10 \times T = 940 \text{ ms} \sim 1 \text{ sec.}$

$t_{WAIT}$  is needed to ensure that the input capacitors are charged to AVDD/2 before turning on the power stage.

When  $t_{WAIT} < t_{INT}$ , the power stage does not start switching until 650 ms has elapsed after  $\overline{STDN}$  (see Figure 44). However, note that this method does not ensure pop-and-click suppression because of less than recommended or insufficient  $t_{WAIT}$ .

Figure 44. Power-Up Sequence, twait < tint

The ADAU1590 uses three separate supplies: AVDD (3.3 V analog for PGA and modulator), DVDD (3.3 V digital for control logic and clock oscillator), and PVDD (9 V to 18 V power stage and level shifter). Separate pins are provided for the AVDD, DVDD, and PVDD supply connections, as well as AGND, DGND, and PGND.

In addition, the ADAU1590 incorporates a built-in undervoltage lockout logic on DVDD as well as PVDD. This helps detect undervoltage operation and eliminates the need to have an external mechanism to sense the supplies.

The ADAU1590 monitors the DVDD and PVDD supply voltages and prevents the power stage from turning on if either of the supplies are not present or are below the operating threshold. Therefore, if DVDD is missing or below the operating threshold, for example, the power stage does not turn on, even if PVDD is present, or vice versa.

Because this protection is only present on DVDD and PVDD and not on AVDD, shorting both AVDD and DVDD externally or generating AVDD and DVDD from one power source is recommended. This ensures that both AVDD and DVDD supplies are tracking each other and avoids the need to monitor the sequence with respect to PVDD. This also ensures minimal pop and click during power-up.

When using separate AVDD and DVDD supplies, ensure that both supplies are stable before unmuting or turning on the power stage.

Similarly, during shutdown, pulling  $\overline{\text{MUTE}}$  to logic low before pulling  $\overline{\text{STDN}}$  down is recommended. However, where a fault event occurs, the power stage shuts down to protect the part. In this case, depending on the signal level, there is some pop at the speaker.

To shut down the power supplies, it is highly recommended to mute the amplifier before shutting down any of the supplies. After  $\overline{\text{MUTE}}$  is shut down, shut down the supplies in the following order: PVDD, DVDD, then AVDD. Where AVDD and DVDD are generated from a single source, turn PVDD off before DVDD and AVDD, and after issuing  $\overline{\text{MUTE}}$ .

#### DC OFFSET AND POP NOISE

This section describes the cause of dc offset and pop noise during turn-on/turn-off. The turn-on/turn-off pop in amplifiers depend mainly on the dc offset, therefore, care must be taken to reduce the dc offset at the output.

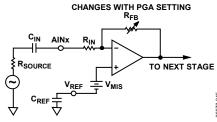

The first stage of ADAU1590 has an inverting PGA amplifier, as shown in Figure 45.

Figure 45. Input Equivalent Circuit

where:

$R_{IN} = 20 \text{ k}\Omega$ , fixed internally.

R<sub>FB</sub> is the gain feedback resistor (value depends on the PGA setting).

R<sub>SOURCE</sub> is the source resistance.

$C_{IN}$  is the input coupling capacitor (2.2  $\mu$ F typical).

$C_{REF}$  is the filter capacitor for  $V_{REF}$ .

V<sub>REF</sub> is the analog reference voltage (AVDD/2 typical).

$V_{\text{MIS}}$  is the dc offset due to mismatch in the op amp.

As shown in Figure 45, the dc offset at the output can be due to  $V_{\text{MIS}}$  (the dc offset from mismatch in the op amp) and due to leakage current of the  $C_{\text{IN}}$  capacitor.

Normally, the offset due to leakage current in the  $C_{\rm IN}$  is less and can be ignored compared to  $V_{\rm MIS}$ . The  $V_{\rm MIS}$  is mainly responsible for the dc offset at the output. The ADAU1590 uses special self-calibration or a dc offset trim circuit, which controls the dc offset (due to  $V_{\rm MIS}$ ) to within  $\pm 3$  mV. The  $V_{\rm MIS}$  can vary for each part as well as for voltage and temperature. The trim circuit ensures that the offset is limited within specified limits and provides virtually pop-free operation every time the part is turned on. However, care must be taken while unmuting or during the power-up sequence.

During the initial power-up,  $C_{\rm IN}$  and  $C_{\rm REF}$  are charging to AVDD/2 and, during this time, there can be dc offset at the output (see Figure 45). This depends on the PGA gain setting. The dc offset is multiplied by the PGA gain setting. If the amplifier is kept in mute during this charging and self-trimming event for the recommended  $t_{\rm WAIT}$  time, the dc offset at the output remains within  $\pm 3$  mV. For more details on  $t_{\rm WAIT}$ , refer to the Power-Up/Power-Down Sequence section.

The amount of pop at the turn-on depends on  $t_{WAIT}$ , which in turn depends on the values of  $C_{REF}$  and  $C_{IN}$ . The following section describes how to select the value for the  $C_{REF}$  and  $C_{IN}$ .

### SELECTING VALUE FOR CREE AND CIN

The  $C_{REF}$  is the capacitor used for filtering the noise from AVDD on  $V_{REF}$ .  $V_{REF}$  is used for the biasing of the internal analog amplifier as well as the modulator. Therefore, care must be taken to ensure that the recommended minimum value is used. The minimum recommended value for  $C_{REF}$  is 4.7 µF.

$C_{\rm IN}$  is the input coupling capacitor and is used to decouple the inputs from the external dc. The  $C_{\rm IN}$  value determines the low corner frequency of the amplifier. It can be determined from the following equation:

$$f_{LOW} = \frac{1}{2 \times \pi \times R_{IN} \times C_{IN}}$$

where:

$f_{LOW}$  is the low corner frequency (-3 dB).

$R_{IN}$  is the input resistance (20 k $\Omega$ ).

$C_{IN}$  is the input coupling capacitor.

Note that  $R_{IN} = 20 \text{ k}\Omega$ , provided that  $R_{SOURCE}$  is <1 k $\Omega$ . If  $R_{SOURCE}$  is sizable with respect to  $R_{IN}$ , it also must be taken into account in calculation.

From the preceding equation,  $f_{LOW}$  can be found for the desired frequency response.

The recommended value for  $C_{IN}$  is 2.2  $\mu$ F, giving  $f_{LOW} = 3.6$  Hz, and should keep 20 Hz roll-off within -0.5 dB.

However, if a higher than recommended  $C_{\rm IN}$  value is used for better low frequency response, care must be taken to ensure that appropriate  $t_{\rm WAIT}$  is used. See the Power-Up/Power-Down Sequence section for more details.

#### **MONO MODE**

The ADAU1590 mono mode can be enabled by pulling MO/ST (Pin 11) to logic high. In this mode, the left channel input and modulator is active and feeds PWM data to both the left and right power stages. However, the respective power FETs need to be connected externally for higher current capability. That is, connect OUTL+ with OUTR+ and OUTL- with OUTR-. The mono mode gives the capability to drive lower impedance loads without invoking current limit. However, the output power is limited by PVDD and temperature limits. See the typical application schematic in Figure 47 for details.

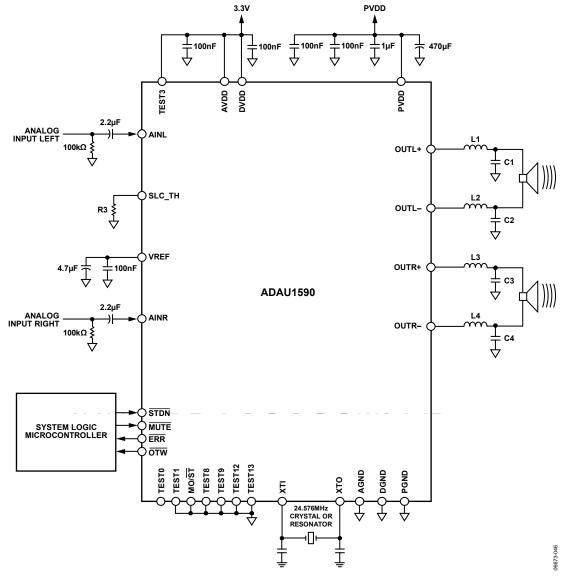

### **POWER SUPPLY BYPASSING**

Because Class-D amplifiers utilize high frequency switching, care must be taken to bypassing the power supply.

For reliable operation, using 100 nF ceramic surface-mount capacitors for the PVDD and PGND pins is recommended. The minimum of two capacitors are needed: one between Pin 45/Pin 46 (PVDD) and Pin 47/Pin 48 (PGND), the other between Pin 39/Pin 40 (PVDD) and Pin 37/Pin 38 (PGND). In addition, these

must be placed very close to the respective pins with direct connection. This is important for reliable and safe operation of the device. One additional 1  $\mu F$  capacitor in parallel to the 100 nF capacitor is also recommended. A bulk bypass capacitor of 470  $\mu F$  is also recommended to remove the low frequency ripple due to load current.

Similarly, one 100 nF capacitor is recommended between each DVDD/DGND and AVDD/AGND. These capacitors also must be placed close to their respective pins with direct connection.

#### **CLOCK**

The ADAU1590 uses 24.576 MHz for the master clock, which is  $512 \times f_s$  ( $f_s = 48$  kHz). There are several options for providing the clock.

#### **Option 1: Using a Quartz Crystal**

A quartz crystal of 24.576 MHz frequency can be connected between the XTI and XTO pins using two load capacitors suitable for the crystal oscillation mode.

#### **Option 2: Using a Ceramic Resonator**

The ADAU1590 can also be used with ceramic resonators similar to crystal by using the XTI and XTO pins.

#### **Option 3: Using an External Clock**

The ADAU1590 can be provided with an external clock of 24.576 MHz at the XTI pin. The logic level for the clock input should be in the range of 3.3 V and 50% typical duty cycle.

For systems using multiple ADAU1590s, it is recommended to use only one clock source if the ADAU1590s share the same power supply to prevent the beat frequencies of asynchronous clocks from appearing in the audio band.

Multiple ADAU1590s can be connected in a daisy chain by providing or generating a master clock from one ADAU1590 and subsequently connecting its XTO output to the XTI input of the next ADAU1590, and so on. However, using a simple logic buffer between the XTO pin of one ADA1590 to the XTI pin of the next ADAU1590 is recommended. Because the clock output is now buffered, it can be connected to the XTI inputs of the remaining ADAU1590s, depending on the fanout capability of the logic buffer used.

# **APPLICATIONS INFORMATION**

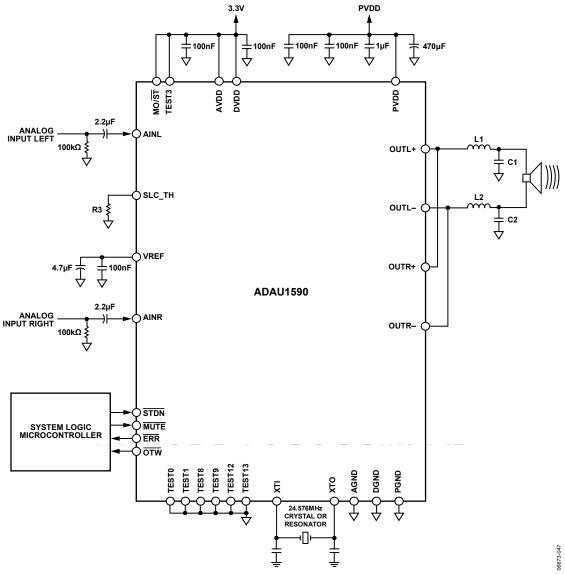

Figure 46. Typical Stereo Application Circuit

Table 11. R3—Slicer Threshold Resistor

| V <sub>TH</sub> (V) | R3 (kΩ) |

|---------------------|---------|

| 1.1                 | 24.9    |

| 1.17                | 20.5    |

| 1.24                | 16.5    |

| 1.32                | 12.4    |

**Table 12. Output Filter Component Values**

| Load Impedance (Ω) | Inductance<br>L1 to L4 (μH) | Capacitance<br>C1 to C4 (μF) |

|--------------------|-----------------------------|------------------------------|

| 4                  | 10                          | 1.5                          |

| 6                  | 15                          | 1                            |

| 8                  | 22                          | 0.68                         |

Figure 47. Typical Mono Application Circuit

For component values, refer to the stereo application circuit in Figure 46.

## **OUTLINE DIMENSIONS**

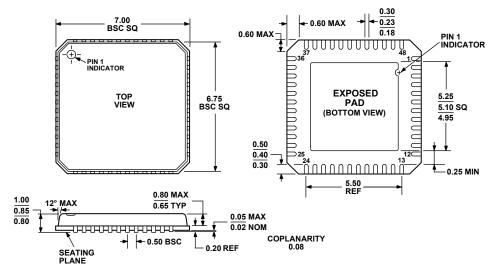

#### COMPLIANT TO JEDEC STANDARDS MO-220-VKKD-2

Figure 48. 48-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 7 mm × 7 mm Body, Very Thin Quad (CP-48-1) Dimensions shown in millimeters

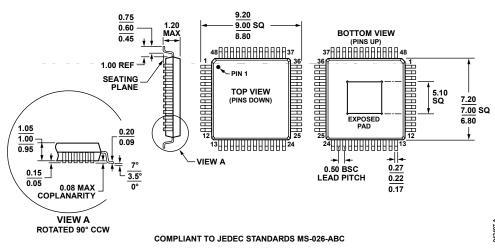

Figure 49. 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP\_EP] (SV-48-5) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                         | Temperature<br>Range | Package Description                                                     | Package<br>Option |

|-------------------------------|----------------------|-------------------------------------------------------------------------|-------------------|

| ADAU1590ACPZ <sup>1</sup>     | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ]                        | CP-48-1           |

| ADAU1590ACPZ-RL1              | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ], 13"Tape and Reel      | CP-48-1           |

| ADAU1590ACPZ-RL7 <sup>1</sup> | -40°C to +85°C       | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ], 7"Tape and Reel       | CP-48-1           |

| ADAU1590ASVZ <sup>1</sup>     | -40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP]                   | SV-48-5           |

| ADAU1590ASVZ-RL1              | −40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP], 13"Tape and Reel | SV-48-5           |

| ADAU1590ASVZRL7 <sup>1</sup>  | −40°C to +85°C       | 48-Lead Thin Quad Flat Package, Exposed Pad [TQFP_EP], 7"Tape and Reel  | SV-48-5           |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

NOTES