# ANALOG 12-Bit CCD Signal Processor with V-Driver and Processor Timing Concretes and *Precision Timing* Generator

AD9920A

### **FEATURES**

Integrated 19-channel V-driver 1.8 V AFETG core 24 programmable vertical clock signals Correlated double sampler (CDS) with -3 dB, 0 dB, +3 dB, and +6 dB gain 12-bit, 40.5 MHz analog-to-digital converter (ADC) Black level clamp with variable level control Complete on-chip timing generator Precision Timing core with ~400 ps resolution On-chip 3 V horizontal and RG drivers General-purpose outputs (GPOs) for shutter and system support On-chip sync generator with external sync input On-chip 1.8 V low dropout (LDO) 105-lead 8 mm × 8 mm CSP\_BGA package

#### **APPLICATIONS**

**Digital still cameras**

## **GENERAL DESCRIPTION**

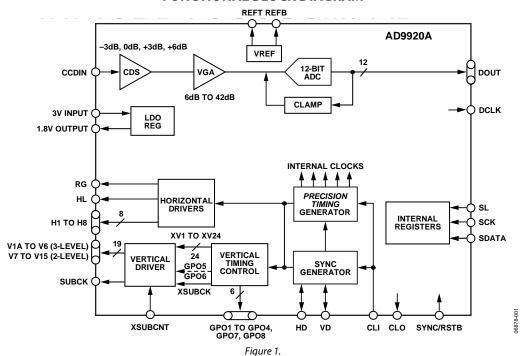

The AD9920A is a highly integrated charge-coupled device (CCD) signal processor for digital still camera applications. It includes a complete analog front end (AFE) with analog-to-digital conversion, combined with a full-function programmable timing generator and 19-channel vertical driver (V-driver). The timing generator is capable of supporting up to 26 vertical clock signals to control advanced CCDs. The on-chip V-driver supports up to 19 channels for use with 6-field CCDs. A Precision Timing™ core allows adjustment of high speed clocks with approximately 400 ps resolution at 40.5 MHz operation. The AD9920A also contains six GPOs that can be used for shutter and system functions.

The analog front end includes black level clamping, variable gain CDS, and a 12-bit ADC. The timing generator provides all the necessary CCD clocks: RG, H-clocks, V-clocks, sensor gate pulses, substrate clock, and substrate bias control.

The AD9920A is specified over an operating temperature range of  $-25^{\circ}$ C to  $+85^{\circ}$ C.

# FUNCTIONAL BLOCK DIAGRAM

For more information about the AD9920A, contact Analog Devices via email at afe.ccd@analog.com.

**NOTES**

----