# High Performance HDMI™/DVI Transmitter

AD9889

#### **FEATURES**

HDMI/DVI transmitter compatible with HDMI 1.1 and HDCP 1.1

Single 1.8 V power supply Video/audio inputs are 3.3 V tolerant

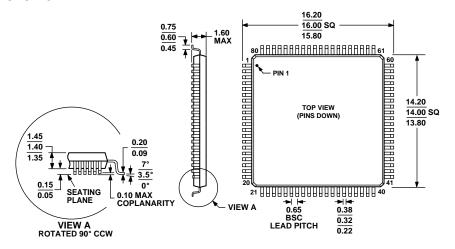

80-lead, Pb-free LQFP Digital video

80 MHz operation supports all video formats from 480i to 1080i and 720p

Programmable 2-way color space converter Supports RGB, YCbCr, DDR, ITU656 formats Auto input video format detection

#### **Digital audio**

Supports standard S/PDIF for stereo or compressed audio up to 192 kHz

8-channel LPCM I2S audio up to 192 kHz

Special features for easy system design

On-chip MPU to perform HDCP operations On-chip I<sup>2</sup>C master to handle EDID reading 5 V tolerant I<sup>2</sup>C and MPD I/Os, no extra device needed

No audio master clock needed for S/PDIF support

#### **APPLICATIONS**

DVD players and recorders

Digital set-top boxes

AV receivers

Digital cameras and camcorders

#### **GENERAL DESCRIPTION**

The AD9889 is an 80 MHz, high-definition multimedia interface (HDMITM 1.1) transmitter. It supports HDTV formats up to 1080i and 720p, and graphic resolutions up to XGA (1024  $\times$  768 @ 75 Hz). With the inclusion of HDCP, the AD9889 allows the secure transmission of protected content as specified by the HDCP 1.1 protocol.

The AD9889 supports both S/PDIF and 8-channel I<sup>2</sup>S audio. Its high fidelity 8-channel I<sup>2</sup>S can transmit either stereo or 7.1 surround audio at 192 kHz. The S/PDIF can carry stereo LPCM (linear pulse code modulation) audio or compressed audio including Dolby\* Digital, DTS\*, and THX\*.

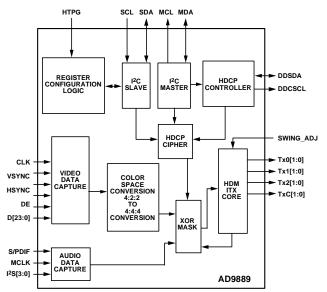

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The AD9889 helps to reduce system design complexity and cost by incorporating such features as HDCP master,  $I^2C$  master for EDID reading, a single 1.8 V power supply, and 5 V tolerance on  $I^2C$  and hot plug detect pins.

Fabricated in an advanced CMOS process, the AD9889 is provided in a space-saving, 80-lead, surface-mount, Pb-free plastic LQFP and is specified over the 0°C to 70°C temperature range.

#### **EVALUATION KITS AND OTHER RESOURCES**

Evaluation kits, reference design schematics, software quick start guide, and codes are available from Analog Devices local sales and marketing personnel.

# **TABLE OF CONTENTS**

| Features                                           | I <sup>2</sup> S Au |

|----------------------------------------------------|---------------------|

| Applications1                                      | S/PDII              |

| Functional Block Diagram 1                         | CTS G               |

| General Description                                | N Para              |

| Evaluation Kits and Other Resources                | CTS P               |

| Revision History                                   | Packet              |

| Electrical Specifications                          | Pixel F             |

| Absolute Maximum Ratings                           | HDCP                |

| Explanation of Test Levels                         | EDID                |

| ESD Caution                                        | Interru             |

| Pin Configuration and Function Descriptions6       | Power               |

| I <sup>2</sup> C Addresses                         | 2-Wire S            |

| List of Reference Documents                        | 2-Wire S            |

| Format Standards                                   | Source              |

| Design Guide9                                      | 2-Wire S            |

| General Description9                               | – Data T            |

| Video Data Capture9                                | Serial 1            |

| Input Formats9                                     | PCB Lay             |

| 4:2:2 to 4:4:4 Data Conversion                     | Power               |

| Horizontal Sync, Vertical Sync, and Degeneration14 | Digital             |

| Degeneration14                                     | Color Sp            |

| HSYNC and VSYNC Generation                         | Outline I           |

| Color Space Conversion Matrix (CSC) 16             | Orderi              |

| Audio Data Capture                                 |                     |

| 1'S Audio                                                    |

|--------------------------------------------------------------|

| S/PDIF Audio12                                               |

| CTS Generation                                               |

| N Parameter                                                  |

| CTS Parameter                                                |

| Packet Configuration                                         |

| Pixel Repetition                                             |

| HDCP Handling                                                |

| EDID Reading                                                 |

| Interrupts                                                   |

| Power Management                                             |

| 2-Wire Serial Register Map                                   |

| 2-Wire Serial Control Register Detail Chip Identification 33 |

| Source Product Description (SPD) Infoframe                   |

| 2-Wire Serial Control Port                                   |

| Data Transfer via Serial Interface                           |

| Serial Interface Read/Write Examples                         |

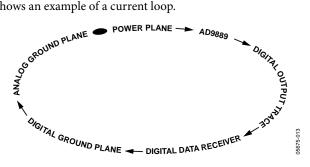

| PCB Layout Recommendations                                   |

| Power Supply Bypassing                                       |

| Digital Inputs                                               |

| Color Space Converter (CSC) Common Settings 43               |

| Outline Dimensions                                           |

| Ordering Guide45                                             |

#### **REVISION HISTORY**

10/05—Revision 0: Initial Version

# **ELECTRICAL SPECIFICATIONS**

Table 1.

|                                                                       |      |            | ΑI                     | )9889KSTZ        | -80  |                                                  |

|-----------------------------------------------------------------------|------|------------|------------------------|------------------|------|--------------------------------------------------|

| Parameter                                                             | Temp | Test Level | Min                    | Тур              | Max  | Unit                                             |

| DIGITAL INPUTS                                                        |      |            |                        |                  |      |                                                  |

| Input Voltage, High (V <sub>IH</sub> )                                | Full | VI         | 1.4                    |                  |      | V                                                |

| Input Voltage, Low (V <sub>IL</sub> )                                 | Full | VI         |                        |                  | 0.7  | V                                                |

| Input Current, High (V <sub>IH</sub> )                                | Full | V          |                        |                  | -1.0 | mA                                               |

| Input Current, Low (V <sub>IL</sub> )                                 | Full | V          |                        |                  | +1.0 | mA                                               |

| Input Capacitance                                                     | 25°C | V          |                        | 3                |      | рF                                               |

| DIGITAL OUTPUTS                                                       |      |            |                        |                  |      | ·                                                |

| Output Voltage, High (V <sub>OH</sub> )                               | Full | VI         | AV <sub>DD</sub> – 0.1 |                  |      | V                                                |

| Output Voltage, Low (V <sub>OL</sub> )                                | Full | VI         |                        |                  | 0.4  | V                                                |

| THERMAL CHARACTERISTICS                                               |      |            |                        |                  |      |                                                  |

| θ <sub>IC</sub> Junction-to-Case                                      |      |            |                        |                  |      |                                                  |

| Thermal Resistance                                                    |      | V          |                        |                  | 25   | °C/W                                             |

| θ <sub>IA</sub> Junction-to-Ambient                                   |      |            |                        |                  |      |                                                  |

| Thermal Resistance                                                    | 1    | V          |                        |                  | 30   | °C/W                                             |

| Ambient Temperature                                                   | Full | v          | 0                      | 25               | 70   | ∘€, ₩                                            |

| DC SPECIFICATIONS                                                     |      |            | +                      |                  |      | <del>                                     </del> |

| Input Leakage Current, In                                             | 25°C | VI         | -10                    |                  | +10  | μΑ                                               |

| Input Clamp Voltage (–16 mA)                                          | 25°C | V          |                        | -0.8             | 1 10 | V                                                |

| Input Clamp Voltage (+16 mA)                                          | 25°C | V          |                        | +0.8             |      | ľ                                                |

| Differential High Level Output Voltage                                | 25 C | V          |                        | AV <sub>CC</sub> |      | V                                                |

| Differential Output Short-Circuit Current                             |      | v          |                        | AVCC             | 10   | μA                                               |

| POWER SUPPLY                                                          |      | V          |                        |                  | 10   | μΛ                                               |

|                                                                       | Full | - IV       | 1.71                   | 1.8              | 1.89 | V                                                |

| V <sub>DD</sub> (All) Supply Voltage                                  |      |            | 1.71                   | 1.0              |      |                                                  |

| V <sub>DD</sub> Supply Voltage Noise                                  | Full | V          |                        |                  | 50   | mV p-p                                           |

| Complete Power-Down Current<br>(Everything Except I <sup>2</sup> C)   | 25°C | IV         |                        | 6                | 13   | mA                                               |

| Quiet Power Down Current<br>(Monitor Detect On)                       | 25°C | VI         |                        | 7                |      | mA                                               |

| Transmitter Supply Current                                            | 25°C | VI         |                        | 165              |      | mA                                               |

| (27 MHz Typical Random Pattern)                                       | 23 C | *'         |                        | 105              |      | 1117                                             |

| Transmitter Supply Current                                            | 25°C | IV         |                        | 185              | 205  | mA                                               |

| (80 MHz Typical Random Pattern)                                       | 25 C | 17         |                        | 105              | 203  | 11171                                            |

| Transmitter Total Power                                               |      |            |                        |                  |      |                                                  |

| (80 MHz Single Pixel Stripe Pattern; Worst Case Operating Conditions) | Full | VI         |                        |                  | 430  | mW                                               |

| AC SPECIFICATIONS                                                     |      |            |                        |                  |      |                                                  |

| CLK Frequency                                                         | 25°C | IV         | 13.5                   |                  | 80   | MHz                                              |

| CLK Duty Cycle                                                        | 25°C | VI         | 40%                    |                  | 60%  |                                                  |

| Worst Case CLK Input Jitter                                           | Full | VI         |                        |                  | 1.0  | ns                                               |

| Setup Time to CLK Falling Edge                                        | 1    | VI         | TBD                    |                  | TBD  | ns                                               |

| Hold Time to CLK Falling Edge                                         |      | VI         | TBD                    |                  | TBD  | ns                                               |

| TMDS Differential Swing                                               |      | VII        | 800                    | 1000             | 1200 | mV                                               |

| VSYNC and HSYNC Delay from DE Falling Edge                            | 1    | VI         |                        | 1                |      | UI                                               |

| VSYNC and HSYNC Delay to DE Rising Edge                               |      | VI         |                        | 1                |      | UI                                               |

| DE High Time                                                          | 25°C | VI         |                        |                  | 8191 | UI                                               |

| DE Low Time                                                           | 25°C | VI         |                        | 138              | •    | UI                                               |

| Differential Output Swing Low-to-High Transition Time                 | 25°C | VII        | 75                     |                  | 490  | ps                                               |

| Differential Swing Output High-to-Low Transition Time                 | 25°C | VII        | 75                     |                  | 490  | ps                                               |

|                                           |      |            |     | AD9889KSTZ | -80 |      |

|-------------------------------------------|------|------------|-----|------------|-----|------|

| Parameter                                 | Temp | Test Level | Min | Тур        | Max | Unit |

| AUDIO ACTIMING                            |      |            |     |            |     |      |

| Sample Rate (I <sup>2</sup> S and S/PDIF) | Full | IV         | 32  |            | 192 | kHz  |

| I <sup>2</sup> S Cycle Time               | 25°C | IV         |     |            | 1   | UI   |

| I <sup>2</sup> S Setup Time               | 25°C | IV         |     | 15         |     | ns   |

| I <sup>2</sup> S Hold Time                | 25°C | IV         |     | 0          |     | ns   |

| Audio Pipeline Delay                      | 25°C | IV         |     | 75         |     | us   |

------

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                    | Rating                            |

|------------------------------|-----------------------------------|

| Digital Inputs               | 5 V to 0.0 V                      |

| Digital Output Current       | 20 mA                             |

| Operating Temperature Range  | -40°C to +85°C<br>-65°C to +150°C |

| Storage Temperature Range    | −65°C to +150°C                   |

| Maximum Junction Temperature | 150°C                             |

| Maximum Case Temperature     | 150°C                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **EXPLANATION OF TEST LEVELS**

Table 3.

| Level | Test                                                                               |

|-------|------------------------------------------------------------------------------------|

| I     | 100% production tested.                                                            |

| II    | 100% production tested at 25°C and sample tested at specified temperatures.        |

| Ш     | Sample tested only.                                                                |

| IV    | Parameter is guaranteed by design and characterization testing.                    |

| V     | Parameter is a typical value only.                                                 |

| VI    | 100% production tested at 25°C; guaranteed by design and characterization testing. |

| VII   | Limits defined by HDMI specification.                                              |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

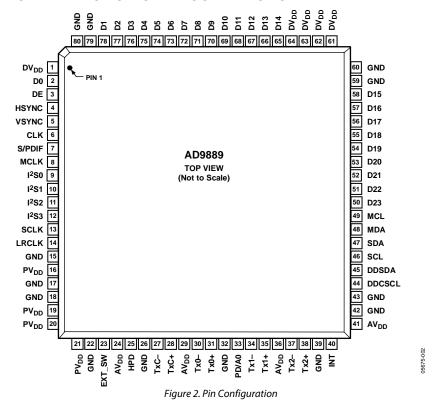

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 4. Complete Pinout List**

| Pin Type | Pin No.     | Mnemonic              | Description                                               | Value      |

|----------|-------------|-----------------------|-----------------------------------------------------------|------------|

| INPUTS   |             |                       |                                                           |            |

|          | 50 to 58,   |                       |                                                           |            |

|          | 65 to 78, 2 | D[23:0]               | Video Data Input                                          | 1.8 V CMOS |

|          | 6           | CLK                   | Video Clock Input                                         | 1.8 V CMOS |

|          | 3           | DE                    | Data Enable Bit for Digital Video                         | 1.8 V CMOS |

|          | 4           | HSYNC                 | Horizontal SYNC Input                                     | 1.8 V CMOS |

|          | 5           | VSYNC                 | Vertical SYNC Input                                       | 1.8 V CMOS |

|          | 23          | EXT_SW                | Differential Output Swing Adjustment                      | 1.8 V CMOS |

|          | 25          | HPD                   | Hot Plug Detect Signal                                    | 1.8 V CMOS |

|          | 7           | S/PDIF                | S/PDIF (Sony/Philips Digital Interface) Audio Input Pin   | 1.8 V CMOS |

|          | 8           | MCLK                  | Audio Reference Clock, $128 \times fs$ or $256 \times fs$ | 1.8 V CMOS |

|          | 12 to 9     | I <sup>2</sup> S[3:0] | I <sup>2</sup> S Audio Data Inputs                        | 1.8 V CMOS |

|          | 13          | SCLK                  | I <sup>2</sup> S Audio Clock                              | 1.8 V CMOS |

|          | 14          | LRCLK                 | Left/Right Channel Selection                              | 1.8 V CMOS |

|          | 33          | PD/A0                 | Power-Down Control                                        | 1.8 V CMOS |

| OUTPUTS  |             |                       |                                                           |            |

|          | 28, 27      | TxC+                  | Differential Clock Output                                 | TMDS       |

|          |             | TxC-                  | Differential Clock Output Complement                      |            |

|          | 38, 37      | Tx2+                  | Differential Output Channel 2                             | TMDS       |

|          |             | Tx2-                  | Differential Output Channel 2 Complement                  |            |

|          | 35, 34      | Tx1+                  | Differential Output Channel 1                             | TMDS       |

|          |             | Tx1-                  | Differential Output Channel 1 Complement                  |            |

|          | 31, 30      | Tx0+                  | Differential Output Channel 0                             | TMDS       |

|          |             | Tx0-                  | Differential Output Channel 0 Complement                  |            |

|          | 40          | INT                   | Monitor Sense Connection Status                           | 1.8 V CMOS |

| Pin Type     | Pin No.                                                     | Mnemonic  | Description                              | Value      |

|--------------|-------------------------------------------------------------|-----------|------------------------------------------|------------|

| POWER SUPPLY |                                                             |           |                                          |            |

|              | 24, 29, 36, 41                                              | $AV_{DD}$ | Output Power Supply                      | 1.8 V      |

|              | 1, 61, 62, 63, 64                                           | $DV_DD$   | Digital and I/O Power Supply             | 1.8 V      |

|              | 16, 19, 20, 21                                              | $PV_{DD}$ | PLL Power Supply                         | 1.8 V      |

|              | 15, 17, 18, 22,<br>26, 32, 39, 42,<br>43, 59, 60, 79,<br>80 | GND       | Ground                                   | 0 V        |

| CONTROL      |                                                             |           |                                          |            |

|              | 47                                                          | SDA       | Serial Port Data I/O                     | 3.3 V CMOS |

|              | 46                                                          | SCL       | Serial Port Data Clock (100 kHz Maximum) | 3.3 V CMOS |

|              | 48                                                          | MDA       | Serial Port Data I/O to HDCP Keys        | 3.3 V CMOS |

|              | 49                                                          | MCL       | Serial Port Data Clock to HDCP Keys      | 3.3 V CMOS |

|              | 45                                                          | DDSDA     | Serial Port Data I/O to Receiver         | 3.3 V CMOS |

|              | 44                                                          | DDCSCL    | Serial Port Data Clock to Receiver       | 3.3 V CMOS |

#### **Table 5. Pin Function Descriptions**

| Pin Mnemonic          | Description                                                                                                                                       |  |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OUTPUTS               |                                                                                                                                                   |  |  |  |  |  |  |

| TxC+                  | Differential Clock Output at Pixel Clock Rate; Transition Minimized Differential Signaling (TMDS).                                                |  |  |  |  |  |  |

| TxC-                  | Differential Clock Output Complement.                                                                                                             |  |  |  |  |  |  |

| Tx2+                  | Differential Output of the Red Data at 10× the Pixel Clock Rate; TMDS.                                                                            |  |  |  |  |  |  |

| Tx2-                  | Differential Red Output Complement.                                                                                                               |  |  |  |  |  |  |

| Tx1+                  | Differential Output of the Green Data at 10× the Pixel Clock Rate; TMDS.                                                                          |  |  |  |  |  |  |

| Tx1-                  | Differential Green Output Complement.                                                                                                             |  |  |  |  |  |  |

| Tx0+                  | Differential Output of the Blue Data at 10× the Pixel Clock Rate; TMDS.                                                                           |  |  |  |  |  |  |

| Tx0-                  | Differential Blue Output Complement.                                                                                                              |  |  |  |  |  |  |

| INT                   | Monitor Sense.                                                                                                                                    |  |  |  |  |  |  |

| SERIAL PORT (2-WIRE)  |                                                                                                                                                   |  |  |  |  |  |  |

| SDA                   | Serial Port Data I/O.                                                                                                                             |  |  |  |  |  |  |

| SCL                   | Serial Port Data Clock.                                                                                                                           |  |  |  |  |  |  |

| DDSDA                 | Serial Port Data I/O Master to Receiver.                                                                                                          |  |  |  |  |  |  |

| DDCSCL                | Serial Port Data Clock Master to Receiver.                                                                                                        |  |  |  |  |  |  |

| MDA                   | Serial Port Data I/O Master to HDCP Keys.                                                                                                         |  |  |  |  |  |  |

| MCL                   | Serial Port Data Clock Master to HDCP Keys.                                                                                                       |  |  |  |  |  |  |

|                       | For a full description of the 2-wire serial register and how it works, refer to the 2-Wire Serial Control Port section.                           |  |  |  |  |  |  |

| INPUTS                |                                                                                                                                                   |  |  |  |  |  |  |

| D[23:0]               | Digital Input in RGB or YCbCr Format.                                                                                                             |  |  |  |  |  |  |

| CLK                   | Video Clock Input.                                                                                                                                |  |  |  |  |  |  |

| DE                    | Data Enable for Video Data.                                                                                                                       |  |  |  |  |  |  |

| HSYNC                 | Horizontal Sync Input.                                                                                                                            |  |  |  |  |  |  |

| VSYNC                 | Vertical Sync Input. This is the input for vertical sync.                                                                                         |  |  |  |  |  |  |

| EXT_SW                | Swing Adjust Sets the Differential Output Voltage or Swing. An 887 $\Omega$ resistor (1% tolerance) should be placed between this pin and ground. |  |  |  |  |  |  |

| HPD                   | Hot Plug Detect. This indicates to the interface whether the receiver is connected.                                                               |  |  |  |  |  |  |

| S/PDIF                | S/PDIF Audio Input. This is the audio input from a Sony/Philips Digital Interface.                                                                |  |  |  |  |  |  |

| MCLK                  | Audio Reference Clock. Set either to $128 \times fs$ or $256 \times fs$ .                                                                         |  |  |  |  |  |  |

| I <sup>2</sup> S[3:0] | I <sup>2</sup> S Audio Inputs. These represent the eight channels of audio (two per input) available through I <sup>2</sup> S.                    |  |  |  |  |  |  |

| I <sup>2</sup> S CLK  | I <sup>2</sup> S Audio Clock.                                                                                                                     |  |  |  |  |  |  |

| LRCLK                 | Left/Right Channel Selection.                                                                                                                     |  |  |  |  |  |  |

| PD/A0                 | Power Down.                                                                                                                                       |  |  |  |  |  |  |

| Pin Mnemonic | Description                                                                                                                                                                                                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY |                                                                                                                                                                                                                                                                                              |

| $DV_{DD}$    | Main Power Supply. These pins supply power to the main elements of the circuit. They should be filtered and as quiet as possible.                                                                                                                                                            |

| $AV_{DD}$    | Output Power Supply                                                                                                                                                                                                                                                                          |

| $PV_{DD}$    | Clock Generator Power Supply. The most sensitive portion of the AD9889 is the clock generation circuitry. These pins provide power to the clock PLL (phase-locked loop) and help the user design for optimal performance. The designer should provide quiet, noise-free power to these pins. |

| GND          | Ground. The ground return for all circuitry on-chip. It is recommended that the AD9889 be assembled on a single solid ground plane, with careful attention given to ground current paths.                                                                                                    |

#### I<sup>2</sup>C ADDRESSES

The SDA/SCL programming address is 0x72 or 0x7A based on whether A0 is pulled high ( $10 \text{ k}\Omega$  resistor = 0x7A) or pulled low ( $10 \text{ k}\Omega$  resistor = 0x72).

The MDA/MCL EEPROM address is 0xA0.

The EDID EEPROM on the receiver is expected to have an address of 0xA0.

#### **LIST OF REFERENCE DOCUMENTS**

#### Table 6.

| Document       | Description                                                                    |

|----------------|--------------------------------------------------------------------------------|

| EIA/CEA-861B   | Describes audio and video infoframes as well as the E-EDID structure for HDMI. |

| HDMI V1.1      | Defining document for HDMI Version 1.1. Can be located at www.hdmi.org.        |

| HDCPv1.0       | Defining document for HDCP Version 1.1. Can be located at www.digital-cp.com.  |

| ITU-R BT.656-3 | Defining document for BT656.                                                   |

#### **FORMAT STANDARDS**

In this document, data is represented in a variety of ways.

#### Table 7.

| Data Type | Format                                                                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| 0xNN      | Hexadecimal (base-16) numbers are represented using the C language notation, preceded by 0x.                                   |

| 0bNN      | Binary (base-2) numbers are represented using the C language notation, preceded by 0b.                                         |

| NN        | Decimal (base-10) numbers are represented using no additional prefixes or suffixes.                                            |

| Bit       | Bits are numbered in little-endian format, that is, the least significant bit (LSB) of a byte or word is referred to as Bit 0. |

### **DESIGN GUIDE**

#### **GENERAL DESCRIPTION**

The AD9889 HDMI transmitter provides a high bandwidth digital content protected (HDCP) digital link between a wide range of digital input formats—both audio and video (see Table 8) and output formats (see Table 9). Video and audio data are captured and prepared for transmission while three separate I<sup>2</sup>C buses (two of which are masters) are used to program and provide content protection for the data to be transmitted.

#### **VIDEO DATA CAPTURE**

The AD9889 can accept video data from as few as eight pins (YCbCr DDR) representing 8-bit data or as many as 24 pins representing 12-bit data. The AD9889 is capable of detecting all of the 34 video formats defined in the EIA/CEA-861B specification. If video ID (VID) 32, 33, or 34 is present, the user needs to set Register R0x15[0] to 0b1, as these modes have  $V_{\text{REF}}$  frequencies of 30 Hz or less. The user can read the detected video format at R0x3E[7:2]. Formats outside the EIA/CEA-861B specification can be read in R0x3F[7:5]. Detailed line count differences for 240p and 288p modes can be read from R0x3F[4:3]. In order to distinguish between an aspect ratio of 4:3 and one of 16:9, R0x17[1] should be set accordingly.

**Table 8. Input Formats Supported**

| No. of Bits | Input Format          |

|-------------|-----------------------|

| 12          | RGB (DDR)             |

| 12          | YCbCr 4:4:4 (DDR)     |

| 24          | RGB 4:4:4             |

| 24          | YCbCr 4:4:4           |

| 16          | YCbCr 4:2:2 (ITU.601) |

| 20          | YCbCr 4:2:2 (ITU.601) |

| 24          | YCbCr 4:2:2 (ITU.601) |

| 8           | YCbCr (DDR)           |

| 10          | YCbCr (DDR)           |

| 12          | YCbCr (DDR)           |

| 8           | YCbCr 4:2:2 (ITU.656) |

| 10          | YCbCr 4:2:2 (ITU.656) |

| 12          | YCbCr 4:2:2 (ITU.656) |

**Table 9. Output Formats Supported**

| No. of Bits | Output Format |

|-------------|---------------|

| 24          | RGB 4:4:4     |

| 24          | YCbCr 4:4:4   |

| 16          | YCbCr 4:2:2   |

| 20          | YCbCr 4:2:2   |

| 24          | YCbCr 4:2:2   |

#### **INPUT FORMATS**

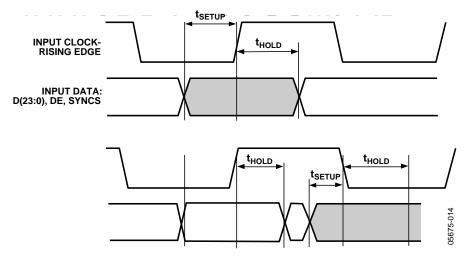

Figure 3. Timing for Data Input

#### Normal 4:4:4 Input Format (RGB or YCbCr) Input ID = 0

An input format of RGB 4:4:4 or YCbCr 4:4:4 can be selected by setting the input ID (R0x15[3:1]) to 0b000. The input color space (CS) must be selected by setting R0x16[0] to 0b0 for RGB or 0b1 for YCbCr. There is no need to set the input style (R0x16[3:2]).

Table 10.

|              |    |                                              |  |  |  |  |  |  |  | D | ata<2 | 23:0> |  |  |  |  |  |  |  |  |  |  |  |  |

|--------------|----|----------------------------------------------|--|--|--|--|--|--|--|---|-------|-------|--|--|--|--|--|--|--|--|--|--|--|--|

| Input Format | 23 |                                              |  |  |  |  |  |  |  |   |       |       |  |  |  |  |  |  |  |  |  |  |  |  |

| RGB 4:4:4    |    | R[7:0] G[7:0] B[7:0]                         |  |  |  |  |  |  |  |   |       |       |  |  |  |  |  |  |  |  |  |  |  |  |

| YCbCr 4:4:4  |    | R[7:0] G[7:0] B[7:0] Ctr[7:0] Y[7:0] Cb[7:0] |  |  |  |  |  |  |  |   |       |       |  |  |  |  |  |  |  |  |  |  |  |  |

#### YCbCr 4:2:2 Formats (24 Bits, 20 Bits, or 16 Bits) with Separate Sync, Input ID = 1

An input with YCbCr 4:2:2 with separate syncs can be selected by setting the Input ID (R0x15[3:1]) to 0b001. The input CS (R0x16[0]) must be set to 0b1 for proper operation. The data bit width (24 bits, 20 bits, or 16 bits) must be set with R0x16[5:4]. The three input pin assignment styles are shown in Table 11. The input style can be set in R0x16[3:2].

Table 11.

|                  |      |       |    |      |       |    |    |    |     |         | Data < | <23:0 | >    |        |   |   |     |       |      |   |    |      |      |   |

|------------------|------|-------|----|------|-------|----|----|----|-----|---------|--------|-------|------|--------|---|---|-----|-------|------|---|----|------|------|---|

| Input Format     | 23   | 22    | 21 | 20   | 19    | 18 | 17 | 16 | 5 1 | 5 14    | 13     | 12    | 11   | 10     | 9 | 8 | 7   | 6     | 5    | 4 | 3  | 2    | 1    | 0 |

|                  |      |       |    |      |       |    |    |    | :   | Style 1 |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

| YCbCr 4:2:2 Sep. |      |       |    | Cb[  | 11:4] |    |    |    |     |         |        | Y[11  | :4]  |        |   |   |     | Cb[   | 3:0] |   |    | Y[3  | 3:0] |   |

| Sync (24 bit)    |      |       |    | Cr[1 | 11:4] |    |    |    |     |         |        | Y[11  | :4]  |        |   |   |     | Cr[3  | 3:0] |   |    | Y[3  | 3:0] |   |

| YCbCr 4:2:2 Sep. |      |       |    | Cb   | [9:2] |    |    |    |     |         |        | Y[9:  | 2]   |        |   |   | Cb  | [1:0] |      |   | Y[ | 1:0] |      |   |

| Sync (20 bit)    |      |       |    | Cr[  | 9:2]  |    |    |    |     |         |        | Y[9:  | 2]   |        |   |   | Cr[ | 1:0]  |      |   | Y[ | 1:0] |      |   |

| YCbCr 4:2:2 Sep. |      |       |    | Cb   | [7:0] |    |    |    |     |         |        | Y[7:  | 0]   |        |   |   |     |       |      |   |    |      |      |   |

| Sync (20 bit)    |      |       |    | Cr[  | 7:0]  |    |    |    |     |         |        | Y[7:  | 0]   |        |   |   |     |       |      |   |    |      |      |   |

|                  |      |       |    |      |       |    |    |    |     | Style 2 |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

| 24-bit           | Cb[1 | 11:0] |    |      |       |    |    |    |     |         |        |       | Y[1  | 1:0]   |   |   |     |       |      |   |    |      |      |   |

|                  | Cr[1 | 1:0]  |    |      |       |    | _  |    | -   |         | _      | _     | -Y[1 | l:0] - | - |   |     |       |      |   |    |      |      |   |

| 20-bit           | Cb[9 | 9:0]  |    |      |       |    |    |    |     |         | Y[9:   | 0]    |      |        |   |   |     |       |      |   |    |      |      |   |

|                  | Cr[9 | :0]   |    |      |       |    |    |    |     |         | Y[9:   | 0]    |      |        |   |   |     |       |      |   |    |      |      |   |

| 16-bit           | Cb[7 | 7:0]  |    |      |       |    |    |    | Υ   | [7:0]   |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

|                  | Cr[7 | :0]   |    |      |       |    |    |    | Y   | [7:0]   |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

|                  |      |       |    |      |       |    |    |    | :   | Style 3 |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

| 24-bit           | Y[11 | :0]   |    |      |       |    |    |    |     |         |        |       | Cb[  | 11:0]  |   |   |     |       |      |   |    |      |      |   |

|                  | Y[11 | :0]   |    |      |       |    |    |    |     |         |        |       | Cr[1 | 1:0]   |   |   |     |       |      |   |    |      |      |   |

| 20-bit           | Y[9: | 0]    |    |      |       |    |    |    |     |         | Cb[    | 9:0]  |      |        |   |   |     |       |      |   |    |      |      |   |

|                  | Y[9: | 0]    |    |      |       |    |    |    |     |         | Cr[9   | 9:0]  |      |        |   |   |     |       |      |   |    |      |      |   |

| 16-bit           | Y[7: | 0]    |    |      |       |    |    |    | C   | b[7:0]  |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

|                  | Y[7: | 0]    |    |      |       |    |    |    | C   | r[7:0]  |        |       |      |        |   |   |     |       |      |   |    |      |      |   |

#### YCbCr 4:2:2 Formats (24 Bits, 20 Bits, or 16 Bits) with Embedded Syncs, Input ID = 2

An input with YCbCr 4:2:2 with embedded syncs can be selected by setting the input ID (R0x15[3:1]) to 0b010. HS YNC and VSYNC are embedded as Start of Active Video (SAV) and End of Active Video (EAV). The input CS (R0x16[0]) must be set to 0b1 for proper operation. The data bit width (24 = 12 bits, 20 = 10 bits, or 16 = 8 bits) must be set with R0x16[5:4]. The three input pin assignment styles are shown in Table 12. The input style can be set in R0x16[3:2]. The only difference between Input ID 1 and Input ID 2 is that the syncs on ID 2 are embedded in the data much like ITU 656 running at  $1 \times$  clock and double width.

Table 12.

|                  |      |        |    |    |    |    |    |    |         | Di         | ata < | 23:0> | >      |        |   |   |     |       |   |   |    |      |   |   |

|------------------|------|--------|----|----|----|----|----|----|---------|------------|-------|-------|--------|--------|---|---|-----|-------|---|---|----|------|---|---|

| Input Format     | 23   | 22     | 21 | 20 | 19 | 18 | 17 | 16 | 15 1    | 14         | 13    | 12    | 11     | 10     | 9 | 8 | 7   | 6     | 5 | 4 | 3  | 2    | 1 | 0 |

|                  |      |        |    |    |    |    |    |    | Styl    | e 1        |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

| YCbCr 4:2:2 Sep. | Cb[´ | 11:4]  |    |    |    |    |    |    | Y[11:4  | <u>.]</u>  |       |       |        |        |   |   | Cb  | [3:0] |   |   | Y[ | 3:0] |   |   |

| Sync (24 bit)    | Cr[1 | 1:4]   |    |    |    |    |    |    | Y[11:4  | <b>!</b> ] |       |       |        |        |   |   | Cr[ | [3:0] |   |   | Y[ | 3:0] |   |   |

| YCbCr 4:2:2 Sep. | Cb[9 | 9:2]   |    |    |    |    |    |    | Y[9:2]  |            |       |       |        |        |   |   | Cb  | [1:0] |   |   | Y[ | 1:0] |   |   |

| Sync (20 bit)    | Cr[9 | :2]    |    |    |    |    |    |    | Y[9:2]  |            |       |       |        |        |   |   | Cr[ | [1:0] |   |   | Y[ | 1:0] |   |   |

| YCbCr 4:2:2 Sep. | Cb[7 | 7:0]   |    |    |    |    |    |    | Y[7:0]  |            |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

| Sync (16 bit)    | Cr[7 | ':0]   |    |    |    |    |    |    | Y[7:0]  |            |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

|                  |      |        |    |    |    |    |    |    | Styl    | e 2        |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

| 24-bit           | Cb[´ | 11:0]  |    |    |    |    |    |    |         |            |       |       | Y[11   | :0]    |   |   |     |       |   |   |    |      |   |   |

|                  | Cr[1 | 1:0]   |    |    |    |    |    |    |         |            |       |       | Y[11   | :0]    |   |   |     |       |   |   |    |      |   |   |

| 20-bit           | Cb[9 | 9:0]   |    |    |    |    |    |    |         |            | Y[9:0 | 0]    |        |        |   |   |     |       |   |   |    |      |   |   |

|                  | Cr[9 | :0]    |    |    |    |    |    |    |         |            | Y[9:0 | 0]    |        |        |   |   |     |       |   |   |    |      |   |   |

| 16-bit           | Cb[7 | 7:0]   |    |    |    |    |    |    | Y[7:0]  |            |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

|                  | Cr[7 | ':0]   |    |    |    |    |    |    | Y[7:0]  |            |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

|                  |      |        |    |    |    |    |    |    | Styl    | e 3        |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

| 24-bit           | Y[11 | 1:0]   |    |    |    |    |    |    |         |            |       |       | Cb[    | 11:0]  |   |   |     |       |   |   |    |      |   |   |

|                  | Y[11 | l:0] _ |    |    |    |    |    | -  |         | _          | _     | _     | - Cr[1 | 1:0] _ | - |   |     |       |   |   |    |      |   |   |

| 20-bit           | Y[9: |        |    |    |    |    |    |    |         |            | Cb[9  |       |        |        |   |   |     |       |   |   |    |      |   |   |

|                  | Y[9: |        |    |    |    |    |    |    |         |            | Cr[9  | :0]   |        |        |   |   |     |       |   |   |    |      |   |   |

| 16-bit           | Y[7: | 0]     |    |    |    |    |    |    | Cb[7:0  |            |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

|                  | Y[7: | 0]     |    |    |    |    |    |    | Cr[7:0] | ]          |       |       |        |        |   |   |     |       |   |   |    |      |   |   |

#### YCbCr 4:2:2 Formats (Double Data Rate) Formats (12, 10, or 8 bits) with Separate Syncs, Input ID = 3

An input with YCbCr 4:2:2 DDR data and separate syncs can be selected by setting the input ID (R0x15[3:1]) to 0b011. The input CS (R0x16 [0]) must be set to 0b1. The data bit width (12 bits, 10 bits, or 8 bits) must be set with R0x16[5:4]. The two input pin assignment styles are shown in Table 13. The input style can be set in R0x16[3:2].

Table 13.

|                |                |         |              |                   |                        |                             |                                  |                                       |        | Data                                               | <23:                                                                      | 0>                                                                                               |                                                                   |                                                                                                                                 |    |    |       |       |    |      |    |    |    |

|----------------|----------------|---------|--------------|-------------------|------------------------|-----------------------------|----------------------------------|---------------------------------------|--------|----------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----|----|-------|-------|----|------|----|----|----|

| 23             | 22             | 21      | 20           | 19                | 18                     | 17                          | 16                               | 15                                    | 14     | 13                                                 | 12                                                                        | 11                                                                                               | 10                                                                | 9                                                                                                                               | 8  | 7  | 6     | 5     | 4  | 3    | 2  | 1  | 0  |

|                |                |         |              |                   |                        |                             |                                  |                                       | Style  | 1                                                  |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    |      |    |    |    |

|                |                |         |              |                   |                        |                             |                                  | Cb/                                   | Y/Cr/\ | /[11:4                                             |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    | [3:0 | )] |    |    |

|                |                |         |              |                   |                        |                             |                                  | Cb/                                   | Y/Cr/\ | ′[9:2]                                             |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    | [1:0 | )] |    |    |

| Cb/Y/Cr/Y[5:0] |                |         |              |                   |                        |                             |                                  |                                       |        |                                                    |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    |      |    |    |    |

|                |                |         |              |                   |                        |                             |                                  |                                       | Style  | 2                                                  |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    |      |    |    |    |

|                |                |         |              |                   |                        |                             |                                  |                                       |        |                                                    |                                                                           | Cb/                                                                                              | Y/Cr/\                                                            | /[11:0                                                                                                                          | 0] |    |       |       |    |      |    |    |    |

|                | Cb/Y/Cr/Y[9:0] |         |              |                   |                        |                             |                                  |                                       |        |                                                    |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    |    |       |       |    |      |    |    |    |

|                |                |         |              |                   |                        |                             |                                  |                                       |        |                                                    |                                                                           |                                                                                                  |                                                                   |                                                                                                                                 |    | Cb | /Y/Cr | /Y[7: | 0] |      |    |    |    |

|                | 23             | 23   22 | 23   22   21 | 23   22   21   20 | 23   22   21   20   19 | 23   22   21   20   19   18 | 23   22   21   20   19   18   17 | 23   22   21   20   19   18   17   16 | Cb/    | Style<br>  Cb/Y/Cr/\<br>  Cb/Y/Cr/\<br>  Cb/Y/Cr/\ | 23 22 21 20 19 18 17 16 15 14 13  Style 1  Cb/Y/Cr/Y[11:4] Cb/Y/Cr/Y[9:2] | 23 22 21 20 19 18 17 16 15 14 13 12    Style   Cb/Y/Cr/Y[11:4]   Cb/Y/Cr/Y[9:2]   Cb/Y/Cr/Y[7:0] | Style 1  Cb/Y/Cr/Y[11:4]  Cb/Y/Cr/Y[9:2]  Cb/Y/Cr/Y[7:0]  Style 2 | 23   22   21   20   19   18   17   16   15   14   13   12   11   10    Style 1  Cb/Y/Cr/Y[11:4]  Cb/Y/Cr/Y[9:2]  Cb/Y/Cr/Y[7:0] | 23 | 23 | 23    | 23    | 23 | 23   | 23 | 23 | 23 |

#### YCbCr 4:2:2 DDR (Double Data Rate) Formats (12 Bits, 10 Bits, or 8 Bits) with Embedded Syncs. Input ID = 4

An input with YCbCr 4:2:2 DDR data and embedded syncs (ITU 656) can be selected by setting the input ID (R0x15[3:1]) to 0b100. The input CS (R0x16[0]) must be set to 0b1. The data bit width (12 bits, 10 bits, or 8 bits) must be set with R0x16[5:4]. The two input pin assignment styles are shown in Table 14. The input style can be set in R0x16[3:2]. The order of data input is the order in the table (for example, 12-bit data is accepted as Cb0, Y0, Cr0, Y1, Cb2, Y2, Cr2, Y3).

Table 14.

|              |                |                      |    |    |    |    |    |    |      | D      | ata <2 | 23:0> |     |        |        |      |       |      |       |      |      |    |   |   |

|--------------|----------------|----------------------|----|----|----|----|----|----|------|--------|--------|-------|-----|--------|--------|------|-------|------|-------|------|------|----|---|---|

| Input Format | 23             | 22                   | 21 | 20 | 19 | 18 | 17 | 16 | 15   | 14     | 13     | 12    | 11  | 10     | 9      | 8    | 7     | 6    | 5     | 4    | 3    | 2  | 1 | 0 |

|              |                |                      |    |    |    |    |    |    | St   | yle 1  |        |       |     |        |        |      |       |      |       |      |      |    |   |   |

| 12-bit       |                |                      |    |    |    |    |    |    | Cb/\ | //Cr/Y | [11:4] |       |     |        |        |      |       |      |       |      | [3:0 | 0] |   |   |

| 10-bit       |                | Cb/Y/Cr/Y[9:2] [1:0] |    |    |    |    |    |    |      |        |        |       |     |        |        |      |       |      |       |      |      |    |   |   |

| 8-bit        | Cb/Y/Cr/Y[7:0] |                      |    |    |    |    |    |    |      |        |        |       |     |        |        |      |       |      |       |      |      |    |   |   |

|              |                |                      |    |    |    |    |    |    | St   | yle 2  |        |       |     |        |        |      |       |      |       |      |      |    |   |   |

| 12-bit       |                |                      |    |    |    |    |    |    |      |        |        |       | Cb/ | Y/Cr/\ | /[11:0 | 0]   |       |      |       |      |      |    |   |   |

| 10-bit       |                |                      |    |    |    |    |    |    |      |        |        |       |     |        | Cb     | /Y/C | r/Y[9 | 9:0] |       |      |      |    |   |   |

| 8-bit        |                |                      |    |    |    |    |    |    |      |        |        |       |     |        |        |      | Cb    | /Y/C | r/Y[7 | ':0] |      |    |   |   |

#### Normal 4:4:4 input format (RGB or YCbCr) Clocked at Double Data Rate (DDR), Input ID = 5

An input with YCbCr 4:2:2 DDR data and separate syncs can be selected by setting the input ID (R0x15[3:1]) to 0b011. The input CS (R0x16[0]) must be set to 0b1. The data bit width (12 bits, 10 bits, or 8 bits) must be set with R0x16[5:4]. The three input pin assignment styles are shown in Table 15. The input style can be set in R0x16[3:2].

Table 15.

|                                                 |    |    |    |    |    |    |    |    |      | D   | ata < | 23:0> | •    |      |   |   |      |      |   |   |       |            |   |   |

|-------------------------------------------------|----|----|----|----|----|----|----|----|------|-----|-------|-------|------|------|---|---|------|------|---|---|-------|------------|---|---|

| Input Format                                    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15   | 14  | 13    | 12    | 11   | 10   | 9 | 8 | 7    | 6    | 5 | 4 | 3     | 2          | 1 | 0 |

|                                                 |    |    |    |    |    |    |    |    | Styl | e 1 |       |       |      |      |   |   |      |      |   |   |       |            |   |   |

| RGB 4:4:4 (DDR)                                 |    |    |    |    |    |    |    | _  | _    | _   |       |       | G[3: | 0]-  | - |   | B[7: | 0]   |   |   |       |            |   |   |

| (1 <sup>st</sup> edge,<br>2 <sup>nd</sup> edge) |    |    |    |    |    |    |    |    |      |     |       |       | R[7: | 0]   |   |   |      |      |   |   | G[7:4 | 1]         |   |   |

| YCbCr 4:4:4 (DDR)                               |    |    |    |    |    |    |    |    |      |     |       |       | Y[3: | 0]   |   | 0 | Cb[7 | 7:0] |   |   |       |            |   |   |

| (1 <sup>st</sup> edge,<br>2 <sup>nd</sup> edge) |    |    |    |    |    |    |    |    |      |     |       |       | Cr[7 | :0]  |   |   |      |      |   |   | Y[7:4 | <u>.</u> ] |   |   |

|                                                 |    |    |    |    |    |    |    |    | Styl | e 2 |       |       |      |      |   |   |      |      |   |   |       |            |   |   |

| RGB 4:4:4 (DDR)                                 |    |    |    |    |    |    |    |    |      |     |       |       | R[7: | 0]   |   |   |      |      |   |   | G[7:4 | 1]         |   |   |

| (1 <sup>st</sup> edge,<br>2 <sup>nd</sup> edge) |    |    |    |    |    |    |    |    |      |     |       |       | G[3: | 0]   |   | I | B[7: | 0]   |   |   |       |            |   |   |

| YCbCr 4:4:4 (DDR)<br>(1 st edge,                |    |    |    |    |    |    |    |    |      |     |       |       | Cr[7 | :0]  |   |   |      |      |   |   | Y[7:4 | <u>.]</u>  |   |   |

| 2 <sup>nd</sup> edge)                           |    |    |    |    |    |    |    |    |      |     |       |       | Y[3: | 0]   |   | ( | Cb[7 | 7:0] |   |   |       |            |   |   |

|                                                 |    |    |    |    |    |    |    |    | Styl | e 3 |       |       |      |      |   |   |      |      |   |   |       |            |   |   |

| YCbCr 4:4:4 (DDR)                               |    |    |    |    |    |    |    |    |      |     |       |       | Y[7: | 0]   |   |   |      |      |   |   | Cb[7  | :4]        |   |   |

| (1 <sup>st</sup> edge,<br>2 <sup>nd</sup> edge) |    |    |    |    |    |    |    |    |      |     |       | ,     | Cb[3 | 3:0] |   | ( | Cr[7 | :0]  |   | • |       |            |   |   |

#### YCbCr 4:2:2 Formats (24, 20, or 16 bits) DDR with Separate Sync, Input ID = 6

An input format of YCbCr 4:2:2 DDR can be selected by setting the input ID (R0x15[3:1]) to 0b110. The three different input pin assignment styles are shown in Table 16. The input style can be set in R0x16[3:2]. The input CS (R0x16[0]) must be set to 0b1. The data bit width (12, 10, or 8 bits) must be set to with R0x16[5:4].

The  $1^{st}$  or the  $2^{nd}$  edge may be the rising or falling edge. The data input edge is defined in R0x16[1]. 0b0 = rising edge; 0b1 = falling edge. Pixel 0 is the first pixel of the 4:2:2 word and should be where DE starts.

Table 16.

|                       |    |                   |       |    |    |    |     |       | D      | ata<2 | 23:0> |          |   |       |         |     |      |     |       |     |

|-----------------------|----|-------------------|-------|----|----|----|-----|-------|--------|-------|-------|----------|---|-------|---------|-----|------|-----|-------|-----|

| Input Format          | 23 | 22 2              | 1 20  | 19 | 18 | 17 | 16  | 15    | 14     | 13    | 12    | 11 10    | 9 | 8     | 7 6     | 5 ! | 5    | 4 3 | 3 2   | 1 ( |

|                       |    | ,                 |       |    |    |    |     | Style | e 1    |       |       |          |   |       |         |     |      |     |       |     |

| YCbCr 4:2:2 Sep       |    |                   |       |    |    |    |     | 1     | st Edg | je    |       | Y[7:4]   |   |       | Cb[3    | :0] |      | Y[3 | :0]   |     |

| Syncs (DDR)           |    | 1 <sup>st</sup> F | Pixel |    |    |    | nd  |       |        |       | •     | Cb[11:4] |   |       | •       |     |      | Y[1 | 1:8]  |     |

| 12-bit                |    |                   |       |    |    | Ec | lge |       |        |       |       |          |   |       |         |     |      |     |       |     |

|                       |    | 2 <sup>nd</sup>   | Pixel |    |    |    |     |       |        |       |       | Y[7:4]   |   |       | Cr[3:0] |     |      | _   | 3:0]  |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[11:4] |   |       |         |     |      |     | 11:8] | 1   |

| YCbCr 4:2:2 Sep       |    |                   |       |    |    |    |     |       |        |       |       | Y[5:4]   | ( | Cb[3  | :0]     |     | 3:0] |     |       |     |

| Syncs (DDR)<br>10-bit |    |                   |       |    |    |    |     |       |        |       |       | Cb[9:4]  |   |       |         |     | 9:6] |     |       |     |

| 10-bit                |    |                   |       |    |    |    |     |       |        |       |       | Y[5:4]   | ( | Cr[3: | :0]     | _   | 3:0] |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[9:4]  |   |       |         | Y[9 | 9:6] |     |       |     |

| YCbCr 4:2:2 Sep.      |    |                   |       |    |    |    |     |       |        |       |       | Cb[3:0]  |   |       | ′[3:0]  |     |      |     |       |     |

| Syncs (DDR)           |    |                   |       |    |    |    |     |       |        |       |       | Cb[7:4]  |   |       | ′[7:4]  |     |      |     |       |     |

| 8-bit                 |    |                   |       |    |    |    |     |       |        |       |       | Cr[3:0]  |   |       | '[3:0]  |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[7:4]  |   | Y     | ′[7:4]  |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     | Style | e 2    |       |       |          |   |       |         |     |      |     |       |     |

| 12-bit                |    |                   |       |    |    |    |     |       | _      |       |       | Y[11:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cb[11:0] |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[11:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[11:0] |   |       |         |     |      |     |       | 1   |

| 10-bit                |    |                   |       |    |    |    |     |       |        |       |       | Y[9:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cb[9:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[9:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[9:0]  |   |       |         |     |      | ,   |       |     |

| 8-bit                 |    |                   |       |    |    |    |     |       |        |       |       | Y[7:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cb[7:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[7:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[7:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     | Style | e 3    |       |       |          |   |       |         |     |      |     |       |     |

| 12-bit                |    |                   |       |    |    |    |     |       |        |       |       | Cb[11:0] |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[11:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[11:0] |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[11:0]  |   |       |         |     |      |     |       | 1   |

| 10-bit                |    |                   |       |    |    |    |     |       |        |       |       | Cb[9:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[9:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[9:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[9:0]   |   |       |         |     |      |     |       |     |

| 8-bit                 |    |                   |       |    |    |    |     |       |        |       |       | Cb[7:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[7:0]   |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Cr[7:0]  |   |       |         |     |      |     |       |     |

|                       |    |                   |       |    |    |    |     |       |        |       |       | Y[7:0]   |   |       |         |     |      |     |       |     |

#### 4:2:2 TO 4:4:4 DATA CONVERSION

The AD9889 has the ability to convert YCbCr video from 4:4:4 to 4:2:2 and 4:2:2 to 4:4:4. To convert from 4:4:4 to 4:2:2, the video data goes through a filter first to remove any artificial downsampling noise. To convert from 4:2:2 to 4:4:4, the AD9889 utilizes either the zero-order upconversion (pixel repetition) or first-order upconversion (linear interpolation). The upconversion and downconversion are used when the video output timing format does not match the video input timing format. The video output format is set by Register R0x16[7:6]. The video input format is set by the video ID (R0x15[3:1]) and video color space (R0x16[0]). The default mode for upconversion is pixel repetition. To use linear interpolation, set Register R0x17[2] to 1.

# HORIZONTAL SYNC, VERTICAL SYNC, AND DEGENERATION

When transmitting video data across the TMDS interface, it is necessary to have an HSYNC, VSYNC, and data enable (DE) defined for the image. ITU-656 based sources have start of active video (SAV) and end of active video (EAV) signals built in, but the HSYNC and VSYNC must be generated (the DE is implied by the SAV and EAV signals). Other sources (with separate syncs) have HSYNC, VSYNC, and DE supplied at the same time as the pixel data.

#### **DEGENERATION**

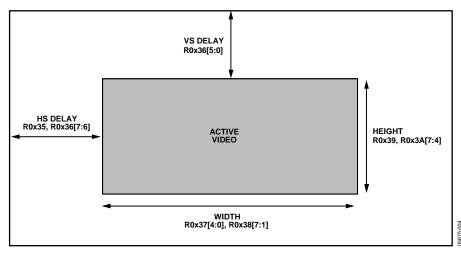

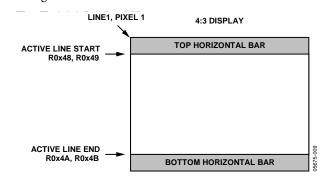

The AD9889 offers a choice of DE from an external pin, or an internally generated DE. To activate the internal DE generation, set Register R0x17[0] to 1. Register R0x35 to Register R0x3A are used to define the DE. R0x35 and R0x36[7:6] define the number of pixels from the HS leading edge to the DE leading edge. R0x36[5:0] are the number of HSYNCs between the leading edge of VS and DE. R0x37[7:5] defines the difference of HS counts during VS blanking for interlace video. R0x37[4:0] and R0x38[7:1] indicate the width of the DE. R0x39 and R0x3A[7:4] are the number of lines of active video (see Figure 4).

#### **HSYNC AND VSYNC GENERATION**

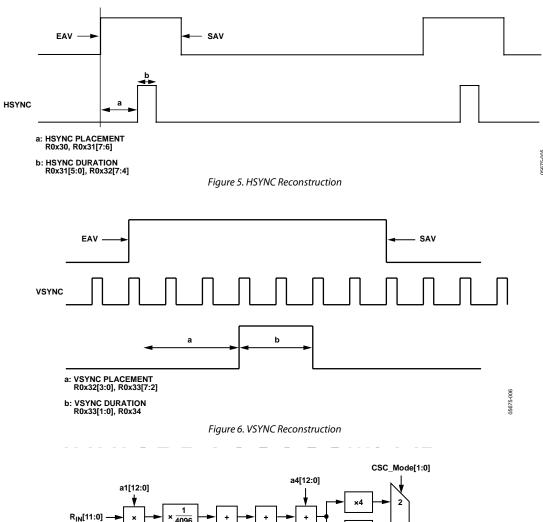

For video with embedded HSYNC and VSYNC, such as EAV and SAV, found in ITU 656 format, it is necessary to reconstruct HSYNC and VSYNC. This is done with Register R0x30 to Register R0x34. R0x30 and R0x31[7:6] specify the number of pixels between the HSYNC leading edge and the trailing edge of DE. Register R0x31[5:0] and Register R0x32[7:4] are the duration of the HSYNC in pixel clocks. R0x32[3:0] and R0x33[7:2] are the number of HS pulses between the trailing edge of the last DE and the leading edge of the VSYNC pulse. Register R0x33[1:0] and Register R0x34[7:0] are the duration of VSYNC in units of HSYNCs. HSYNC and VSYNC polarity can be specified by setting R0x17[6] (for VSYNC) and R0x17[5] (for HSYNC).

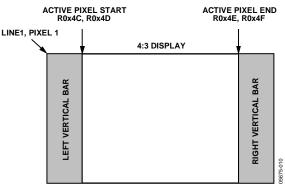

Figure 4. Active Video

Figure 7. Single CSC Channel

#### **COLOR SPACE CONVERSION MATRIX (CSC)**

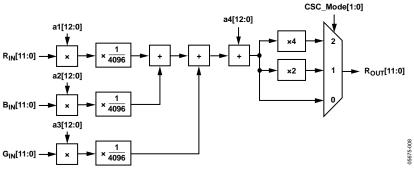

The color space conversion matrix in the AD9889 consists of three identical processing channels. In each channel, three input values are multiplied by three separate coefficients. Also included are an offset value for each row of the matrix and a scaling multiple for all values. Each value is 13-bit, twos complement resolution to ensure the signal integrity is maintained. The CSC is designed to run at speeds up to 80 MHz supporting resolutions up to 1080i at 60 Hz and UXGA at 60 Hz. With any-to-any color space support, RGB, YUV, YCbCr, and other formats are supported by the CSC.

The main inputs,  $R_{\rm IN}$ ,  $G_{\rm IN}$ , and  $B_{\rm IN}$  come from the 8-bit to 12-bit inputs from each channel. These inputs are based on the input format detailed in Table 10 to Table 16. The mapping of these inputs to the CSC inputs is shown in Table 17.

**Table 17. CSC Port Mapping**

| Input Channel | CSC Input Channel |

|---------------|-------------------|

| R/Cr          | R <sub>IN</sub>   |

| Gr/Y          | G <sub>IN</sub>   |

| B/Cb          | Bin               |

One of the three channels is represented in Figure 7. In each processing channel the three inputs are multiplied by three separate coefficients marked a1, a2, and a3. These coefficients are divided by 4096 to obtain nominal values ranging from -0.9998 to +0.9998. The variable labeled a4 is used as an offset control. The CSC\_Mode setting is the same for all three processing channels. This multiplies all coefficients and offsets by a factor of 2CSC\_Mode.

The functional diagram for a single channel of the CSC as per Figure 7 is repeated for the remaining G and B channels. The coefficients for these channels are b1, b2, b3, b4, c1, c2, c3, and c4.

A programming example and register settings for several common conversions are listed in the Color Space Converter (CSC) Common Settings section.

For a detailed functional description and more programming examples, refer to AN-795, *The AD9880 Color Space Converter User's Guide.*

### **AUDIO DATA CAPTURE**

The AD9889 is capable of receiving audio data in either I<sup>2</sup>S or S/PDIF format for packetization and transmission over the HDMI interface.

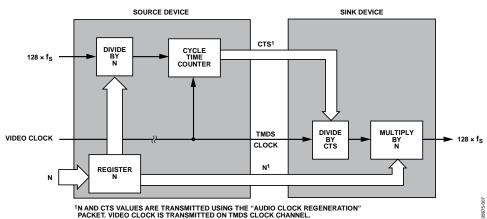

#### I<sup>2</sup>S AUDIO

The AD9889 can accommodate from two to eight channels of I²S audio at up to a 192 kHz sampling rate. Selection of I²S audio mode (vs. S/PDIF) is set with R0x0A[4] = 0. The detected sampling frequency (from 32 kHz to 192 kHz) can be read in R0x04[7:4]. The output sampling frequency (from 32 kHz to 192 kHz) can be selected with R0x15[7:4]. The number of channels and the specific channels can be selected in R0x0C[5:2] and R0x50[7:5]. If all eight channels (I²S0 to I²S3) are required, setting all bits or R0x0C[5:2] to 1 selects eight channels. If I²S0 only is needed, setting R0x0C[2] to 1 selects this. The placement of these packets with respect to their output can be specified in Register R0x0E to Register R0x11. Default settings place all channels in their respective position (I²S0 left channel in Channel 0 left position, I²S3 right channel in Channel 3 right position), but this mapping is completely programmable.