# 16-Bit, 2.5 MHz/5 MHz/10 MHz, 30 MSPS to 160 MSPS Dual Continuous Time Sigma-Delta ADC

# **Preliminary Technical Data**

AD9262

#### **FEATURES**

SNR: 82.5 dB (84.5 dBFS) to 10 MHz input

SFDR: 87 dBc to 10 MHz input

Noise figure: 15dB Input impedance: 1 k $\Omega$  Power: 675 mW

1.8 V analog supply operation 1.8 V to 3.3 V output supply Selectable bandwidth

2.5 MHz/5 MHz/10 MHz real 5 MHz/10 MHz/20MHz complex Output data rate: 30 MSPS to 160 MSPS

Integrated decimation filters

Integrated sample rate converter

On-chip PLL clock multiplier

On-chip voltage reference

Offset binary, Gray code, or twos complement data format

Serial control interface (SPI)

#### **APPLICATIONS**

Baseband quadrature receivers: CDMA2000, WCDMA, multicarrier GSM/EDGE, 802.16x, and LTE

Quadrature sampling instrumentation

**Medical equipment**

Radio detection and ranging (RADAR)

## **GENERAL DESCRIPTION**

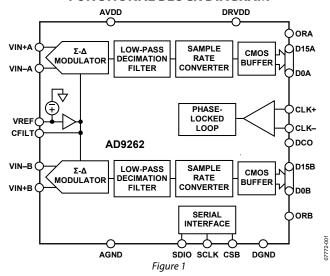

The AD9262 is a dual, 16-bit analog-to-digital converter (ADC) based on a continuous time sigma-delta ( $\Sigma$ - $\Delta$ ) architecture that achieves 86 dB of dynamic range over a 10 MHz input bandwidth. The integrated features and characteristics unique to the continuous time  $\Sigma$ - $\Delta$  architecture significantly simplify its use and minimize the need for external components.

The AD9262 has a resistive input impedance that relaxes the requirements of the driver amplifier. In addition, a  $32\times$  oversampled  $5^{th}$ -order continuous time loop filter significantly attenuates out of band signals and aliases, reducing the need for external filters at the input.

An external clock input or the integrated integer-N PLL provides the 640 MHz internal clock needed for the oversampled continuous time  $\Sigma\text{-}\Delta$  modulator. On-chip decimation filters and sample rate converters reduce the modulator data rate from 640 MSPS to a user-defined output data rate between 30 MSPS to 160 MSPS, enabling a more efficient and direct interface.

#### FUNCTIONAL BLOCK DIAGRAM

The digital output data is presented in offset binary, Gray code, or twos complement format. A data clock output (DCO) is provided to ensure proper timing with the receiving logic. The AD9262 has the added feature of interleaving Channel A and Channel B data onto one 16-bit bus, simplifying on-board routing.

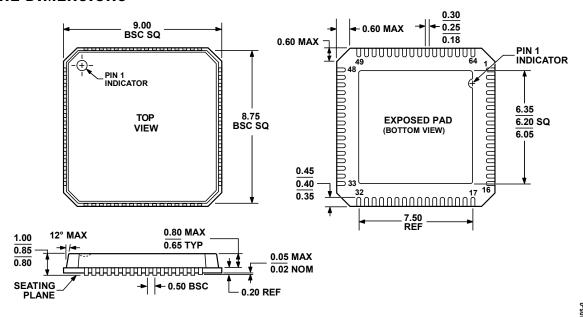

The ADC is available in three different bandwidth options of 2.5 MHz, 5 MHz, and 10 MHz, and operates on a 1.8 V analog supply and a 1.8 V to 3.3 V digital supply, consuming 675 mW. The AD9262 is available in a 64-lead LFCSP and is specified over the industrial temperature range (-40°C to +85°C).

## **PRODUCT HIGHLIGHTS**

- Continuous time Σ-Δ architecture efficiently achieves high dynamic range and wide bandwidth.

- Passive input structure reduces or eliminates the requirements for a driver amplifier.

- 3. An oversampling ratio of 32× and high order loop filter provide excellent alias rejection reducing or eliminating the need for antialiasing filters.

- 4. An integrated decimation filter, sample rate converter, PLL clock multiplier, and voltage reference provide ease of use.

- 5. Operates from a single 1.8 V analog power supply and 1.8 V to 3.3 V output supply.

- 6. A standard serial port interface (SPI) supports various product features and functions.

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-220-VMMD-4

Figure 2. 64-Lead Frame Chip Scale Package [LFCSP\_VQ] 9 mm × 9 mm Body, Very Thin Quad Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                       | Temperature Range | Package Description                              | Package Option |

|-----------------------------|-------------------|--------------------------------------------------|----------------|

| AD9262BCPZ-10 <sup>12</sup> | -40°C to +85°C    | 64-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | TBD            |

| AD9262BCPZ-5 <sup>1,2</sup> | -40°C to +85°C    | 64-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | TBD            |

| AD9262BCPZ <sup>1, 2</sup>  | -40°C to +85°C    | 64-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | TBD            |

| AD9262-10EBZ <sup>1</sup>   |                   | Evaluation Board                                 |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> It is required that the exposed paddle be soldered to the AGND plane to achieve the best electrical and thermal performance.