# 50 dB GSM PA Controller

# AD8315

#### FEATURES

Complete RF detector/controller function >50 dB range at 0.9 GHz (-49 dBm to +2 dBm, re 50 Ω) Accurate scaling from 0.1 GHz to 2.5 GHz Temperature-stable linear-in-dB response Log slope of 23 mV/dB, intercept at -60 dBm at 0.9 GHz True integration function in control loop Low power: 20 mW at 2.7 V, 38 mW at 5 V Power-down to 10.8 μW

#### **APPLICATIONS**

Single, dual, and triple band mobile handset (GSM, DCS, EDGE) Transmitter power control

### **GENERAL DESCRIPTION**

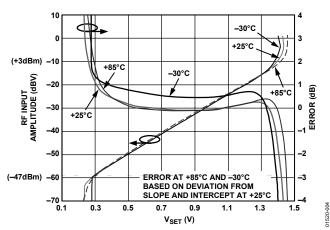

The AD8315 is a complete low cost subsystem for the precise control of RF power amplifiers operating in the frequency range 0.1 GHz to 2.5 GHz and over a typical dynamic range of 50 dB. It is intended for use in cellular handsets and other battery-operated wireless devices. The log amp technique provides a much wider measurement range and better accuracy than controllers using diode detectors. In particular, its temperature stability is excellent over a specified range of  $-30^{\circ}$ C to  $+85^{\circ}$ C.

Its high sensitivity allows control at low signal levels, thus reducing the amount of power that needs to be coupled to the detector.

For convenience, the signal is internally ac-coupled. This high-pass coupling, with a corner at approximately 0.016 GHz, determines the lowest operating frequency. Therefore, the source can be dc grounded.

The AD8315 provides a voltage output, VAPC, that has the voltage range and current drive to directly connect to most handset power amplifiers' gain control pin. VAPC can swing from 250 mV above ground to within 200 mV below the supply voltage. Load currents of up to 6 mA can be supported.

The setpoint control input is applied to the VSET pin and has an operating range of 0.25 V to 1.4 V. The associated circuit determines the slope and intercept of the linear-in-dB measurement system; these are nominally 23 mV/dB and -60 dBm for a 50  $\Omega$  termination (-73 dBV) at 0.9 GHz. Further simplifying the application of the AD8315, the input resistance of the setpoint interface is over 100 M $\Omega$ , and the bias current is typically 0.5  $\mu$ A.

–The AĐ8315-is available in MSOP and LFCSP packages and consumes 8.5 mA from a 2.7 V to 5.5 V supply. When powered down, the sleep current is 4  $\mu$ A.

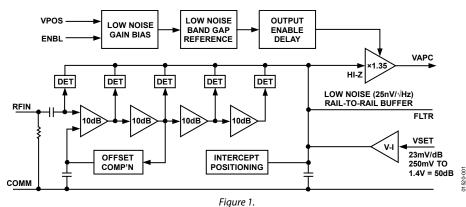

#### FUNCTIONAL BLOCK DIAGRAM

rigure i

Rev. C Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2006 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications1                               |

| General Description                         |

| Functional Block Diagram1                   |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings                    |

|                                             |

| ESD Caution5                                |

| ESD Caution                                 |

|                                             |

| Pin Configuration and Function Descriptions |

| Pin Configuration and Function Descriptions |

| Pin Configuration and Function Descriptions |

|   | Practical Loop                       | . 15 |

|---|--------------------------------------|------|

|   | A Note About Power Equivalency       | . 16 |

|   | Basic Connections                    | . 16 |

|   | Range on VSET and RFIN               | . 17 |

|   | Transient Response                   | . 17 |

|   | Mobile Handset Power Control Example | . 18 |

|   | Enable and Power-On                  | . 19 |

|   | Input Coupling Options               | . 19 |

|   | Using the Chip Scale Package         | . 20 |

|   | Evaluation Board                     | . 20 |

| ( | Dutline Dimensions                   | . 22 |

|   | Ordering Guide                       | . 23 |

### **REVISION HISTORY**

| 6/06—Rev. B to Rev. C     |           |

|---------------------------|-----------|

| Updated Format            | Universal |

| Changes to Ordering Guide |           |

#### 1/03-Rev. 0 to Rev. B

| Edits to Product Description Section | 1 |

|--------------------------------------|---|

| Edit to Functional Block Diagram     | 1 |

| Edits to Specifications              | 2 |

| Edits to Absolute Maximum Ratings    | 3 |

| Ordering Guide Updated               | 3 |

| TPC 9 Replaced with New Figure       | 5 |

| Edits to TPC 27                      | 8 |

| Edit to Figure 1                     | 9 |

| Edit to Figure 3                     |   |

| Edit to Equation 9                   |   |

| Edit to Equation 10                  |   |

|                                      |   |

| Edit to Equation 11                        | 10 |

|--------------------------------------------|----|

| Edits to Example section                   | 10 |

| Edit to Basic Connections Section          | 12 |

| Edits to Input Coupling Options Section    | 14 |

| Table III Becomes Table II                 | 15 |

| Table II Recommended Components Deleted    | 15 |

| Using the Chip-Scale Package Section Added | 15 |

| Edits to Evaluation Board Section          | 15 |

| Figure 12 Title Edited                     | 16 |

| Figure 13 Title Edited                     | 16 |

| 8-Lead Chip Scale Package (CP-8) Added     | 17 |

| Updated Outline Dimensions                 | 17 |

|                                            |    |

10/99—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\text{S}}$  = 2.7 V, T = 25°C, 52.3  $\Omega$  termination on RFIN, unless otherwise noted.

### Table 1.

| Parameter                          | Conditions                                                                                                  | Min  | Тур                    | Max  | Unit   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------------------------|------|--------|

| OVERALL FUNCTION                   |                                                                                                             |      |                        |      |        |

| Frequency Range <sup>1</sup>       | To meet all specifications                                                                                  | 0.1  |                        | 2.5  | GHz    |

| Input Voltage Range                | ±1 dB log conformance, 0.1 GHz                                                                              | -57  |                        | -11  | dBV    |

| Equivalent dBm Range               |                                                                                                             | -44  |                        | +2   | dBm    |

| Logarithmic Slope <sup>2</sup>     | 0.1 GH                                                                                                      | 21.5 | 24                     | 25.5 | mV/dB  |

| Logarithmic Intercept <sup>2</sup> | 0.1 GHz                                                                                                     | -79  | -70                    | -64  | dBV    |

| Equivalent dBm Level               |                                                                                                             | -66  | -57                    | -51  | dBm    |

| RF INPUT INTERFACE                 | Pin RFIN                                                                                                    |      |                        |      |        |

| Input Resistance <sup>3</sup>      | 0.1 GHz                                                                                                     |      | 2.8                    |      | kΩ     |

| Input Capacitance <sup>3</sup>     | 0.1 GHz                                                                                                     |      | 0.9                    |      | pF     |

| OUTPUT                             | Pin VAPC                                                                                                    |      |                        |      |        |

| Minimum Output Voltage             | $V_{\text{SET}} \le 200 \text{ mV}$ , ENBL high                                                             | 0.25 | 0.27                   | 0.3  | V      |

|                                    | ENBL low                                                                                                    |      | 0.02                   |      | V      |

| Maximum Output Voltage             | $R_L \ge 800 \ \Omega$                                                                                      | 2.45 |                        | 2.6  | V      |

| vs. Temperature <sup>4</sup>       | $85^{\circ}$ C, V <sub>POS</sub> = 3 V, I <sub>OUT</sub> = 6 mA                                             | 2.54 |                        |      | V      |

| General Limit                      | $2.7 \text{ V} \leq V_{\text{POS}} \leq 5.5 \text{ V}, \text{ R}_{\text{L}} = \infty$                       |      | V <sub>POS</sub> - 0.1 |      | V      |

| Output Current Drive               | Source/Sink                                                                                                 |      | 5/200                  |      | mA/μA  |

| Output Buffer Noise                |                                                                                                             |      | 25                     |      | nV√Hz  |

| Output Noise                       | RF input = 2 GHz, 0 dBm, $f_{NOISE}$ = 100 kHz, $C_{FLT}$ = 220 pF                                          |      | 130                    |      | nV/√Hz |

| Small Signal Bandwidth             | 0.2 V to 2.6 V swing                                                                                        |      | 30                     |      | MHz    |

| Slew Rate                          | 10% to 90%, 1.2 V step (V <sub>SET</sub> ), open loop <sup>5</sup>                                          |      | 13                     |      | V/µs   |

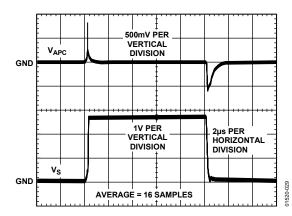

| Response Time                      | FLTR = open, see Figure 26                                                                                  |      | 150                    |      | ns     |

| SETPOINT INTERFACE                 | Pin VSET                                                                                                    |      |                        |      |        |

| Nominal Input Range                | Corresponding to central 50 dB                                                                              | 0.25 |                        | 1.4  | V      |

| Logarithmic Scale Factor           |                                                                                                             |      | 43.5                   |      | dB/V   |

| Input Resistance                   |                                                                                                             |      | 100                    |      | kΩ     |

| Slew Rate                          |                                                                                                             |      | 16                     |      | V/µs   |

| ENABLE INTERFACE                   | Pin ENBL                                                                                                    |      |                        |      |        |

| Logic Level to Enable Power        |                                                                                                             | 1.8  |                        | VPOS | V      |

| Input Current when Enable          |                                                                                                             |      | 20                     |      | μΑ     |

| High                               |                                                                                                             |      |                        |      |        |

| Logic Level to Disable Power       |                                                                                                             |      |                        | 0.8  | V      |

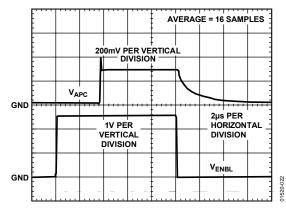

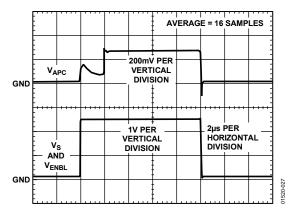

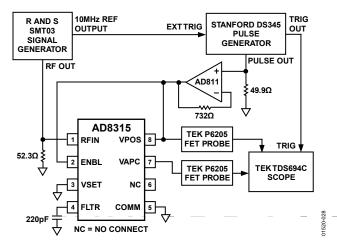

| Enable Time                        | Time from ENBL high to $V_{APC}$ within 1% of final value,<br>$V_{SET} \le 200$ mV, refer to Figure 23      |      | 4                      | 5    | μs     |

| Disable Time                       | Time from ENBL low to $V_{APC}$ within 1% of final value,<br>$V_{SET} \le 200$ mV, refer to Figure 23       |      | 8                      | 9    | μs     |

| Power-On/Enable Time               | Time from VPOS/ENBL high to $V_{APC}$ within 1% of final value,<br>$V_{SET} \le 200$ mV, refer to Figure 28 |      | 2                      | 3    | μs     |

|                                    | Time from VPOS/ENBL low to $V_{APC}$ within 1% of final value,<br>$V_{SET} \le 200$ mV, refer to Figure 28  |      | 100                    | 200  | ns     |

| Parameter                    | Conditions                                | Mi  | n Ty | o Max | Unit |

|------------------------------|-------------------------------------------|-----|------|-------|------|

| POWER INTERFACE              | Pin VPOS                                  |     |      |       |      |

| Supply Voltage               |                                           | 2.7 | ,    | 5.5   | V    |

| Quiescent Current            | ENBL high                                 |     | 8.5  | 10.7  | mA   |

| Over Temperature             | $-30^{\circ}C \le T_{A} \le +85^{\circ}C$ |     |      | 12.9  | mA   |

| Disable Current <sup>6</sup> | ENBL low                                  |     | 4    | 10    | μΑ   |

| Over Temperature             | $-30^{\circ}C \le T_A \le +85^{\circ}C$   |     |      | 13    | μΑ   |

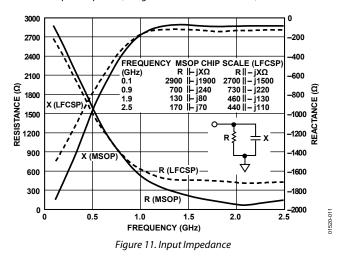

<sup>1</sup> Operation down to 0.02 GHz is possible.

<sup>2</sup> Mean and standard deviation specifications are available in Table 2

<sup>3</sup> See Figure 11 for plot of input impedance vs. frequency.

<sup>4</sup> This parameter is guaranteed but not tested in production. Limit is –3 sigma from the mean.

<sup>5</sup> Response time in a closed-loop system depends on the filter capacitor (C<sub>FLT</sub>) used and the response of the variable gain element.

<sup>6</sup> This parameter is guaranteed but not tested in production. Maximum specified limit on this parameter is the 6 sigma value.

#### Table 2. Typical Specifications at Selected Frequencies at 25°C (Mean and Sigma)

|                 |          |       |           |       |       | ±1 dB D     | ynamic Rang | e           |

|-----------------|----------|-------|-----------|-------|-------|-------------|-------------|-------------|

|                 | Slope (m | V/dB) | Intercept | (dBV) | Low   | Point (dBV) | High        | Point (dBV) |

| Frequency (GHz) | Mean     | Sigma | Mean      | Sigma | Mean  | Sigma       | Mean        | Sigma       |

| 0.1             | 23.8     | 0.3   | -70.1     | 1.8   | -57.7 | 1.3         | -10.6       | 0.8         |

| 0.9             | 23.2     | 0.4   | -72.6     | 1.8   | -61.0 | 1.3         | -11.2       | 0.8         |

| 1.9             | 22.2     | 0.3   | -73.8     | 1.6   | -62.9 | 0.9         | -18.5       | 1.7         |

| 2.5             | 22.3     | 0.4   | -75.6     | 1.5   | -64.0 | 1.1         | -20.0       | 1.7         |

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 14010 5.                                   |                       |

|--------------------------------------------|-----------------------|

| Parameter                                  | Rating                |

| Supply Voltage VPOS                        | 5.5 V                 |

| Temporary Overvoltage VPOS                 |                       |

| (100 cycles, 2 sec duration, ENBL Low)     | 6.3 V                 |

| VAPC, VSET, ENBL                           | 0 V, V <sub>POS</sub> |

| RFIN                                       | 17 dBm                |

| Equivalent Voltage                         | 1.6 V rms             |

| Internal Power Dissipation                 | 60 mW                 |

| θ <sub>JA</sub> (MSOP)                     | 200°C/W               |

| θ <sub>JA</sub> (LFCSP, Paddle Soldered)   | 80°C/W                |

| $\theta_{JA}$ (LFCSP, Paddle Not Soldered) | 200°C/W               |

| Maximum Junction Temperature               | 125°C                 |

| Operating Temperature Range                | -40°C to +85°C        |

| Storage Temperature Range                  | –65°C to +150°C       |

| Lead Temperature (Soldering 60 sec)        |                       |

| MSOP                                       | 300°C                 |

| LFCSP                                      | 240°C                 |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can\_discharge without\_detection. Although this product features\_proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

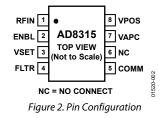

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### Table 4. Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                  |

|---------|----------|------------------------------------------------------------------------------|

| 1       | RFIN     | RF Input.                                                                    |

| 2       | ENBL     | Connect to VPOS for Normal Operation Connect Pin to Ground for Disable Mode. |

| 3       | VSET     | Setpoint Input. Nominal input range 0.25 V to 1.4 V.                         |

| 4       | FLTR     | Integrator Capacitor. Connect between FLTR and COMM.                         |

| 5       | COMM     | Device Common (Ground).                                                      |

| 6       | NC       | No Connection.                                                               |

| 7       | VAPC     | Output. Control voltage for gain control element.                            |

| 8       | VPOS     | Positive Supply Voltage: 2.7 V to 5.5 V.                                     |

# TYPICAL PERFORMANCE CHARACTERISTICS

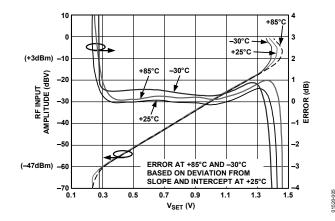

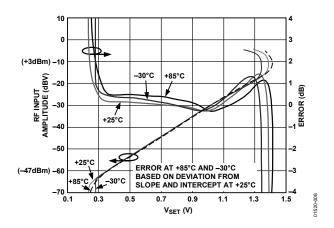

Figure 4. Input Amplitude and Log Conformance vs. VSET at 0.1 GHz

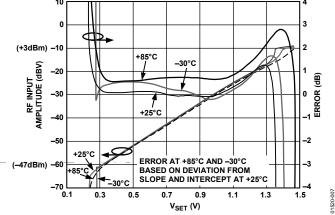

Figure 5. Input Amplitude and Log Conformance vs. VSET at 0.9 GHz

Figure 8. Input Amplitude and Log Conformance vs. V<sub>SET</sub> at 2.5 GHz

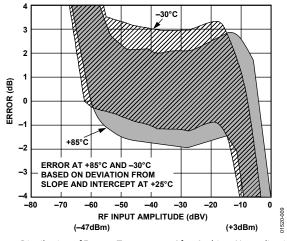

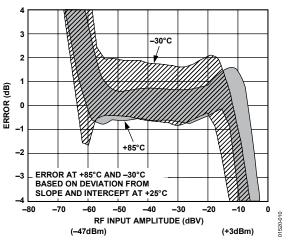

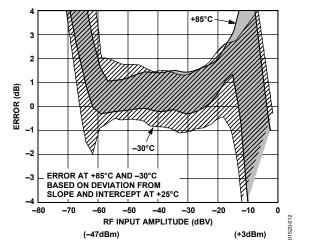

Figure 9. Distribution of Error at Temperature After Ambient Normalization vs. Input Amplitude, 3 Sigma to Either Side of Mean, 0.1 GHz

Figure 10. Distribution of Error at Temperature After Ambient Normalization vs. Input Amplitude, 3 Sigma to Either Side of Mean, 0.9 GHz

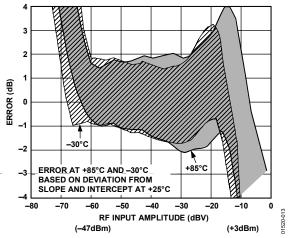

Figure 12. Distribution of Error at Temperature After Ambient Normalization vs. Input Amplitude, 3 Sigma to Either Side of Mean, 1.9 GHz

Figure 13. Distribution of Error at Temperature After Ambient Normalization vs. Input Amplitude, 3 Sigma to Either Side of Mean, 2.5 GHz

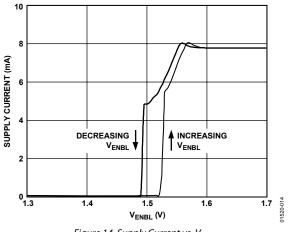

Figure 14. Supply Current vs. VENBL

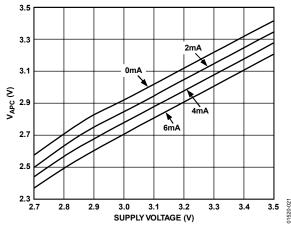

Figure 21. Maximum VAPC Voltage vs. Supply Voltage by Load Current

Figure 22. ENBL Response Time

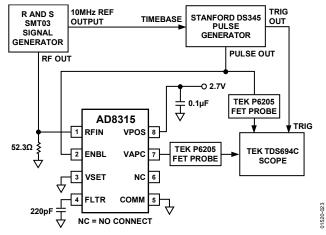

Figure 23. Test Setup for ENBL Response Time

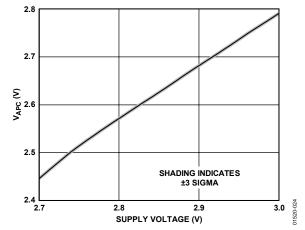

Figure 24. Maximum VAPC Voltage vs. Supply Voltage with 4 mA Load Current

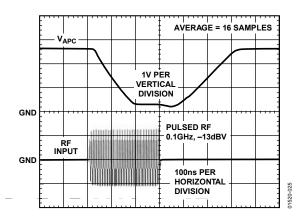

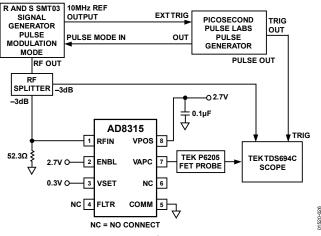

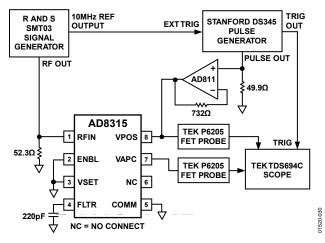

Figure 25. VAPC Response Time, Full-Scale Amplitude Change, Open-Loop

Figure 26. Test Setup for VAPC Response Time

Figure 27. Power-On and Power-Off Response with VSET Grounded

Figure 28. Test Setup for Power-On and Power-Off Response with VSET Grounded

Figure 29. Power-On and Power-Off Response with VSET and ENBL Grounded

Figure 30. Test Setup for Power-On and Power-Off Response with VSET and ENBL Grounded

### THEORY OF OPERATION

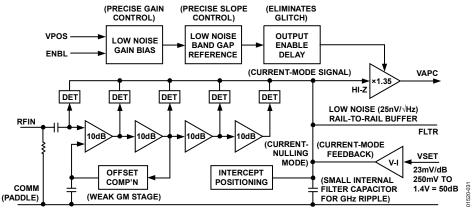

The AD8315 is a wideband logarithmic amplifier (log amp) similar in design to the AD8313 and AD8314. However, it is strictly optimized for use in power control applications rather than as a measurement device. Figure 31 shows the main features in block schematic form. The output (Pin 7, VAPC) is intended to be applied directly to the automatic power-control (APC) pin of a power amplifier module.

### **BASIC THEORY**

Logarithmic amplifiers provide a type of compression in which a signal having a large range of amplitudes is converted to one of smaller range. The use of the logarithmic function uniquely results in the output representing the decibel value of the input. The fundamental mathematical form is:

$$V_{OUT} = V_{SLP} \log_{10} \frac{V_{IN}}{V_Z}$$

(1)

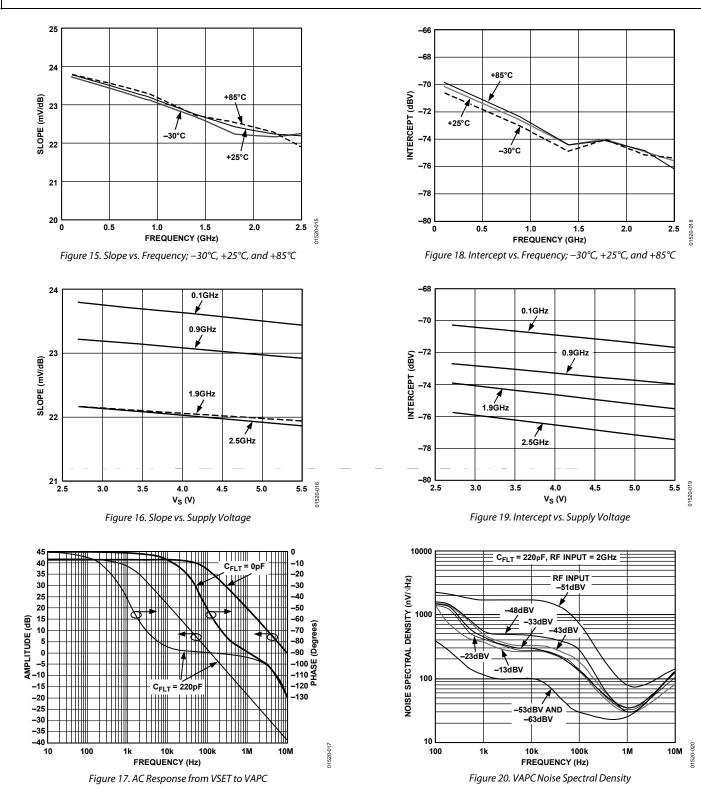

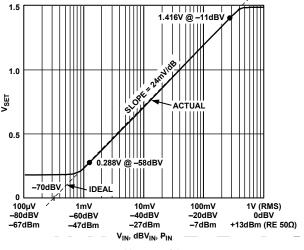

Here  $V_{IN}$  is the input voltage,  $V_Z$  is called the intercept (voltage) because when  $V_{IN} = V_Z$  the argument of the logarithm is unity and thus the result is zero, and  $V_{SLP}$  is called the slope (voltage), which is the amount by which the output changes for a certain change in the ratio ( $V_{IN}/V_Z$ ). When BASE-10 logarithms are used, denoted by the function log<sub>10</sub>,  $V_{SLP}$  represents the volts/ decade, and since a decade corresponds to 20 dB,  $V_{SLP}/20$ represents the volts/dB. For the AD8315, a nominal (low frequency) slope of 24 mV/dB was chosen, and the intercept  $V_Z$  – was placed at the equivalent of -70 dBV for a sine wave input (316  $\mu$ V rms). This corresponds to a power level of -57 dBm when the net resistive part of the input impedance of the log amp is 50  $\Omega$ . However, both the slope and the intercept are dependent on frequency (see Figure 15 and Figure 18).

Keeping in mind that log amps do not respond to power but only to voltages and that the calibration of the intercept is waveform dependent and is only quoted for a sine wave signal, the equivalent power response can be written as

$$V_{OUT} = V_{DB} \left( P_{IN} - P_Z \right) \tag{2}$$

where:

$P_{IN}$ , the input power, and  $P_Z$ , the equivalent intercept, are both expressed in dBm (thus, the quantity in parentheses is simply a number of decibels).

$V_{DB}$  is the slope expressed as so many mV/dB.

For a log amp having a slope  $V_{DB}$  of 24 mV/dB and an intercept at -57 dBm, the output voltage for an input power of -30 dBm is 0.024 [-30 - (-57)] = 0.648 V.

Further details about the structure and function of log amps can be found in data sheets for other log amps produced by Analog Devices, Inc. Refer to the AD640 data sheet and AD8307 data sheet, both of which include a detailed discussion of the basic principles of operation and explain why the intercept depends on waveform, an important consideration when complex modulation is imposed on an RF carrier.

Figure 31. Block Schematic

The intercept need not correspond to a physically realizable part of the signal range for the log amp. Therefore, the specified intercept is -70 dBV, at 0.1 GHz, whereas the smallest input for accurate measurement (a +1 dB error, see Table 2) at this frequency is higher, being about -58 dBV. At 2.5 GHz, the +1 dB error point shifts to -64 dBV. This positioning of the intercept is deliberate and ensures that the V<sub>SET</sub> voltage is within the capabilities of certain DACs, whose outputs cannot swing below 200 mV. Figure 32 shows the 100 MHz response of the AD8315; the vertical axis does not represent the output (at pin VAPC) but the value required at the power control pin, VSET, to null the control loop.

Figure 32. Basic Calibration of the AD8315 at 0.1 GHz

#### **CONTROLLER-MODE LOG AMPS**

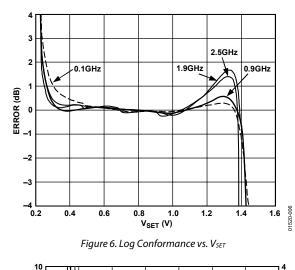

The AD8315 combines the two key functions required for the measurement and control of the power level over a moderately wide dynamic range. First, it provides the amplification needed to respond to small signals in a chain of four amplifier/limiter cells (see Figure 31), each having a small signal gain of 10 dB and a bandwidth of approximately 3.5 GHz. At the output of each of these amplifier stages is a full-wave rectifier, essentially a square law detector cell that converts the RF signal voltages to a fluctuating current having an average value that increases with signal level. A further passive detector stage is added before the first stage. These five detectors are separated by 10 dB, spanning some 50 dB of dynamic range. Their outputs are each in the form of a differential current, making summation a simple matter. It is readily shown that the summed output can closely approximate a logarithmic function. The overall accuracy at the extremes of this total range, viewed as the deviation from an ideal logarithmic response, that is, the log conformance error, can be judged by referring to Figure 6, which shows that errors across the central 40 dB are moderate. Other performance curves show how conformance to an ideal logarithmic function varies with supply voltage, temperature, and frequency.

In a device intended for measurement applications, this current would then be converted to an equivalent voltage, to provide the log ( $V_{IN}$ ) function shown in Equation 1. However, the design of the AD8315 differs from standard practice in that its output needs to be a low noise control voltage for an RF power amplifier not a direct measure of the input level. Furthermore, it is highly desirable that this voltage be proportional to the time integral of the error between the actual input  $V_{IN}$  and the dc voltage  $V_{SET}$  (applied to Pin 3, VSET) that defines the setpoint, that is, a target value for the power level, typically generated by a DAC.

This is achieved by converting the difference between the sum of the detector outputs (still in current form) and an internally generated current proportional to V<sub>SET</sub> to a single-sided, current-mode signal. This, in turn, is converted to a voltage (at Pin 4, FLTR, the low-pass filter capacitor node) to provide a close approximation to an exact integration of the error between the power present in the termination at the input of the AD8315 and the setpoint voltage. Finally, the voltage developed across the ground-referenced filter capacitor C<sub>FLT</sub> is buffered by a special low noise amplifier of low voltage gain (×1.35) and presented at Pin 7 (VAPC) for use as the control voltage for the RF power amplifier. This buffer can provide rail-to-rail swings and can drive a substantial load current, including large capacitors. Note that the RF power amplifier is assumed to have a positive slope with RF power increasing monotonically with an increasing APC control voltage.

### CONTROL LOOP DYNAMICS

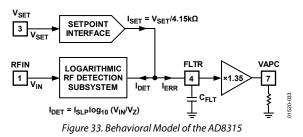

To understand how the AD8315 behaves in a complete control loop, an expression for the current in the integration capacitor as a function of the input  $V_{IN}$  and the setpoint voltage  $V_{SET}$  must be developed (see Figure 33).

First, the summed detector currents are written as a function of the input

$$I_{DET} = I_{SLP} \log_{10} \left( V_{IN} / V_Z \right) \tag{3}$$

where:

*I*<sub>DET</sub> is the partially filtered demodulated signal, whose exact average value is extracted through the subsequent integration step.

$I_{SLP}$  is the current-mode slope and has a value of 115  $\mu A$  per decade (that is, 5.75  $\mu A/dB).$

$V_{IN}$  is the input in V rms.

$V_Z$  is the effective intercept voltage, which, as previously noted, is dependent on waveform but is 316  $\mu V$  rms (–70 dBV) for a sine wave input.

Now the current generated by the setpoint interface is simply

$$I_{SET(4)} = V_{SET}/415 \text{ k}\Omega \tag{4}$$

The difference between this current and  $I_{DET}$  is applied to the loop filter capacitor  $C_{FLT}$ . It follows that the voltage appearing on this capacitor,  $V_{FLT}$ , is the time integral of the difference current:

$$V_{FLT}(s) = (I_{SET} - I_{DET})/sC_{FLT}$$

(5)

$$=\frac{V_{SET}/4.15 \text{ k}\Omega - I_{SLP} \log_{10} (V_{IN}/V_Z)}{sC_{FLT}}$$

(6)

The control output V<sub>APC</sub> is slightly greater than this, because the gain of the output buffer is ×1.35. In addition, an offset voltage is deliberately introduced in this stage; this is inconsequential because the integration function implicitly allows for an arbitrary constant to be added to the form of Equation 6. The polarity is such that VAPC rises to its maximum value for any value of V<sub>SET</sub> greater than the equivalent value of V<sub>IN</sub>. In practice, the  $V_{APC}$  output rails to the positive supply under this condition unless the control loop through the power amplifier is present. In other words, the AD8315 seeks to drive the RF power to its maximum value whenever it falls below the setpoint. The use of exact integration results in a final error that is theoretically 0, and the logarithmic detection law would ideally result in a constant response time following a step change of either the setpoint or the power level, if the poweramplifier control function were likewise linear in dB. However, this latter condition is rarely true, and it follows that in practice, the loop response time depends on the power level, and this effect can strongly influence the design of the control loop.

Equation 6 can be restated as

$$V_{APC}(s) = \frac{V_{SET} - V_{SLP} \log_{10} \left( V_{IN} / V_Z \right)}{sT}$$

(7)

where  $V_{SLP}$  is the volts-per-decade slope from Equation 1, having a value of 480 mV/decade, and *T* is an effective time constant for the integration, being equal to 4.15 k $\Omega \times C_{FLT}/1.35$ ; the resistor value comes from the setpoint interface scaling Equation 4 and the factor 1.35 arises because of the voltage gain of the buffer. Therefore, the integration time constant can be written as

$$T = 3.07 C_{FLT}$$

in  $\mu$ s, when C is expressed in nF (8)

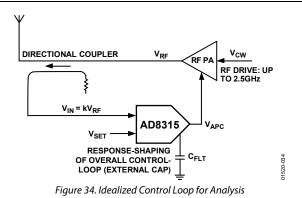

To simplify our understanding of the control loop dynamics, begin by assuming that the power amplifier gain function is actually linear in dB, and for the moment, use voltages to express the signals at the power amplifier input and output. Let the RF output voltage be  $V_{PA}$  and let its input be  $V_{CW}$ . Furthermore, to characterize the gain control function, this form is used

$$V_{PA} = G_{O} V_{CW} 10^{(V_{APC}/V_{GBC})}$$

(9)

where:

$G_0$  is the gain of the power amplifier when  $V_{APC} = 0$ .

$V_{GBC}$  is the gain scaling.

While few-amplifiers conform so conveniently to this law, it provides a clearer starting point for understanding the more complex situation that arises when the gain control law is less ideal.

This idealized control loop is shown in Figure 34. With some manipulation, it is found that the characteristic equation of this system is

$$V_{APC}(s) = \frac{(V_{SET} \ V_{GBC})/V_{SLP} - V_{GBC} \ \log_{10}(kG_{O} \ V_{CW}/V_{Z})}{1 + sT_{O}}$$

(10)

where:

*k* is the coupling factor from the output of the power amplifier to the input of the AD8315 (for example,  $\times 0.1$  for a 20 dB coupler).

$T_{O}$  is a modified time constant (V<sub>GBC</sub>/V<sub>SLP</sub>)T.

This is quite easy to interpret. First, it shows that a system of this sort exhibits a simple single-pole response, for any power level, with the customary exponential time domain form for either increasing or decreasing step polarities in the demand level  $V_{\text{SET}}$  or the carrier input  $V_{\text{CW}}$ . Second, it reveals that the final value of the control voltage  $V_{\text{APC}}$  is determined by several fixed factors:

$$V_{APC}\left(\tau = \infty\right) = \left(V_{SET} V_{GBC}\right) / V_{SLP} - \log_{10}\left(kG_O V_{CW} / V_Z\right) (11)$$

#### Example

Assume that the gain magnitude of the power amplifier runs from a minimum value of ×0.316 (-10 dB) at  $V_{APC}$  = 0 to ×100 (40 dB) at  $V_{APC}$  = 2.5 V. Applying Equation 9, G<sub>0</sub> = 0.316 and  $V_{GBC}$  = 1 V. Using a coupling factor of k = 0.0316 (that is, a 30 dB directional coupler) and recalling that the nominal value of  $V_{SLP}$  is 480 mV and  $V_Z$  = 316 µV for the AD8315, first calculate the range of values needed for  $V_{SET}$  to control an output range of +33 dBm to -17 dBm. This can be found by noting that, in the steady state, the numerator of Equation 7 must be 0, that is:

$$V_{SET} = V_{SLP} \log_{10} \left( k V_{PA} / V_Z \right) \tag{12}$$

where  $V_{IN}$  is expanded to  $kV_{PA}$ , the fractional voltage sample of the power amplifier output. For 33 dBm,  $V_{PA} = 10$  V rms, which evaluates to

$$V_{SET}(max) = 0.48 \log_{10} (316 \text{ mV}/316 \mu\text{V}) = 1.44 \text{ V}$$

(13)

For a delivered power of -17 dBm,  $V_{PA} = 31.6$  mV rms

$$V_{SET}(min) = 0.48 \log_{10} (1 \text{ mV}/316 \,\mu\text{V}) = 0.24 \text{ V}$$

(14)

Check that the power range is 50 dB, which should correspond to a voltage change in  $V_{SET}$  of 50 dB × 24 mV/dB = 1.2 V, which agrees.

Now, the value of  $V_{APC}$  is of interest, although it is a dependent parameter, inside the loop. It depends on the characteristics of the power amplifier, and the value of the carrier amplitude  $V_{CW}$ . Using the control values previously derived, that is,  $G_0 = 0.316$  and  $V_{GBC} = 1$  V, and assuming the applied power is fixed at -7 dBm (so  $V_{CW} = 100$  mV rms), the following is true using Equation 11

$$V_{APC}(max) = (V_{SET}V_{GBC})/V_{SLP} - \log_{10} kG_0 V_{CW}/V_Z$$

= (1.44 × 1)/0.48 - log<sub>10</sub>(0.0316 × 0.316 × 0.1/316 µV)

= 3.0 - 0.5 = 2.5 V (15)

$$V_{APC}(min) = (V_{SET}V_{GBC})/V_{SLP} - \log_{10} kG_0 V_{CW}/V_Z$$

= (0.24 × 1)/0.48 - log<sub>10</sub>(0.0316 × 0.316 × 0.1/316 µV)

= 0.5 - 0.5 = 0 (16)

both of which results are consistent with the assumptions made about the amplifier control function. Note that the second term is independent of the delivered power and a fixed function of the drive power.

Finally, using the loop time constant for these parameters and an illustrative value of 2 nF for the filter capacitor  $C_{\text{FLT}}$

$$T_{O} = (V_{GBC}/V_{SLP}) T$$

= (1/0.48)3.07 µs × 2 (nF) = 12.8 µs (17)

#### PRACTICAL LOOP

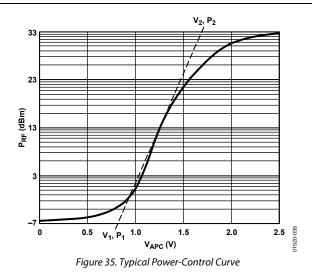

At present time, power amplifiers, or VGAs preceding such amplifiers, do not provide an exponential gain characteristic. It follows that the loop dynamics (the effective time constant) varies with the setpoint because the exponential function is unique in providing constant dynamics. The procedure must therefore be as follows. Beginning with the curve usually provided for the power output vs. the APC voltage, draw a tangent at the point on this curve where the slope is highest (see Figure 35). Using this line, calculate the effective minimum value of the variable  $V_{GBC}$  and use it in Equation 17 to determine the time constant. Note that the minimum in  $V_{GBC}$  corresponds to the maximum rate of change in the output power vs.  $V_{APC}$ .

For example, suppose it is found that, for a given drive power, the amplifier generates an output power of  $P_1$  at  $V_{APC} = V_1$  and  $P_2$  at  $V_{APC} = V_2$ . Then, it is readily shown that

$$V_{GBC} = 20 (V_2 - V_1) / (P_2 - P_1)$$

(18)

This should be used to calculate the filter capacitance. The response time at high and low power levels (on the shoulders of the curve shown in Figure 35) is slower. Note also that it is sometimes useful to add a 0 in the closed-loop response by placing a resistor in series with C<sub>FLT</sub>. For more information on this, see the Transient Response section.

### A NOTE ABOUT POWER EQUIVALENCY

In using the AD8315, it must be understood that log amps do not fundamentally respond to power. It is for this reason that dBV (decibels above 1 V rms) are used rather than the commonly used metric of dBm. The dBV scaling is fixed, independent of termination impedance, while the corresponding power level is not. For example, 224 mV rms is always -13 dBV (with one further condition of an assumed sinusoidal waveform; see the AD640 data sheet for more information about the effect of waveform on logarithmic intercept), and this corresponds to a power of 0 dBm when the net impedance at the input is 50  $\Omega$ . When this impedance is altered to 200  $\Omega$ , however, the same voltage corresponds to a power level that is four times smaller  $(P = V^2/R)$  or -6 dBm. A dBV level can be converted to dBm in the special case of a 50  $\Omega$  system and a sinusoidal signal by simply adding 13 dB (0 dBV is then, and only then, equivalent to 13 dBm).

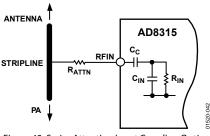

Therefore, the external termination added ahead of the AD8315 determines the effective power scaling. This often takes the form of a simple resistor (52.3  $\Omega$  provides a net 50  $\Omega$  input), but more elaborate matching networks can be used. The choice of impedance determines the logarithmic intercept, that is, the input power for which the  $V_{\text{SET}}$  vs.  $P_{\text{IN}}$  function would cross the baseline if that relationship were continuous for all values of V<sub>IN</sub>. This is never the case for a practical log amp; the intercept (so many dBV) refers to the value obtained by the minimum error straight line fit to the actual graph of  $V_{\text{SET}}$  vs.  $P_{\text{IN}}$  (more generally,  $V_{IN}$ ). Where the modulation is complex, as in CDMA, the calibration of the power response needs to be adjusted; the intercept remains stable for any given arbitrary waveform. When a true power (waveform independent) response is needed, a mean-responding detector, such as the AD8361, should be considered.

The logarithmic slope,  $V_{SLP}$  in Equation 1, which is the amount by which the setpoint voltage needs to be changed for each decibel of input change (voltage or power), is, in principle, independent of waveform or termination impedance. In practice, it usually falls off somewhat at higher frequencies, due to the declining gain of the amplifier stages and other effects in the detector cells (see Figure 15).

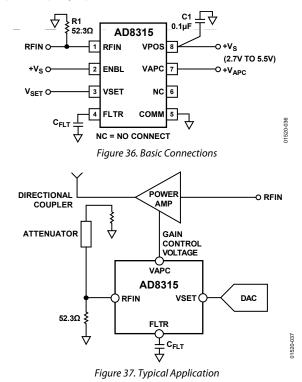

### **BASIC CONNECTIONS**

Figure 36 shows the basic connections for operating the AD8315, and Figure 37 shows a block diagram of a typical application. The AD8315 is typically used in the RF power control loop of a mobile handset.

A supply voltage of 2.7 V to 5.5 V is required for the AD8315. The supply to the VPOS pin should be decoupled with a low inductance 0.1  $\mu$ F surface-mount ceramic capacitor, close to the device. The AD8315 has an internal input coupling capacitor. This negates the need for external ac coupling. This capacitor, along with the low frequency input impedance of the device of approximately 2.8 k $\Omega$ , sets the minimum usable input frequency to around 0.016 GHz. A broadband 50  $\Omega$  input match is achieved in this example by connecting a 52.3  $\Omega$  resistor between RFIN and ground. A plot of input impedance vs. frequency is shown in Figure 11. Other coupling methods are also possible (see Input Coupling Options section).

In a power control loop, the AD8315 provides both the detector and controller functions. A sample of the power amplifier's (PA) output power is coupled to the RF input of the AD8315, usually via a directional coupler. In dual-mode applications, where there are two PAs and two directional couplers, the outputs of the directional couplers can be passively combined (both PAs will never be turned on simultaneously) before being applied to the AD8315.

A setpoint voltage is applied to VSET from the controlling source (generally, this is a DAC). Any imbalance between the RF input level and the level corresponding to the setpoint voltage is corrected by the AD8315's VAPC output that drives the gain control terminal of the PA. This restores a balance between the actual power level sensed at the input of the AD8315 and the value determined by the setpoint. This assumes that the gain control sense of the variable gain element is positive, that is, an increasing voltage from VAPC tends to increase gain.

$V_{APC}$  can swing from 250 mV to within 100 mV of the supply rail and can source up to 6 mA. If the control input of the PA needs to source current, a suitable load resistor can be connected between VAPC and COMM. The output swing and current sourcing capability of VAPC is shown in Figure 21.

### **RANGE ON VSET AND RFIN**

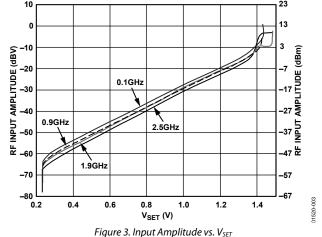

The relationship between the RF input level and the setpoint voltage follows from the nominal transfer function of the device (see Figure 4, Figure 5, Figure 7, and Figure 8). At 0.9 GHz, for example, a voltage of 1 V on VSET indicates a demand for -30 dBV (-17 dBm, re 50  $\Omega$ ) at RFIN. The corresponding power level at the output of the power amplifier is greater than this amount due to the attenuation through the directional coupler.

For setpoint voltages of less than approximately 250 mV,  $V_{APC}$  remains unconditionally at its minimum level of approximately 250 mV. This feature can be used to prevent any spurious emissions during power-up and power-down phases.

Above 250 mV,  $V_{SET}$  has a linear control range up to 1.4 V, corresponding to a dynamic range of 50 dB. This results in a slope of 23 mV/dB or approximately 43.5 dB/V.

### TRANSIENT RESPONSE

The time domain response of power amplifier control loops, using any kind of controller, is only partially determined by the choice of filter, which, in the case of the AD8315, has a true integrator form 1/sT, as shown in Equation 7, with a time constant given by Equation 8. The large signal step response is also strongly dependent on the form of the gain-control law. Nevertheless, some simple rules can be applied. When the filter capacitor C<sub>FLT</sub> is very large, it dominates the time domain response, but the incremental bandwidth of this loop still varies as VAPC traverses the nonlinear gain-control function of the PA, as shown in Figure 35. This bandwidth is highest at the point where the slope of the tangent drawn on this curve is greatest, that is, for power outputs near the center of the PA's range, and is much reduced at both the minimum and the maximum power levels, where the slope of the gain control curve is lowest due to its S-shaped form.

Using smaller values of  $C_{FLT}$ , the loop bandwidth generally increases in inverse proportion to its value. Eventually, however, a secondary effect appears due to the inherent phase lag in the power amplifier's control path, some of which can be due to parasitic or deliberately added capacitance at the VAPC pin. This results in the characteristic poles in the ac loop equation moving off the real axis and thus becoming complex (and somewhat resonant). This is a classic aspect of control loop design. The lowest permissible value of  $C_{FLT}$  needs to be determined experimentally for a particular amplifier. For GSM and DCS power amplifiers,  $C_{FLT}$  typically ranges from 150 pF to 300 pF.

In many cases, some improvement in the worst-case response time can be achieved by including a small resistance in series with  $C_{FLT}$ ; this generates an additional 0 in the closed-loop transfer function, that serves to cancel some of the higher order poles in the overall loop. A combination of main capacitor  $C_{FLT}$ shunted by a second capacitor and resistor in series is also useful in minimizing the settling time of the loop.

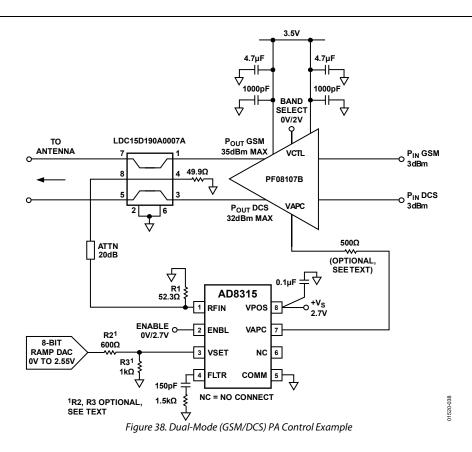

#### **MOBILE HANDSET POWER CONTROL EXAMPLE**

Figure 38 shows a complete power amplifier control circuit for a dual-mode handset. The PF08107B (Hitachi), a dual mode (GSM, DCS) PA, is driven by a nominal power level of 3 dBm. The PA has a single gain control line; the band to be used is selected by applying either 0 V or 2 V to the PA's VCTL input.

Some of the output power from the PA is coupled off using a dual-band directional coupler (Murata LDC15D190A0007A). This has a coupling factor of approximately 19 dB for the GSM band and 14 dB for DCS and an insertion loss of 0.38 dB and 0.45 dB, respectively. Because the PF08107B transmits a maximum power level of 35 dBm for GSM and 32 dBm for DCS, additional attenuation of 20 dB is required before the coupled signal is applied to the AD8315. This results in peak input levels to the AD8315 of -4 dBm (GSM) and -2 dBm (DCS). While the AD8315 gives a linear response for input levels up to 2 dBm, for highly temperature-stable performance at maximum PA output power, the maximum input level should be limited to approximately -2 dBm (see Figure 5 and Figure 7). This does, however, reduce the sensitivity of the circuit at the low end.

The operational setpoint voltage, in the range 250 mV to 1.4 V, is applied to the VSET pin of the AD8315. This is typically supplied by a DAC. The AD8315's VAPC output drives the level control pin of the power amplifier directly.  $V_{APC}$  reaches a maximum value of approximately 2.5 V on a 2.7 V supply while delivering the 3 mA required by the level control input of the PA. This is more than sufficient to exercise the gain control range of the PA.

During initialization and completion of the transmit sequence,  $V_{\text{APC}}$  should be held at its minimum level of 250 mV by keeping  $V_{\text{SET}}$  below 200 mV.

In this example,  $V_{SET}$  is supplied by an 8-bit DAC that has an output range from 0 V to 2.55 V or 10 mV per bit. This sets the control resolution of VSET to 0.4 dB/bit (0.04 dB/mV times 10 mV). If finer resolution is required, the DAC's output voltage can be scaled using two resistors, as shown in Figure 38. This converts the DAC's maximum voltage of 2.55 V down to 1.6 V and increases the control resolution to 0.25 dB/bit.

A filter capacitor ( $C_{FLT}$ ) must be used to stabilize the loop. The choice of  $C_{FLT}$  depends to a large degree on the gain control dynamics of the power amplifier, something that is frequently poorly characterized, so some trial and error can be necessary.

In this example, a 150 pF capacitor is used and a 1.5 k $\Omega$  series resistor is included. This adds a zero to the control loop and

increases the phase margin, which helps to make the step response of the circuit more stable when the PA output power is low and the slope of the PA's power control function is the steepest.

A smaller filter capacitor can be used by inserting a series resistor between VAPC and the control input of the PA. A series resistor works with the input impedance of the PA to create a resistor divider and reduces the loop gain. The size of the resistor divider ratio depends upon the available output swing of  $V_{APC}$  and the required control voltage on the PA.

This technique can also be used to limit the control voltage in situations where the PA cannot deliver the power level being demanded by VAPC. Overdrive of the control input of some PAs causes increased distortion. It should be noted, however, that if the control loop opens (that is, V<sub>APC</sub> goes to its maximum value in an effort to balance the loop), the quiescent current of the AD8315 increases somewhat, particularly at supply voltages greater than 3 V.

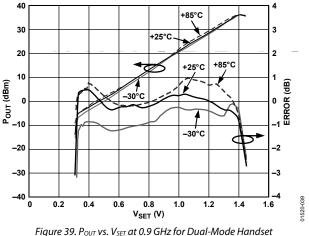

Figure 39 shows the relationship between  $V_{\text{SET}}$  and output power ( $P_{\text{OUT}}$ ) at 0.9 GHz . The overall gain control function is linear in dB for a dynamic range of over 40 dB. Note that for  $V_{\text{SET}}$  voltages below 300 mV, the output power drops off steeply as  $V_{\text{APC}}$  drops toward its minimum level of 250 mV.

Power Amplifier Application, –30°C, +25°C, and +85°C

### **ENABLE AND POWER-ON**

The AD8315 can be disabled by pulling the ENBL pin to ground. This reduces the supply current from its nominal level of 7.4 mA to 4  $\mu$ A. The logic threshold for turning on the device is at 1.5 V with 2.7 V supply voltage. A plot of the enable glitch is shown in Figure 22. Alternatively, the device can be completely disabled by pulling the supply voltage to ground. To minimize glitch in this mode, ENBL and VPOS should be tied together. If VPOS is applied before the device is enabled, a narrow 750 mV glitch results (see Figure 29).

In both situations, the voltage on VSET should be kept below 200 mV during power-on and power-off to prevent any unwanted transients on VAPC.

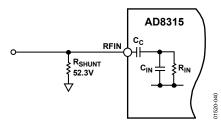

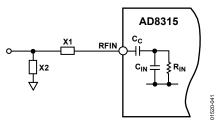

### INPUT COUPLING OPTIONS

The internal 5 pF coupling capacitor of the AD8315, along with the low frequency input impedance of 2.8 k $\Omega$ , give a high-pass input corner frequency of approximately 16 MHz. This sets the minimum operating frequency. Figure 40, Figure 41, and Figure 42 show three options for input coupling. A broadband resistive match can be implemented by connecting a shunt resistor to ground at RFIN (see Figure 40). This 52.3  $\Omega$  resistor (other values can also be used to select different overall input impedances) combines with the input impedance of the AD8315 to give a broadband input impedance of 50  $\Omega$ . While the input resistance and capacitance (C<sub>IN</sub> and R<sub>IN</sub>) of the AD8315 varies from device to device by approximately  $\pm 20\%$ , and over frequency (see Figure 11), the dominance of the external shunt resistor means that the variation in the overall input impedance is close to the tolerance of the external resistor. This method of matching is most useful in wideband applications or in multiband systems where there is more than one operating frequency.

A reactive match can also be implemented as shown in Figure 41. This is not recommended at low frequencies as device tolerances dramatically vary the quality of the match because of the large input resistance. For low frequencies, Figure 40 or Figure 42 is recommended.

In Figure 41, the matching components are drawn as generic reactances. Depending on the frequency, the input impedance and the availability of standard value components, either a capacitor or an inductor is used. As in the previous case, the input impedance at a particular frequency is plotted on a Smith Chart and matching components are chosen (shunt or series L, shunt or series C) to move the impedance to the center of the chart.

Figure 40. Broadband Resistive Input Coupling Option

Figure 41. Narrow-Band Reactive Input Coupling Option

Figure 42. Series Attention Input Coupling Option

Figure 42 shows a third method for coupling the input signal into the AD8315. A series resistor, connected to the RF source, combines with the input impedance of the AD8315 to resistively divide the input signal being applied to the input. This has the advantage of very little power being tapped off in RF power transmission applications.

### USING THE CHIP SCALE PACKAGE

On the underside of the chip scale package, there is an exposed paddle. This paddle is internally connected to the chip's ground. There is no thermal requirement to solder the paddle down to the printed circuit board's ground plane. However, soldering down the paddle has been shown to increase the stability over frequency of the AD8315 ACP's response at low input power levels (that is, at around -45 dBm) in the DCS and PCS bands.

### **EVALUATION BOARD**

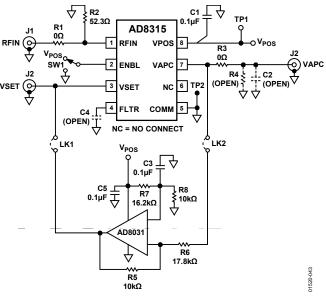

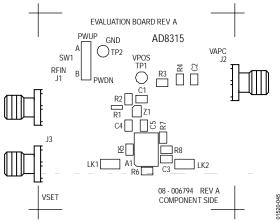

Figure 43 shows the schematic of the AD8315 MSOP evaluation board. The layout and silkscreen of the component side are shown in Figure 44 and Figure 45. An evaluation board is also available for the LFCSP package (see the Ordering Guide for exact part numbers). Apart from the slightly smaller device footprint, the LFCSP evaluation board is identical to the MSOP board. The board is powered by a single supply in the 2.7 V to 5.5 V range. The power supply is decoupled by a single 0.1  $\mu F$  capacitor.

Table 5 details the various configuration options of the evaluation board.

Figure 43. Evaluation Board Schematic (MSOP)

| Component  | Function                                                                                                                                                                                                                                                                                                                                                  | Default Condition                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| TP1, TP2   | Supply and Ground Vector Pins.                                                                                                                                                                                                                                                                                                                            | Not Applicable                                                |

| SW1        | Device Enable. When in Position A, the ENBL pin is connected to VPOS and the AD8315 is in operating mode. In Position B, the ENBL pin is grounded putting the device in power-down mode.                                                                                                                                                                  | SW1 = A                                                       |

| R1, R2     | Input Interface. The 52.3 $\Omega$ resistor in Position R2 combines with the AD8315's internal input<br>impedance to give a broadband input impedance of around 50 $\Omega$ . A reactive match can be<br>implemented by replacing R2 with an inductor and R1 (0 $\Omega$ ) with a capacitor. Note that the<br>AD8315's RF input is internally ac-coupled. | R2 = 52.3 $\Omega$ (Size 0603)<br>R1 = 0 $\Omega$ (Size 0402) |

| R3, R4, C2 | Output Interface. R4 and C2 can be used to check the response of VAPC to capacitive and resistive loading. R3/R4 can be used to reduce the slope of VAPC.                                                                                                                                                                                                 | R4 = C2 = Open (Size 0603)<br>R3 = 0 Ω (Size 0603)            |

| C1         | Power Supply Decoupling. The nominal supply decoupling consists of a 0.1 μF capacitor.                                                                                                                                                                                                                                                                    | C1 = 0.1 μF (Size 0603)                                       |

| C4         | Filter Capacitor. The response time of VAPC can be modified by placing a capacitor between FLTR (Pin 4) and ground.                                                                                                                                                                                                                                       | C4 = Open (Size 0603)                                         |

| LK1, LK2   | Measurement Mode. A quasimeasurement mode can be implemented by installing LK1 and LK2 (connecting an inverted VAPC to VSET) to yield the nominal relationship between RFIN and VSET. In this mode, a large capacitor (0.01 $\mu$ F or greater) must be installed in C4.                                                                                  | LK1, LK2 = Installed                                          |

#### Table 5. Evaluation Board Configuration Options

Figure 44. Layout of Component Side (MSOP)

Figure 45. Silkscreen of Component Side (MSOP)

For operation in controller mode, both jumpers, LK1 and LK2, should be removed. The setpoint voltage is applied to VSET, RFIN is connected to the RF source (PA output or directional coupler), and VAPC is connected to the gain control pin of the PA. When used in controller mode, a capacitor must be installed in C4 for loop stability. For GSM/DCS handset power amplifiers, this capacitor should typically range from 150 pF to 300 pF.

A quasimeasurement mode (where the AD8315 delivers an output voltage that is proportional to the log of the input signal) can be implemented, to establish the relationship between VSET and RFIN, by installing the two jumpers, LK1 and LK2. This mimics an AGC loop. To establish the transfer function of the log amp, the RF input should be swept while the voltage on VSET is measured, that is, the SMA connector labeled VSET now acts as an output. This is the simplest method to validate operation of the evaluation board. When operated in this mode, a large capacitor (0.01  $\mu$ F or greater) must be installed in C4 (filter capacitor) to ensure loop stability.

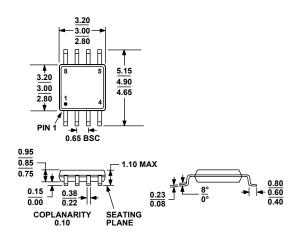

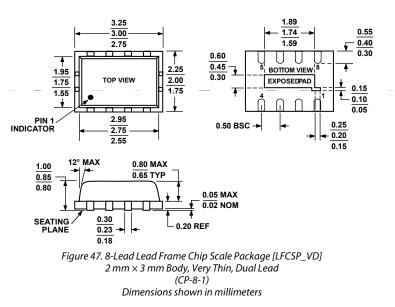

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 46. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description                | Package Option | Ordering Quantity | Branding |

|------------------------------|-------------------|------------------------------------|----------------|-------------------|----------|

| AD8315ARM                    | -30°C to +85°C    | 8-Lead MSOP, Tube                  | RM-8           | 50                | J7A      |

| AD8315ARM-REEL               | -30°C to +85°C    | 8-Lead MSOP, 13" Tape and Reel     | RM-8           | 3,000             | J7A      |

| AD8315ARM-REEL7              | -30°C to +85°C    | 8-Lead MSOP, 7" Tape and Reel      | RM-8           | 1,000             | J7A      |

| AD8315ARMZ <sup>1</sup>      | -30°C to +85°C    | 8-Lead MSOP, Tube                  | RM-8           | 50                | Q0S      |

| AD8315ARMZ-RL <sup>1</sup>   | −30°C to +85°C    | 8-Lead MSOP, 13" Tape and Reel     | RM-8           | 3,000             | Q0S      |

| AD8315-EVAL                  |                   | MSOP Evaluation Board              |                |                   |          |

| AD8315ACP-REEL               | -30°C to +85°C    | 8-Lead LFCSP_VD, 13" Tape and Reel | CP-8-1         | 10,000            | J7       |

| AD8315ACP-REEL7              | -30°C to +85°C    | 8-Lead LFCSP_VD, 7" Tape and Reel  | CP-8-1         | 3,000             | J7       |

| AD8315ACPZ-REEL <sup>1</sup> | -30°C to +85°C    | 8-Lead LFCSP_VD, 13" Tape and Reel | CP-8-1         | 10,000            | 0J       |

| AD8315ACPZ-REEL71            | -30°C to +85°C    | 8-Lead LFCSP_VD, 7" Tape and Reel  | CP-8-1         | 3,000             | 0J       |

| AD8315ACP-EVAL               |                   | LFCSP_VD Evaluation Board          |                |                   |          |

| AD8315CSURF                  |                   | Die, Surf Tape                     | DIE            | 5,000             |          |

| AD8315ACHIPS                 |                   | Die, Waffle Pack                   | DIE            | 325               |          |

$^{1}$  Z = Pb-free part.

# NOTES

©2006 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. C01520-0-6/06(C)

www.analog.com

Rev. C | Page 24 of 24