ADS1201

# High Dynamic Range DELTA-SIGMA MODULATOR

# FEATURES

- 130dB DYNAMIC RANGE

- FULLY DIFFERENTIAL INPUT

- TWO-WIRE INTERFACE

- INTERNAL/EXTERNAL REFERENCE

- ON-CHIP SWITCHES FOR CALIBRATION

# **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- INSTRUMENTATION

- SMART TRANSMITTERS

- PORTABLE INSTRUMENTS

- WEIGH SCALES

- PRESSURE TRANSDUCERS

# DESCRIPTION

The ADS1201 is a precision, 130dB dynamic range, delta-sigma ( $\Delta\Sigma$ ) modulator operating from a single +5V supply. The differential inputs are ideal for direct connection to transducers or low level signals. With the appropriate digital filter and modulator rate, the device can be used to achieve 24-bit analog-to-digital (A/D) conversion with no missing codes. Effective resolution of 20 bits can be maintained with a digital filter bandwidth of 1kHz at a modulator rate of 320kHz.

The ADS1201 is designed for use in high resolution measurement applications including smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation. It is available in a 16-lead SOIC package.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = +5V$ , MCLK = 320kHz, REF<sub>EN</sub> LOW, BIAS<sub>EN</sub> LOW, and external +2.5V reference, unless otherwise specified.

|                                                                                                                                                                               |                                                                                                                                  | ADS1201U                   |                                                                |                                          |                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------|------------------------------------------|-------------------------------------------------|--|

| PARAMETER                                                                                                                                                                     | CONDITIONS                                                                                                                       | MIN                        | TYP                                                            | MAX                                      | UNITS                                           |  |

| ANALOG INPUT<br>Absolute Input Voltage Range                                                                                                                                  | With V <sub>BIAS</sub> (1)                                                                                                       | 0<br>-10                   |                                                                | +5<br>+10                                | V                                               |  |

| Differential Input Voltage Range                                                                                                                                              | With V <sub>BIAS</sub> <sup>(1)</sup>                                                                                            | -5<br>-20                  | See Note 2                                                     | +5<br>+20                                | V<br>V<br>V                                     |  |

| Input Impedance<br>Input Capacitance                                                                                                                                          |                                                                                                                                  |                            | 250 <sup>(4)</sup><br>8                                        |                                          | kΩ<br>pF                                        |  |

| Input Leakage Current                                                                                                                                                         | At T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                          |                            | 5                                                              | 50<br>1                                  | pA<br>nA                                        |  |

| SYSTEM PERFORMANCE<br>Dynamic Range<br>Integral Linearity Error                                                                                                               | 10Hz Bandwidth <sup>(5)</sup><br>60Hz Bandwidth <sup>(5)</sup><br>1kHz Bandwidth <sup>(5)</sup><br>60Hz Bandwidth <sup>(5)</sup> | 115(6)                     | 130 <sup>(6)</sup><br>120 <sup>(6)</sup><br>115 <sup>(6)</sup> | ±0.0015                                  | dB<br>dB<br>dB<br>%FSR                          |  |

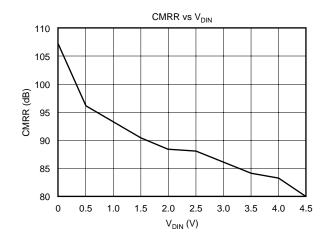

| Offset Error <sup>(2)</sup><br>Offset Drift <sup>(3)</sup><br>Gain Error <sup>(2)</sup><br>Gain Error Drift <sup>(3)</sup><br>Common-Mode Rejection<br>Power Supply Rejection | 1kHz Bandwidth <sup>(5)</sup><br>At DC                                                                                           | 80                         | See Note 7<br>1<br>See Note 7<br>1<br>100<br>80                | ±0.0015                                  | %FSR<br>μV<br>μV/°C<br>ppm<br>μV/°C<br>dB<br>dB |  |

| REFERENCE<br>Internal Reference (REF <sub>OUT</sub> )<br>Drift<br>Noise                                                                                                       |                                                                                                                                  | 2.4                        | 2.5<br>25<br>50                                                | 2.6                                      | V<br>ppm/°C<br>µVp-p                            |  |

| Load Current<br>Output Impedance<br>External Reference (REF <sub>IN</sub> )                                                                                                   | Source or Sink                                                                                                                   | -1<br>2.0                  | 2                                                              | 1<br>3.0                                 | mA<br>Ω<br>V                                    |  |

| Load Current<br>V <sub>BIAS</sub> Output<br>Drift<br>Load Current                                                                                                             | Using Internal Reference                                                                                                         | 3.15                       | 3.3<br>50                                                      | 2.5<br>3.45<br>10                        | μA<br>V<br>ppm/°C<br>mA                         |  |

| DIGITAL INPUT/OUTPUT<br>Logic Family                                                                                                                                          |                                                                                                                                  | Т                          | L Compatible CM                                                | os                                       |                                                 |  |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                         |                                                                                                                                  | 2.0<br>-0.3<br>2.4<br>0.02 |                                                                | DV <sub>DD</sub> +0.3<br>0.8<br>0.4<br>1 | V<br>V<br>V<br>MHz                              |  |

| POWER SUPPLY REQUIREMENTS<br>Power Supply Voltage<br>Supply Current                                                                                                           | Specified Performance                                                                                                            | 4.75                       |                                                                | 5.25                                     | V                                               |  |

| Analog Current<br>Digital Current                                                                                                                                             |                                                                                                                                  |                            | 4.6<br>0.4                                                     |                                          | mA<br>mA                                        |  |

| Additional Analog Current<br>REF <sub>OUT</sub> Enabled<br>V <sub>BIAS</sub> Enabled<br>Total Power Dissipation                                                               | No Load<br>No Load<br>REF <sub>OUT</sub> , V <sub>BIAS</sub> Disabled                                                            |                            | 1.6<br>1<br>25                                                 | 40                                       | mA<br>mA<br>mW                                  |  |

| TEMPERATURE RANGE<br>Specified Performance                                                                                                                                    |                                                                                                                                  | -40                        |                                                                | +85                                      | °C                                              |  |

NOTES: (1) This range is set with external resistors and  $V_{BIAS}$  (as described in the text). Other ranges are possible. (2) After the on-chip offset and gain calibration functions have been employed. (3) Re-calibration can reduce these errors. (4) Input impedance changes with MCLK. (5) Assume brick wall digital filter is used. (6) 20 Log (full scale/rms noise). (7) After calibration, these errors will be of the order of the effective resolution.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Input: Current ±100mA, Momentary                         |

|-----------------------------------------------------------------|

| ±10mA, Continuous                                               |

| Voltage AGND –0.3V to AV <sub>DD</sub> +0.3V                    |

| AV <sub>DD</sub> to DV <sub>DD</sub> 0.3V to 6V                 |

| AV <sub>DD</sub> to AGND0.3V to 6V                              |

| DV <sub>DD</sub> to DGND0.3V to 6V                              |

| AGND to DGND ±0.3V                                              |

| REF <sub>IN</sub> Voltage to AGND0.3V to AV <sub>DD</sub> +0.3V |

| Digital Input Voltage to DGND0.3V to DV <sub>DD</sub> +0.3V     |

| Digital Output Voltage to DGND0.3V to DV <sub>DD</sub> +0.3V    |

| Lead Temperature (soldering, 10s) +300°C                        |

| Internal Power Dissipation 500mW                                |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

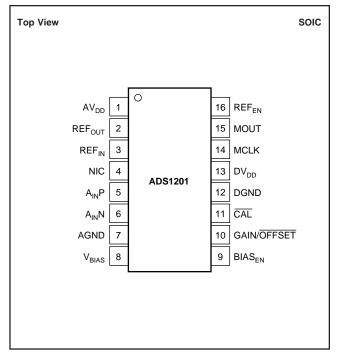

### **PIN CONFIGURATION**

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **PIN DESCRIPTIONS**

| PIN NO | NAME               | DESCRIPTION                                                                                                                      |  |

|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | AV <sub>DD</sub>   | Analog Input: Analog Supply, +5V nominal.                                                                                        |  |

| 2      | REF <sub>OUT</sub> | Analog Output: Internal Reference Voltage Output: +2.5V nominal.                                                                 |  |

| 3      | REFIN              | Analog Input: Reference Voltage Input.                                                                                           |  |

| 4      | NIC                | Not Internally Connected.                                                                                                        |  |

| 5      | A <sub>IN</sub> P  | Analog Input: Noninverting Input.                                                                                                |  |

| 6      | A <sub>IN</sub> N  | Analog Input: Inverting Input.                                                                                                   |  |

| 7      | AGND               | Analog Input: Analog Ground.                                                                                                     |  |

| 8      | V <sub>BIAS</sub>  | Analog Output: Bias Voltage Output, nominally<br>+3.3V (with +2.5V reference).                                                   |  |

| 9      | BIAS <sub>EN</sub> | Digital Input: Bias Voltage Enable Input (HIGH = enabled, LOW = disabled).                                                       |  |

| 10     | GAIN/OFFSET        | Digital Input: Gain/Offset Calibration Select Input<br>(with CAL LOW; HIGH = gain configuration,<br>LOW = offset configuration). |  |

| 11     | CAL                | Digital Input: Calibration Control Input (HIGH =<br>normal operation, LOW = gain or offset<br>calibration configuration).        |  |

| 12     | DGND               | Digital Input: Digital Ground.                                                                                                   |  |

| 13     | DV <sub>DD</sub>   | Digital Input: Digital Supply, +5V nominal.                                                                                      |  |

| 14     | MCLK               | Digital Input: Modulator Clock Input. CMOS compatible.                                                                           |  |

| 15     | MOUT               | Digital Output: Modulator Output.                                                                                                |  |

| 16     | REF <sub>EN</sub>  | Digital Input: REF <sub>OUT</sub> Voltage Enable Input<br>(HIGH = enabled, LOW = disabled).                                      |  |

### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA |

|----------|---------|------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| ADS1201U | SOL-16  | 211                          | -40°C to +85°C                    | ADS1201U           | ADS1201U                          | Rails              |

| "        | "       | "                            | "                                 | "                  | ADS1201U/1K                       | Tape and Reel      |

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /1K indicates 1000 devices per reel). Ordering 1000 pieces of "ADS1201U/1K" will get a single 1000-piece Tape and Reel.

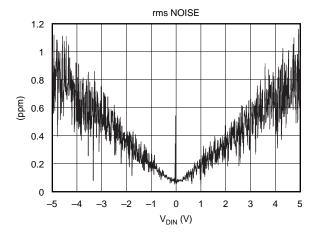

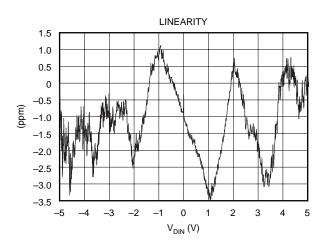

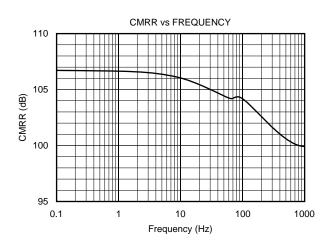

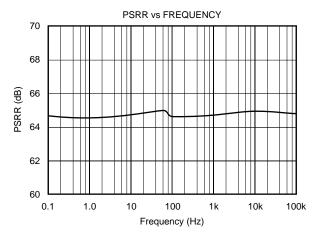

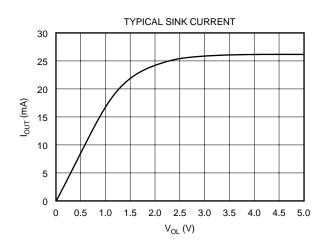

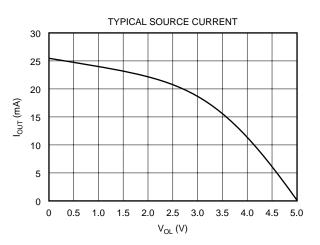

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = +5V$ , MCLK = 320kHz, REF<sub>EN</sub> LOW, BIAS<sub>EN</sub> LOW, and external +2.5V reference, unless otherwise specified.

# TYPICAL PERFORMANCE CURVES (Cont.)

At T<sub>A</sub> = +25°C, AV<sub>DD</sub> = DV<sub>DD</sub> = +5V, MCLK = 320kHz, REF<sub>EN</sub> LOW, BIAS<sub>EN</sub> LOW, and external +2.5V reference, unless otherwise specified.

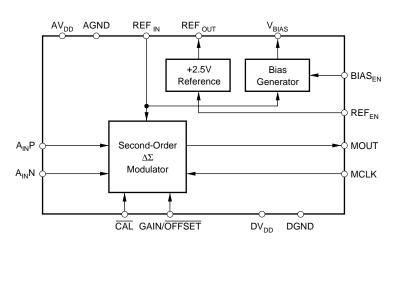

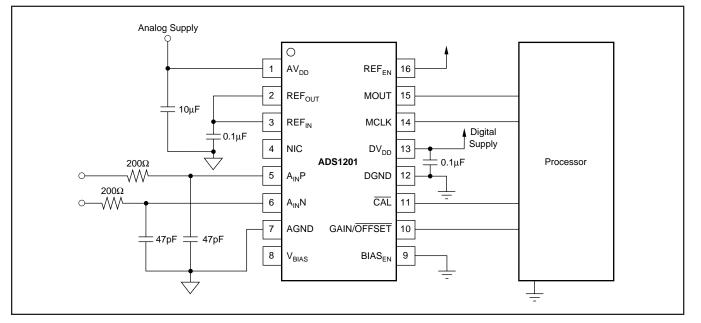

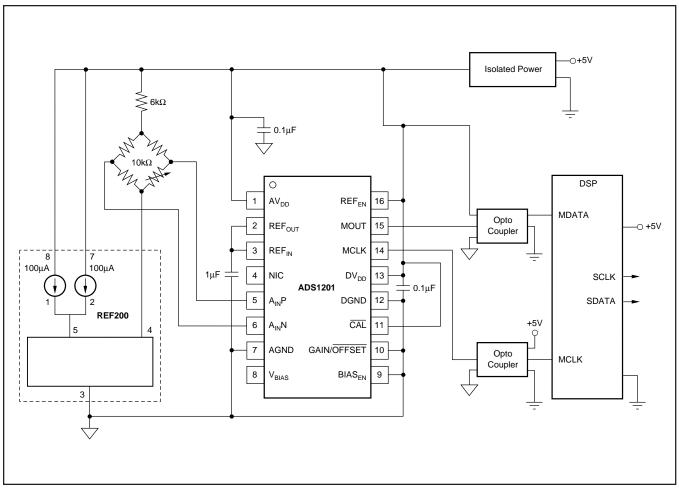

## **GENERAL DESCRIPTION**

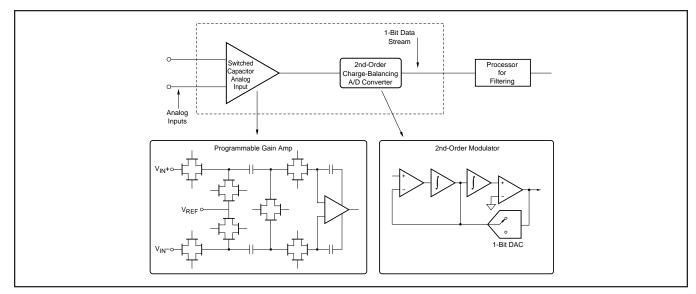

The ADS1201 is a single channel, second-order, CMOS analog modulator designed for high resolution conversions from dc to 1000Hz. The output of the converter (MOUT) provides a stream of digital ones and zeros. The time average of this serial output is proportional to the analog input voltage. The combination of an ADS1201 and a processor that is programmed to implement a digital filter results in a high resolution A/D converter system. This system allows flexibility with the digital filter design and is capable of A/D conversion results that have a dynamic range that exceeds 130dB (see Figure 1).

# THEORY OF OPERATION

The differential analog input of the ADS1201 is implemented with a switched capacitor circuit. This switched capacitor circuit implements a 2nd-order modulator stage which digitizes the input signal into a binary output stream. The input stage of the converter can be configured to sample an analog signal or to perform a calibration which quantifies offset and gain errors. The sample clock (MCLK) provides the switched capacitor network and modulator clock signal for the A/D conversion process, as well as the output data framing clock. Different frequencies for this clock allows for a variety of performance solutions in resolution and signal bandwidth. The analog input signal is continuously sampled by the A/D converter and compared to an internal or external voltage reference. A digital stream appears at the output of the converter. This digital stream accurately represents the analog input voltage over time.

FIGURE 1. Connection Diagram for the ADS1201 Delta-Sigma Modulator Including External Processor.

ADS1201

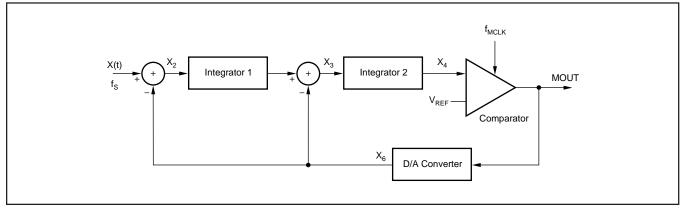

FIGURE 2. Block Diagram of the ADS1201.

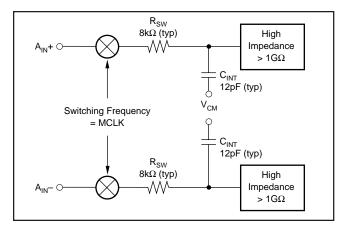

### ANALOG INPUT STAGE Analog Input

The input design topology of the ADS1201 is based on a fully differential switched capacitor architecture. This input stage provides the mechanism to achieve low system noise, high common-mode rejection (100dB) and excellent power supply rejection. The input impedance of the analog input is dependent on the input capacitor and modulator clock frequency (MCLK), which is also the sampling frequency of the converter. Figure 3 shows the basic input structure of the ADS1201. The relationship between the input impedance of the ADS1201 and the modulator clock frequency is:

$$A_{IN}$$

Input Impedance( $\Omega$ ) =  $\frac{1E12}{12 \cdot f_{MCLK}}$

The input impedance becomes a consideration in designs where the source impedance of the input signal is significant. In this case, it is possible for a portion of the signal to be lost across this external source impedance. The importance of this effect depends on the desired system performance.

There are two restrictions on the analog input signal to the ADS1201. Under no conditions should the current into or

FIGURE 3. Input Impedance of the ADS1201.

ADS1201

out of the analog inputs exceed 10mA. In addition, the linearity of the device is guaranteed only when the analog voltage applied to either input resides within the range defined by AGND = > -30mV and  $< = AV_{DD} + 30$ mV. If either of the inputs exceed these limits, the input protection diodes on the front end of the converter will begin to turn on. This will induce leakage paths resulting in nonlinearities in the conversion process.

For this reason, the 0V to 5V input range must be used with caution. Should  $AV_{DD}$  be 4.75V, the analog input signal would swing outside the guaranteed specifications of the device. Designs utilizing this mode of operation should consider limiting the span to a slightly smaller range. Common-mode voltages are also a significant concern and must be carefully analyzed.

#### Modulator

The modulator sampling frequency (MCLK) can be operated over a range of 20kHz to 1MHz. The frequency of MCLK can be increased to improve the performance of the converter or adjusted to comply with the clock requirements of the application.

The modulator topology is fundamentally a 2nd-order, chargebalancing A/D converter, as the one conceptualized in Figure 4. The analog input voltage and the output of the 1-bit DAC is differentiated, providing an analog voltage at X<sub>2</sub> and  $X_3$ . The voltage at  $X_2$  and  $X_3$  are presented to their individual integrators. The output of these integrators progress in a negative or positive direction. When the value of the signal at X<sub>4</sub> equals the comparator reference voltage, the output of the comparator switches from negative to positive or positive to negative, depending on its original state. When the output value of the comparator switches from a HIGH to LOW or vise versa, the 1-bit DAC responds on the next clock pulse by changing its analog output voltage at X<sub>6</sub>, causing the integrators to progress in the opposite direction. The feedback of the modulator to the front end of the integrators force the value of the integrator output to track the average of the input.

#### **REFERENCE CIRCUIT**

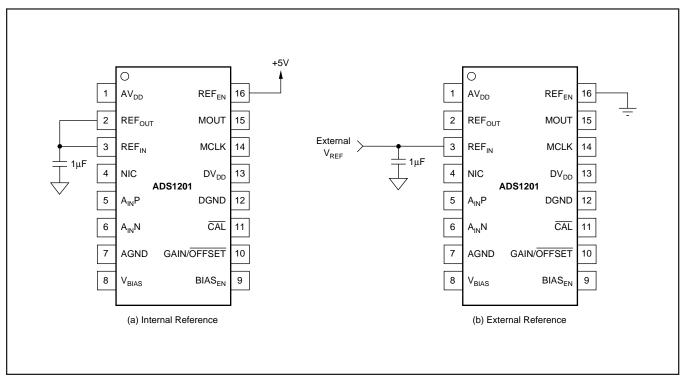

There are two reference circuits included in the ADS1201 converter:  $V_{REF}$  (REF<sub>IN</sub>, REF<sub>OUT</sub>) and  $V_{BIAS}$ . The circuitry for  $V_{REF}$  is configured to allow the user to utilize the internal reference on the chip or provide an external reference to the converter (see Figure 5). The second reference,  $V_{BIAS}$ , is derived from  $V_{REF}$ , whether it is internal or external.  $V_{BIAS}$  is exclusively an output reference. This ratiometric relationship between  $V_{REF}$  and  $V_{BIAS}$  reduces system errors when two separate bias voltages are required in the application.

#### **REFERENCE INPUT (REFIN)**

The reference input ( $\text{REF}_{\text{IN}}$ ) of the ADS1201 can be configured so that the 2.5V (nominal) internal or external reference can be used in the conversion process. If the internal refer-

ence is used, the correct connection configuration is shown in Figure 5a. The capacitor in this circuit is absolutely required if low noise performance is desired.

An external reference can be used to reduce the noise in the conversion process. If an external reference is used, care should be taken to insure that the selected reference has low noise performance. The appropriate connection circuit of an external reference is shown in Figure 5b. The reference must be configured with appropriate capacitors to reduce the high frequency noise that may be contributed by the reference. The input impedance of  $\text{REF}_{\text{IN}}$  changes with the modulator clock frequency. The relationship is:

Typical REF<sub>IN</sub> Input Impedance =

$$\frac{1E12}{50 \cdot f_{MCLK}}$$

FIGURE 4. Block Diagram of a Second-Order Modulator.

FIGURE 5. Two Voltage Reference Connection Alternatives for the ADS1201.

The reference input voltage can vary between 2V and 3V. Higher reference voltages will cause the full-scale range to increase while the internal circuit noise of the converter remains approximately the same. This will increase the LSB weight but not the internal noise, resulting in increased signal-to-noise ratio. Likewise, lower reference voltages will decrease the signal-to-noise ratio.

The internal reference, which generates +2.5V, can be disabled when an external reference is used. This internal reference is disabled with the  $\text{REF}_{\text{EN}}$  pin. When the reference is disabled, the supply current (AV<sub>DD</sub>) of the converter will reduce by approximately 1.6mA.

### **REFERENCE OUTPUT (VREF<sub>OUT</sub>)**

The ADS1201 contains an internal +2.5V reference. When using this feature,  $\text{REF}_{\text{EN}}$  must be HIGH (see Figure 5). Tolerances, drift, noise, and other specifications for this

| REF <sub>EN</sub> | REF <sub>OUT</sub> |  |

|-------------------|--------------------|--|

| LOW               | High Impedance     |  |

| HIGH              | 2.5V (nominal)     |  |

TABLE I. Reference Enable.

reference are given in the Specifications table. Note that this reference is not designed to sink or to source more than 1mA of current. In addition, loading the reference with a dynamic or variable load is not recommended. This can result in small changes in reference voltage as the load changes.

### VOLTAGE BIAS OUTPUT (V<sub>BIAS</sub>)

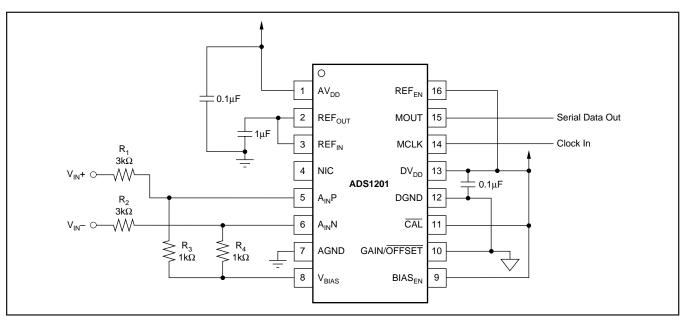

The  $V_{BIAS}$  output voltage is dependent on the reference input (REF<sub>IN</sub>) voltage and is approximately 1.33 times as great. The output of  $V_{BIAS}$  is used to bias input signals of greater than 5V. If a resistor network is used in combination with the  $V_{BIAS}$  output, the signal range can be scaled and level shifted to match the input range of the ADS1201. Figure 6 shows a connection diagram which will allow the ADS1201 to accept a ±10V input signal (20V full-scale range). If BIAS<sub>EN</sub> is HIGH, the voltage at  $V_{BIAS}$  will be 3.3V (assumes a 2.5V nominal  $V_{REF}$ ).

FIGURE 6. ±10V Bipolar Input Configuration Using V<sub>BIAS</sub>.

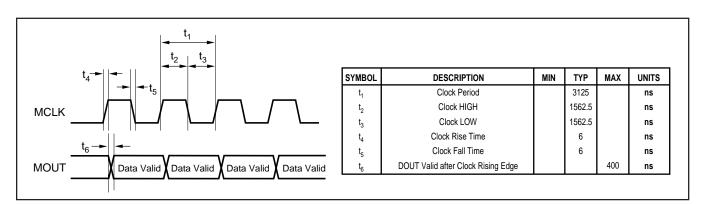

FIGURE 7. Timing Diagram for the Digital Interface of the ADS1201.

| BIAS <sub>EN</sub> | V <sub>BIAS</sub>        |  |

|--------------------|--------------------------|--|

| LOW                | High Impedance           |  |

| HIGH               | 1.33V • V <sub>REF</sub> |  |

TABLE II. Bias Enable.

When enabled, the  $V_{BIAS}$  circuitry consumes approximately 1mA with no external load. The maximum current into or out of  $V_{BIAS}$  should not exceed 10mA.

On power-up, external signals may be present before  $V_{BIAS}$  is enabled. This can create a situation in which a negative voltage is applied to the analog inputs, reverse biasing the negative input protection diode of the ADS1201. This situation should not be a problem as long as the resistors  $R_1$  and  $R_2$  limit the current being sourced by each analog input to be under 10mA. A potential of 0V at the analog input pin ( $A_{IN}P$  or  $A_{IN}N$ ) should be used in the calculation.

### DIGITAL OUTPUT

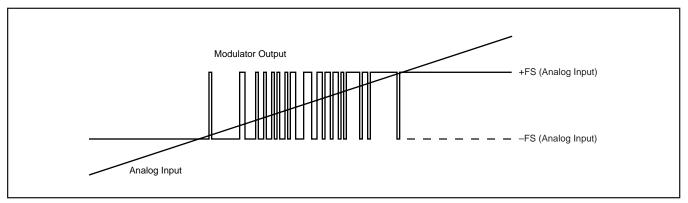

The timing diagram for the ADS1201 data retrieval is shown in Figure 7. MCLK initiates the modulator process for the ADS1201 and is used as a system clock by the ADS1201, as well as a framing clock for data out. The modulator output data, which is a serial stream, is available on the MOUT pin. Typically, MOUT is read on the falling edge of MCLK. Under any situation with MCLK, the duty cycle must be kept constant for reliable, repeatable results. An input differential signal of 0V will ideally produce a stream of ones and zeros that are HIGH 50% of the time and LOW 50% of the time. A differential input of 5V will produce a stream of ones and zeros that are HIGH 90% of the time. A differential input of -5V will produce a stream of ones and zeros that are HIGH 10% of the time. The input voltage versus the output modulator signal is shown in Figure 8.

### **OFFSET and GAIN CALIBRATION**

The ADS1201 offers a self-calibration function that is implemented with the GAIN/ $\overline{OFFSET}$  and  $\overline{CAL}_{EN}$  pins. Both conditions provide an output stream of data, similar to normal operation where the converter is configured to sample an input signal at  $A_{IN}$ .

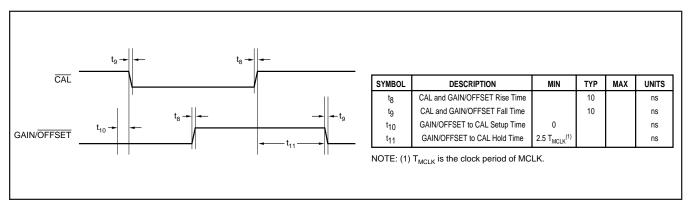

The offset and gain errors of the ADS1201 are calibrated independently. For best operation, the offset should be calibrated first, followed by the gain. The calibration implementation timing diagram is shown in Figure 9. The calibration mode pins control the calibration functions of the ADS1201.

Calibration should be performed once and then normal operation can be resumed. Calibration of offset and gain is recommended immediately after power-on and whenever there is a "significant" change in the operating environment. Significant changes in the operating environment include a change of the MCLK frequency, MCLK duty cycle, power

FIGURE 8. Analog Input versus Modulator Output of the ADS1201.

FIGURE 9. Timing Diagram for the Calibration Feature of the ADS1201.

| GAIN/OFFSET | $\overline{\mathrm{CAL}}_{\mathrm{EN}}$ |                                                                                      |

|-------------|-----------------------------------------|--------------------------------------------------------------------------------------|

| 0           | 1                                       | Normal Mode                                                                          |

| 0           | 0                                       | Offset Calibration, Analog inputs shorted to ground internally.                      |

| 1           | 0                                       | Full-Scale Calibration, Analog inputs are referenced to V <sub>REF</sub> internally. |

TABLE III. Calibration Enable.

supply,  $V_{REF}$ , or temperature. The amount of change which could cause a re-calibration is dependent on the application and effective resolution of the system.

The results of the calibration calculations are stored in two registers in the processor chip (see Figure 1). These two calibration results can then be used to calibrate the input signal results with one of the following formulas:

Equivalent Calibrated Output Code = FSC  $(FO_1 - FO_2)/(FO_3 - FO_2)$

where  $FO_1 = Filter$  output code of an applied input voltage

$FO_2$  = Filter output code of the offset calibration

$FO_3$  = Filter output code of the gain calibration

FSC = Desired full-scale output

With a simple sinc filter, the calibrated A/D conversion would equal:

Equivalent Calibrated Input Voltage =  $(N_1 - N_2) \cdot V_{REF} / (N_3 - N_2)$

```

where N_1 = number of ones counted (or digital equivalent

after filtering) over given time (t_M) with an applied input voltage

N_2 = number of ones counted (or digital equivalent after filtering)

during offset calibration where t_{12} = t_M

N_3 = number of ones counted (or digital equivalent after filtering)

during gain calibration where t_{13} = t_M

```

A system calibration can be performed by applying two known voltage levels to the input of the converter. In this situation, the GAIN/ $\overline{OFFSET}$  and  $\overline{CAL}_{EN}$  pins are not used. Rather, the digital output of these two known voltages are accumulated by the processor. With this data, the processor can determine the calibration register values that are appropriate for the application.

# LAYOUT CONSIDERATIONS

### POWER SUPPLIES

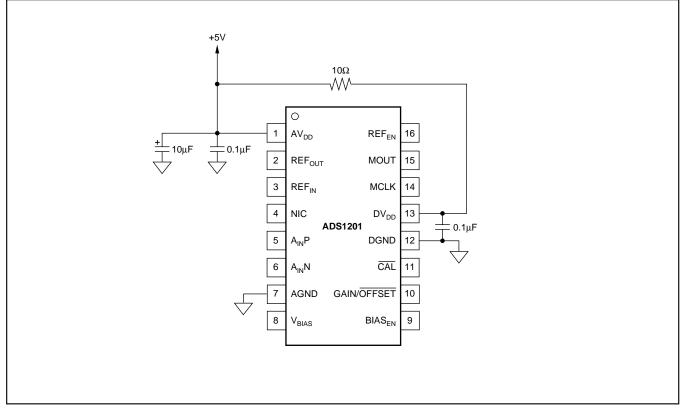

The ADS1201 requires the digital supply ( $DV_{DD}$ ) to be no greater than the analog supply ( $AV_{DD}$ ). Failure to observe this condition could cause permanent damage to the ADS1201. The best scheme is to power the analog section of the design and  $AV_{DD}$  from one +5V line and the digital section and  $DV_{DD}$  from a separate +5V line (from the same supply). If there are separate analog and digital power supplies for the ADS1201, a good design approach would be to have the analog supply come up first, followed by the digital supply. Another approach that can be used to control the analog and digital power supply differences is shown in Figure 10. In this circuit, a connection has been made between the ADS1201 supply pins via a 10 $\Omega$  resistor. The combination of this resistor and the decoupling capacitors provides some filtering between  $DV_{DD}$  and  $AV_{DD}$ .

The analog supply should be well regulated and low noise. For designs requiring very high resolution from the ADS1201, power supply rejection will be a concern. The requirements for the digital supply are not strict. However, high frequency noise on  $DV_{DD}$  can capacitively couple into the analog portion of the ADS1201. This noise can originate from switching power supplies, microprocessors or digital signal processors.

For either supply, high frequency noise will generally be rejected by the external digital filter at integer multiples of MCLK. Just below and above these frequencies, noise will alias back into the pass-band of the digital filter, affecting the conversion result.

Inputs to the ADS1201, such as  $A_{IN}$ , REF<sub>IN</sub>, and MCLK, should not be present before the analog and digital supplies are on. Violating this condition could cause latch-up. If these signals are present before the supplies are on, series resistors should be used to limit the input current.

If one supply must be used to power the ADS1201, the system's analog supply should be used to power both  $AV_{DD}$  and  $DV_{DD}$ . Experimentation may be the best way to determine the appropriate connection between  $AV_{DD}$  and  $DV_{DD}$ .

### GROUNDING

The analog and digital sections of the design should be carefully and cleanly partitioned. Each section should have its own ground plane with no overlap between them. AGND should be connected to the analog ground plane as well as all other analog grounds. DGND should be connected to the digital ground plane and all digital signals referenced to this plane.

The ADS1201 pinout is such that the converter is cleanly separated into an analog and digital portion. This should allow simple layout of the analog and digital sections of the design.

For a signal converter system, AGND and DGND of the ADS1201 can be connected together. Do not join the ground planes, but connect the two with a moderate signal trace underneath the converter. For multiple converters, connect the two ground planes at one location as central to all of the converters as possible. In some cases, experimentation may be required to find the best point to connect the two planes together. Experimentation may be the best way to determine the appropriate connection between AGND and DGND.

### DECOUPLING

Good decoupling practices should be used for the ADS1201 and for all components in the design. All decoupling capacitors, specifically the  $0.1\mu$ F ceramic capacitors, should be placed as close as possible to the pin being decoupled. A  $1\mu$ F and  $10\mu$ F capacitor, in parallel with the  $0.1\mu$ F ceramic capacitor, should be used to decouple AV<sub>DD</sub> to AGND. At a minimum, a  $0.1\mu$ F ceramic capacitor should be used to decouple DV<sub>DD</sub> to DGND, as well as for the digital supply on each digital component.

FIGURE 10. Power Supply Connection Using One Power Plane and One Digital Plane.

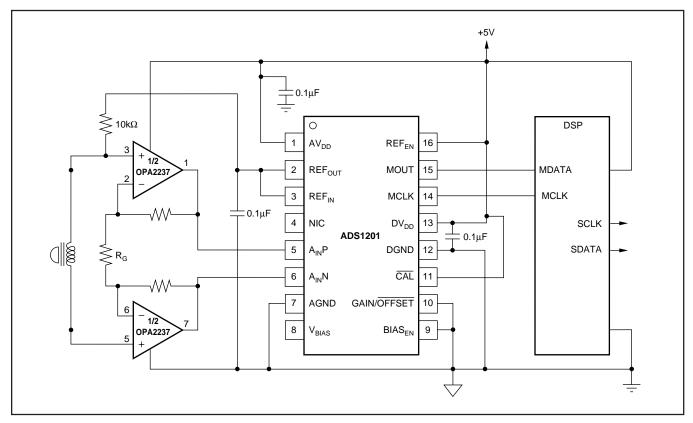

FIGURE 11. Bridge Transducer Interface with Current Excitation.

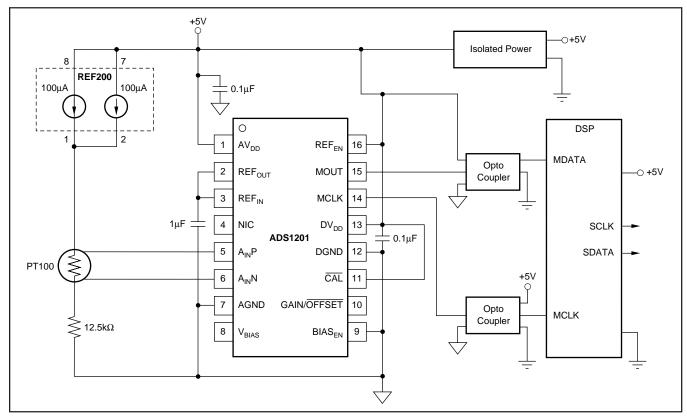

FIGURE 12. PT100 Interface with Current Excitation.

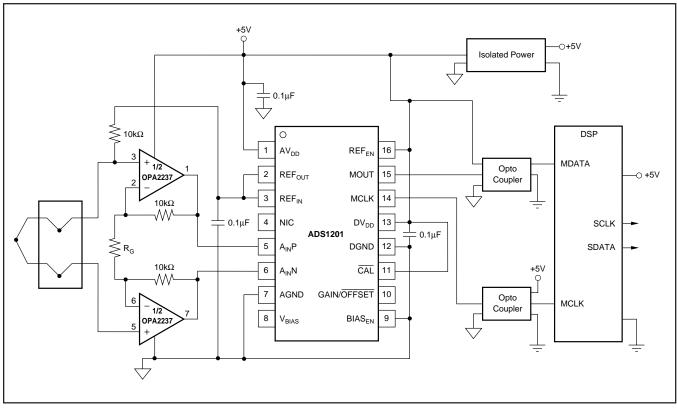

FIGURE 13. Geophone Interface.

FIGURE 14. Single-Supply, High Accuracy Thermocouple Interface.

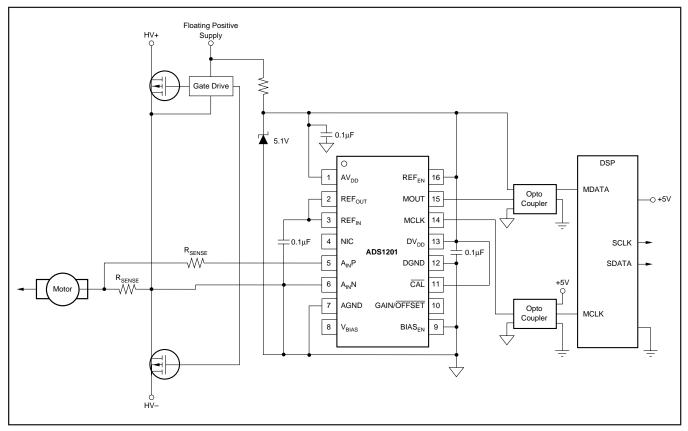

FIGURE 15. Motor Controller Sensing Circuit.