SUN MICROELECTRONICS

July 1997

# UltraSPARC™-I

DATA SHEET

First Generation SPARC v9 64-Bit Microprocessor With VIS

#### **DESCRIPTION**

The STP1030A, UltraSPARC-I, is a high-performance, highly-integrated superscalar processor implementing the SPARC V9 64-bit RISC architecture. The STP1030A is capable of sustaining the execution of up to four instructions per cycle even in the presence of conditional branches and cache misses. This sustained performance is supported by a decoupled Prefetch and Dispatch Unit (PDU) with an Instruction Buffer to feed the Execution Unit. Load buffers on the input side of the Execution Unit, together with store buffers on the output side, completely decouple pipeline execution from data cache misses. Instructions predicted to be executed are issued in program order to multiple functional units and execute in parallel. Such predictively-issued instructions can complete out of order. To further increase the number of instructions executed per cycle, instructions from different blocks (for instance, those before and after a conditional branch) can be issued in the same group.

The STP1030A supports 2D as well as 3D graphics, image processing, video compression and decompression, and video effects through the sophisticated Visual Instruction Set (VIS). VIS provides high levels of multimedia performance, including real-time H.261 video compression/ decompression and a single stream of MPEG-2 decompression at full broadcast quality with no additional hardware support.

#### Features:

- · SPARC V9 Architecture Compliant

- Binary Compatible with all SPARC Application code

- Multimedia Capable Visual Instruction Set (VIS)

- · Multi-Processing Support

- Glueless 4-Processor Connection -- Minimum Latency

- Snooping or Directory Based Protocol Support

- · 4-way SuperScalar Design with 9 Execution Units

- 4 Integer Execution Units

- 3 Floating-Point Execution Units

- 2 Graphics Execution Units

- · Selectable Little- or Big-Endian Byte Ordering

- · 64-Bit Address Pointers

- · 16-Kilobyte Non-Blocking Data Cache

- 16-Kilobyte Instruction Cache

- In-Cache 2-bit Branch Prediction

- Single Cycle Branch Following

- · Integrated Second Level Cache Controller

- 2.6 Gigabyte/sec Processor-Cache Bandwidth (167

- 3.2 Gigabyte/sec Processor-Cache Bandwidth (200 MHz)

- · Block Load/Store Instructions

- 1.3 Gigabyte/sec Processor-Memory Bandwidth (167

- 1.6 Gigabyte/sec Processor-Memory Bandwidth (200 MHz)

- · Ease of Use

- JTAG Boundary Scan

- Performance Instrumentation

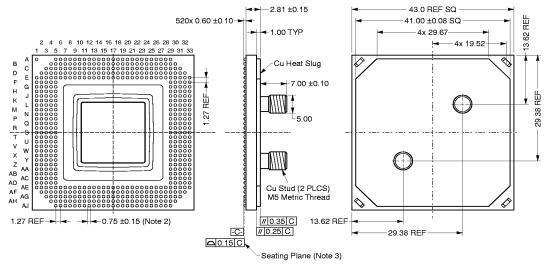

- · Technology/Packaging

- 0.4um 4-Layer Metal CMOS Process

- Operates at 3.3V

- 521 Pin Plastic Ball Grid Array (BGA)

- · Power Management

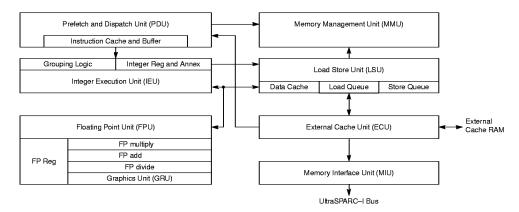

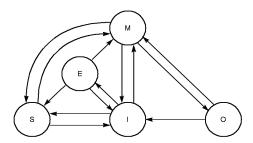

Figure 1. Functional Block Diagram

#### TECHNICAL OVERVIEW

In a single chip implementation, UltraSPARC-I integrates the following components (see Figure 1):

- Prefetch, branch prediction and dispatch unit (PDU)

- 16-Kilobyte instruction cache (I-Cache)

- Memory management unit (MMU) containing two 64-entry buffers

- a 64-entry instruction translation lookaside buffer (iTLB)

- a 64-entry data translation lookaside buffer (dTLB)

- Integer execution unit (IEU) with two arithmetic logic units (ALUs)

- · Load and store unit with a separate address generation adder

- Load buffer and store buffer decoupling data accesses from the pipeline

- 16-Kilobyte data cache (D-Cache)

- · Floating-point unit (FPU) with independent add, multiply and divide/square root sub-units

- Graphics unit (GRU) composed of two independent execution pipelines

- External cache (E-Cache) control unit

- Memory interface unit, responsible for main memory and I/O accesses

#### Prefetch and Dispatch Unit (PDU)

The prefetch and dispatch unit fetches instructions before they are actually needed in the pipeline, so the execution units do not starve. Instructions can be prefetched from all levels of the memory hierarchy, including the instruction cache, the external cache and the main memory. In order to prefetch across conditional branches, a dynamic branch prediction scheme is implemented in hardware. The outcome of a branch is based on a two-bit history of the branch. A "next field" associated with groups of four instructions in the instruction cache (I-Cache) points to the next I-Cache line to be fetched. The use of the next field makes it possible to follow taken branches and basically provides the same instruction bandwidth achieved while running sequential code. Prefetched instructions are stored in the instruction buffer until they are sent to the rest of the pipeline. Up to 12 instructions can be buffered.

## Instruction Cache (I-Cache)

The instruction cache is a 16-Kilobyte pseudo-two-way set-associative cache with 32 byte blocks. The cache is physically indexed and contains physical tags. The set is predicted as part of the "next field" so that only the index bits of an address are necessary to address the cache (13 bits, which matches the minimum page size). The instruction cache returns up to 4 instructions from an 8-instruction-wide line.

#### Memory Management Unit (MMU)

The MMU provides mapping between a 44-bit virtual address and a 41-bit physical address. That is accomplished through a 64-entry iTLB for instructions and a 64-entry dTLB for data, both fully associative. UltraSPARC–I provides hardware support for a software-based TLB miss strategy. A separate set of global registers is available to process an MMU trap. Page sizes of 8-, 64-, and 512-Kilobytes and 4 Megabytes are supported.

July 1997

SUN MICROELECTRONICS

#### Integer Execution Unit (IEU)

Two arithmetic logic units (ALUs) form the main computational part of the IEU. An early-out multi-cycle integer multiplier and a multi-cycle integer divider are also part of the IEU. Eight register windows and four sets of global registers are provided (normal, alternate, MMU and interrupt globals). The trap registers (UltraSPARC–I supports five levels of traps) are part of the IEU.

#### Load/Store Unit (LSU)

The LSU is responsible for generating the virtual address of all loads and stores (including atomics and ASI loads), for accessing the data cache, for decoupling load misses from the pipe through the load buffer, and for decoupling the stores through a store buffer. One load or one store can be issued per cycle.

## Data Cache (D-Cache)

The data cache is a write-through, non-allocating, 16 Kilobyte, direct-mapped cache with two 16-byte sub-blocks per line. It is virtually indexed and physically tagged. The tag array is dual-ported so that tag updates due to line fills do not collide with tag reads for incoming loads. Snoops to the D-Cache use the second tag port so that an incoming load can proceed without being held up by a snoop.

#### Floating-Point Unit (FPU)

Separating the execution units in the FPU allows UltraSPARC–I to issue and execute two floating-point instructions per cycle. Source data and result data are stored in the 32-entry register file, where each entry can contain a 32-bit value or a 64-bit value. Most instructions are fully pipelined (throughput of one per cycle), have a latency of three, and are not affected by the precision of the operands. (That is. latency is the same for single or double precision.) The divide and square- root instructions are not pipelined. These take 12 cycles (single precision) or 22 cycles (double precision) to execute, but they do not stall the processor. Other instructions, following the divide/square root, can be issued, executed, and retired to the register file before the divide/square root finishes. A precise exception model is maintained by synchronizing the floating-point pipe with the integer pipe and by predicting traps for long-latency operations.

#### Graphics Unit (GRU)

UltraSPARC–I introduces a comprehensive set of graphics instructions that provide fast hardware support for two-dimensional and three-dimensional image and video processing, image compression, audio processing, and similar functions. Sixteen-bit and 32-bit partitioned add, boolean, and compare are provided. Eight-bit and 16-bit partitioned multiplies are supported. Single cycle pixel distance, data alignment, packing and merge operations are all supported in the GRU.

#### External Cache Unit (ECU)

The main role of the ECU is to handle I-Cache and D-Cache misses efficiently. The ECU can handle one access per cycle to the external cache (E-Cache). Accesses to the external cache are pipelined, take three cycles (pin-to-pin) and return 16 bytes of instructions or data per cycle. This can effectively make the external cache a part of the pipeline. Programs with large data sets, data can keep data in the external cache and schedule instructions with load latencies based on the E-Cache latency. Floating-point applications can use this feature to effectively "hide" D-Cache misses. The size of the external cache can be 512 Kilobytes, or 1-, or 2-, or 4 Megabytes, but the line size is always 64 bytes. A MOESI protocol ("modified, owned, exclusive, shared, invalid"-- see "Cache Coherence Protocol" on page 7) helps to maintain coherency across the system.

The ECU provides overlap processing during load and store misses. For instance, stores that hit the E-Cache can proceed while a load miss is being processed. The ECU is also capable of processing reads and writes indiscriminately without a costly turnaround penalty (only 2 cycles). The ECU also handles snoops.

Block loads and block stores load or store a 64-byte line of data from memory to the floating-point register file. These are also processed efficiently by the ECU, providing high transfer bandwidth without polluting the internal or external caches.

## Memory Interface Unit (MIU)

The MIU handles all transactions with the system, such as external cache misses, interrupts, snoops, write-backs, and so forth. The MIU communicates with the system at a frequency lower than that of UltraSPARC–I (either 1/2 or 1/3).

#### **ULTRASPARC-I SUBSYSTEMS**

#### Subsystem Description

In the discussion which follows, "system" refers to any other location within the same coherency domain as UltraSPARC–I. For instance, the term includes caches of other processors connected to the interconnect.

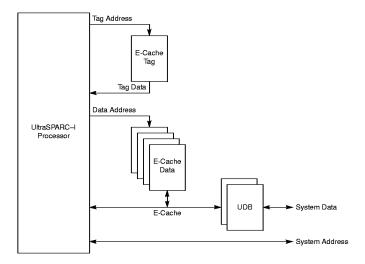

A complete UltraSPARC–I subsystem consists of one UltraSPARC–I processor, synchronous SRAM components for the external cache tags and data, and the UltraSPARC Data Buffer (UDB), which has two identical UltraSPARC data buffer microchips. The UDB isolates the E-Cache from the system and provides data buffers for incoming and outgoing system transactions; UDB also provides ECC generation and checking.

Figure 2. UltraSPARC-I System Interface

#### Overview of UltraSPARC-I Interface

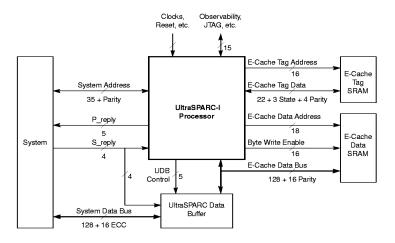

The main interfaces to and from UltraSPARC–I are shown in *Figure 3*. A typical module includes an external cache composed of the tag unit and the data unit. Both of them can be implemented using commodity SRAMs. Separate address and data buses are provided from and to the tag and data SRAMs for increased performance. The main role of the UDB is to isolate UltraSPARC–I and its external cache from the main system data bus so that the interface can operate at processor speed (reduced capacitance loading). The data buffer also provides overlap between system transactions and local E-Cache transactions even when the latter need to use part of the data buffer. The logic to control the UDB is included on UltraSPARC–I to provide fast data transfers between UltraSPARC–I and the external cache and the system. A separate address bus and separate control signals are provided for supporting system transactions. Clock signals, reset pins, observability pins, and JTAG support are also part of UltraSPARC–I interfaces discussed here.

6 SUN MICROELECTRONICS July 1997

7

Figure 3. Main UltraSPARC-I Interfaces

#### Cache Coherence Protocol

This section describes the protocol used to maintain coherency between the internal caches of UltraSPARC–I, on the one hand, and the external cache and the system, on the other.

Inclusion in the E-Cache is maintained for both the I-Cache and the D-Cache. (All lines containing data currently held in the internal caches are in the external cache, even when the caches are turned off.) The state of these lines forms a part of the tag kept in the external tag RAM.

The cache coherence protocol is point-to-point write-invalidate. It is based on the 5 MOESI states maintained in the E-Cache tags of each master port (that is, each UltraSPARC-I). The E-Cache tags have one of the following five states (MOESI):

- Exclusively Modified (M)

- Shared Modified (O)

- Exclusive Clean (E)

- Shared Clean (S)

- Invalid (I)

Three bits in the tag RAM define the state of each line as follows:

**TABLE 1: External Cache Coherency State Definition**

|                          |       | State Bit |           |  |  |

|--------------------------|-------|-----------|-----------|--|--|

| STATE                    | Valid | Modified  | Exclusive |  |  |

| Invalid (I)              | 0     | 0         | 0         |  |  |

| Shared Clean (S)         | 1     | 0         | 0         |  |  |

| Exclusive Clean (E)      | 1     | 0         | 1         |  |  |

| Shared Modified (O)      | 1     | 1         | 0         |  |  |

| Exclusively Modified (M) | 1     | 1         | 1         |  |  |

The cache coherence protocol operates only on physically indexed physically tagged (PIPT) writeback caches. The unit of cache coherence is a block size of 64 bytes which corresponds to one E-Cache line. Coherent read/write transactions transfer data in 64-byte blocks only, using 4 quadwords.

The state diagram representing the allowed transactions is shown in *Figure 4*.

Figure 4. Cache Coherency Protocol State Diagram

Table 2 describes all the transitions between the states, as shown in Figure 4. It also shows the transactions that are initiated by either UltraSPARC–I or the system and the acknowledgment that is expected after completion of each transaction.

SUN MICROELECTRONICS July 1997

**TABLE 2: Transitions Allowed for Cache Coherency Protocol**

|         | Load miss; data coming from memory to an invalid line (no other cache has the data).                                | P_RDS_REQ                   | S RBU                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------|

| 1 → S   |                                                                                                                     |                             | סבוובט                                                                 |

| a       | Load miss; data provided by another cache or memory to an invalid line (another cache has the data or I-Cache miss. | P_RDS_REQ                   | S_RBS                                                                  |

|         |                                                                                                                     | P_RDSA_REQ                  | S_RBS                                                                  |

|         | Store miss, atomic miss on invalid line.                                                                            | P_RDO_REQ                   | S_RBU                                                                  |

|         | Store hit or atomic hit to Exclusive Clean line.                                                                    | No Transaction              | No Transaction                                                         |

|         | Request from the system to share this line (load miss from another processor).                                      | S_CPB_REQ,<br>S_CPB_MSI_REQ | P_SACK   P_SACKD<br>followed by S_CRAB                                 |

| E→I     | i) A clean line is victimized by the processor.                                                                     | P_RDS_REQ<br>or             | S_RBU or S_RBS                                                         |

|         | I-Cache miss.                                                                                                       | P_RDSA_REQ<br>or            | S_RBS                                                                  |

|         | Write miss.                                                                                                         | P_RDO_REQ                   | S_RBU                                                                  |

|         | ii) Request from system to copyback and invalidate this line (store miss from another processor).                   | S_CPI_REQ                   | P_SACK P_SACKD<br>followed by S_CRAB                                   |

|         | iii) Request from SC to invalidate this line (block store from another processor)                                   | S_INV_REQ                   | P_SACK P_SACKD                                                         |

| S → M   | Store hit, atomic hit to Shared Clean line                                                                          | P_RDO_REQ                   | S_OAK                                                                  |

| S → I i | i) A Shared Clean line is victimized by UltraSPARC.                                                                 | P_RDS_REQ                   | S_RBU or S_RBS                                                         |

|         |                                                                                                                     | or                          |                                                                        |

|         | I-Cache miss.                                                                                                       | P_RDSA_REQ                  | S_RBS                                                                  |

|         |                                                                                                                     | or                          |                                                                        |

|         | Write hit on shared line.                                                                                           | P_RDO_REQ                   | S_RBU                                                                  |

| i       | ii) Another processor wants to write this shared line.                                                              | S_INV_REQ                   | P_SACK P_SACKD                                                         |

|         |                                                                                                                     | or                          |                                                                        |

|         |                                                                                                                     | S_CPI_REQ                   | P_SACK P_SACKD                                                         |

|         |                                                                                                                     |                             | followed by S_CRAB                                                     |

|         | iii) Request from SC to invalidate this line (block store from another processor).                                  | S_INV_REQ                   | P_SACK P_SACKD                                                         |

|         | Request from another processor to read a modified line,                                                             | S_CPB_REQ                   | P_SACK P_SACKD                                                         |

| r       | memory is not updated (as opposed to $M \rightarrow S$ ).                                                           |                             | followed by S_CRAB                                                     |

|         | i) A Modified line is victimized by the processor (Writeback).                                                      | P_WRB_REQ                   | S_WAB or S_WBCAN if system takes ownership before completing Writeback |

|         | ii) Request from system to copyback and invalidate this line (store miss from another processor).                   | S_CPI_REQ                   | P_SACK P_SACKD<br>followed by S_CRAB                                   |

|         | iii) Request from system to invalidate this line (block store from another processor)                               | S_INV_REQ                   | P_SACK P_SACKD                                                         |

|         | Request from another processor to read this line, memory                                                            | S_CPB_MSI_REQ               | P_SACK P_SACKD                                                         |

| ļi.     | is updated so line becomes clean ( $c.f. M \rightarrow O$ )                                                         |                             | followed by S_CRAB                                                     |

| O → M   | Store hit, atomic hit to Modified line, PREFETCH.                                                                   | P_RDO_REQ                   | S_OAK                                                                  |

#### UltraSPARC-I as a Bus Port

The UltraSPARC–I Port Architecture defines protocols for a family of tightly coupled, cache consistent, shared memory multiprocessor systems. The UltraSPARC–I bus provides low latency to memory, as well as high bandwidth and fast microprocessor data sharing. UltraSPARC–I bus transactions are carried over a packet-switched bus with independent scheduling of separate (and possibly multiple) address and data buses.

The UltraSPARC–I processor and its cache subsystem (including the UDB) form an UltraSPARC–I bus module. This module interfaces to the interconnect using the UltraSPARC–I bus interface definition called the UltraSPARC Port Architecture (UPA). (For more information, refer to the manual entitled *UPA Interconnect Architecture*.) The I/O subsystem and the graphics subsystem may also reside on an UltraSPARC–I bus module.

The physical connections between UltraSPARC-I and the UltraSPARC-I bus mainly consist of the following:

- a bidirectional address bus for transaction requests between UltraSPARC–I and the UltraSPARC–I bus interface

- two unidirectional (one incoming, one outgoing) reply buses for flow control

- a bidirectional request for a distributed address bus arbitration scheme

The snoop bus, although not part of the UltraSPARC–I module, is present and is used to manage duplicate tags, and for efficient data sharing.

*Table 3* shows the UltraSPARC–I Port interface as specified in the *UPA Interconnect Architecture* and the corresponding pins for UltraSPARC–I.

**TABLE 3: UPA Port Interface**

| UPA Port Interface |    | UltraSPARC-I Interface |

|--------------------|----|------------------------|

| UPA_DataBus[144]   | <> | EDATA[127:0],          |

|                    |    | EDPAR[15:0]            |

| UPA_ECC_Valid[2]   | <> |                        |

| UPA_AddressBus[37] | <> | SYSADDR[38]            |

| UPA_Addr_Valid     | <> | ADR_VLD                |

| UPA_Addr_Arb[5]    | <> | NODE_RQ[2:0],          |

|                    |    | REQUEST_OUT,           |

|                    |    | SC_RQ                  |

| UPA_P_REPLY[5]     | <  | P_REPLY[5]             |

| UPA_S_REPLY[5]     | >  | S_REPLY[3:0]           |

| UPA_SnoopBus[36]   | >  |                        |

| UPA_SnoopCntl[13]  | <> |                        |

| UPA_Port_ID[5]     | >  |                        |

| UPA_Reset          | >  | RESET                  |

| UPA_Sys_Clk[2]     | >  | CLKA,                  |

|                    |    | CLKB                   |

| UPA_ClkCntl[4]     | <> |                        |

| UPA_JTAG[4]        | >  |                        |

| UPA_Slave_INT      | >  |                        |

| UPA_Mode           | >  |                        |

| UPA_Wakeup_Reset   | >  |                        |

UltraSPARC–I is both a bus master and a bus slave. As a bus master UltraSPARC–I issues read/write transactions to the interconnect using part of the UltraSPARC-I bus transaction set. UltraSPARC–I splits transactions into two independent classes:

- Class 0 contains read transactions due to cache misses and block loads

- Class 1 contains writeback requests, write invalidate requests, block stores, interrupt requests, and non-cached read/write requests.

Transactions in each class are strongly ordered by the interconnect. As a bus master, UltraSPARC—I has a physically addressed coherent cache (the E-Cache), which participates in the MOESI cache coherence protocol, and responds to the interconnect for copyback and invalidation requests.

As a bus slave, UltraSPARC-I responds to a noncached read of its bus port ID.

UltraSPARC—I is both an interrupter and an interrupt receiver. It has the capability to generate interrupt packets to other UltraSPARC—I bus interrupt receivers, and it can receive interrupts coming from other interrupters.

July 1997

SUN MICROELECTRONICS

## UPA Transactions Supported by UltraSPARC-I

#### Transactions Initiated by UltraSPARC-I

The UltraSPARC–I bus transactions initiated by UltraSPARC–I are sent off through the system address bus. Four bits in the packet identifying the transaction type are encoded according to the UltraSPARC–I bus definition of the corresponding transaction:

- P\_RDS\_REQ (Read To Share): Coherent read with intent to share; UltraSPARC-I issues this in response to a load miss.

- P\_RDSA\_REQ (Read to Share Always): Coherent read with intent to share "always;" UltraSPARC–I issues this in response to an E-Cache miss generated by an instruction fetch.

- P\_RDO\_REQ (Read to Own): Coherent read with invalidate; UltraSPARC—I issues this in response to a store miss, a store hit on a shared line, or a read-with-intent-to-write for merging partial writes, such as for read-modify-writes.

- P\_RDD\_REQ (Read to Discard): Coherent read with no intent to cache the data; UltraSPARC-I issues this during block loads.

- P\_WRB\_REQ (Writeback): Generated when a dirty victimized block from the E-Cache must be written back to its home location. The writeback is associated with a prior coherent read transaction to the same E-Cache location.

- P\_WRI\_REQ (Write Invalidate): Coherent write and invalidate request; UltraSPARC-I issues this during a block store.

- P\_INT\_REQ (Interrupt): Interrupt transaction request packet. UltraSPARC–I issues this to deliver a 64-byte interrupt packet to the destination (see ASI Registers definition in *UltraSPARC User's Manual*).

- P\_NCRD\_REQ (Noncached Read): Used when a load or a block load is issued to a noncacheable location. One, 2, 4, 8, or 16 bytes can be read with this transaction.

- P\_NCBRD\_REQ (Noncached Block Read): Used when a block read (64 bytes) is made to a noncacheable location.

- P\_NCBWR\_REQ (Noncached Block Write): Generated by UltraSPARC-I when a block write (64 bytes) is made to a noncacheable location.

#### System Transactions Accepted by UltraSPARC-I

- S\_INV\_REQ (Invalidate): Invalidate request from system controller to UltraSPARC-I following a Read To Own (P\_RDO\_REQ) or Write Invalidate (P\_WRI\_REQ) request for a block from another UltraSPARC-I.

- S\_CPB\_REQ (Copyback): Copyback request from the system controller to UltraSPARC-I following a Read To Share (P\_RDS\_REQ) or Read To Share Always (P\_RDSA\_REQ) request for a block from another UltraSPARC-I.

- S\_CPI\_REQ (Copyback Invalidate): Copyback and Invalidate request from the system controller to UltraSPARC-I in response to a Read To Own (P\_RDO\_REQ) request for a block from another UltraSPARC-I.

- S\_CPD\_REQ (Copyback To Discard): Sent at the UltraSPARC-I bus interface to UltraSPARC-I in order to service a Read To Discard (P\_RDD\_REQ) issued by another UltraSPARC-I. This transaction does not generate a state change for the E-Cache and does not require a flush of the store buffer tag check.

- P\_NCRD\_REQ (Noncached Read): The only slave read transaction that should be sent to UltraSPARC–I. UltraSPARC–I responds to this request by sending the value of its bus port ID to the data bus. The transaction starts as a P\_NCRD\_REQ from an UltraSPARC–I bus master, and is forwarded by the system controller to UltraSPARC–I. UltraSPARC–I replies through a P\_RAS. The system controller issues an S\_SRS to drive the data on SYSDATA. Finally the requesting master gets the data when the system controller issues an S\_RAS.

- P\_INT\_REQ (Interrupt): Interrupt transaction request packet sent by another UltraSPARC-I. In parallel, the 64-byte interrupt data packet is placed on SYSDATA, and S\_SWIB is sent to instruct the UltraSPARC Data Buffer to accept the data.

#### Responses to Transactions Initiated by the System (P\_Reply)

P\_reply is an acknowledgment from UltraSPARC–I to the system, in response to a request that the system sent to UltraSPARC–I previously. There are five unidirectional (output only) pins on UltraSPARC–I connected directly to the system.

- P\_IDLE (Idle): This is the default state of the wires. It indicates no reply.

- P\_SNACK (Non-Existent Block): Reply by UltraSPARC–I indicating that the requested block from a snoop does not exist in the external cache (only set when DTAGs are not present).

- P\_RAS (Read Acknowledge Single): 16 bytes of read data is ready in the output data queue on the UDB. Sent following a single non-cacheable read request from an UltraSPARC-I (reply to P\_NCRD\_REQ).

- P\_SACK (Coherent Read Acknowledge Block): Asserted for a coherent (snoop) S\_REQ when the data is in the cache and not pending a writeback due to victimization. Indicates data is available in the UDB. (Reply to S\_CPB\_REQ, S\_CPD\_REQ, S\_CPI\_REQ, or S\_INV\_REQ.)

- P\_SACKD (Coherent Read Acknowledge Block for Dirty Victim): Asserted for a coherent (snoop) S\_REQ when the data has been victimized and is pending a writeback. Indicates data is available in the UDB. (Reply to S\_CPB\_REQ, S\_CPD\_REQ, S\_CPI\_REQ, or S\_INV\_REQ.)

- P\_IAK (Interrupt Acknowledge): UltraSPARC–I sends a P\_IAK to acknowledge that the interrupt transaction delivered by the system has been serviced. This implies that there is room on the UDB for another interrupt request and its 64 bytes of data.

- P\_RERR (Read Error): Returned by UltraSPARC-I in response to a noncached block read request (P\_NCBRD) sent to it. No data is transferred. Cacheable read requests produce undefined results.

- P\_FERR (Fatal Error): Sent when UltraSPARC—I detects a parity error on the SYSADDR bus or E-Cache

tags. Indicates that the system should generate a system-wide power-on reset.

July 1997

SUN MICROELECTRONICS

#### TABLE 4: P\_REPLY Encoding

| Type    | Cycles | Name                            | Reply to Which Transaction | Class | Туре  |

|---------|--------|---------------------------------|----------------------------|-------|-------|

| P_IDLE  | 1      | Idle                            | Default State              | 0     | 00000 |

| P_FERR  | 1      | Fatal Error                     | All transactions, any time | Х     | 0100  |

| P_RERR  | 2      | Read Data Error                 | P_NCBRD_REQ                | С     | 0101  |

| P_SNACK | 2      | Coherent S_REQ Non-Existent ACK | S_REQ                      | С     | 0111  |

| P_RAS   | 2      | Read Acknowledge Single         | P_NCRD_REQ                 | С     | 1000  |

| P_SACK  | 2      | Coherent S_REQ ACK              | S_REQ                      | С     | 1010  |

| P_IAK   | 2      | Interrupt Acknowledge           | P_INT_REQ                  | С     | 1100  |

| P_SACKD | 2      | Coherent S_REQ Dirty Victim ACK | S_REQ                      | С     | 1101  |

The class values are indicated as follows:

- 0 = hardwired to 0

- X = don't care

- C = Copied from the associated P\_REQ packet

# $System \ Responses \ (S\_REPLY) \ to \ Transaction \ Request \ (P\_REQ) \ or \ Acknowledgment \ (P\_REPLY) \ from \ UltraSPARC-I$

This is also a unidirectional point-to-point connection between the system and UltraSPARC-I.

- S\_IDLE (Idle): The default state of the wires. It indicates no reply.

- S\_RTO (Read Time-Out): Forwards the Read Time Out (P\_RTO) reply from the slave that UltraSPARC-I tried to access. Note that time-outs on writes are reported asynchronously via interrupt by the detecting slave UltraSPARC-I.

- S\_ERR (Error): Asserted by the system if the situations described in the UltraSPARC–I bus specification occur. (See the manual on *UPA Interconnect Architecture*.)

- S\_WAS (Write Acknowledge Single): Generated by the system following a noncacheable write request from UltraSPARC-I (P\_NCWR\_REQ). It causes 16 bytes of data from the UDB to be put on SYSDATA.

- S\_WAB (Write Acknowledge Block): Generated by the system following a noncacheable block store (P\_NCBWR\_REQ), a writeback request (P\_WRB\_REQ), or a write invalidate request during a block store with invalidate (P\_WRI\_REQ). It causes 64 bytes of data to be put on SYSDATA.

- S\_OAK (Ownership Acknowledged Block): Generated by the system when UltraSPARC–I wants permission to write to a block that is already in the E-Cache. No data transfer occurs.

- S\_RBU (Read Block Unshared Acknowledge): The system commands the input data queue of the UDB to

accept 64 bytes of unshared or noncached data from SYSDATA. This is in response to a P\_RDS\_REQ, a

P\_RDO\_REQ, or a P\_NCBRD\_REQ.

- S\_RBS (Read Block Shared Acknowledge): The system commands the input data queue of the UDB to accept 64 bytes of shared data from SYSDATA. This is a response to a P\_RDS\_REQ or a P\_RDSA\_REQ.

- S\_RAS (Read Acknowledge Single): The system commands the UDB to accept 16 bytes of data from SYSDATA. This is a response to a noncacheable read request (P\_NCRD\_REQ).

- S\_SRS (Read Single Acknowledge): The system commands the UDB to drive 16 bytes of data onto SYSDATA. This follows a P\_RAS from UltraSPARC–I indicating the data to be ready in the UDB.

- S\_CRAB (Copyback Read Block Acknowledge): The system commands the UDB to drive 64 bytes of copyback data onto SYSDATA. This follows a P\_SACK or P\_SACKD from UltraSPARC–I indicating the copyback data to be ready in the UDB.

- S\_SWIB (Interrupt Write Block Acknowledge): The system commands the UDB to accept 64 bytes of interrupt data from SYSDATA. In parallel the P\_INT\_REQ packet that was initiated by the interrupting UltraSPARC—I is sent to the target UltraSPARC—I on SYSADDR.

- S\_WBCAN (Writeback Cancel Acknowledge): The system generates this to cancel a previous writeback by UltraSPARC–I (P\_WRB\_REQ).

- S\_INAK (Interrupt NACK): The system generates this if the receiver of an UltraSPARC–I interrupt request (P\_INT\_REQ) cannot accept another interrupt packet at the moment. This reply effectively removes the interrupt packet from the UDB queue; software on the originator should retry later. This is the only transaction that is NACK'ed by the system; S\_INAK sets a bit in an ASI register on UltraSPARC (see *UltraSPARC User's Manual*.)

TABLE 5: S\_REPLY Encoding

| S_REPLY  | Name Reply to Which Transaction                                  |                                           | Туре |

|----------|------------------------------------------------------------------|-------------------------------------------|------|

| S_IDLE   | Idle                                                             | Default State                             | 0000 |

| S_ERR    | Error                                                            | Report Error to Master                    | 0001 |

| S_CRAB   | Coherent Read Acknowledge block                                  | To slave for P_CRAB reply                 | 0010 |

| S_WBCAN  | Writeback Cancel                                                 | To Master for P_WRB_REQ                   | 0011 |

| S_WAS    | Write Acknowledge Single                                         | To Master for P_NCWR_REQ                  | 0100 |

| S_WAB    | Write Acknowledge Block                                          | To Master for any block write             | 0101 |

| S_OAK    | Ownership Acknowledge                                            | To Master for P_RDO_REQ                   | 0110 |

| S_INAK   | Interrupt Nack                                                   | To Master for P_INT_REQ                   | 0111 |

| S_RBU    | Read Block Acknowledge Unshared                                  | To Master for any block read              | 1000 |

| S_RBS    | Read block Acknowledge Shared To Master for coherent shared read |                                           | 1001 |

| S_RAS    | Read Acknowledge Single                                          | To Master for P_NCRD_REQ                  | 1010 |

| S_RTO    | Read Time Out                                                    | To Master, forwarding of P_RTO            | 1011 |

| S_SRS    | Slave Read Single Read 16 bytes of data from slave               |                                           | 1110 |

| S_SWIB   | Slave Write Interrupt Block                                      | Write 64 bytes of interrupt data to slave | 1101 |

| Reserved | _                                                                | _                                         | 1111 |

## Interaction between the E-Cache and UltraSPARC Data Buffers (UDB)

External cache accesses, although synchronous to the internal clock, are not closely coupled to the pipeline. Full throughput to the external cache is supported and can make the E-Cache look like a very large D-Cache. The micro-architecture used to support this consists of the load buffer, dual ported tags, separate address buses for tag and data, and so forth.

The UDB isolates the system data bus from UltraSPARC–I. The UDB allows data transfers between UltraSPARC–I and the memory system or I/O (for example, noncacheable stores). The data buffer also enables transfers between the E-Cache and the memory system (for instance, writebacks) to occur much more rapidly since system arbitration and system throughput are hidden by the internal buffering of the UDB. Overlapping of transactions is also possible which increases overall bandwidth. Interrupt "packets" are handled by the UDB, which also generates and checks error correction code (ECC).

The external cache consists of two parts:

- E-Cache TAG RAM, which contains the physical tags of the cached lines and 3 bits of state information

- E-Cache DATA RAM, which contains the data for each cache line

Both these parts can be built out of commodity SRAMs. The parts operate synchronously with UltraSPARC–I (and so are known as Synchronous Static RAMs). The external cache sizes supported by UltraSPARC–I are: 512 Kilobytes, and 1-, 2-, or 4 Megabytes. The size of the cache is established at boot time by software.

Each byte in the RAMs is accompanied by a parity bit (three bits for the tags and 16 bits for data).

The clients for the external cache are UltraSPARC–I and the UDB. More specifically for Ultra-SPARC-I, they are the load buffer, the store buffer, the prefetch unit, and the data buffer. If the working set is too large for the D-Cache, it may still fit the E-Cache. So loads that miss the D-Cache are sent to the E-Cache. All cacheable stores go to the E-Cache (the D-Cache is write-through), but not necessarily in order with respect to load accesses. All I-Cache misses generate a request for the E-Cache. The UltraSPARC Data Buffer returns data from main memory during an E-Cache miss or a load to noncacheable locations. Writebacks (the process of writing a dirty line back to memory before a fill) generate data transfers from the E-Cache to the UDB, controlled entirely by the CPU. Copybacks (responses to snoop hits) also generate transfers from the E-Cache to the UDB.

Each UltraSPARC data buffer microchip has a 4-entry-by-16-byte read buffer that can hold a 64-byte line coming from main memory due to an E-Cache read miss or a non-cacheable read. The outgoing buffer (that is, the buffer receiving data from the UltraSPARC–I and sending it to the system) is divided into three parts. There is an  $8\times16$  byte writeback buffer, an  $8\times16$  byte non-cacheable store buffer, and a  $4\times16$  byte snoop buffer. Note that the writeback buffer can be snooped; consequently, internal bypass is provided to send the writeback data to the port requesting the snoop on the interconnect. Three 64-bit registers are provided to hold an incoming interrupt data packet, while three more are provided to hold an interrupt data packet waiting to be sent

SUN MICROELECTRONICS

July 1997

## SIGNAL DESCRIPTIONS

## Quick Pin Reference - UPA Interface

| Symbol       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                           |  |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SYSADR[35:0] | I/O  | Bidirectional UltraSPARC-I transaction request bus. Maximum of 3 other masters and 1 system controller can be connected to this bus. (3.3V, UPA) [1]                                                                                                                                                                                        |  |

| ADR_VLD      | I/O  | Bidirectional radial UltraSPARC-I Bus signal between UltraSPARC-I and the system. Driven bulltraSPARC-I to initiate SYSADR transactions to the system. Driven by the system to initiate Coherency, Interrupt or Slave transactions to UltraSPARC-I. Synchronous to the system clock (3.3V, UPA)                                             |  |

| NODE_RQ[2:0] | I    | UltraSPARC-I system address bus arbitration request from up to 3 other UltraSPARC-I bus orts that might be sharing the SYSADR. Used by UltraSPARC-I for the distributed SYSADR rbitration protocol. Connection to other UltraSPARC-I bus ports is strictly dependent on the flaster ID allocation. Synchronous to system clock. (3.3V, UPA) |  |

| SC_RQ        | I    | UltraSPARC-I system address bus arbitration request from the system. Used by UltraSPARC-I for the distributed SYSADR arbitration protocol. Synchronous to system clock. (3.3V, UPA)                                                                                                                                                         |  |

| S_REPLY[3:0] | I    | UltraSPARC-I system Reply packet, driven to UltraSPARC-I. Bit 4 of the UltraSPARC-I bus S_REPLY is not used by UltraSPARC-I. Synchronous to system clock. (3.3V, UPA)                                                                                                                                                                       |  |

| DATA_STALL   | I    | This is asserted with or after an S_REPLY to hold output system data or signal the delay in arrival of input data from the system. (3.3V, UPA)                                                                                                                                                                                              |  |

| P_REPLY[4:0] | 0    | UltraSPARC-I processor reply packet, driven by UltraSPARC-I to the system. Synchronous to system clock. (3.3V, UPA)                                                                                                                                                                                                                         |  |

| NODEX_RQ     | 0    | UltraSPARC-I system address bus arbitration request. Asserted when UltraSPARC-I needs to drive SYSADR. Connected to all other UltraSPARC-I bus ports which share this address bus, and the system. Synchronous to system clock. (3.3V, UPA)                                                                                                 |  |

<sup>1. 3.3</sup>V UPA pins: SYSADR[35:0], ADR\_VLD, NODE\_RQ[2:0], SC\_RQ, S\_REPLY[[3:0], DATA\_STALL, P\_REPLY[4:0], NODEX\_RQ, STOP\_CLOCK, TDI, TCK, TMS, TRST, EXT\_EVENT, RESET, XIR.

## UltraSPARC™-I First Generation SPARC v9 64-Bit Microprocessor With VIS

## Quick Pin Reference - External Cache Interface

| Symbol         | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EDATA[127:0]   | I/O  | E-Cache data bus. Connects UltraSPARC-I to the E-Cache data SRAMs and the UDB. Synchronous to processor clock.                                                                                                                                                                                                                                                                                                            |  |

| EDPAR[15:0]    | I/O  | Data bus parity. Odd parity is driven for all EDATA transfers, and checked if UltraSPARC–I or the UDB is the receiver. The most significant bit serves as the parity for the most significant byte of EDATA. Synchronous to processor clock.                                                                                                                                                                              |  |

| TDATA[24:0]    | I/O  | Bidirectional data bus for E-Cache tag SRAMs. Bits [24:22] carry the MOESI state: Dirty,<br>Exclusive, Valid. Bits[21:0] carry the physical address bits [40:19]. This allows a minimum control of 512 Kilobytes. All of the TDATA bits are used, even when the E-Cache is greater than<br>Kilobytes. This is because there is no sizing in the tag compare for E-Cache hit generation<br>Bynchronous to processor clock. |  |

| TPAR[3:0]      | I/O  | Bidirectional data bus for E-Cache tag SRAMs. Odd Parity for TDATA[24:0]. TPAR[3] covers TDATA[24:22]. TPAR[2] covers TDATA[21:16]. TPAR[1] covers TDATA[15:8], TPAR[0] covers TDATA[7:0]. Synchronous to processor clock.                                                                                                                                                                                                |  |

| BYTEWE_L[15:0] | 0    | Byte write enables for synchronous pipelined E-Cache SRAMs. Bit [0] controls EDATA[127:120]. Bit [15] controls EDATA[7:0]. Byte write control is necessary because the first-level data cache is write-through. Synchronous to processor clock.                                                                                                                                                                           |  |

| ECAD[17:0]     | 0    | Address for E-Cache data SRAMs. Corresponds to physical address [21:4]. Allows a maximum 4 Megabyte E-Cache. Synchronous to processor clock.                                                                                                                                                                                                                                                                              |  |

| ECAT[15:0]     | 0    | Address for E-Cache tag SRAMs. Corresponds to physical address [21:6]. Allows a maximum 4 Megabyte E-Cache. Synchronous to processor clock.                                                                                                                                                                                                                                                                               |  |

| DSYN_WR_L      | 0    | Write enable for E-Cache data SRAMs. Active low. Synchronous to processor clock.                                                                                                                                                                                                                                                                                                                                          |  |

| DOE_L          | 0    | Active low for all SRAM data reads and writes. Synchronous to processor clock.                                                                                                                                                                                                                                                                                                                                            |  |

| TSYN_WR_L      | 0    | Write enable for E-Cache tag SRAMs. Active low. Synchronous to processor clock.                                                                                                                                                                                                                                                                                                                                           |  |

| TOE_L          | 0    | Active low for all tag data SRAM reads and writes. Synchronous to processor clock.                                                                                                                                                                                                                                                                                                                                        |  |

## Quick Pin Reference - Clock Interface

| Symbol              | Type | Name and Function                                                                                                                                                                                    |  |

|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKA                | ı    | This pin provides STP1030A with its primary clock source and is the positive differential clock input.                                                                                               |  |

| CLKB                | 1    | This pin provides STP1030A with its primary clock source and is the negative differential clock<br>nput.                                                                                             |  |

| LOOPCAP             | I    | The external PLL loop filter connects to this pin to filter the analog voltage which controls the PLL<br>VCO.                                                                                        |  |

| SCLK_MODE           | ı    | Indicates clock divider mode - system frequency is /2 or /3 of the processor frequency                                                                                                               |  |

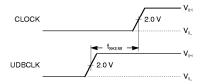

| UDBCLKA,<br>UDBCLKB | -    | These are differential inputs of the system clock. They are used to generate the phase signal which allows UltraSPARC-I to synchronize communication to the system with respect to the system clock. |  |

| PLLBYPASS           | I    | When asserted this pin causes the phase-lock loop to be bypassed. The clock from the differential receiver is directly passed to the clock trunk.                                                    |  |

| STOP_CLOCK          | 0    | Indicates clock has stopped.                                                                                                                                                                         |  |

| L5CLK               | 0    | A buffered version of UltraSPARC-I's internal level 5 clock. Used to determine PLL lock or clock tree delay when UltraSPARC-I is in PLL bypass mode.                                                 |  |

## Quick Pin Reference - JTAG/Debug Interface

| Symbol           | Type | Name and Function                                                                                                                                                                                                                                                                       |  |

|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TDO              | 0    | IEEE 1149 test data output. A three-state signal driven only when that TAP controller is in the shift-DR state.                                                                                                                                                                         |  |

| TDI              | - 1  | IEEE 1149 test data input. This pin is internally pulled to logic one when not driven.                                                                                                                                                                                                  |  |

| TCK              | I    | IEEE 1149 test clock input. This pin if not hooked to a clock source must always be driven to a logic 1 or a logic 0.                                                                                                                                                                   |  |

| TMS              | - 1  | IEEE 1149 test mode select input. This pin is internally pulled to logic one when not driven.                                                                                                                                                                                           |  |

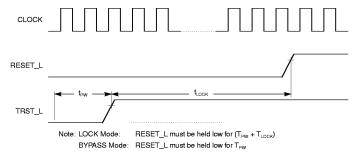

| TRST_L           | - 1  | IEEE 1149 test reset input (active low). This pin is internally pulled to logic one when not driven.                                                                                                                                                                                    |  |

| RAM_TEST         | I    | When asserted this pin forces the processor into SRAM test mode allowing direct access to the cache SRAMs for memory testing.                                                                                                                                                           |  |

| MISC_BIDIR[14:0] | I/O  | These are miscellaneous bidirectional signals used for test, debug and instrumentation. Some of them are used to improve internal operation observability, such as pipeline monitoring signals. Their exact functions are TBD.                                                          |  |

| EXT_EVENT        | I/O  | This is an open drain bidirectional signal used to indicate the clock should be stopped. This signal is wired-or with the other EXT_EVENT signals from other devices so that once one is activated all are activated. It is a debug signal which is set inactive on production systems. |  |

| PM_OUT           | 0    | Used for on-chip process monitors (reserved for IC manufacturing use).                                                                                                                                                                                                                  |  |

| TEMP_SEN[1:0]    | 0    | Defines the end points of the temperature sense element on the module used to measure the processor temperature (reserved for IC manufacturing use).                                                                                                                                    |  |

## Quick Pin Reference - Initialization Interface

| Symbol  | Туре | Name and Function                                                                                                  |

|---------|------|--------------------------------------------------------------------------------------------------------------------|

| RESET_L | I    | Driven for POR (power-on) resets. Asserted asynchronously. Deasserted synchronous to system clock. Active low.     |

| XIR_L   | I    | Driven to signal XIR resets. Actually acts like a non-maskable interrupt. Synchronous to system clock. Active low. |

| EPD     | 0    | Asserted when UltraSPARC-I is in power-down mode.                                                                  |

## Quick Pin Reference - UDB Chip Interface

| Symbol        | Туре | Name and Function                                                                                                                                                                                 |  |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| UDB_UEH       | I    | Asserted when the High UDB drives Edata[127:64], if there is an uncorrectable ECC error associated with that data. Synchronous to system clock.                                                   |  |

| UDB_UEL       | I    | serted when the Low UDB drives Edata[63:0], if there is an uncorrectable ECC error sociated with that data. Synchronous to system clock.                                                          |  |

| UDB_CEH       | I    | Asserted when the High UDB drives Edata[127:64], if the data has a corrected single-bit error. Synchronous to system clock.                                                                       |  |

| UDB_CEL       | I    | Asserted when the Low UDB drives Edata[63:0], if the data has a corrected single-bit error. Synchronous to system clock.                                                                          |  |

| UDB_CNTL[4:0] | 0    | UltraSPARC-I controls the UDB's drive and receive of EDATA. Asserted with valid EDATA when driving data to UDB. Asserted the cycle before the UDB should drive data. Synchronous to system clock. |  |

## TIMING CONSIDERATIONS

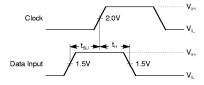

This section describes the logical timing for the transactions occurring between UltraSPARC–I, the external cache, and the data buffer. The diagrams are based on a clock with a 50% duty cycle. The transitions represented in the diagrams show what occurs at the pins of UltraSPARC–I. The position of the transitions relative to the clock transitions is correct but not drawn to scale (for instance, a set up time of 1 ns is represented by showing the transition of the incoming signal changing slightly before the rising edge of the clock).

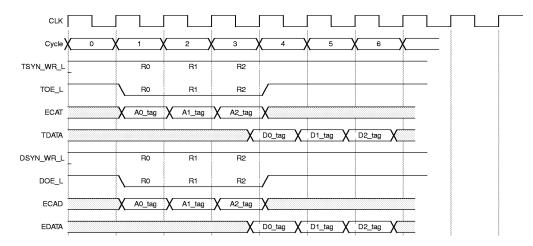

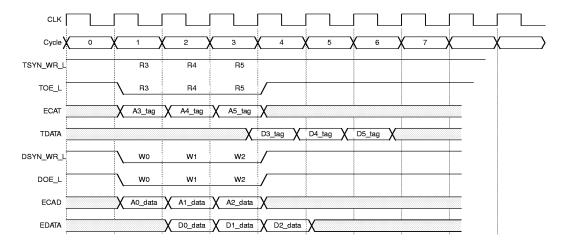

#### Coherent Read Hit

Coherent reads that hit the E-Cache are represented in *Figure 5*. With UltraSPARC–I there is no difference between burst reads and two consecutive reads. The signals used for a single read are simply duplicated for each subsequent read.

The timing diagram shows three consecutive reads that hit the E-Cache. The control signals (TSYN\_WR\_L, TOE\_L) and the address for the tag read (ECAT) as well as the control signals (DSYN\_WR\_L, DOE\_L) and the address for the data (ECAD) are shown to transition shortly after the rising edge of the clock. Two cycles later, the data for both the tag read and data read is back at the pins of the CPU shortly before the next rising edge (This meets set up time and clock skew.) Notice that the reads are fully pipelined and thus full throughput is achieved. (There are three requests made before the data of the first request comes back and the latency of each request is three cycles.)

Figure 5. Coherent Read Hit Timing

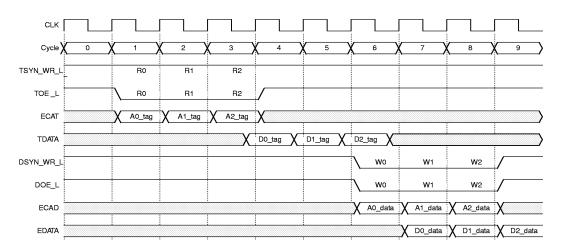

#### **Coherent Write Hits**

Writes to the external cache are processed through independent tag and data transactions. First the tag and the state bits of the E-Cache line corresponding to the write are read. If the access is a hit and the state is exclusive or modified, the data is written to the data RAM.

In the timing diagram shown in *Figure 6*, three consecutive write hits to M state lines are shown. Access to the first tag (D0\_tag) is started by asserting TSYN\_WR\_L and TOE\_L and by sending the tag address (A0\_tag). In the cycle after the tag data (D0\_tag) comes back, it is determined by UltraSPARC–I that the access is a hit and that the line is in M state (Modified). In the next clock cycle, a request is made to write the data. The data address is presented on the ECAD pins in the cycle after the request (cycle 7 for W0) and the data is sent in the following cycle (cycle 8), as shown in *Figure 6*. Separating the address and the data by one cycle reduces the turn around penalty when reads are immediately followed by writes (discussed in "Coherent Read Followed by a Coherent Write" on page 24).

Figure 6. Coherent Write Hit to M State Line

If the line is in exclusive state then the tag is updated to Modified at the same time as the data is written as shown in *Figure 7*. Otherwise, the tag port is available for a tag check of a younger store during the data write. In the timing diagram, the store buffer is empty when the first write request is made. That is why there is no overlap between the tag accesses and the write accesses. In normal operation the tag access for one write can be done in parallel with the data write of the previous write. This independence of the tag and data buses make the peak store bandwidth as high as the load bandwidth (one per cycle).

Figure 7. Coherent Writes with E to M Updates

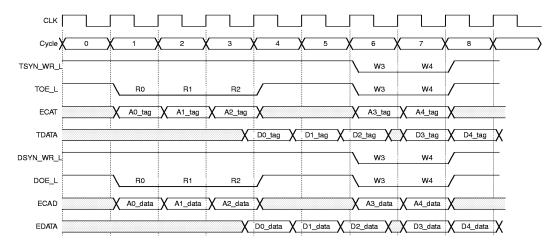

## Overlap of Tag and Data Access

Figure 8 shows the overlap of tag and data accesses. The data for three previous writes (W0, W1 and W2) is written while three tag accesses (reads) are made for three younger stores (R3, R4 and R5). If the line is in Shared or Owned state, then a read for ownership is performed before writing the data. If the access is a miss then a line is victimized and the data is written after the new line is brought in (discussed in a later section).

Figure 8. Overlap Between Tag Access and Data Write for Coherent Writes

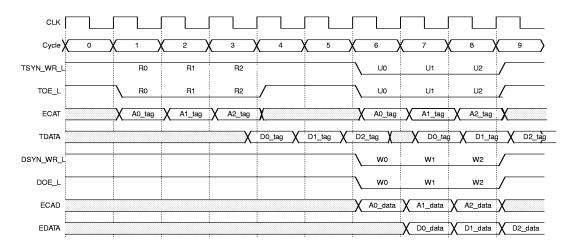

#### Coherent Read Followed by a Coherent Write

When a read is made to the E-Cache, the three cycle latency causes the data bus to be busy two cycles after the address appears at the pins. For a processor without delayed writes, writes have to be held for two cycles in order to avoid collisions between the data of the write and the data coming back from the read. Additionally, an extra cycle is necessary to switch the driver of the E-Cache data bus from the SRAMs to UltraSPARC–I (due to electrical considerations). UltraSPARC–I uses a one-deep write buffer in the data SRAMs to reduce the turnaround penalty (going from reads to writes) to two cycles. The data of a write is sent one cycle after the address (*Figure 9*). Note that there is no penalty for going from writes to reads. *Figure 9* shows the two-cycle penalty between reads and writes. The figure represents three reads followed by two writes and two tag updates. The two-cycle penalty applies to both tag accesses and data accesses (two dead cycles between A2\_tag and A3\_tag as well as between A2\_data and A3\_data).

Figure 9. Reads Followed by Writes; Turn Around Penalty

## **ELECTRICAL SPECIFICATIONS**

## Absolute Maximum Ratings[1]

| Symbol           | Parameter                                                                      | Rating                        | Units |

|------------------|--------------------------------------------------------------------------------|-------------------------------|-------|

| V <sub>DD</sub>  | Supply voltage range                                                           | 0 to 4.0                      | V     |

| V <sub>I</sub>   | Input voltage range                                                            | -0.5 to V <sub>DD</sub> + 0.5 | V     |

| V <sub>o</sub>   | Output voltage range                                                           | -0.5 to V <sub>DD</sub> + 0.5 | V     |

| I <sub>IK</sub>  | Input clamp current ( $V_1 < 0$ or $V_1 > V_{CC}$ )                            | ±20                           | mA    |

| I <sub>ok</sub>  | Output clamp current (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) | ±50                           | mA    |

| I <sub>OL</sub>  | Current into any output in the low state                                       | 50                            | mA    |

| T <sub>STG</sub> | Storage temperature                                                            | -40 to 150                    | ∞C    |

Operation of the device at values in excess of those listed above will result in degradation or destruction of the device. All voltages are defined

with respect to ground. Functional operation of the device at these or any other conditions beyond those indicated under "recommended

operating conditions "is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| Symbol           | Paran                       | neter          | Min  | Тур                   | Max                   | Units |

|------------------|-----------------------------|----------------|------|-----------------------|-----------------------|-------|

| V <sub>DD</sub>  | Supply voltage              |                | 3.2  | 3.3                   | 3.465                 | V     |

| V <sub>ss</sub>  | Ground                      |                | _    | 0                     | -                     | V     |

| V <sub>IH</sub>  | High-level input voltage    | All except CLK | 2.0  | -                     | V <sub>DD</sub> + 0.3 | V     |

|                  | CLK                         | 2.4            | -    | V <sub>DD</sub> + 0.3 | V                     |       |

| $V_{\mathbb{L}}$ | Low-level input voltage     | All except CLK | -0.3 | _                     | 0.8                   | V     |

| V <sub>IL</sub>  |                             | CLK            | -0.3 | _                     | 1.6                   | V     |

| I <sub>OH</sub>  | High-level output current   | •              | _    | -                     | -4.0                  | mA    |

| I <sub>OL</sub>  | Low-level output current    |                | _    | _                     | 8.0                   | mA    |

| T <sub>J</sub>   | Operating junction temperat | ure            | _    | _                     | 105                   | ∞c    |

| T <sub>A</sub>   | Operating ambient tempera   | ture           | 0    | _                     | [1]                   | ∞c    |

<sup>1.</sup> Maximum ambient temperature is limited by air flow such that the maximum junction temperature does not exceed T<sub>J</sub>.

#### UltraSPARC™-I First Generation SPARC v9 64-Bit Microprocessor With VIS

## DC Characteristics

| Symbol                            | Parameter                                                               | Conditions                                    | Min | Тур | Max | Units |  |

|-----------------------------------|-------------------------------------------------------------------------|-----------------------------------------------|-----|-----|-----|-------|--|

| V <sub>OH</sub>                   | High-level output voltage                                               | V <sub>DD</sub> = Min, I <sub>OH</sub> = Max  | 2.4 | _   | _   | ٧     |  |

| V <sub>OL</sub>                   | Low-level output voltage [1]                                            | $V_{DD} = Min, I_{OL} = Max$                  | _   | _   | 0.4 | V     |  |

| V <sub>IH</sub>                   | High-level input voltage (except CLKA, CLKB, UDBCLKA, UDBCLKB, LOOPCAP) | V <sub>DD</sub> = Max                         | 2.0 | -   | -   | V     |  |

|                                   | High -level input voltage (CLKA, CLKB, UDBCLKA, UDBCLKB)                | V <sub>DD</sub> = Max                         | 2.4 | _   | -   | ٧     |  |

| V <sub>IL</sub>                   | Low-level input voltage (except CLKA, CLKB, UDBCLKA, UDBCLKB, LOOPCAP)  | V <sub>DD</sub> = Min                         | _   | _   | 0.8 | V     |  |

|                                   | Low-level input voltage (CLKA, CLKB, UDBCLKA, UDBCLKB, LOOPCAP)         | $V_{DD} = Min$                                | -   | -   | 0.8 | V     |  |

| V <sub>IH</sub> , V <sub>IL</sub> | High-level, low-level input voltage for LOOPCAP                         | Pin should be grounded                        | -   | 0   | -   | V     |  |

| I <sub>DDD</sub>                  | Supply current                                                          | V <sub>DD</sub> = Max, freq = 167 MHz         | _   | 8   | 8.5 | Α     |  |

|                                   |                                                                         | V <sub>DD</sub> = Max, freq = 200MHz          | _   | 9.5 | 10  | Α     |  |

| l <sub>oz</sub>                   | High-impedance output current [2]                                       | $V_{DD} = Max, V_{O} = V_{DD}$                | -10 | -   | 10  | μuA   |  |

|                                   |                                                                         | $V_{DD} = Max, V_{O} = V_{SS}$                | -10 | -   | 10  | иμА   |  |

| I <sub>1</sub>                    | Input current                                                           | $V_{DD} = Max$ , $V_{O} = V_{SS}$ to $V_{DD}$ | -10 | -   | 10  | иμА   |  |

| Cı                                | Input capacitance <sup>[3]</sup>                                        |                                               | _   | 5   | -   | pF    |  |

| Co                                | Output capacitance                                                      |                                               | _   | 10  | _   | pF    |  |

<sup>1.</sup> STOP\_CLK has no  $V_{\text{OL}}$  specification.

Only bidirectional lines can be three-state. Output-only cannot be three-state. All bidirectional lines will be three-stated when RESET\_L is held LOW and SRAM\_TEST is held high.

<sup>3.</sup> This specification is provided as an aid to board design. This specification is not assured during manufacturing testing.

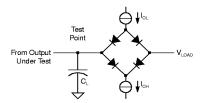

## AC Characteristics - Signal Timing (Except Clock and JTAG)

|                               |                                      |                                                                                                                  |                                                     | 167  | MHz  | 200  |      |       |

|-------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|------|------|------|-------|

| Symbol                        | Parameter                            | Signals                                                                                                          | Conditions                                          | Min  | Max  | Min  | Max  | Units |

| t <sub>su</sub> [1]           | Input setup<br>time to CLK           | SYSADDR[35:0], ADR_VLD,<br>SCLK_MODE, NODE_RQ[2:0],                                                              | Figure 12                                           | 2.4  | _    | 2.2  | -    | ns    |

| t <sub>H</sub> <sup>[1]</sup> | Input hold<br>time to CLK            | SC_RQ, S_REPLY[3:0], DATA_STALL, EDATA[127:0], EDPAR[15:0], TDATA[24:0], TPAR[3:0], RESET_L <sup>⊗</sup> , XIR_L |                                                     | 0.9  | _    | 0.9  | -    | ns    |

| t <sub>PD</sub> [1]           | Output delay from CLK                | SYSADDR[35:0], ADR_VLD,<br>EDATA[127:0], EDPAR[15:0],                                                            | $I_{OL} = 8 \text{ mA}$<br>$I_{OH} = -4 \text{ mA}$ | _    | 2.55 | -    | 1.95 | ns    |

| t <sub>OH</sub> [1]           | Output hold<br>time from<br>CLK      | TDATA[24:0], TPAR[3:0], BYTEWE_L, ECAT[15:0], TSYN_WR_L, TOE_L, P_REPLY[4:0], NODEX_RQ                           | $C_L = 35 \text{ pF}$ $V_{LOAD} = 1.5 \text{V}$     | 0.2  | _    | 0.2  | -    | ns    |

| t <sub>PD</sub> [1]           | Output delay from CLK                | ECAD[17:0], DOE_L,DSYN_WR                                                                                        |                                                     | -    | 2.55 | -    | 1.55 | ns    |

| t <sub>OH</sub> [1]           | Output hold time from CLK            | ECAD[17:0],DOE_L,DSYN_WR                                                                                         |                                                     | 0.2  | -    | 0.2  | -    | ns    |

| t <sub>PD</sub> [1]           | Output delay from CLK                | STOP_CLK, EPD                                                                                                    |                                                     | _    | 4.8  | -    | 4.4  | ns    |

| t <sub>OH</sub> [1]           | Output hold<br>time from<br>CLK      | EPD                                                                                                              |                                                     | 0.5  | -    | 0.5  | -    | ns    |

| t <sub>LOCK</sub>             | PLL                                  |                                                                                                                  |                                                     | 6.0  |      | 5.0  |      | uµs   |

|                               | acquisition<br>time                  |                                                                                                                  |                                                     | 1000 |      | 1000 |      | cycle |

| t <sub>skew</sub>             | UDBCLK<br>skew to CLK <sup>[3]</sup> |                                                                                                                  | Figure 14                                           | 0    | 1.3  | 0    | 1.3  | ns    |

<sup>1.</sup> All timing requirements are specified with PLL enabled.

July 1997

SUN MICROELECTRONICS

<sup>2.</sup> RESET\_L is asserted asynchronously but deasserted synchronously.

<sup>3.</sup> UDBCLK is before CLK as shown in Figure 14.

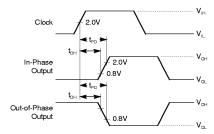

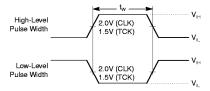

## AC Characteristics - Clock Timing

|                           |                                            |                              | 167 MHz |     |                              |     |     |       |

|---------------------------|--------------------------------------------|------------------------------|---------|-----|------------------------------|-----|-----|-------|

| Symbol                    | Parameter                                  | Min                          | Тур     | Max | Min                          | Тур | Max | Units |

| t <sub>CYC</sub> (CLK)    | Processor clock Tcycle time [1]            | 6                            | _       | _   | 5                            | -   | -   | ns    |

| t <sub>w</sub> (CLK)      | Processor clock duty cycle [1]             | 40                           | 50      | 60  | 40                           | 50  | 60  | %     |

| t <sub>SLEW</sub> (CLK)   | Clock input slew rate [1]                  | 3                            | -       | -   | 3                            | -   | -   | V/ns  |

| t <sub>CYC</sub> (UDBCLK) | UDBCLK clock cycle time (Divide-by-2 Mode) | t <sub>cyc</sub><br>(CLK) x2 | _       | -   | t <sub>cyc</sub><br>(CLK) x2 | -   | -   | ns    |

| t <sub>cyc</sub> (UDBCLK) | UDBCLK clock cycle time (Divide-by-3 Mode) | t <sub>cyc</sub><br>(CLK) x3 | _       | -   | t <sub>cyc</sub><br>(CLK) x3 | -   | -   | ns    |

| t <sub>w</sub> (UDBCLK)   | UDBCLK duty cycle                          | 40                           | 50      | 60  | 40                           | 50  | 60  | %     |

| t <sub>w</sub> (RESET_L)  | RESET pulse width LOCK MODE                | 10                           | _       | _   | 10                           | -   | _   | ns    |

| t <sub>w</sub> (RESET_L)  | RESET pulse width BYPASS MODE              | t <sub>cyc</sub><br>(CLK) x3 | _       | _   | t <sub>cyc</sub><br>(CLK) x3 | -   | _   | ns    |