### **Features**

- M-976-2C2 MFC Transceiver

- Designed for R2 MF signaling transmit and receive levels used in China

- Direct A-Law PCM digital input

- 2.048 Mb/s clocking

- Programmable forward/backward mode

- · Programmable compelled/direct control

- Operates with standard codecs for analog interfacing

- Microprocessor read/write interface

- Binary or 2-of-6 data formats

- Dual-channel

- 5 volt power

# **Applications**

- Test equipment

- Trunk adapters

- Paging terminals

- Traffic recorder

- PBX's

# Description

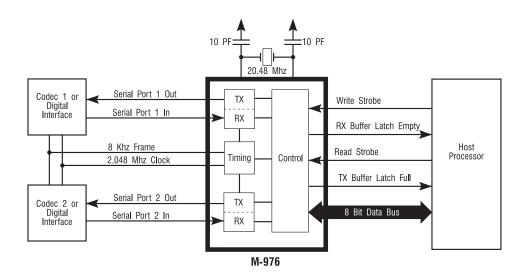

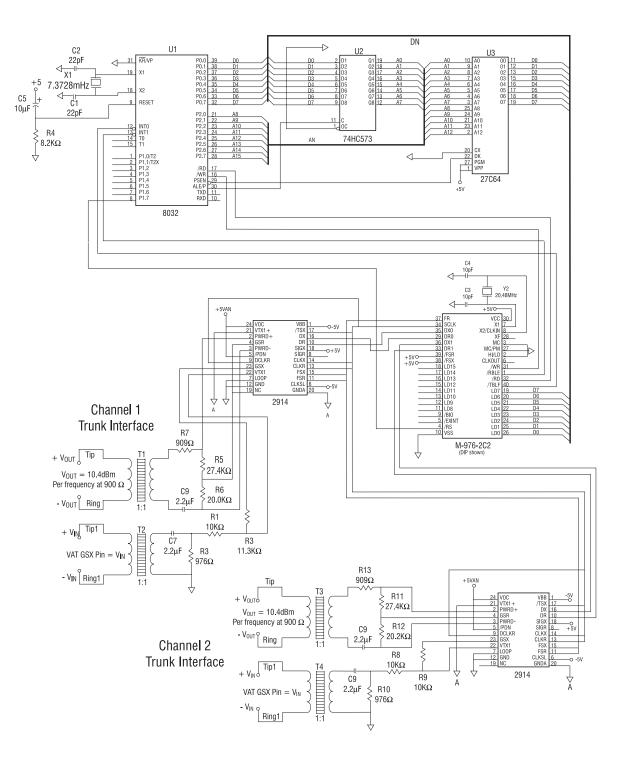

The M-976-2C2 MFC Transceiver contains all the logic necessary to transmit and receive MF signaling used in China, both (forward) and (backward) multifrequency signals on one integrated circuit (IC). The M-976 provides two transceiver channels.

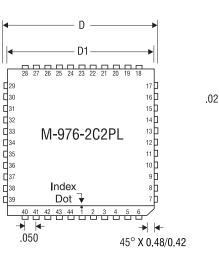

Operating with a 20.48 MHz crystal, the M-976 is capable of providing a direct digital interface to an Alaw-encoded PCM digital input. Each channel can be connected to an analog source using a coder-decoder (codec) as shown in the Block Diagram below.

The M-976 can be configured by the customer to operate with the transmitter and receiver either coupled together or independent, allowing it to handle a compelled cycle automatically or via command from the host processor. The M-976 is configured and controlled through an integral coprocessor port.

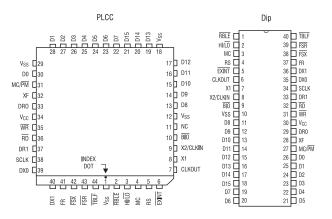

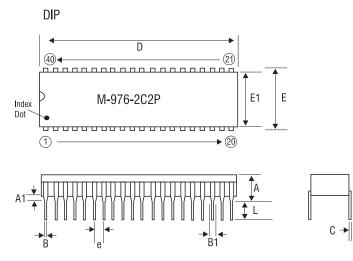

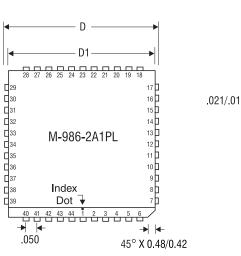

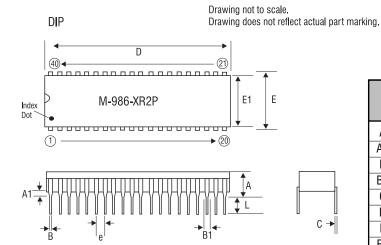

The M-976-2C2X is available in two packaging options. The M-976-2C2P is a plastic 40-pin DIP and the M-976-2C2PL is a 44-pin plastic leaded chip carrier.

### **Ordering Information**

| Part #      | Description        |

|-------------|--------------------|

| M-976-2C2P  | 40-pin plastic DIP |

| M-976-2C2PL | 44-pin PLCC        |

# Block Diagram

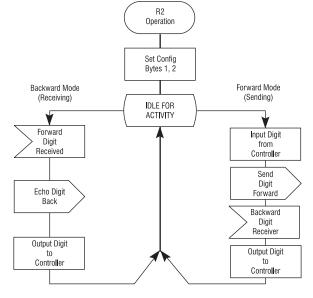

# **Functional Description**

The M-976 can be set up for various operating modes by writing two configuration bytes to the coprocessor port. The format of the two configuration bytes is shown in the Configuration Bytes table on page 2 and the configuration options are described in the following paragraphs.

### **Configuration Options**

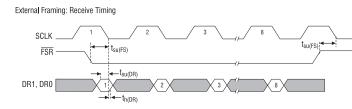

*External/Internal Codec Clock (ECLK):* If external codec clocking is selected, an external clocking source provides an 8kHz transmit framing clock and an 8kHz receive framing clock. It also provides a serial bit clock with a frequency that is a multiple of 8 kHz between 2.496 MHz and 216 kHz for exchange of data via the serial ports. When internal codec clocking is selected, the M-976 provides an 8kHz framing clock and a 2.048 MHz serial bit clock.

*Binary/2 of 6 Input/Output (IOM):* When the 2-of-6 input/output is selected, the M-976 encodes the received R2 MF tone pair into a 6-bit format, where each bit represents one of the six possible frequencies. A logic high level indicates the presence of a frequency. The digital input to the M-976 that selects the transmitted R2 MF tone pair must also be coded in the 2-of-6 format.

When binary input/output is selected, the M-976 encodes the received MF tone pair into a 4 bit binary format. The digital input to the M-976 that selects the

transmitted R2 MF tone pair must also be coded in a 4 bit binary format.

*Enable/Disable Channel (ENC):* When a channel is disabled, the receiver does not process its codec input for R2 MF tones, and the transmitter does not respond to transmit commands. If a transmit command is given while the channel is enabled, the tone off command must be given before the channel is disabled. Disabling the channel does not automatically shut off the transmitter. When a channel is enabled, the receiver and transmitter for that channel function normally.

*End-of-Digit Indication (EOD):* The end-of-digit indication option configures the M-976 to inform the host processor when the far end terminates transmission of the R2 MF tone it is sending. If this option is disabled, the host processor will not be notified when tone transmission terminates.

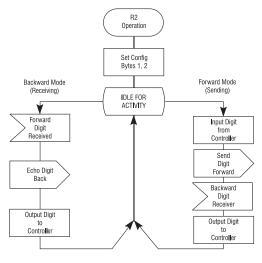

Automatic Compelled/Manual Sequence Signaling (CMP): When manual mode is selected, R2 MF tone transmission is turned on and off only via command from the host processor.

If the automatic mode is selected, the transmitter and receiver perform the compelled signaling handshake automatically. The specifics of operation are different for the forward and backward configurations.

In forward mode, the transceiver can exist in two states, STATE 1 and STATE 2:

• STATE 1: No backward signal detected.

|       |       |            | Configurat                                                            | ion Byte 1                                                            |                      |                   |         |  |  |  |

|-------|-------|------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|-------------------|---------|--|--|--|

| Bit 7 | Bit 6 | Bit 5      | Bit 4                                                                 | Bit 3                                                                 | Bit 2                | Bit 1             | Bit O   |  |  |  |

| 0     | 0     | ECLK       | IOM                                                                   | ENC1                                                                  | EOD1                 | CMP1              | FB1     |  |  |  |

| ECLK  | Chanı | nels 1 & 2 | 1 = External cod                                                      | lec clock; 0 = Inter                                                  | nal codec clock      |                   |         |  |  |  |

| IOM   | Chanı | nels 1 & 2 | 1 = Binary inpu                                                       | t/output; 0 = 2-of-6                                                  | input/output         |                   |         |  |  |  |

| ENC1  | Chanı | nel 1      | 1 = Enable char                                                       | inel; 0 = Disable ch                                                  | annel                |                   |         |  |  |  |

| EOD1  | Chanı | nel 1      | 1 = Indicate end                                                      | l of digit; 0 = No er                                                 | nd of digit indicati | ion               |         |  |  |  |

| CMP1  | Chanı | nel 1      | 1 = Automatic (                                                       | 1 = Automatic Compelled mode; 0 = Manual mode                         |                      |                   |         |  |  |  |

| FB1   | Chanı | nel        | 1 = Forward mode (Tx backward frequencies and Rx forward frequencies) |                                                                       |                      |                   |         |  |  |  |

|       |       |            | 0 = Backward n                                                        | node (Tx backward                                                     | frequencies and I    | Rx forward freque | encies) |  |  |  |

|       |       | _          | Configurat                                                            | ion Byte 2                                                            |                      |                   |         |  |  |  |

| Bit 7 | Bit 6 | Bit 5      | Bit 4                                                                 | Bit 3                                                                 | Bit 2                | Bit 1             | Bit O   |  |  |  |

| 0     | 1     | 1          | 0                                                                     | ENC2                                                                  | EOD2                 | CMP2              | FB2     |  |  |  |

| ENC2  | Chanı | nel 2      | 1 = Enable channel; 0 = Disable channel                               |                                                                       |                      |                   |         |  |  |  |

| EOD2  | Chanı | nel 2      | 1 = Indicate end of digit; 0 = No end of digit indication             |                                                                       |                      |                   |         |  |  |  |

| CMP2  | Chanı | nel 2      | 1 = Automatic Compelled mode; 0 = Manual mode                         |                                                                       |                      |                   |         |  |  |  |

| FB2   | Chanı | nel 2      | 1 = Forward mo                                                        | 1 = Forward mode (Tx forward frequencies and Rx backward frequencies) |                      |                   |         |  |  |  |

|       |       |            | 0 = Backward n                                                        | node(Tx backward f                                                    | frequencies and F    | Rx forward freque | encies) |  |  |  |

### **Configuration Bytes**

Transmitter under control of the host.

• STATE 2: Backward signal detected. Transmitter off unconditionally.

A Transmit Tone Command written while the transceiver is in STATE 1 will be acted upon immediately. The transmitter is unconditionally disabled upon entry into STATE 2. If a transmit command is written to the transceiver while in STATE 2, that command will become pending. Upon entry into STATE 1, a pending transmit command is acted upon.

In backward mode, the transceiver can exist in two states, STATE 1 and STATE 2:

- STATE 1: No forward signal detected. Transmitter off unconditionally.

- STATE 2: Forward signal detected. Transmitter transmits backward signal.

A transmit tone command written while the transceiver is in STATE 2 will be acted upon immediately. The transmitter is unconditionally disabled upon entry into STATE 1. If a transmit command is written to the transceiver while in STATE 1, that command will become pending. Upon entry into STATE 2, a pending transmit command is acted upon.

# **Binary Coding Format**

# Automatic Compelled Mode Operation

EXAMPLE: Assume that the transceivers at both ends of a link are configured in automatic compelled mode. Both transceivers are in STATE 1. A compelled signaling sequence begins with the R2F host writing a transmit command byte to its transceiver via the coprocessor bus. The transceiver immediately begins transmitting the signal.

| Byte                      | Bit 7     | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2    | Bit 1      | Bit O  |

|---------------------------|-----------|-----------|---------|-------|-------|----------|------------|--------|

| Transmit tone command     | 1         | CHN       | 0       | 0     | A     | В        | С          | D      |

| Receive tone return       | 0         | CHN       | 0       | 0     | A     | В        | С          | D      |

| CHN: 1 = channel 2; 0 = c | nannel 1  |           |         |       |       |          | ·          |        |

| R2 MF Frequencies:        |           |           |         |       |       |          |            |        |

| ABCD For                  | ward (Hz) | Backwai   | rd (Hz) | ABCD  | Forw  | ard (Hz) | Backwar    | d (Hz) |

| 0000 Tone                 | off       | Tone off  |         | 1000  | 1500  | & 1860   | 1020 & 66  | 0      |

| 0001 1380                 | & 1500    | 1140 & 10 | 020     | 1001  | 1620  | & 1860   | 900 & 660  |        |

| 0010 1380                 | & 1620    | 1140 & 90 | 00      | 1010  | 1740  | & 1860   | 780 & 660  |        |

| 0011 1500                 | & 1620    | 1020 & 90 | 00      | 1011  | 1380  | & 1980   | 1140 & 54  | 0      |

| 0100 1380                 | & 1740    | 1140 & 78 | 30      | 1100  | 1500  | & 1980   | 1020 & 540 | 0      |

| 0101 1500                 | & 1740    | 1020 & 78 | 30      | 1101  | 1620  | & 1980   | 900 & 540  |        |

| 0110 1620                 | & 1740    | 900 & 780 | )       | 1110  | 1740  | & 1980   | 780 & 540  |        |

| 0111 1380                 | & 1860    | 1140 & 66 | 60      | 1111  | 1860  | & 1980   | 660 & 540  |        |

### 2 of 6 Coding Format

| Byte                    | Bit 7       | Bit 6  | Bit 5    | Bit 4    | Bit 3 | Bit 2       | Bit 1 | Bit O    |

|-------------------------|-------------|--------|----------|----------|-------|-------------|-------|----------|

| Transmit tone command   | 1           | CHN    | F6       | F5       | F4    | F3          | F2    | F1       |

| Receive tone return     | 0           | CHN    | F6       | F5       | F4    | F3          | F2    | F1       |

| CHN: 1 = channel 2; 0 = | channel 1   |        |          |          |       |             |       |          |

| R2 MF Frequencies:      |             |        |          |          |       |             |       |          |

| Bit name F              | orward (Hz) | Backwa | ard (Hz) | Bit name | Fo    | orward (Hz) | Backw | ard (Hz) |

| F6 1                    |             |        | 16       | 1620     |       |             |       |          |

| F5 1                    | 860         | 660    |          | F2       | 15    | 00          | 1020  |          |

| F4 1                    | 740         | 780    |          | F1       | 13    | 80          | 1140  |          |

The R2B transceiver detects the signal, enters STATE 2, and outputs the received tone code to its host via the coprocessor port. If the R2B host had determined the next tone to transmit and written a transmit command to the transceiver prior to entry into STATE 2, the state transition will cause this tone to be transmitted. Otherwise, the R2B transmitter waits for a transmit tone command from the host, and starts transmitting a tone once the transmit tone command is received.

The R2F transceiver detects the backward signal, enters STATE 2, and outputs the received tone code to its host. Entry into STATE 2 unconditionally disables the transmitter.

The R2B transceiver detects the absence of signal, enters STATE 1, and informs the host with the end-oftone code if configured to do so. Entry into STATE 1 unconditionally disables the transmitter.

The R2F transceiver detects the absence of signal, enters STATE 1, and informs the host with the end-oftone code if configured to do so. If the R2F host had determined the next signal to transmit and written a transmit command to the transceiver prior to entry into STATE 1, the state transition y20will cause this signal to be transmitted. Otherwise, the transmitter remains silent until the next transmit command by its host.

*Forward/Backward Frequencies (FB):* When forward mode is selected, the R2F (forward) frequencies are transmitted and R2B (backward) frequencies are received. When backward mode is selected, R2B frequencies are transmitted and R2F frequencies are received. The R2F frequencies are 1380, 1500, 1620, 1740, 1860, and 1980 Hertz. The R2B frequencies are 540, 660, 780, 900, 1020, and 1140 Hz.

*Initial Configuration:* The configuration of the M-976 immediately after a reset will be as follows:

- End-of-digit indication ON

- Forward mode ON

- Channel disabled

- 2-of-6 input/output

- External serial and serial frame clocks.

Also, the M-976 will place 00 hex on the coprocessor port to indicate to the host processor that it is working.

# **Transmit Tone Command**

The transmit tone command allows the host processor to transmit any two of the 6 possible frequencies in the transmission mode the channel has been configured for (forward or backward). The format of the command depends on whether the M-976 is configured for binary format or 2-of-6 format.

### **Recieved Tone Detection**

When a tone is detected by the M-976, the TBLF output goes low, indicating reception of the tone to the

host processor. The host processor can determine which tone was detected and which channel the tone was detected on by reading data from the M-976 coprocessor port. The M-976 will return a single byte indicating the tone received and the channel that the tone was received on. The format of the returned byte depends on whether the M-976 is configured for binary or 2-of-6 coding. See Tables 2 and 3.

# **Coprocessor Port**

Commands are written to the M-976 via the coprocessor port, and data indicating the received R2 MF tone is read from the coprocessor port.

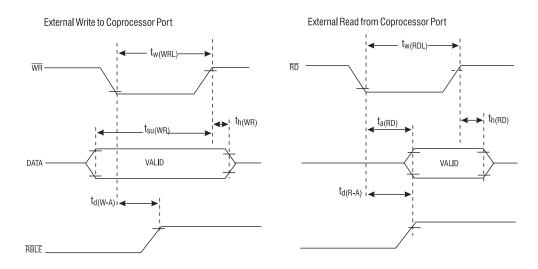

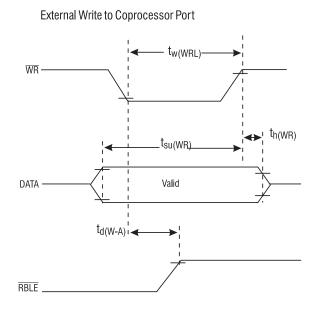

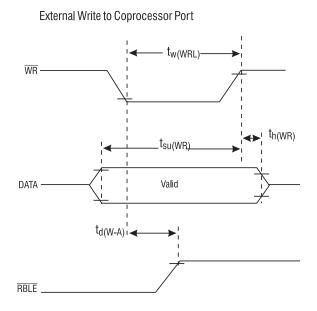

*Writing to the Coprocessor Port:* The following sequence describes writing a command to the M-976.

- (1) The  $\overline{\text{WR}}$  signal is driven low by the host processor.

- (2) The RBLE (receive buffer latch empty) signal transitions to a logic high level.

- (3) Data is written from LD7-LD0 to the receive buffer latch (D7-D0) when the WR signal goes high.

- (4) The RBLE signal transitions to a logic low level after the M-976 reads the data. This signals the host processor that the receive buffer is empty.

# Note: The RBLE should be low before writing to the coprocessor.

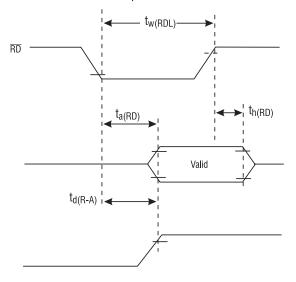

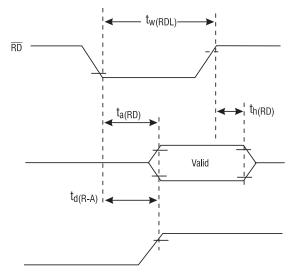

Reading the Coprocessor Port: The following sequence describes reading received tone information from the coprocessor port.

- (1) The TBLF (transmit buffer latch full) port pin on the M-976 goes low indicating the reception of a tone.

- (2) The host processor detects the low logic level on the TBLF pin either by polling a connected port pin or by an interrupt.

- (3) The host processor drives the RD signal low.

- (4) The TBLF (transmit buffer latch full) signal transitions to a logic high level.

- (5) Data is driven onto D7-D0 by the M-976 until the RD signal is driven high by the host processor.

### **Clock Characteristics and Timing**

Internal Clock Option: The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN. The crystal must be 20.48 MHz, fundamentalmode, and parallel resonant, with an effective series resistance of 30 ohms, a power dissipation of 1 mW, and be specified at a load capacitance of 20 pf.

External Clock Option: An external frequency source

can be used by injecting the frequency directly in X2/CLKIN, with X1 left unconnected. The external frequency injected must conform to the specifications Table on page 7.

# Flammability/Reliability Specifications

| Reliability:  |  |

|---------------|--|

| Flammability: |  |

480 FITS (failures/billion hours) Passes UL 94 V-0 tests

# **Signal Description**

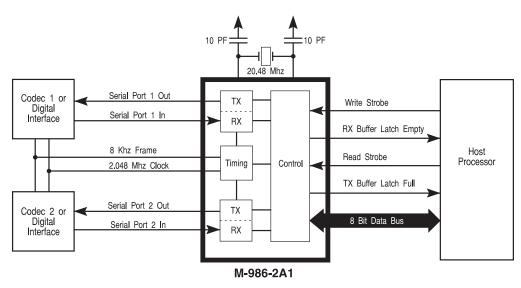

| Signal            | DIP<br>Pinout      | PLCC<br>Pinout      | I/O/Z             | Description                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|--------------------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: Pl          | ease see the follo | wing definitions: [ | )IP = Dual In-lin | e Package PLCC = Plastic Leaded Chip Carrier                                                                                                                                                                                                                                                                                                                |

| D8-D15            | 11-18              | 13-17, 19-21        | I/0/Z             | Unused. Leave open.                                                                                                                                                                                                                                                                                                                                         |

| D0-D7             | 19-26              | 22-28, 30           | I/0/Z             | 8-bit coprocessor latch.                                                                                                                                                                                                                                                                                                                                    |

| TBLF              | 40                 | 44                  | 0                 | Transmit buffer latch full flag.                                                                                                                                                                                                                                                                                                                            |

| RBLE              | 1                  | 2                   | 0                 | Receive buffer latch empty flag                                                                                                                                                                                                                                                                                                                             |

| HI/ <del>LO</del> | 2                  | 3                   |                   | Latch byte select pin. Tie low.                                                                                                                                                                                                                                                                                                                             |

| BIO               | 9                  | 10                  |                   | Unused. Leave open.                                                                                                                                                                                                                                                                                                                                         |

| RD                | 32                 | 36                  | 1/0               | Used by the external processor to read from the coprocessor latch by driving the $\overline{RD}$ line active (low), thus enabling the output latch to drive the latched data. When the data has been read, the external device must bring the $\overline{RD}$ line high.                                                                                    |

| EXINT             | 5                  | 6                   | I                 | Unused. Leave open.                                                                                                                                                                                                                                                                                                                                         |

| MC                | 3                  | 4                   | I                 | Microcomputer mode select pin. Tie low.                                                                                                                                                                                                                                                                                                                     |

| MC/PM             | 27                 | 31                  | I                 | Coprocessor mode select pin. Tie low.                                                                                                                                                                                                                                                                                                                       |

| RS                | 4                  | 5                   | I                 | Reset input for initializing the device. When an active low is placed on $\overline{\text{RS}}$ pin for a minimum of five clock cycles, $\overline{\text{RD}}$ and $\overline{\text{WR}}$ are forced high, and the data bus (D7 through D0) goes to a high impedance state. The serial port clock and transmit outputs also go to the high impedance state. |

| WR                | 31                 | 35                  | 1/0               | Used by the external processor to write data to the coprocessor port. To write data the external processor drives the WR line low, places data on the data bus, and then drives the WR line high to clock the data into the on-chip latch.                                                                                                                  |

| XF                | 28                 | 32                  | 0                 | Watchdog signal. Toggles at least once every 15 milliseconds when<br>the processor is functioning properly. If the pin is not toggled at<br>least once every 15 ms, the processor is lost and should be reset.                                                                                                                                              |

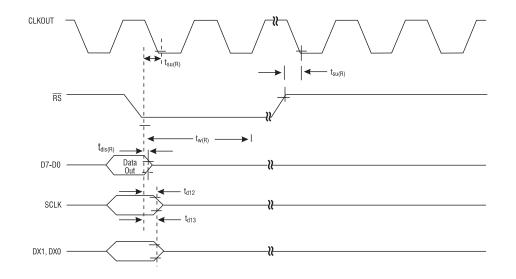

| CLKOUT            | 6                  | 7                   | 0                 | System clock output (one-fourth crystal/CLKIN frequency, nominally 5.12 MHz).                                                                                                                                                                                                                                                                               |

| V <sub>cc</sub>   | 30                 | 34                  | I                 | 5V supply pin.                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>   | 10                 | 1, 12, 18, 29       | I                 | Ground pin.                                                                                                                                                                                                                                                                                                                                                 |

| X1                | 7                  | 8                   | 0                 | Crystal output pin for internal oscillator. If an internal oscillator is not used, this pin should be left unconnected.                                                                                                                                                                                                                                     |

| X2/CLKIN          | 8                  | 9                   | I                 | Input pin to the internal oscillator (X2) from the crystal.<br>Alternatively, an input pin for the external oscillator (CLKIN).                                                                                                                                                                                                                             |

| DR0 & DR1         | 29 & 33            | 33, 37              | I                 | Serial-port receive-channel inputs. 2.048 MHz serial data is received<br>in the receive registers via these pins. DR0 = channel 1; DR1 =<br>channel 2                                                                                                                                                                                                       |

| DX0 & DX1         | 35 & 36            | 39, 40              | 0                 | Serial-port transmit-channel outputs. 2.048 MHz serial data is transmitted from the transmit registers on these pins. These outputs are in the high-impedance state when not transmitting.                                                                                                                                                                  |

# Signal Description (continued)

| Signal | DIP<br>Pinout | PLCC<br>Pinout | I/O/Z | Description                                                                                                                                                                                                                                                                                                            |

|--------|---------------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FR     | 37            | 41             | 0     | 8 kHz internal serial-port framing output. If internal clocking is selected, serial-port transmit and receive operations occur simultaneously on an active (high) FR framing pulse.                                                                                                                                    |

| FSR    | 39            | 43             | I     | 8 kHz external serial-port receive-framing input. If external clocking<br>is selected, data is received via the receive pins (DR1 and DR0) on<br>the active (low) FSR input. The falling edge of FSR initiates the<br>receive process, and the rising edge causes the M-986 to process<br>the data.                    |

| FSX    | 38            | 42             | Ι     | 8 kHz external serial-port transmit-framing input. If external clocking<br>is enabled, data is transmitted on the transmit pins (DX1, DX0) on<br>the active (low) input. The falling edge of FSX initiates the transmit<br>process,and the rising edge causes the M-986 to internally load data<br>for the next cycle. |

| SCLK   | 34            | 38             | I/0/Z | 2.048 MHz serial-port clock. Master clock for transmitting and receiving serial-port data. Configured as an input in external clocking mode or output in internal clocking mode. Reset (RS) forces SCLK to the high-impedance state.                                                                                   |

# Absolute Maximum Ratings Over Specified Temperature Range

| Supply voltage range, V <sub>CC</sub> | -0.3 V to 7 V  |

|---------------------------------------|----------------|

| Input voltage range                   | -0.3 V to 15 V |

| Output voltage range                  | -0.3 V to 15 V |

| Ambient air temperature range         | 0°C to 70°C    |

| Storage temperature range             | -45°C to 150°C |

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure of the device to the absolute maximum ratings for an extended period may degrade the device and effect its reliability.

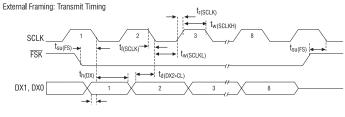

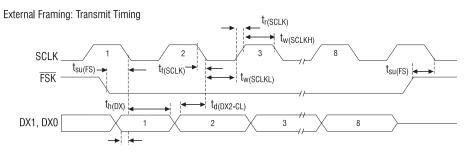

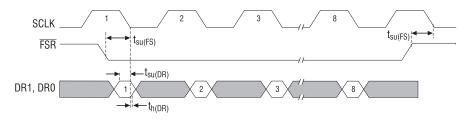

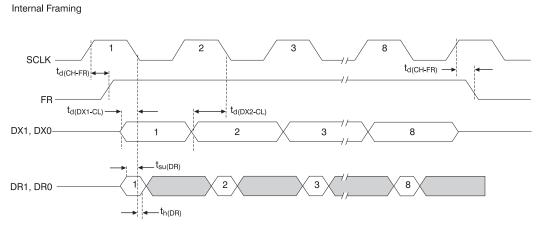

# **Serial Port Timing**

|                         | Parameter                                    | Min | Nom    | Max  | Units |

|-------------------------|----------------------------------------------|-----|--------|------|-------|

| t <sub>d</sub> (CH-FR)  | Internal framing delay from SCLK rising edge | -   | -      | 70   | ns    |

| t <sub>d</sub> (DX1-CL) | DX bit 1 valid before SCLK falling edge      | 20  | -      | -    | ns    |

| t <sub>d</sub> (DX2-CL) | DX bit 2 valid before SCLK falling edge      | 20  | -      | -    | ns    |

| t <sub>h</sub> (DX)     | DX hold time after SCLK falling edge         | 244 | -      | -    | ns    |

| t <sub>su</sub> (DR)    | DR setup time before SCLK falling edge       | 20  | -      | -    | ns    |

| t <sub>h</sub> (DR)     | DR hold time after SCLK falling edge         | 20  | -      | -    | ns    |

| t <sub>c</sub> (SCLK)   | Serial port clock cycle time                 | 399 | 488.28 | 4770 | ns    |

| t <sub>f</sub> (SCLK)   | Serial port clock fall time                  | -   | -      | 30   | ns    |

| t <sub>r</sub> (SCLK)   | Serial port clock rise time                  | -   | -      | 30   | ns    |

| t <sub>w</sub> (SCLKL)  | Serial port clock low-pulse duration*        | 220 | 244.14 | 2500 | ns    |

| t <sub>w</sub> (SCLKH)  | Serial port clock high-pulse duration*       | 220 | 244.14 | 2500 | ns    |

| t <sub>su</sub> (FS)    | FSX/FSR setup time before SCLK falling edge  | 100 | -      | -    | ns    |

$^{\star}$  The duty cycle of the serial port clock must be within 45% to 55%.

|                 | Paramete             | r             | Test Conditions              |                                | Min                  | Тур | Max | Unit |

|-----------------|----------------------|---------------|------------------------------|--------------------------------|----------------------|-----|-----|------|

| I <sub>CC</sub> | Supply current       | f = 20.5 MHz, | V <sub>CC</sub> = 5.5V,      |                                | -                    | 50  | 75  | mA   |

|                 |                      |               | T <sub>A</sub> = 0° to 70 °C |                                |                      |     |     |      |

| V <sub>OH</sub> | High-level output vo | oltage        | I <sub>OH</sub> = MAX        |                                | 2.4                  | 3   | -   | V    |

|                 |                      |               | I <sub>0H</sub> = 20 μ A     |                                | V <sub>CC</sub> -0.4 | -   | -   | V    |

| V <sub>OL</sub> | Low-level output vo  | ltage         | I <sub>OL</sub> = MAX        |                                | -                    | 0.3 | 0.6 | V    |

| I <sub>oz</sub> | Off-state output cur | rent          | V <sub>CC</sub> = MAX        | $V_0 = 2.4 V$<br>$V_0 = 0.4 V$ | -                    | -   | 20  | μA   |

|                 |                      |               |                              | $V_0 = 0.4 V$                  | -                    | -   | -20 | μA   |

| II.             | Input current        |               | $V_1 = V_{SS}$ to $V_{CC}$   | Except CLKIN                   | -                    | -   | ±20 | μA   |

|                 |                      |               |                              | CLKIN                          | -                    | -   | ±50 | μA   |

| CI              | Input capacitance    | Data bus      | f = 1 MHz, all oth           | ner pins 0 V                   | -                    | 25  | -   | pF   |

|                 |                      | All others    |                              |                                | -                    | 15  | -   | pF   |

| Co              | Output capacitance   | Data bus      |                              |                                | -                    | 25  | -   | pF   |

|                 |                      | All others    |                              |                                | -                    | 10  | -   | pF   |

# **Electrical Characteristics/Temperature Range**

# **External Frequency Specifications**

|                     | Parameter                    | Min    | Nom    | Max    | Unit |

|---------------------|------------------------------|--------|--------|--------|------|

| t <sub>c</sub> (MC) | Master clock cycle time      | 48.818 | 48.828 | 48.838 | ns   |

| t <sub>r</sub> (MC) | Rise time master clock input | -      | 5      | 10     | ns   |

| t <sub>f</sub> (MC) | Pulse duration master clock  | 20     | -      | -      | ns   |

# **Recommended Operating Conditions**

|                 | Parameter                               |                         | Min  | Nom | Max  | Unit |

|-----------------|-----------------------------------------|-------------------------|------|-----|------|------|

| V <sub>cc</sub> | Supply voltage                          |                         | 4.75 | 5   | 5.25 | V    |

| V <sub>SS</sub> | Supply voltage                          |                         | -    | 0   | -    | V    |

| V <sub>IH</sub> | High-level input voltage                | All inputs except CLKIN | 2    | -   | -    | V    |

|                 |                                         | CLKIN                   | 3    | -   | -    | V    |

| V <sub>IL</sub> | Low-level input voltage                 | All inputs except MC/MP | -    | -   | 0.8  | V    |

|                 |                                         | MC/MP                   | -    | -   | 0.6  | V    |

| I <sub>он</sub> | High-level output current (all outputs) |                         | -    | -   | -300 | μA   |

| I <sub>OL</sub> | Low-level output current (all outputs)  |                         | -    | -   | 2    | mA   |

| T <sub>A</sub>  | Operating free-air temperature          |                         | 0    | -   | 70   | ٦°   |

# **Coprocessor Interface Timing**

|                       | Parameter                                       | Min | Nom | Max | Unit |

|-----------------------|-------------------------------------------------|-----|-----|-----|------|

| t <sub>d(R-A)</sub>   | RD low to TBLF high                             | -   | -   | 75  | ns   |

| t <sub>d(W-A)</sub>   | WR low to RBLE high                             | -   | -   | 75  | ns   |

| t <sub>a(RD)</sub>    | RD low to data valid                            | -   | -   | 80  | ns   |

| t <sub>h(RD)</sub>    | Data hold time after $\overline{	ext{RD}}$ high | 25  | -   | -   | ns   |

| t <sub>su(WR)</sub>   | Data setup time prior to WR high                | 30  | -   | -   | ns   |

| t <sub>h(WR)</sub>    | Data hold time after WR high                    | 25  | -   | -   | ns   |

| t <sub>w(RDL)</sub>   | RD low-pulse duration                           | 80  | -   | -   | ns   |

| t <sub>w(WRL)</sub>   | WR low-pulse duration                           | 60  | -   | -   | ns   |

| t <sub>wr(RBLE)</sub> | RBLE↑ to RBLE↓                                  | -   | -   | 1   | ms   |

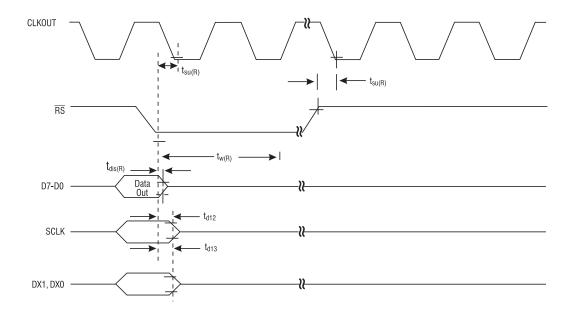

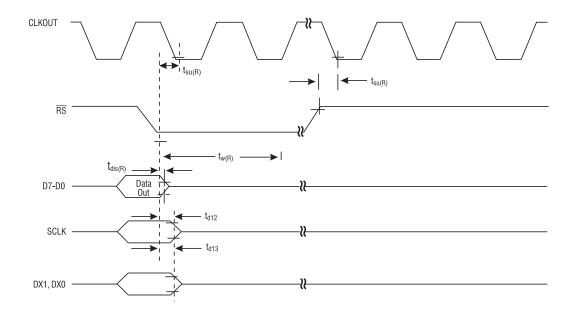

# Reset (RS) Timing

|                      | Parameter                                                         | Test Conditions         | Min | Max | Unit |

|----------------------|-------------------------------------------------------------------|-------------------------|-----|-----|------|

| t <sub>dis</sub> (R) | Data bus disable time after $\overline{RS}$                       | R <sub>L</sub> = 825 Ω  | -   | 75  | ns   |

| t <sub>d12</sub>     | Delay time from $\overline{\text{RS}}$ to high-impedance SCLK     | C <sub>L</sub> = 100 pF | -   | 200 | ns   |

| t <sub>d13</sub>     | Delay time from $\overline{\text{RS}}$ to high-impedance DX1, DX0 |                         | -   | 200 | ns   |

| t <sub>su</sub> (R)  |                                                                   |                         |     | -   | ns   |

| t <sub>w</sub> (R)   | RS pulse duration                                                 | 245                     | -   | ns  |      |

# **CLKOUT Timing Parameters**

|                      | Parameter                                          | Test Conditions         | Min    | Nom    | Max | Unit |

|----------------------|----------------------------------------------------|-------------------------|--------|--------|-----|------|

| t <sub>c</sub> (C)   | CLKOUT cycle time                                  | 195.27                  | 195.31 | 195.35 | ns  |      |

| t <sub>r</sub> (C)   | CLKOUT rise time                                   | R <sub>L</sub> = 825 Ω  | -      | 10     | -   | ns   |

| t <sub>f</sub> (C)   | CLKOUT fall time                                   | C <sub>L</sub> = 100 pF | -      | 8      | -   | ns   |

| t <sub>d</sub> (MCC) | Delay time CLKIN $\uparrow$ to CLKOUT $\downarrow$ |                         | 25     | -      | 60  | ns   |

# **Transmitter Characteristics**

|                 | Parameter                            | Test Conditions    | Min   | Тур   | Max   | Unit |

|-----------------|--------------------------------------|--------------------|-------|-------|-------|------|

| F <sub>os</sub> | Frequency offset                     | From nominal       | -     | -     | ±4    | Hz   |

| TŴ              | Twist                                | High/low           | -     | -     | ±0.6  | dB   |

| A <sub>S</sub>  | Signal amplitude                     | Per component      | -9.00 | -8.00 | -7.00 | dBm0 |

| Ts              | Time skew                            | Between components | -     | -     | 0.5   | ms   |

| P <sub>hi</sub> | Power due to harmonic distortion and |                    |       |       |       |      |

|                 | intermodulation                      | 300 to 400 Hz      | -     | -     | -46.5 | dBm0 |

# **Reciever Characteristics**

|                  | Parameter                                                 | Test Conditions                                          | Min  | Max | Unit |

|------------------|-----------------------------------------------------------|----------------------------------------------------------|------|-----|------|

| A <sub>d</sub>   | Detect amplitude                                          | Per frequency                                            | -31  | -1  | dBm0 |

| A <sub>nd</sub>  | No-detect amplitude                                       | Per frequency                                            | -38  | -31 | dBm0 |

| F <sub>d</sub>   | Detect with frequency offset                              | From nominal                                             | ±10  | -   | Hz   |

| TW <sub>d</sub>  | Detect with twist                                         | Adjacent frequencies                                     | ±5   | -   | dB   |

| _                |                                                           | Nonadjacent frequencies                                  | ±7   | -   | dB   |

| TW <sub>nd</sub> | No detect with twist                                      |                                                          |      | -   | dB   |

| T3 <sub>r</sub>  | Third R2F tone reject Relative to highest level frequency |                                                          | -20  | -   | dB   |

| FF <sub>d</sub>  | Detect R2B with R2F disturbing                            | Above lowest level R2B tone<br>(-12.5 dBm0 max.)         | 13.5 | -   | dB   |

| FT <sub>nd</sub> | No detect R2F with 2 out-of-band sine waves               | Any frequencies from<br>330 - 1150 Hz and 2130 - 3400 Hz | -1   | -   | dBm0 |

| RT <sub>nd</sub> | No detect R2B with 2 out-of-band sine waves               | Any frequencies from 1300-3400 Hz                        | -1   | -   | dBm0 |

| T <sub>on</sub>  | Tone time                                                 | Reject                                                   | 7    | -   | ms   |

| T <sub>int</sub> | Interrupted tone time                                     | Reject                                                   | 7    | -   | ms   |

| T <sub>or</sub>  | Operate and release time                                  |                                                          | -    | 80  | ms   |

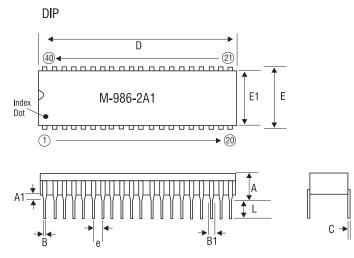

# **Pin Assignments**

CLARE

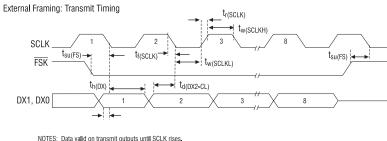

# **External Framing Timing Diagrams**

NOTES: Data valid on transmit outputs until SCLK rises. The most significant bit is shifted first.

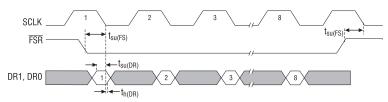

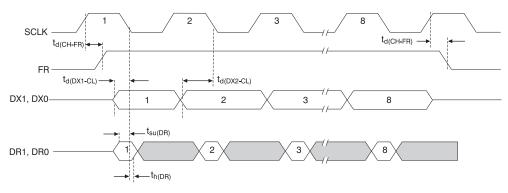

# **Internal Framing Timing**

#### Internal Framing 2 8 SCLK t<sub>d(CH-FR)</sub> t<sub>d(CH-FR)</sub> FR t<sub>d(DX1-CL)</sub> t<sub>d(DX2-CL)</sub> DX1, DX0-1 2 3 8 t<sub>su(DR)</sub> DR1, DR0 2 3 8 Note: The most significant bit is shifted first.

# **Reset Timing**

# Coprocessor Timing

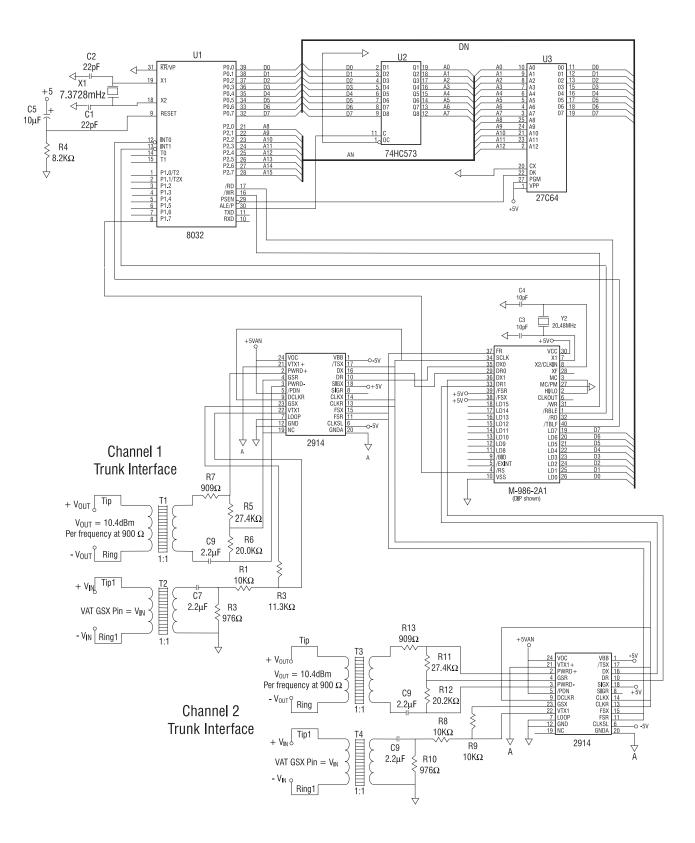

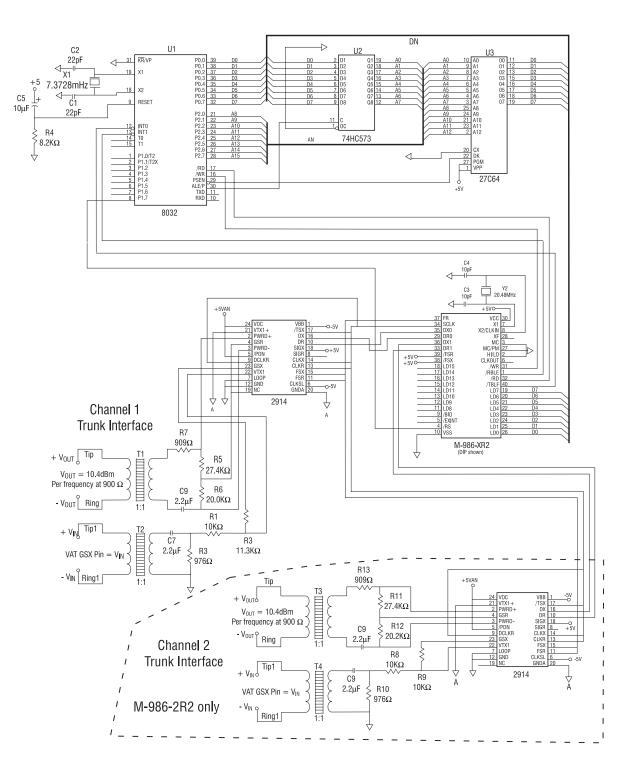

# M-986 Dual Channel 4-Wire Interface Circuit

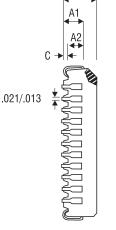

# **Mechanical Dimensions**

|    |          | Tolera | ances       |       |  |

|----|----------|--------|-------------|-------|--|

|    | (inc     | hes)   | Metric (mm) |       |  |

|    | Min      | Max    | Min         | Max   |  |

| Α  | -        | .250   | -           | 6.35  |  |

| A1 | .015     | -      | .39         |       |  |

| В  | .014     | .022   | .36         | .56   |  |

| B1 | .030     | .070   | .77         | 1.78  |  |

| С  | .008     | .015   | .20         | .38   |  |

| D  | 1.98     | 2.095  | 50.30       | 53.20 |  |

| E  | .600     | .625   | 15.24       | 15.87 |  |

| E1 | .485     | .580   | 12.32       | 14.73 |  |

| е  | .100 BSC |        | 2.54        | BSC   |  |

| L  | .115     | .200   | 2.93        | 5.08  |  |

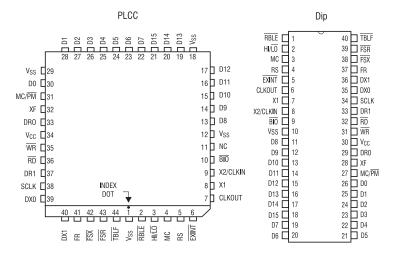

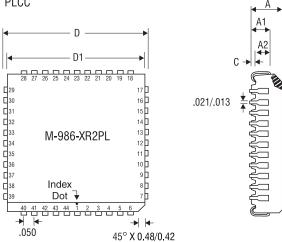

PLCC

|    | Tolerances |      |        |       |  |  |

|----|------------|------|--------|-------|--|--|

|    |            | hes) | Metric |       |  |  |

|    | Min        | Max  | Min    | Max   |  |  |

| A  | .165       | .180 | 4.19   | 4.57  |  |  |

| A1 | .090       | .20  | 2.29   | 5.08  |  |  |

| A2 | .062       | .083 | 1.58   | 2.11  |  |  |

| С  | .020       | min  | .51    | min   |  |  |

| D  | .685       | .695 | 17.40  | 17.65 |  |  |

| D1 | .650       | .653 | 16.51  | 16.66 |  |  |

Drawing not to scale. Drawing does not reflect actual part marking.

### **CLARE LOCATIONS**

Clare Headquarters 78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900 Toll Free: 1-800-27-CLARE

Clare Switch Division 4315 N. Earth City Expressway Earth City, MO 63045 Tel: 1-314-770-1832 Fax: 1-314-770-1812

Clare Micronix Division 145 Columbia Aliso Viejo, CA 92656-1490 Tel: 1-949-831-4622 Fax: 1-949-831-4628

### SALES OFFICES

### **AMERICAS**

#### Americas Headquarters

Clare 78 Cherry Hill Drive Beverly, MA 01915 Tel: 1-978-524-6700 Fax: 1-978-524-4900 Toll Free: 1-800-27-CLARE

#### **Eastern Region**

Clare 603 Apache Court Mahwah, NJ 07430 Tel: 1-201-236-0101 Fax: 1-201-236-8685 Toll Free: 1-800-27-CLARE

#### **Central Region**

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824

#### Western Region

Clare 1852 West 11th Street, #348 Tracy, CA 95376 Tel: 1-209-832-4367 Fax: 1-209-832-4732 Toll Free: 1-800-27-CLARE

#### Canada

Clare Canada Ltd. 3425 Harvester Road, Suite 202 Burlington, Ontario L7N 3N1 Tel: 1-905-333-9066 Fax: 1-905-333-1824

### EUROPE

#### **European Headquarters**

CP Clare nv Bampslaan 17 B-3500 Hasselt (Belgium) Tel: 32-11-300868 Fax: 32-11-300890

#### France

Clare France Sales Lead Rep 99 route de Versailles 91160 Champlan France Tel: 33 1 69 79 93 50 Fax: 33 1 69 79 93 59

#### Germany

Clare Germany Sales ActiveComp Electronic GmbH Mitterstrasse 12 85077 Manching Germany Tel: 49 8459 3214 10 Fax: 49 8459 3214 29

#### Italy

C.L.A.R.E.s.a.s. Via C. Colombo 10/A I-20066 Melzo (Milano) Tel: 39-02-95737160 Fax: 39-02-95738829

#### Sweden

Clare Sales Comptronic AB Box 167 S-16329 Spånga Tel: 46-862-10370 Fax: 46-862-10371

#### **United Kingdom**

Clare UK Sales Marco Polo House Cook Way Bindon Road Taunton UK-Somerset TA2 6BG Tel: 44-1-823 352541 Fax: 44-1-823 352797

### **ASIA/PACIFIC**

#### Asian Headquarters

Clare Room N1016, Chia-Hsin, Bldg II, 10F, No. 96, Sec. 2 Chung Shan North Road Taipei, Taiwan R.O.C. Tel: 886-2-2523-6368 Fax: 886-2-2523-6369

#### http://www.clare.com

Clare, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in Clare's Standard Terms and Conditions of Sale, Clare, Inc. assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of Clare's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. Clare, Inc. reserves the right to discontinue or make changes to its products at any time without notice.

Specification: DS-M976-2C2-R3 ©Copyright 2001, Clare, Inc. All rights reserved. Printed in USA. 7/17/01

### **Features**

- Direct A-Law or µ-Law PCM digital input

- 2.048 Mb/s clocking

- Operates with standard codecs for analog interfacing

- Microprocessor read/write interface

- Binary or 2-of-6 data formats

- Dual-channel

- 5 volt power

### Applications

- Test equipment

- Trunk adapters

- Paging terminals

- Traffic recorders

- PBXs

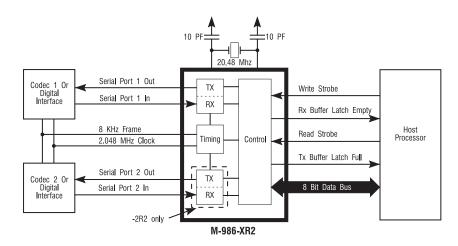

### Description

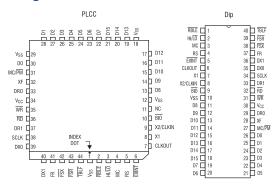

The M-986-2A1 dual channel MF Transceiver contains all the logic necessary to transmit and receive (North American) CCITT Region 1 multifrequency signals on one integrated circuit (IC).

Operating with a 20.48 MHz crystal, the M-986 is capable of providing a direct digital interface to a mlaw or A-law encoded PCM digital input. Each channel can be connected to an analog source using a coderdecoder (codec) as shown in the Block Diagram below.

The M-986 is configured and controlled through an integral coprocessor port.

### **Ordering Information**

| Part #      | Description        |

|-------------|--------------------|

| M-986-2A1P  | 40-pin plastic DIP |

| M-986-2A1PL | 44-pin PLCC        |

### **Block Diagram**

### Absolute Maximum Ratings Over Specified Temperature Range

| Supply voltage range, V <sub>CC</sub> | -0.3 V to 7 V  |

|---------------------------------------|----------------|

| Input voltage range                   | -0.3 V to 15 V |

| Output voltage range                  | -0.3 V to 15 V |

| Ambient air temperature range         | 0° to 150°C    |

| Storage temperature range             | -45°C to 150°C |

# **Function Description**

The M-986-2A1 can be set up for various modes of operation by writing two configuration bytes to the coprocessor port. The format of the two configuration bytes is shown in the Configuration Table on page 3 and the configuration options are described in the following paragraphs.

# **Configuration Options**

*External/Internal Codec Clock (ECLK):* If external codec clocking is selected, an external clocking source provides an 8 kHz transmit framing clock and an 8 kHz receive framing clock. It also provides a serial bit clock with a frequency that is a multiple of 8 kHz between 216 kHz and 2.496 MHz for exchange of data via the serial ports. When internal codec clocking is selected, the M-986-2A1 provides an 8 kHz framing clock and a 2.048 MHz serial bit clock.

2 of 6/Binary Input/Output (IOM): When the 2-of-6 input/output is selected, the M-986-2A1 encodes the received R1 MF tone pair into a 6-bit format, where each bit represents one of the six possible frequencies. A logic high level indicates the presence of a frequency. The digital input to the M-986-2A1 that selects the transmitted R1 MF tone pair must also be coded in the 2-of-6 format. Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure of the device to the absolute maximum ratings for an extended period may degrade the device and effect its reliability.

When binary input/output is selected, the M-986-2A1 encodes the received R1 MF tone pair into a 4 bit binary format. The digital input to the M-986-2A1 that selects the transmitted R1 MF tone pair must also be coded in a 4 bit binary format.

Enable/Disable Channel (ENC): When a channel is disabled, the receiver does not process its codec input for R1 MF tones, and the transmitter does not respond to transmit commands. If a transmit command is given while the channel is enabled, the "tone off" command must be given before the channel is disabled. Disabling the channel does not automatically shut off the transmitter. When a channel is enabled, the receiver and transmitter for that channel function normally.

Long/Short KP Tone Detection Time (KPL): When long KP tone detection is selected, the minimum on time for the KP tone to be detected is 55 milliseconds. When short KP tone detection is selected, the minimum on time for the KP tone to be detected is 30 milliseconds (the same as the minimum on time for the rest of the MF tones).

Enable MF Tone Detection After Reception of KP (KPEN): When this feature is enabled, MF tone detection is enabled after reception of the KP tone, and disabled after reception of ST, ST1, ST2, or ST3 tones. When this feature is disabled, MF tone detection is always enabled. Select A or  $\mu$ -law input/output (AMU) for A-law encoding, this bit is set to a 1, for  $\mu$ -law encoding it is set to 0.

|                 | Parameter Test Condition |               |                            | lin                           | Тур                  | Max | Unit |    |

|-----------------|--------------------------|---------------|----------------------------|-------------------------------|----------------------|-----|------|----|

| I <sub>cc</sub> | Supply current           | f = 20.5 MHz, | V <sub>CC</sub> = 5.5V,    |                               | -                    | 50  | 75   | mA |

|                 |                          |               | $T_A = 0^\circ$ to 70 °C   |                               |                      |     |      |    |

| V <sub>OH</sub> | High-level output vo     | oltage        | I <sub>OH</sub> = MAX      |                               | 2.4                  | 3   | -    | V  |

|                 |                          |               | I <sub>OH</sub> = 20 μ A   |                               | V <sub>CC</sub> -0.4 | -   | -    | V  |

| V <sub>OL</sub> | Low-level output vo      | ltage         | I <sub>OL</sub> = MAX      | DL = MAX                      |                      | 0.3 | 0.6  | V  |

| I <sub>oz</sub> | Off-state output cur     | rent          | $V_{CC} = MAX$             | V0 = 2.4 V                    | -                    | -   | 20   | μA |

|                 |                          |               |                            | V0 = 0.4 V                    | -                    | -   | -20  | μA |

| I,              | Input current            |               | $V_1 = V_{SS}$ to $V_{CC}$ | Except CLKIN                  | -                    | -   | ±20  | μA |

|                 |                          |               |                            | CLKIN                         | -                    | -   | ±50  | μA |

| C               | Input capacitance        | Data bus      | f = 1 MHz, all oth         | f = 1 MHz, all other pins 0 V |                      | 25  | -    | pF |

|                 |                          | All others    |                            |                               | -                    | 15  | -    | pF |

| $C_0$           | Output capacitance       | Data bus      |                            |                               | -                    | 25  | -    | pF |

|                 |                          | All others    |                            |                               | -                    | 10  | -    | pF |

# **Electrical Characteristics/Temperature Range**

# Configuration

CLARE

|                   | Configuration Byte 1                                                                             |       |                                                                                                                                                                                                                                                                                                                                                                |              |       |       |       |  |

|-------------------|--------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|-------|--|

| Bit 7             | Bit 6                                                                                            | Bit 5 | Bit 4                                                                                                                                                                                                                                                                                                                                                          | Bit 3        | Bit 2 | Bit 1 | Bit O |  |

| 0                 | 0                                                                                                | ECLK  | IOM                                                                                                                                                                                                                                                                                                                                                            | ENCI         | KPL1  | KPEN1 | 0     |  |

| IOM<br>ENC<br>KPL | ECLK Channels 1 & 2<br>IOM Channels 1 & 2<br>ENC1 Channel 1<br>KPL1 Channel 1<br>KPEN1 Channel 1 |       | <ul> <li>1 = External codec clock; 0 = Internal codec clock</li> <li>1 = Binary input/output; 0 = 2-of-6 input/output</li> <li>1 = Enable channel; 0 = Disable channel</li> <li>1 = 55 ms detection time for KP; 0 = 30 ms detection time for KP</li> <li>1 = Enable MF tone detection after KP detection;</li> <li>0 = MF tone detection always on</li> </ul> |              |       |       |       |  |

|                   |                                                                                                  |       | Configura                                                                                                                                                                                                                                                                                                                                                      | ation Byte 2 |       |       |       |  |

| Bit 7             | Bit 6                                                                                            | Bit 5 | Bit 4                                                                                                                                                                                                                                                                                                                                                          | Bit 3        | Bit 2 | Bit 1 | Bit O |  |

| 0                 | 1                                                                                                | 0     | AMU                                                                                                                                                                                                                                                                                                                                                            | ENC2         | KPL2  | KPEN2 | 0     |  |

| ENC<br>KPL        | AMUChannels 1 & 2ENC2Channel 2KPL2Channel 2KPEN2Channel 2                                        |       | <ul> <li>1 = A-law Encoding, 0 = m-law Encoding</li> <li>1 = Enable channel; 0 = Disable channel</li> <li>1 = 55 ms detection time for KP; 0 = 30 ms detection time for KP</li> <li>1 = Enable MF tone detection after KP detection;</li> <li>0 = MF tone detection always</li> </ul>                                                                          |              |       |       |       |  |

Initial Configuration: The configuration of the M-986-2A1 immediately after a reset will be as follows:

- channel disabled

- 2-of-6 input/output

- external serial and serial frame clocks.

Also, the M-986-2A1 will place a 00 hex on the coprocessor port to indicate to the host processor that it is working.

### **Transmit Tone Command**

The transmit tone command allows the host processor to transmit any two of the 6 R1 MF frequencies. The format of the command depends on whether the M-986 is configured for binary format or 2-of-6 format.

### **Recieved Tone Detection**

When a tone is detected by the M-986, the TBLF output goes low, indicating reception of the tone to the host processor. The host processor can determine which tone was detected and which channel the tone was detected on by reading data from the M-986 coprocessor port. The M-986 will return a single byte indicating the tone received and the channel that the tone was received on. The format of the returned byte depends on whether the M-986 is configured for binary or 2-of-6 coding.

### **Coprocessor Port**

Commands are written to the M-986 via the coprocessor port, and data indicating the received R1 MF tone is read from the coprocessor port.

*Writing to the Coprocessor Port:* The following sequence describes writing a command to the M-986.

(1) The WR signal is driven low by the host processor.

(2) The RBLE (receive buffer latch empty) signal transitions to a logic high level.

(3) Data is written from D7-D0 to the receive buffer latch (D7-D0) when the WR signal goes high.

(4) The RBLE signal transitions to a logic low level after the M-986 reads the data. This signals the host processor that the receive buffer is empty.

**Note:** The RBLE should be low before writing to the coprocessor.

Reading the Coprocessor Port: The following sequence describes reading received tone information from the coprocessor port.

(1) The TBLF (transmit buffer latch full) port pin on the M-986 goes low indicating the reception of a tone.

(2) The host processor detects the low logic level on the TBLF pin either by polling a connected port pin or by an interrupt.

(3) The host processor drives the RD signal low.

(4) The TBLF (transmit buffer latch full) signal transition to a logic high level.

(5) Data is driven onto D7-D0 by the M-986 until the RD signal is driven high by the host processor.

# **Clock Characteristics and Timing**

Internal Clock Option: The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN. The frequency of CLKOUT is one-fourth the crystal fundamental frequency. The crystal should be 20.48 MHz, fundamental mode, and parallel resonant, with an effective series resistance of 30 ohms, a power dissipation of 1 mW, and be specified at a load capacitance of 20 pF.

*External Clock Option:* An external frequency source can be used by injecting the frequency directly in X2/CLKIN with X1 left unconnected. The external frequency injected must conform to the specifications listed in External Frequency Specifications table on page 6.

### Flammability/Reliability Specifications

| Reliability:  | 185 FITS failures/billion hours |

|---------------|---------------------------------|

| Flammability: | Passes UL 94 V-0 tests          |

### 2 of 6 Coding Format

| Byte                                                | Bit 7        | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2       | Bit 1    | Bit O |

|-----------------------------------------------------|--------------|-------|----------|-------|-------|-------------|----------|-------|

| Transmit tone comma                                 | nd 1         | CHN   | F6       | F5    | F4    | F3F2        | F1       |       |

| Receive tone return                                 | 0            | CHN   | F6       | F5    | F4    | F3F2        | F1       |       |

| CHN: 1 = channel 2;<br>R1 MF Frequencie<br>Bit name |              | z)    | Bi       | name  |       | Freque      | ncy (Hz) |       |

|                                                     |              | -,    |          |       |       | •           | ,        |       |

| F6                                                  | 1700         |       | F3       |       |       | 1100        |          |       |

| F6<br>F5                                            | 1700<br>1500 |       | F3<br>F2 |       |       | 1100<br>900 |          |       |

### **Binary Coding Format**

| Byte                 |                | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1   | Bit O   |

|----------------------|----------------|---------|---------|-------|-------|-------|-----------|---------|---------|

| Transmit tone con    | nmand          | 1       | CHN     | 0     | 0     | A     | B C       |         | D       |

| Receive tone retur   | m              | 0       | CHN     | 0     | 0     | A     | В         | С       | D       |

| CHN: 1 = channe      | el 2; 0 = char | inel 1  |         |       |       |       |           |         |         |

| <b>R1 MF Frequer</b> | ncies:         |         |         |       |       |       |           |         |         |

| ABCD                 | Frequencie     | es (Hz) | Name    | AB    | CD    |       | Frequenci | es (Hz) | Name    |

| 0000                 | Tone off       |         | -       |       | 1000  |       | 900 & 1   | 500     | Digit 8 |

| 0001                 | 700 & 9        | 00      | Digit 1 |       | 1001  |       | 1100 &    | 1500    | Digit 9 |

| 0010                 | 700 & 1        | 100     | Digit 2 |       | 1010  |       | 1300 &    | 1500    | Digit 0 |

| 0011                 | 900 & 1        | 100     | Digit 3 |       | 1011  |       | 700 & 1   | 700     | ST3     |

| 0100                 | 700 & 1        | 300     | Digit 4 |       | 1100  |       | 900 & 1   | 700     | ST1     |

| 0101                 | 900 & 1        | 300     | Digit 5 |       | 1101  |       | 1100 &    | 1700    | KP      |

| 0110                 | 1100 &         | 1300    | Digit 6 |       | 1110  |       | 1300 &    | 1700    | ST2     |

| 0111                 | 700 & 1        | 500     | Digit 7 |       | 1111  |       | 1500 &    | 1700    | ST      |

# **Signal Description**

| Signal            | Pin     | I/O/Z | Description                                                                                                                                                                                                                                                                                                          |

|-------------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D8            | 18-11   | I/0/Z | Unused. Leave open.                                                                                                                                                                                                                                                                                                  |

| D7-D0             | 19-26   | I/0/Z | 8-bit coprocessor latch.                                                                                                                                                                                                                                                                                             |

| TBLF              | 40      | 0     | Transmit buffer latch full flag.                                                                                                                                                                                                                                                                                     |

| RBLE              | 1       | 0     | Receive buffer latch empty flag.                                                                                                                                                                                                                                                                                     |

| HI/ <del>EO</del> | 2       | I     | Latch byte select pin. Tie low.                                                                                                                                                                                                                                                                                      |

| BIO               | 9       | I     | Unused. Leave open.                                                                                                                                                                                                                                                                                                  |

| RD                | 32      | I/O   | Used by the external processor to read from the coprocessor latch by driving the RD line active (low), thus enabling the output latch to drive the latched data. When the data has been read, the external device must bring the RD line high.                                                                       |

| EXINT             | 5       | I     | Unused. Leave open.                                                                                                                                                                                                                                                                                                  |

| MC                | 3       | I     | Microcomputer mode select pin. Tie low.                                                                                                                                                                                                                                                                              |

| MC/PM             | 27      | I     | Coprocessor mode select pin. Tie low.                                                                                                                                                                                                                                                                                |

| RS                | 4       | Ι     | Reset input for initializing the device. When an active low is placed on RS pin for<br>a minimum of five clock cycles, RD and WR are forced high, and the data bus<br>(LD7 through LD0) goes to a high impedance state. The serial port clock and<br>transmit outputs also go to the high impedance state.           |

| WR                | 31      | Ι/Ο   | Used by the external processor to write data to the coprocessor port. To write data the external processor drives the WR line low, places data on the data bus, and then drives the WR line high to clock the data into the on-chip latch.                                                                           |

| XF                | 28      | 0     | Watchdog signal. Toggles at least once every 10 milliseconds when the processor is functioning properly. If the pin is not toggled at least once every 10 ms, the processor is lost and should be reset.                                                                                                             |

| CLKOUT            | 6       | 0     | System clock output (one-fourth crystal/CLKIN frequency, nominally 5.12 MHz).                                                                                                                                                                                                                                        |

| V <sub>SS</sub>   | 10      | I     | Ground pin.                                                                                                                                                                                                                                                                                                          |

| V <sub>CC</sub>   | 30      | I     | 5V supply pin.                                                                                                                                                                                                                                                                                                       |

| X1                | 7       | 0     | Crystal output pin for internal oscillator. If the internal oscillator is not used, this pin should be left unconnected.                                                                                                                                                                                             |

| X2/CLKIN          | 8       |       | Input pin to the internal oscillator (X2) from the crystal. Alternatively, an input pin for the external oscillator (CLKIN).                                                                                                                                                                                         |

| DR1 & DR0         | 33 & 29 | I     | Serial-port receive-channel inputs. 2.048 MHz serial data is received in the receive registers via these pins. DR0 = channel 1; DR1 = channel 2.                                                                                                                                                                     |

| FR                | 37      | 0     | 8 kHz internal serial-port framing output. If internal clocking is selected,<br>serial-port transmit and receive operations occur simultaneously on an active<br>(high) FR framing pulse.                                                                                                                            |

| DX1 & DX0         | 36 & 35 | 0     | Serial-port transmit-channel outputs. 2.048 MHz serial data is transmitted from the transmit registers on these pins. These outputs are in the high-impedance state when not transmitting. DX0 = channel 1; DX1 = channel 2.                                                                                         |

| FSR               | 39      | I     | 8 kHz external serial-port receive-framing input. If external clocking is selected,<br>data is received via the receive pins (DR1 and DR0) on the active (low) FSR input.<br>The falling edge of FSR initiates the receive process, and the rising edge causes<br>the M-986 to process the data.                     |

| SCLK              | 34      | I/0/Z | 2.048 MHz serial-port clock. Master clock for transmitting and receiving serial-<br>port data. Configured as an input in external clocking mode or output in internal<br>clocking mode. Reset (RS) forces SCLK to the high-impedance state.                                                                          |

| FSX               | 38      | Ι     | 8 kHz external serial-port transmit-framing input. If external clocking is enabled,<br>data is transmitted on the transmit pins (DX1, DX0) on the active (low) input. The<br>falling edge of FSX initiates the transmit process, and the rising edge causes the<br>M-986 to internally load data for the next cycle. |

# **Serial Port Timing**

|                         | Parameter                                    | Min | Nom    | Max  | Unit |

|-------------------------|----------------------------------------------|-----|--------|------|------|

| t <sub>d</sub> (CH-FR)  | Internal framing delay from SCLK rising edge | -   | -      | 70   | ns   |

| t <sub>d</sub> (DX1-CL) | DX bit 1 valid before SCLK falling edge      | 20  | -      | -    | ns   |

| t <sub>d</sub> (DX2-CL) | DX bit 2 valid before SCLK falling edge      | 20  | -      | -    | ns   |

| t <sub>h</sub> (DX)     | DX hold time after SCLK falling edge         | 244 | -      | -    | ns   |

| t <sub>su</sub> (DR)    | DR setup time before SCLK falling edge       | 20  | -      | -    | ns   |

| t <sub>h</sub> (DR)     | DR hold time after SCLK falling edge         | 20  | -      | -    | ns   |

| t <sub>c</sub> (SCLK)   | Serial port clock cycle time                 | 399 | 488.28 | 4770 | ns   |

| t <sub>f</sub> (SCLK)   | Serial port clock fall time                  | -   | -      | 30   | ns   |

| t <sub>r</sub> (SCLK)   | Serial port clock rise time                  | -   | -      | 30   | ns   |

| t <sub>w</sub> (SCLKL)  | Serial port clock low-pulse duration*        | 220 | 244.14 | 2500 | ns   |

| t <sub>w</sub> (SCLKH)  | Serial port clock high-pulse duration*       | 220 | 244.14 | 2500 | ns   |