# <mark>АКМ</mark> АК4543

# AC'97<sup>TM</sup> Rev 2.1 Multimedia Audio CODEC

## Features

- AC'97 Rev. 2.1 Compliant • 18bit Resolution A/D and D/A • Exceeds a PC98/99 Performance Categories: A/D..... 90dBA SNR D/A..... 90dBA SNR D/A + Mixer ..... 89dBA SNR A-A..... 95BA SNR • Analog Inputs: 4 Stereo Inputs: LINE, CD, VIDEO, AUX **Speakerphone and PC BEEP Inputs** 2 Independent MIC Inputs • Direct PC\_Beep Pass Through for lower system costs • Analog Output: Stereo LINE Output with volume control True Line Level with volume control Mono Output with volume control • 3D Stereo Enhancement Multiple codec Capability The AK4543 can work as a Primary or Secondary. • EAPD(External Amplifier Powerdown) Support • Power Supplies:

- Analog 5.0V, Digital 3.3V or 5.0V

- Low Power Consumption

- 200mW(Analog:5V/Digital:3.3V) at full operation

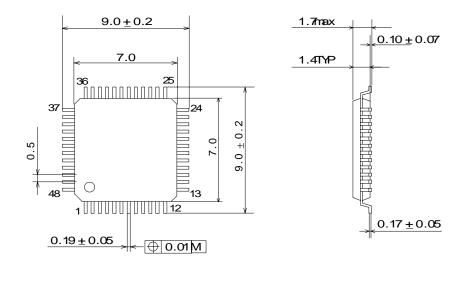

- 48 Pin LQFP Package

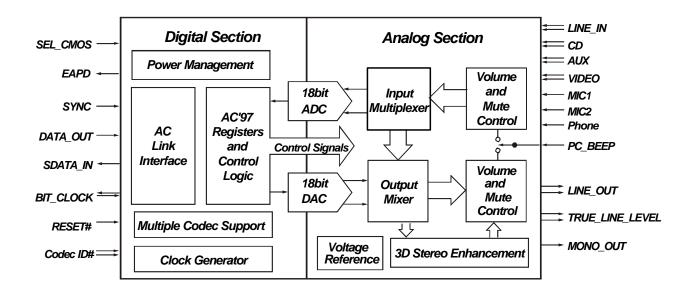

# General Description

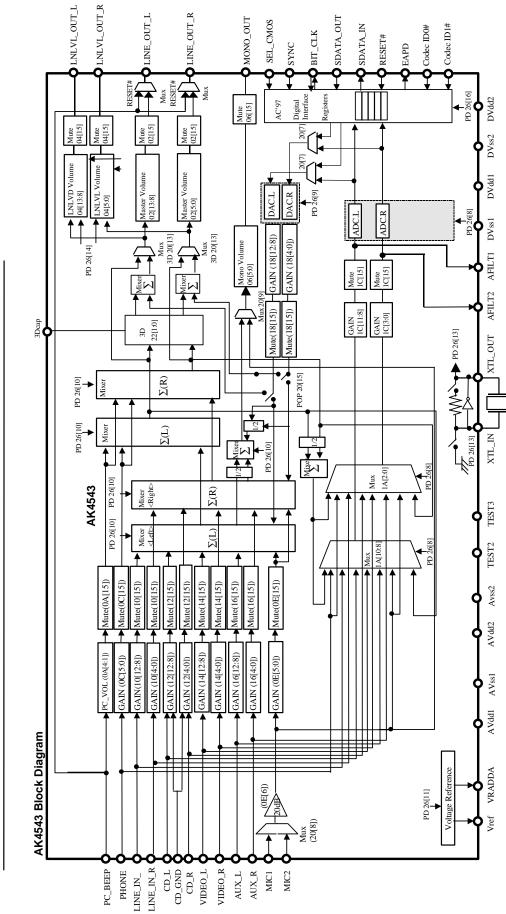

The AK4543 is a 18bit high performance codec compliant with Audio Codec '97 Rev 2.1 requirements. The AC Link serial interface allows the AK4543 to be used with digital controllers as well as custom logic accelerators to meet full PC98 and PC99 requirements for a PCI audio solution.

The AK4543 provides two pairs of stereo outputs with independent volume controls along with a mono output, multiple stereo and mono inputs, are combined to create flexible mixing, gain and mute functions to provide a complete integrated audio solution for PCs.

The AK4543 can function as a Primary AC'97 or Secondary codec depending on the codec ID configuration(Multiple codec extension), making the AK4543 suitable for the docking station application and multiple codec applications such as 4 speaker output or 6 speaker output.

Sampling at 48kHz, the AK4543 provides excellent audio performance, meeting or exceeding all standard requirements. It offers low power consumption, and flexible power-down modes for use in laptops, desktop PCs, and aftermarket add-in boards.

Like the earlier pin-compatible AK4540 and AK4542, the AK4543 is available in a compact 48-lead LQFP package.

The AK4543 is a pin compatible upgrade for the AK4540 and AK4542, some software changes will be required to experience the extra functions of the AK4543.

\* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

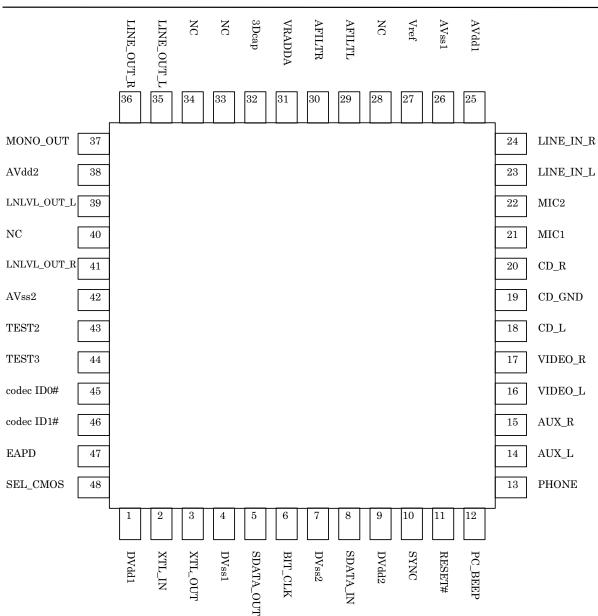

|                 |                   |        | Pin/Function                                                                                                       |

|-----------------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------|

|                 | ~                 |        |                                                                                                                    |

| No.             | Signal Name       | I/0    | Description                                                                                                        |

| 1               | DVdd1             | -      | Digital power supply; 3.3V or 5.0V(DVdd1 = DVdd2)                                                                  |

| 2               | XTL_IN            | T      | 0.1uF + 4.7uF capacitors should be connected to digital ground.<br>24.576MHz(512fs) crystal is normally connected. |

| Z               | (MCLKI)           | 1      | If a crystal is not connected, an external clock can be used.                                                      |

| 3               | XTL_OUT(open)     | 0      | 24.576MHz(512fs) crystal. If an external clock is used, this pin should be open.                                   |

| 4               | DVss1             |        | Digital Ground; 0V                                                                                                 |

| 4               | DV 551            | -      | This pin should be directly connected to DVss2 on board.                                                           |

| 5               | SDATA_OUT         | Ι      | Serial 256-bit AC'97 data stream from digital controller                                                           |

| 6               | BIT_CLK           | I/O    | 12.288MHz(256fs) serial data clock                                                                                 |

|                 | -                 |        | Output when Primary codec(codec ID=00).                                                                            |

|                 |                   |        | Input when Secondary codec(codec ID=01, 10, 11).                                                                   |

| 7               | DVss2             | -      | Digital Ground; 0V                                                                                                 |

|                 |                   |        | This pin should be directly connected to DVss1 on board.                                                           |

| 8               | SDATA_IN          | 0      | Serial 256-bit AC'97 data stream to digital controller                                                             |

| 9               | DVdd2             | -      | Digital power supply; 3.3V or 5.0V(DVdd1 = DVdd2)                                                                  |

| 1.0             | ama               | -      | 0.1 uF + 4.7 uF capacitors should be connected to digital ground.                                                  |

| 10              | SYNC<br>DECE77    | I      | AC'97 Sync Clock, 48kHz(1fs) fixed rate sampling rate                                                              |

| 11              | RESET#            | I      | AC'97 Master Hardware Reset                                                                                        |

| 12              | PC_BEEP           | I      | PC Speaker beep pass through                                                                                       |

| 13              | PHONE             | I      | From telephony subsystem speakerphone                                                                              |

| $\frac{14}{15}$ | AUX_L<br>AUX_R    | I      | Aux Left Channel<br>Aux Right Channel                                                                              |

|                 |                   | _      |                                                                                                                    |

| 16              | VIDEO_L           | I      | Video Audio Left Channel                                                                                           |

| $\frac{17}{18}$ | VIDEO_R<br>CD_L   | I<br>I | Video Audio Right Channel<br>CD Audio Left Channel                                                                 |

| 18              | CD_L<br>CD_GND    | I      | CD Audio Leit Channel<br>CD Audio analog ground; 0V                                                                |

| 19              | CD_GND            | 1      | CD Addio analog ground, ov<br>CD_GND or analog ground should be connected.                                         |

| 20              | CD_R              | Ι      | CD Audio Right Channel                                                                                             |

| 20              | MIC1              | I      | Desktop Microphone Input                                                                                           |

| 22              | MIC2              | I      | Second Microphone Input                                                                                            |

| 23              | LINE_IN_L         | Ī      | Line In Left Channel                                                                                               |

| 24              | LINE_IN_R         | I      | Line In Right Channel                                                                                              |

| 25              | AVdd1             | -      | Analog power supply; 5.0V(AVdd1=AVdd2)                                                                             |

|                 |                   |        | 0.1uF + 4.7uF capacitors should be connected to AVss1(analog ground).                                              |

| 26              | AVss1             | -      | Analog Ground; 0V                                                                                                  |

| 27              | Vref              | 0      | Reference Voltage Output;                                                                                          |

|                 |                   |        | 0.1µF +4.7µF capacitors should be connected to Avss1(analog ground).                                               |

| 28              | NC                | -      | No Connection                                                                                                      |

| 29              | AFILTL            | 0      | Anti-Aliasing Filter Cap; Connected to analog ground with 1nF capacitor.                                           |

| 30              | AFILTR            | 0      | Anti-Aliasing Filter Cap; Connected to analog ground with 1nF capacitor.                                           |

| 31              | VRADDA            | 0      | Vref for ADC and DAC; 0.1µF capacitor should be connected to analog ground.                                        |

| 32              | 3Dcap             | 0      | 3D Enhancement Cap; 27nF capacitor should be connected to analog ground.                                           |

| 33              | NC                | -      | No Connection                                                                                                      |

| 34              | NC                | -      | No Connection                                                                                                      |

| 35              | LINE_OUT_L        | 0      | Line Out Left Channel                                                                                              |

| 36              | LINE_OUT_R        | 0      | Line Out Right Channel                                                                                             |

| 37              | MONO_OUT          | 0      | To telephony subsystem speakerphone                                                                                |

| 38              | AVdd2             | -      | Analog power supply; 5.0V(AVdd1=AVdd2)                                                                             |

| 20              |                   | 0      | 0.1uF capacitor should be connected to AVss2(analog ground).                                                       |

| 39              | LNLVL_OUT_L<br>NC | 0      | True Line Level Out Left Channel                                                                                   |

| 40<br>41        | LNLVL_OUT_R       | - 0    | No Connection<br>True Line Level Out Right Channel                                                                 |

| 41 42           |                   |        | Analog Ground; 0V                                                                                                  |

| 42 43           | AVss2<br>TEST2    | -<br>I | Test pin (This pin should be open for normal operation)                                                            |

| 43              | TEST3             | I      | Test pin (This pin should be open for normal operation)<br>Test pin (This pin should be open for normal operation) |

| $\frac{44}{45}$ | Codec ID0#        | I      | Codec ID configuration(ID select input for multiple codec extension) See Page20.                                   |

| 40              | Codec ID0#        | I      | Codec ID configuration(ID select input for multiple codec extension) See Page20.                                   |

| 40              | EAPD              | 0      | External amplifier powerdown See Page 20.                                                                          |

| - 11            | 14111             | 5      | Encontrat amplifier powerdown Dee Lage 20.                                                                         |

| 48 | SEL_CMOS | Ι | CMOS/TTL selection for digital input levels | See Page 28. |  |  |  |  |

|----|----------|---|---------------------------------------------|--------------|--|--|--|--|

|    |          |   | CMOS: Leave open for 3.3V supply.           |              |  |  |  |  |

|    |          |   | TTL : Tie to GND for 5V supply.             |              |  |  |  |  |

| Absolute Maximum Rating                      |        |      |        |       |  |  |  |  |

|----------------------------------------------|--------|------|--------|-------|--|--|--|--|

| AVss1, AVss2, DVss1, DVss2 =0V (Note 1)      |        |      |        |       |  |  |  |  |

| Parameter                                    | Symbol | min  | max    | Units |  |  |  |  |

| Power Supplies                               |        |      |        |       |  |  |  |  |

| Analog(AVdd1 & AVdd2)                        | VA     | -0.3 | 6.0    | V     |  |  |  |  |

| Digital(DVdd1 & DVdd2)                       | VD     | -0.3 | 6.0    | V     |  |  |  |  |

| Input Current (any pins except for supplies) | IIN    | -    | ±10    | mA    |  |  |  |  |

| Analog Input Voltage                         | VINA   | -0.3 | VA+0.3 | V     |  |  |  |  |

| Digital Input Voltage                        | VIND   | -0.3 | VD+0.3 | V     |  |  |  |  |

| Ambient Temperature                          | Та     | -10  | 70     | °C    |  |  |  |  |

| Storage Temperature                          | Та     | -65  | 150    | °C    |  |  |  |  |

Note 1: All voltages with respect to ground. AGND(AVss1, AVss2) and DGND(DVss1, DVss2) must be the same voltage.

Warning: Operation at or beyond these limits may results in permanent damage to the device. Normal operation is not guaranteed at these extremes.

|                        | Recommended Operating Condition |         |        |       |            |      |       |  |

|------------------------|---------------------------------|---------|--------|-------|------------|------|-------|--|

| AGND, DGND=0V (Note 1) |                                 |         |        |       |            |      |       |  |

| Parameter              |                                 |         | Symbol | min   | typ        | max  | Units |  |

| Power Supplies         | AK4543                          |         |        |       |            |      |       |  |

|                        |                                 | Analog  | VA     | 4.75  | 5.0        | 5.25 | V     |  |

|                        |                                 | Digital | VD     | 3.135 | 3.3 or 5.0 | 5.25 | V     |  |

Note 1 : All voltages with respect to ground.

| AK4543 Analog Ch                                                                                                 | aracteristics  |                  |           |           |

|------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------|-----------|

| Ta=25°C,AVdd=5.0V±5%, DVdd=3.3V±5% or 5V±5%, fs=48K<br>All volume setting for ADC/DAC performance measurement is |                | uency =1kHz      |           |           |

| Parameter                                                                                                        | min            | Тур              | max       | Units     |

| Audio-ADC                                                                                                        |                |                  | •         |           |

| Resolution                                                                                                       |                |                  | 18        | Bits      |

| S/N (A weighted)                                                                                                 | 85             | 90               |           | dB        |

| S/(N+D) (-1dB analog input)                                                                                      | 70             | 77               |           | dBFS      |

| Inter Channel Isolation                                                                                          | 70             | 77               |           | dB        |

| Inter Channel Gain Mismatch                                                                                      |                |                  | 0.5       | dB        |

| Full Scale Input Voltage                                                                                         | 0.88           | 1.0              | 1.12      | Vrms      |

| Power Supply Rejection                                                                                           |                | 50               |           | dB        |

| Audio DAC: measured at AOUTL/AOUTR via MIXER path                                                                |                |                  |           |           |

| Resolution                                                                                                       |                |                  | 18        | Bits      |

| S/N (A weighted)                                                                                                 |                |                  |           |           |

| : mixer+DAC measured at AOUT                                                                                     | 84             | 89               |           | dB        |

| S/(N+D) (-1dB digital input)                                                                                     | 75             | 83               |           | dBFS      |

| Inter Channel Isolation                                                                                          | 70             | 80               |           | dB        |

| Inter Channel Gain Mismatch                                                                                      |                |                  | 1.0       | dB        |

| Full Scale Output Voltage                                                                                        | 0.83           | 0.95             | 1.07      | Vrms      |

| Total Out-of-Band Noise (28.8kHz - 100kHz)                                                                       |                | -70              |           | dB        |

| Power Supply Rejection                                                                                           |                | 50               |           | dB        |

| MIC Amplifier / MUX                                                                                              |                |                  | •         | ·         |

| Gain : 20dB is selected                                                                                          | 18             | 20               | 22        | dB        |

| Master volume (Mono, Stereo, True Line Level Out) :                                                              | -              | -                |           | ab        |

| Step Size                                                                                                        | 1.64D x 62 500 | -1.5             |           | dB        |

| Attenuation Control Range                                                                                        | -46.5          | 1.0              | 0         | dB        |

| Load Resistance                                                                                                  | 10             |                  | 0         | uD<br>kΩ  |

| PC Beep : 3dB x 16 step                                                                                          | 10             |                  |           | K52       |

|                                                                                                                  |                | 2.0              |           | JD        |

| Step Size                                                                                                        | -45            | -3.0             | 0         | dB<br>dB  |

| Attenuation Control Range                                                                                        | -40            |                  | 0         | uБ        |

| Analog Mixer : 1.5dB x 32 step                                                                                   |                | 1 5              |           | 110       |

| Step Size                                                                                                        | 0.1 5          | -1.5             | 110       | dB        |

| Gain Control Range                                                                                               | -34.5          |                  | +12       | dB        |

| Record Gain : 1.5dB x 16 step                                                                                    |                |                  |           | 15        |

| Step Size                                                                                                        |                | +1.5             |           | dB        |

| Gain Control Range                                                                                               | 0              |                  | +22.5     | dB        |

| Mixer                                                                                                            |                |                  | T         |           |

| Input Voltage (except for MIC)                                                                                   |                | 1.0              |           | Vrms      |

| Input Voltage MIC : Gain = 0dB                                                                                   |                | 1.0              |           | Vrms      |

| MIC : Gain = 20dB                                                                                                |                | 0.1              |           | Vrms      |

| S/N(A weighed) : 0dB setting, 1 path is selected at Mixer                                                        | 05             | 05               |           | 110       |

| CD to AOUT:                                                                                                      | 85             | 95<br>05         |           | dB        |

| Other analog input to AOUT                                                                                       |                | 95               |           | dB        |

| Input Impedance (Input gain=0dB, Rec_MUTE=off)<br>PC_BEEP only                                                   | (10)           | 80               |           | ko        |

| Others(PHONE, LINE, CD, AUX, VIDEO)                                                                              | (10) (10)      | $\frac{80}{40}$  |           | $k\Omega$ |

| Input Impedance (MIC1 and MIC2)                                                                                  | (10) (10)      | $\frac{40}{22}$  |           | $k\Omega$ |

|                                                                                                                  | (10)           |                  |           | kΩ        |

| Power Supplies                                                                                                   |                |                  | l         | ┼───┨     |

| Analog Power Supply Current (AVdd1 & AVdd2)                                                                      |                | 96               | 51        |           |

| All ON mode(all PR_bits are 0)<br>Cold Reset status(Reset#=L, Vref is ON)                                        |                | $\frac{36}{2.5}$ | 545       | mA<br>mA  |

| All OFF mode(all PR_bits are 1)                                                                                  |                | 2.5<br>0         | $0.2^{0}$ | mA<br>mA  |

| Digital Power Supply Current(DVdd1 & DVdd2)                                                                      |                | 0                | 0.2       | mA        |

| All ON mode(all PR_bits are 0) at DVDD=5V                                                                        |                | 13               | 20        | mA        |

| All ON mode(all PR_bits are 0) at DVDD=3V                                                                        |                | 6.6              | 20<br>10  | mA        |

| All OFF mode(all PR_bits are 1)                                                                                  |                | 0.0              | 0.2       | mA        |

| moac(an + 10_2000 at 0 1)                                                                                        |                | 5                | 0.1       | *****     |

| 1 <b>1 1</b>                                                       | aracteristics  |      |      |       |

|--------------------------------------------------------------------|----------------|------|------|-------|

| Ta=25°C,AVdd=5.0V $\pm$ 5%, DVdd=3.3V $\pm$ 5% or 5V $\pm$ 5% , fs | s=48KHz(fixed) |      |      | •     |

| Parameter                                                          | min            | typ  | Max  | Units |

| ADC Digital Filter (Decimation LPF)                                |                |      |      |       |

| Passband (±0.2dB)                                                  | 0              |      | 19.2 | kHz   |

| Stopband                                                           | 28.8           |      |      | kHz   |

| Stopband Attenuation                                               | 70             |      |      | dB    |

| Group Delay                                                        |                |      | 0.5  | ms    |

| ADC Digital Filter (HPF)                                           |                |      |      |       |

| Frequency Response; -3dB                                           |                | 7.5  |      | Hz    |

| -0.5 dB                                                            |                | 21   |      |       |

| -0.1dB                                                             |                | 49   |      |       |

| DAC Digital Filter                                                 |                |      |      |       |

| Passband (±0.2dB)                                                  | 0              |      | 19.2 | kHz   |

| Stopband                                                           | 28.8           |      |      | kHz   |

| Group Delay                                                        |                |      | 0.5  | ms    |

| Stopband Rejection                                                 | 70             |      |      | dB    |

| DAC Post filter                                                    |                |      |      |       |

| Passband Frequency Response (0 - 19.2kHz)                          |                | ±0.1 |      | dB    |

| AK4543 DC Characteristics                                                |            |                    |                    |        |        |          |

|--------------------------------------------------------------------------|------------|--------------------|--------------------|--------|--------|----------|

| Ta=-10~70°C, VD=5V±5%(SEL_CMOS=L) or 3.3V±5%(SEL_CMOS=H: Open), VA=5V±5% |            |                    |                    |        |        | nal load |

| Parameter                                                                |            | Symbol             | min                | Тур    | Max    | Units    |

| "H" level input voltage                                                  |            | VIH                |                    | -      | -      |          |

| XTAL_IN                                                                  |            |                    | $0.7 \mathrm{xVD}$ |        |        | V        |

| RESET#, SYNC, SDATA_OUT, I                                               | BIT_CLK    |                    |                    |        |        |          |

| At SEL_COMS=L(GND)                                                       |            |                    | 2.2                |        |        | V        |

| At SEL_COMS=H(Open)                                                      |            | $0.7 \mathrm{xVD}$ |                    |        | V      |          |

| ID0#, ID1#, SEL_CMOS(Pull up)                                            | )          |                    | 0.8xVD             |        |        | V        |

| "L" level input voltage                                                  |            | VIL                | -                  | -      |        |          |

| XTAL_IN                                                                  |            |                    |                    |        | 0.3xVD | V        |

| RESET#, SYNC, SDATA_OUT, I                                               | BIT_CLK    |                    |                    |        |        |          |

| At SEL_COMS=L(GND)                                                       |            |                    |                    |        | 0.8    | V        |

| At SEL_COMS=H(Open)                                                      |            |                    |                    |        | 0.3xVD | V        |

| ID0#, ID1#, SEL_CMOS(Pull up)                                            |            |                    |                    | 0.2xVD | V      |          |

| "H" level output voltage                                                 | Iout= -1mA | VOH                | VD-0.55            | -      | -      | V        |

| "L" level output voltage                                                 | Iout= 1mA  | VOL                | -                  | -      | 0.55   | V        |

| Input leakage current(exclude pull                                       | Iin        | -                  | -                  | ±10    | μA     |          |

| Pull up resistance                                                       |            | Rup                | 50                 | 100    | 200    | kΩ       |

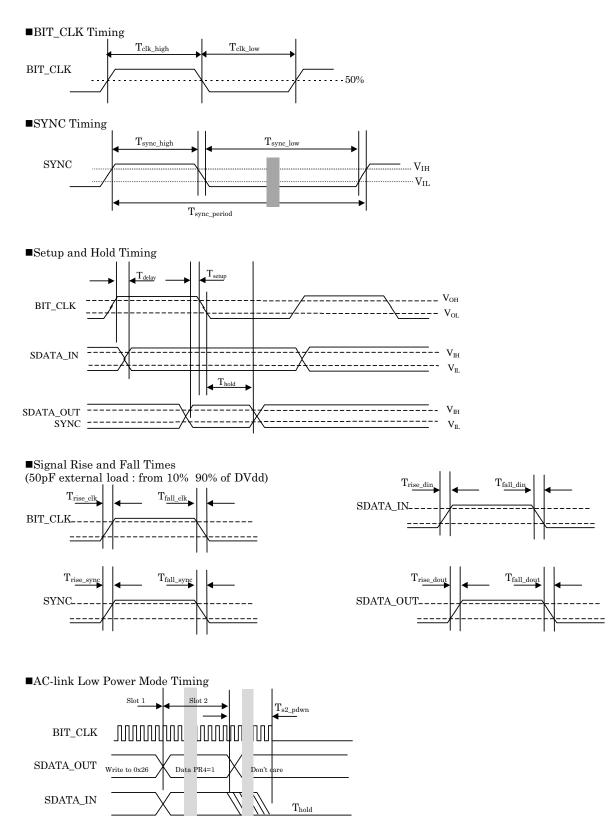

| Sw                                      | vitching Charac                       | teristics |             |          |              |

|-----------------------------------------|---------------------------------------|-----------|-------------|----------|--------------|

| Ta=25°C, AVdd=5.0V±5%, DVdd=3.3V±5% or  |                                       |           |             |          |              |

| Parameter                               | Symbol                                | min       | Тур         | max      | Units        |

| Master Clock Frequency Note)            | Fmclk                                 | -         | 24.576      | -        | MHz          |

| If Crystal is not used.                 |                                       | 45        | 50          | 55       | %            |

| AC link Interface Timing                |                                       |           |             |          |              |

| BIT_CLK frequency                       | Fbclk                                 |           | 12.288      |          | MHz          |

| BIT_CLK clock Period(Tbclk=1/Fbclk)     | Tbclk                                 | -         | 81.38       |          | ns           |

| BIT_CLK low pulse width                 | Tclk_low                              | 36.0      | 40.7        | 45       | ns           |

| BIT_CLK high pulse width                | Tclk_high                             | 36.0      | 40.7        | 45       | ns           |

| BIT_CLK rise time                       | Trise_clk                             | -         | -           | 6        | ns           |

| BIT_CLK fall time                       | Tfall_clk                             | -         | -           | 6        | ns           |

| SYNC frequency                          |                                       | -         | 48          | -        | kHz          |

| SYNC low pulse width                    | Tsync_low                             | -         | 19.5        | -        | μs           |

|                                         |                                       |           | (240 cycle) |          | (Tbclk)      |

| SYNC high pulse width                   | Tsync_high                            | -         | 1.3         | -        | μs           |

|                                         |                                       |           | (16 cycle)  |          | (Tbclk)      |

| SYNC rise time                          | Trise_sync                            | -         | -           | 6        | ns           |

| SYNC fall time                          | Tfall_sync                            | -         | -           | 6        | ns           |

| Setup time(SYNC, SDATA_OUT)             | Tsetup                                | 10.0      | -           | -        | ns           |

| Hold time(SYNC, SDATA_OUT)              | Thold                                 | 25.0      | -           |          | ns           |

| SDATA_IN delay time from BIT_CLK        | Tdelay                                | -         | -           | 15       | ns           |

| rising edge                             | -                                     |           |             |          |              |

| SDATA_IN rise time                      | Trise_din                             | -         | -           | 6        | ns           |

| SDATA_IN fall time                      | Tfall_din                             | -         | -           | 6        | ns           |

| SDATA_OUT rise time                     | Trise_dout                            | -         | -           | 6        | ns           |

| SDATA_OUT fall time                     | Tfall_dout                            | -         | -           | 6        | ns           |

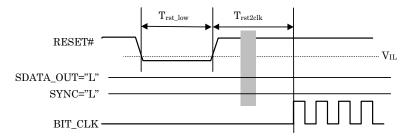

| Cold Rest (SDATA_OUT=L, SYNC=L)         |                                       |           |             |          |              |

| RESET# active low pulse width           | Trst_low                              | 1.0       | -           | -        | μs           |

| RESET# inactive to BIT_CLK delay        | Trst2clk                              | 162.8     |             |          | ns           |

| _ *                                     |                                       | (2 cycle) |             |          | (Tbclk)      |

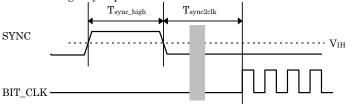

| Warm Rest Timing                        |                                       |           |             |          | , í          |

| SYNC active low pulse width             | Tsync_high                            | 1.0       | 1.3         | -        | μs           |

| r i i i i i i i i i i i i i i i i i i i | ··· · · · · · · · · · · · · · · · · · |           | (16 cycle)  |          | (Tbclk)      |

| SYNC inactive to BIT_CLK delay          | Tsync2clk                             | 162.8     | ()          |          | ns           |

|                                         |                                       | (2 cycle) |             |          | (Tbclk)      |

| AC-link Low Power Mode Timing           |                                       |           |             |          | (= ~ 0 = = ) |

| End of Slot 2 to BIT_CLK, SDATA_IN      | Ts2_pdwn                              | -         | -           | 1.0      | μs           |

| Low                                     | 102_pattin                            |           |             | 1.0      | μο           |

| Activate Test Mode Timing               |                                       | 1         |             |          |              |

| Setup to trailing edge of RESET#        | Tsetup2rst                            | 15.0      |             | -        | ns           |

| Hold from RESET# rising edge            | Thold2rst                             | 100       |             | -        | ns           |

| Rising edge of RESET# to Hi-Z           | Toff                                  |           |             | 50       | ns           |

| Falling edge of RESET# to "L"           | Tlow                                  | _         |             | 50<br>50 | ns           |

Note ) The use of a crystal is recommended. If a master clock is supplied (or if an external oscillator is used), Master Clock should be supplied to XTAL\_IN and XTAL\_OUT should be left open.

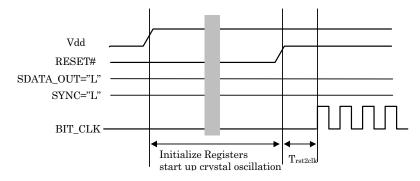

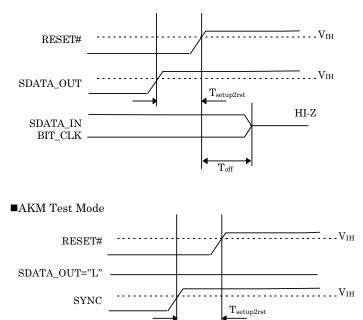

#### Power On

Note that a AK4543 must be in cold reset at power on and RESET# must be low until master clock becomes stable, or a reset must be done once master clock is stable. AVdd or DVdd can be powered from independent supplies.

When using the AK4543 in the multiple codec mode, all codec's connected to the AC-link are waken up at the same time. A common reset line should be used to insure clock synchronization after power up.

#### ■Cold Reset Timing

Note that both SDATA\_OUT and SYNC must be low at the rising edge of RESET# for a cold reset to occur. The AK4543 initializes all registers including the Powerdown Control Registers, BIT-CLK is reactivated and each analog output is in Hi-Z state except for PC Beep while RESET# pin is low. The PC Beep is directly routed to L & R line outputs when AK4543 is in Cold Reset. This is done to allow system sounds to be passed to speaker removing for an internal redundant speaker.

At the rising edge of RESET#, the AK4543 initiates the initialization of analog circuit, which takes 516fs cycles. After that, the mixer of the AK4543 is ready for normal operation.

Status bit in the slot 0 is "0" (not ready) when the AK4543 is in RESET period ("L") or in initialization process. After initialization cycles, the status bit goes to "1" indicating a ready condition.

When the AK4543 is used under the multiple codec configuration and when cold reset is issued, all AK4543 connected to the AC-link will execute a cold reset concurrently.

#### ■Warm Reset

The AK4543 initiates a warm reset process by receiving a single pulse on the sync(Pin10). The AK4543 then clears PR4 bit and PR5 bit in the Powerdown Control Register. However, warm reset does not influence PR0~PR3 or PR6,7 bits in Powerdown Control Register(26h). Note that SYNC signal should synchronize with BIT\_CLK after AK4543 starts to output BIT\_CLK clock. And if an external clock is used, an external clock should be supplied before issuing a sync pulse for warm reset.

Please refer to Powerdown/Powerup sequence of multiple codec configuration on the warm reset when the AK4543 is used under the multiple codec configuration .(See page 24, 25)

# ■Activate Test Mode

Notes:1

1. All AC-link signals are normally low through the trailing edge of RESET#. Bringing SDATA\_OUT high for the rising edge of RESET# causes the AK4543 AC-link outputs to go high impedance which is suitable for ATE in circuit testing. Note that the AK4543 enters in the ATE test mode regardless SYNC is high or low.

2. Bringing both SYNC high and SDATA\_OUT low for the rising edge of RESET# causes AKM test mode.

3. Once test modes have been entered, the only way to return to the normal operating state is to issue "cold reset" which issues RESET# with both SYNC and SDATA\_OUT low.

<sup>&</sup>lt;sup>1</sup> All the following sentences written with small italic font in this document quote the AC'97 component specification.

#### General Description

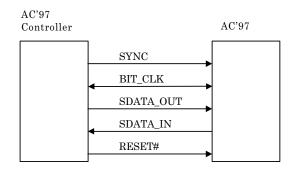

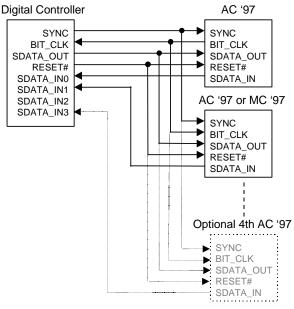

■AC '97 Connection to the Digital AC '97 controller

<sup>2</sup>AC '97 communicates with its companion AC '97 controller via a digital serial link, "AC-link". All digital audio streams, and command/status information are communicated over this point to point serial interconnect. A breakout of the signals connecting the two is shown in the following figure.

## ■AC'97 Digital Interface

The AK4543 incorporates a 5 pin digital serial interface that links it to the AC '97 controller. AC-link is a bi-directional, fixed rate(48kHz), serial PCM digital stream. It handles multiple input, and output audio streams, as well as control register accesses employing a time division multiplexed (TDM) scheme. The AC-link architecture divides each audio frame into 12 outgoing and 12 incoming data streams, each with 20-bit sample resolution. DAC and ADC resolution of the AK4543 is 18 bit resolution. The data streams currently defined by the AC '97 specification include:

| PCM Playback                          | 2 output slots |

|---------------------------------------|----------------|

| 2 channel composite PCM output stream |                |

| PCM Record data                       | 2 input slots  |

| 2 channel composite PCM input stream  |                |

| Control                               | 2 output slot  |

| Control register write port           | -              |

| • Status                              | 2 input slots  |

| Control register read port            | •              |

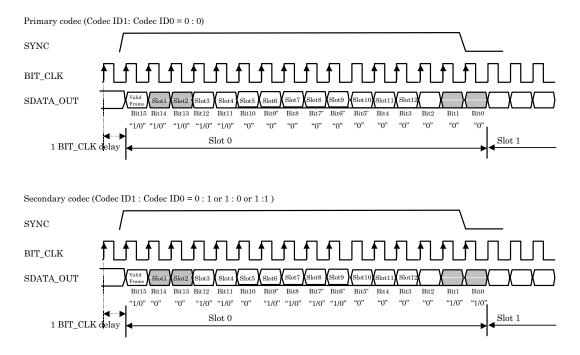

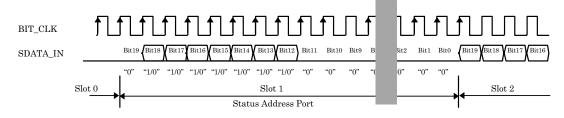

SYNC, fixed at 48 KHz, is derived by dividing down the serial bit clock (BIT\_CLK). BIT\_CLK, fixed at 12.288 MHz, provides the necessary clocking granularity to support 12, 20-bit outgoing and incoming time slots. AC-link serial data is transitioned on each rising edge of BIT\_CLK. The receiver of AC-link data, the AK4543 for outgoing data and AC '97 controller for incoming data, samples each serial bit on the falling edges of BIT\_CLK.

The AK4543 outputs BIT\_CLK when it is assigned as Primary codec by the codec ID configuration ID1# and ID0#. The other hand, the AK4543 receives BIT\_CLK when assigned as the Secondary codec from the Primary device.

The AC-link protocol provides for a special 16-bit slot (Slot 0) wherein each bit conveys a valid tag for its corresponding time slot within the current audio frame. A "1" in a given bit position of slot 0 indicates that the corresponding time slot within the current audio frame has been assigned to a data stream, and contains valid data. If a slot is "Tagged" invalid, it is the responsibility of the source of the data, (The AK4543 for the input stream, AC '97 controller for the output stream), to stuff all bit positions with 0's during that slot's active time.

SYNC remains high for a total duration of 16 BIT\_CLKs at the beginning of each audio frame. The portion of the audio frame where SYNC is high is defined as the "Tag Phase". The remainder of the audio frame where SYNC is low is defined as the "Data Phase". Note that SDATA\_OUT and SDATA\_IN data is delayed one BIT\_CLK becauseAC'97 controller causes SYNC signal high at a rising edge of BIT\_CLK which initiates a frame.

"Output" stream means the direction from AC'97 controller to the AK4543, and "Input" stream means the direction from the AK4543 to AC'97 controller

<sup>&</sup>lt;sup>2</sup>All the following sentences written with small italic font in this document quote the AC'97 component specification.

| Slot         | 0          | 1                  | 2               | 3                | 4                 | 5          | 6                | 7                | 8                 | 9                 | 10         | 11         | 12          |   |

|--------------|------------|--------------------|-----------------|------------------|-------------------|------------|------------------|------------------|-------------------|-------------------|------------|------------|-------------|---|

| SYNC         |            |                    |                 |                  |                   |            |                  |                  |                   |                   |            |            |             |   |

|              | Codec ID1: | Codec ID0=0        | :0 or 0:1       |                  |                   |            |                  |                  |                   |                   |            |            |             |   |

| SDATA<br>OUT | TAG        | Command<br>Address | Command<br>Data | PCM(dac)<br>Left | PCM(dac)<br>Right | All<br>"0" | All<br>"0"       | All<br>"0"       | All<br>"0"        | All<br>"0"        | All<br>"0" | All<br>"0" | All<br>"0"  |   |

|              | Codec ID1: | Codec ID0=1        | :0              |                  |                   |            |                  |                  |                   |                   |            | -          |             |   |

|              | TAG        | Command<br>Address | Command<br>Data | All<br>"0"       | All<br>"0"        | All<br>"0" | All<br>"0"       | PCM(dac)<br>Left | PCM(dac)<br>Right | All<br>"0"        | All<br>"0" | All<br>"0" | All<br>"0"  |   |

|              | Codec ID1: | Codec ID0=1        | :1              |                  |                   |            |                  |                  |                   |                   |            |            |             |   |

|              | TAG        | Command<br>Address | Command<br>Data | All<br>"0"       | All<br>"0"        | All<br>"0" | PCM(dac)<br>Left | All<br>"0"       | All<br>"0"        | PCM(dac)<br>Right | All<br>"0" | All<br>"0" | All<br>"0"  |   |

|              |            |                    |                 |                  |                   |            |                  |                  |                   |                   |            |            |             |   |

| SDATA<br>IN  | TAG        | Status<br>Address  | Status<br>Data  | PCM(adc)<br>Left | PCM(adc)<br>Right | All<br>"0" | All<br>"0"       | All<br>"0"       | All<br>"0"        | All<br>"0"        | All<br>"0" | All<br>"0" | All<br>"0"  |   |

|              |            |                    |                 |                  |                   |            |                  |                  |                   |                   |            |            |             |   |

|              | Tag Phase  | 4                  |                 |                  |                   | Ι          | Data Phase       |                  | 48kHz             |                   |            |            | <b>&gt;</b> | • |

AC-link protocol identifies 13slots of data per frame. The frequency of sync is fixed to 48kHz. Only Slot 0, which is the Tag phase, is 16bits, all other slots are 20bits in length. These slots are explained in later sections.

AC-link Audio Output Frame (SDATA\_OUT)

a)Slot 0

The AK4543 checks bit15 (valid frame bit). Note that when the valid frame bit is "1", at least one bit14-6 (slot 1-9) or bit1-0 must be valid, bit5-2 will be "0" and should be ignored.

If bit 15 is "0", the AK4543 ignores all following information in the frame.

The AK4543 then checks the validity of each bit in the TAG phase (slot 0).

If each bit is "0", the AK4543 ignores the slot indicated by "0". On the other hand, if each bit is "1", the slot is valid. All bits in slot10-12(bit5-3) are "0" and bit2 is also "0".

The AK4543 monitors bit1 and 0, which are codec ID configuration bits used in multiple codec implementations. These bits are used to identify which codec the frame data is issued to.

When codec ID configuration bits1 and 0 which are set by the codec ID configuration 45/46 strapping pins(codec ID0# and ID1#) are set to zero(00), the frame is aimed for the Primary codec. And when codec ID configuration bit1 and 0 are set to non-zero values(01, 10, or 11), the frame is meant for Secondary codec.

A new audio output frame begins with a low to high transition of SYNC. SYNC is synchronous to the rising edge of BIT\_CLK. On the immediately following falling edge of BIT\_CLK, the AK4543 samples the assertion of SYNC. This falling edge marks the time when both sides of AC-link are aware of the start of a new audio frame. On the next rising of BIT\_CLK, the AC '97 controller transitions SDATA\_OUT into the first bit position of slot 0 (Valid Frame bit). Each new bit position is presented to AC-link on a rising edge of BIT\_CLK, and subsequently sampled by the AK4543 on the following falling edge of BIT\_CLK. This sequence ensures that data transitions, and subsequent sample points for both incoming and outgoing data streams are time aligned.

Data should be sent to the AC'97 codec with MSB first through the Pin labled SDATA\_OUT.

The following table shows the relationship of bits 14&13 and the Read/Write operations depending on codec ID configuration.

| Bit 15      | Bit 14: Slot1 Valid Bit | Bit 13: Slot 2 Valid Bit | Read/Write Operation of      | Read/Wirte Operation of      |

|-------------|-------------------------|--------------------------|------------------------------|------------------------------|

| Valid Frame | (Command Address)       | (Command Data)           | Primary AK4543               | Secondary AK4543             |

| 1           | 1                       | 1                        | Read/Write(Normal Operation) | Ignore                       |

| 1           | 0                       | 1                        | Ignore                       | Ignore                       |

| 1           | 1                       | 0                        | Read: Normal Operation       | Ignore                       |

|             |                         |                          | Write: Ignore                |                              |

| 1           | 0                       | 0                        | Ignore                       | Read/Write(Normal Operation) |

AK4543 Addressing: Slot0 Tag Bits

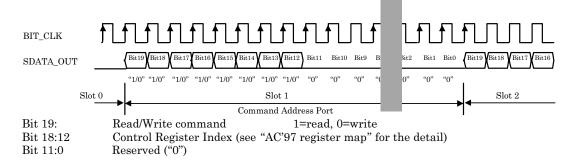

b)Slot1:Command Address Port

Slot1 gives the address of the command data, which is given in the slot 2. The AK4543 has 20 valid registers of 16bit data. See Page17(See AC'97 register map).

Bit18 is equivalent to the most significant bit of the index register address. The AK4543 ignores from bit11 to bit0. These bits will be reserved for future enhancement and must be stuffed with 0's by the AC'97 controller.

c)Slot2:Command Data Port

If bit19 in slot1 is "0", a write command, the AC'97 controller must output Command Data Port data in slot 2 *of the same frame*. If the bit19 in slot1 is "1", a read, the AK4543 will ignore any Command Data Port data in slot2.

Bit19 is equivalent to D15 bit of mixer register value.

d)Slot3 PCM Playback Left Channel (18bits) In the case of codec ID1:codec ID0=0:0 or 0:1, the AK4543 uses the playback(DAC) data format in slot3 for left channel. Playback data format is 18bits MSB first 2's complement. The AC'97 controller should stuff bits1-0 with "0". If valid bit (slot3) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data Bit 1:0 "0" e)Slot4 PCM Playback Right Channel (18bits) In the case of codec ID1:codec ID0=0:0 or 0:1, the AK4543 uses the playback(DAC) data format in the slot4 for right channel. Playback data format is MSB first. Data format is 18bits 2's complement. The AC'97 controller should stuff bits1-0 with "0". If valid bit (slot 4) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data Bit 1:0 "0" f)Slot5 is Not used in the AK4543 The AK4543 will ignore stuffed in this slot. g)Slot6 PCM Playback Left Channel (18bits) In case of codec ID1:codec ID0=1:1, the AK4543 uses the playback(DAC) data in slot 6 for left channel. Playback data format is 18bits MSB first 2's complement. The AC'97 controller should stuff bit1-0 with "0". If valid bit (slot6) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data Bit 1:0 "0" h)Slot7 PCM Playback Left Channel (18bits) In case of codec ID1:codec ID0=1:0, the AK4543 uses the playback(DAC) data in slot7 for left channel. Playback data format is 18bits MSB first 2's complement. The AC'97 controller should stuff bit1-0 with "0". If valid bit (slot7) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data Bit 1:0 "0" i)Slot8 PCM Playback Right Channel (18bits) In case of codec ID1:codec ID0=1:0, the AK4543 uses the playback(DAC) data in slot8 for right channel. Playback data format is 18bits MSB first 2's complement. The AC'97 controller should stuff bit1-0 with "0". If valid bit (slot8) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data "0" Bit 1:0 j)Slot9 PCM Playback Right Channel (18bits) In case of codec ID1:codec ID0=1:1, the AK4543 uses the playback(DAC) data in slot 9 for right channel. Playback data format is 18bits MSB first 2's complement. The AC'97 controller should stuff bit1-0 with "0". If valid bit (slot9) in the slot 0 is invalid ("0"), the AK4543 interprets the data as all "0". Bit19:2 Playback data Bit 1:0 "0"

k)Slot10-12 is Not used in the AK4543 The AK4543 will ignore stuffed in these data slots. ■AC-link Input Frame(SDATA\_IN)

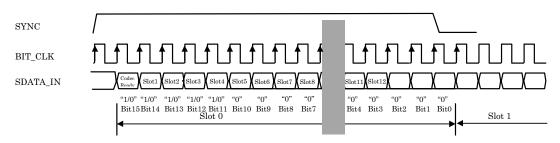

Each AC-link frame consists of one 16bit tag phase and twelve 20bit slots used for data and control.

a)Slot0

Slot0 is a special frame, and consists of 16bits. Slot0 is also called the "Tag phase". The AK4543 supports bits 15-11 and bits1-0. Each bit indicates "1"=valid(normal operation) or ready, "0"=invalid(abnormal operation) or not ready.

If the first bit in the slot 0 is valid, the AK4543 is ready for normal operation. <sup>3</sup>If the "Codec Ready" bit is invalid, the following bits and remaining slots are all "0". The AC'97 controller should ignore the following bits in the slot 0 and all other slots.

Bit 14 means that Slot 1(Status Address) output is valid or invalid. And Bit 13 means that Slot 2(Status Data ) is valid or invalid.

The following table shows the relationship between Bit 14,13 and each Status of the AK4543.

| Bit 15        | Bit 14           | Bit 13        | Status                                                                                                                                                                                                                                                                                                           |

|---------------|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Codec Ready) | (Status Address) | (Status Data) |                                                                                                                                                                                                                                                                                                                  |

| 1             | 1                | 1             | There is a Read Command in the previous frame.<br>Then both Slot 1 and Slot 2 output normal data.<br>If the access to non-implemented register or odd register is requested, the AK4543<br>returns "valid 7-bit register address in slot 1 and returns "valid"0000h data in slot<br>2 on the next AC-link frame. |

| 1             | 1                | 0             | Prohibited or non-existing                                                                                                                                                                                                                                                                                       |

| 1             | 0                | 0             | There is no Read Command in the previous frame. Both Slot 1 and Slot 2 output All'O'.                                                                                                                                                                                                                            |

| 1             | 0                | 1             | Prohibited or non-existing                                                                                                                                                                                                                                                                                       |

Note 1). The above Read sequence is done as response for previous frames read command. That is, if the previous frame is a Write Command, AK4543 outputs bit14 ="0", bit13 ="0" and slot 1&2 = All"0".

Bit12 means the output of Slot 3(PCM(ADC) Left) is valid or invalid. And Bit 11 means the output of Slot 4(PCM(ADC)Left) is valid or invalid. Bits10-0 are filled with "0".

A new audio input frame begins with a low to high transition of SYNC. SYNC is synchronous to the rising edge of BIT\_CLK. On the immediately following falling edge of BIT\_CLK, the AK4543 samples the assertion of SYNC. This falling edge marks the time when both sides of AC-link are aware of the start of a new audio frame. On the next rising of BIT\_CLK, the AK4543 transitions SDATA\_IN into the first bit position of slot 0 ("Codec Ready" bit). Each new bit position is presented to AC-link on a rising edge of BIT\_CLK, and subsequently sampled by the AC '97 controller on the following falling edge of BIT\_CLK. This sequence ensures that data transitions, and subsequent sample points for both incoming and outgoing data streams are time aligned.

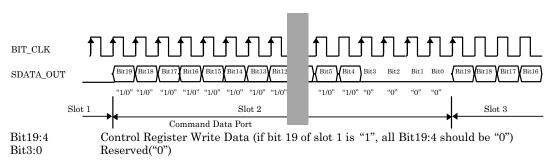

b)Slot1 Status Address Port

Audio input frame slot1's stream echoes the control register index, for historical reference, for the data to be returned in slot2. (Assuming that slots1 valid bit and slot2 valid bit in the slot0 had been tagged "valid" by the AK4543)

<sup>3</sup> When the AC'97 is not ready for normal operation, output bits are not specified in this documents and should be considered as invalid.

This address shows the register index for which data is being returned in the slot2. This address port is a copy of slot1 of the output frame, and index address input to SDATA\_OUT is loop ed back to the AC'97 controller through SDATA\_IN. This allows the controller to insure the AK4543 receives the correct data.

#### c)Slot2: Status Data Port

Status data addressed by the command address port of Output Stream is output through SDATA\_IN pin.Bit19:4Control Register Read Data (the contents of indexed address in the slot 1)Bit3:0"0"

Note that the address of Status Data Port data is consistent with Status Address Port data of slot 1 *in the same frame*. If the read operation is issued in the frame N by the AC'97 controller, Status Data Port data is output through SDATA\_IN in the frame N+1. Note that data is only available in this frame, only one time and that the following frames are invalid if another read operation is not issued.

d)Slot3: PCM Record Left Channel

Record(ADC) data format is 18bits MSB first 2's complement. Lower 2bits of the frame are ignored. If ADC block is powered down, slot-3 valid bit in the slot 0 is invalid ("0"), and data is as all "0".

Bit19:2 Audio ADC left channel output Bit1:0 "0"

e)Slot4: PCM Record Right Channel

Record(ADC) data format is 18bits MSB first 2's complement. Lower 2bits of the frame are ignored. If ADC block is powered down, slot-4 valid bit in the slot 0 is invalid ("0"), and data is as all "0". Bit19:2 Audio ADC right channel output Bit1:0 "0"

f)Slot5: Modem Line Codec The AK4543 does not incorporate the modem codec, all bits are stuffed with "0" in this slot. Bit19:0 "0"

g)Slot6: Microphone Record Data The AK4543 does not incorporate the 3<sup>rd</sup> ADC for microphone, all bits are stuffed with "0" in this slot. Bit19:0 "0"

h)Slots7-12 Reserved for future enhancement Bits19:0 "0"

# ■AC'97 Register Map

Each Register is a 16bit word.

Note: The AK4543 outputs "valid" 0000h if the controller reads an unused or invalid register address.

| Reg<br>Num | Name                | D15  | D14 | D13 | D12 | D11 | D10 | D9   | D8      | D7   | D6   | D5  | D4  | D3  | D2  | D1  | D0  | Default |

|------------|---------------------|------|-----|-----|-----|-----|-----|------|---------|------|------|-----|-----|-----|-----|-----|-----|---------|

| 00h        | Reset               | 0    | "0" | "1" | "0" | "1" | "1" | "0"  | "1"     | "0"  | "1"  | "0" | "1" | "0" | "0" | "0" | "0" | 2D50h   |

| 02h        | Master Volume       | Mute | X   | ML5 | ML4 | ML3 | ML2 | ML1  | ML<br>0 | X    | X    | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 | 8000h   |

| 04         | LINVL Volume        | Mute | Х   | ML5 | ML4 | ML3 | ML2 | ML1  | ML<br>0 | Х    | Х    | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 | 8000h   |

| 06h        | Master Volume Mono  | Mute | Х   | Х   | Х   | Х   | Х   | Х    | X       | Х    | Х    | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 | 8000h   |

| 0Ah        | PC_BEEP Volume      | Mute | Х   | Х   | Х   | Х   | Х   | Х    | Х       | Х    | Х    | Х   | PV3 | PV2 | PV1 | PV0 | Х   | 0000h   |

| 0Ch        | Phone Volume        | Mute | Х   | Х   | Х   | Х   | Х   | Х    | Х       | Х    | Х    | Х   | GN4 | GN3 | GN2 | GN1 | GN0 | 8008h   |

| 0Eh        | Mic Volume          | Mute | Х   | Х   | Х   | Х   | Х   | Х    | Х       | Х    | 20dB | Х   | GN4 | GN3 | GN2 | GN1 | GN0 | 8008h   |

| 10h        | Line In Volume      | Mute | Х   | Х   | GL4 | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | GR4 | GR3 | GR2 | GR1 | GR0 | 8808h   |

| 12h        | CD Volume           | Mute | Х   | Х   | GL4 | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | GR4 | GR3 | GR2 | GR1 | GR0 | 8808h   |

| 14h        | Video Volume        | Mute | Х   | Х   | GL4 | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | GR4 | GR3 | GR2 | GR1 | GR0 | 8808h   |

| 16h        | Aux Volume          | Mute | Х   | Х   | GL4 | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | GR4 | GR3 | GR2 | GR1 | GR0 | 8808h   |

| 18h        | PCM Out Volume      | Mute | Х   | Х   | GL4 | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | GR4 | GR3 | GR2 | GR1 | GR0 | 8808h   |

| 1Ah        | Record Select       | Х    | Х   | Х   | Х   | Х   | SL2 | SL1  | SL0     | Х    | Х    | Х   | Х   | Х   | SR2 | SR1 | SR0 | 0000h   |

| 1Ch        | Record Gain         | Mute | Х   | Х   | Х   | GL3 | GL2 | GL1  | GL0     | Х    | Х    | Х   | Х   | GR3 | GR2 | GR1 | GR0 | 8000h   |

| 20h        | General Purpose     | POP  | Х   | 3D  | Х   | Х   | Х   | MIX  | MS      | LPBK | Х    | Х   | Х   | Х   | Х   | Х   | Х   | 0000h   |

| 22h        | 3D Control          | Х    | Х   | Х   | Х   | Х   | Х   | Х    | Х       | Х    | Х    | Х   | Х   | Х   | Х   | DP1 | DP0 | 0000h   |

| 26h        | Powerdown Ctrl/Stat | PR7  | PR6 | PR5 | PR4 | PR3 | PR2 | PR1  | PR0     | Х    | Х    | Х   | Х   | REF | ANL | DAC | ADC | na      |

| 28h        | Extended Audio ID   | ID1  | ID0 | Х   | Х   | Х   | Х   | AMAP | Х       | Х    | Х    | Х   | Х   | Х   | Х   | Х   | Х   | x200h   |

| 7Ch        | Vendor ID1          | "0"  | "1" | "0" | "0" | "0" | "0" | "0"  | "1"     | "0"  | "1"  | "0" | "0" | "1" | "0" | "1" | "1" | 414Bh   |

| 7Eh        | Vendor ID2          | "0"  | "1" | "0" | "0" | "1" | "1" | "0"  | "1"     | "0"  | "0"  | "0" | "0" | "0" | "0" | "1" | "0" | 4D02h   |

\*) Vender ID of AKM is "AKM" :This ID has been approved by Intel.

\*) The AK4543 outputs "X" bits as "0".

\*) A write on "Invalid" registers will not affect the operation of the AK4543.

\*) ANL, DAC, ADC Bit in register 26h are all "0" following cold reset. When each section is ready for normal operation, the coresponding bit becomes "1". The Powerdown register(26h) is not affected by a write to Reset register(0h). See "Mixer Registers" in AC'97 specification for details. Vref is controlled only by PR3.

■Reset Register (Index 00h)

<Write>

When any value is written to this register, all registers in the AK4543 except for register "26h" Powerdown Ctrl/Stat Register are reset to the default values. The value of this register is not altered.

<Read>

Reading this register returns "2D50h" composed of the ID code of the part, a code for the type of 3D enhancement,  $18\,$

bit ADC/DAC resolution, and a code for True Line Level Out.

\*Setting D14 – D10 "01011" means AKM 3D enhancement which is registered in Audio Codec '97 Component Specification Rev 1.03 and 2.1 .

\*Setting D8 "1" indicates 18bit ADC resolution and D6"1" does DAC resolution.

\*Setting D4 "1" means True Line Level Out is supported with Volume Control(Index 04h).

Play Master Volume Registers (Index 02h,06h) and LINVL(True Line Level Out) Volume Register(Index 04h)

The following table shows the relationship between bits and the attenuation value with step size of 1.5dB. The AK4543 has a range of 0dB to -46.5dB. The AK4543 does not support the optional MX5 bit.

**The AK4543** detects when MX5 is set and set all 5 LSBs to 1s. Example: When the driver writes a "01xxxxx" the AK4543 interpret that as "0011111". When this register is read, the returned value is "0011111".

| Mute | MX5 | MX4 | MX3 | MX2 | MX1 | MX0 | Att.    |

|------|-----|-----|-----|-----|-----|-----|---------|

| 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0dB     |

| 0    | 0   | 0   | 0   | 0   | 0   | 1   | -1.5dB  |

| 0    | 0   | 0   | 0   | 0   | 1   | 0   | -3.0dB  |

| 0    | 0   | 0   | 0   | 0   | 1   | 1   | -4.5dB  |

| -    |     |     |     |     |     |     |         |

| 0    | 0   | 1   | 1   | 1   | 1   | 0   | -45.0dB |

| 0    | 0   | 1   | 1   | 1   | 1   | 1   | -46.5dB |

| -    |     |     |     |     |     |     |         |

| 0    | 1   | Х   | Х   | Х   | Х   | Х   | -46.5dB |

| -    |     |     |     |     |     |     |         |

| 1    | Х   | Х   | Х   | Х   | Х   | Х   | Mute    |

# ■ PC Beep Register (Index 0Ah)

The following table shows the relationship between bits and the attenuation value. The attenuation step is -3dB with a range of 0 to -45dB. PC\_BEEP of the AK4543 is mute off at default state.

The PC Beep is routed to L & R Line outputs directly when AK4543 is in a RESET State(Reset# is "L"). This is so that Power on Self Test(POST) codes can be heard by the user in case of a hardware problem with the PC. After Reset# goes "H", direct PC beep pass thru becomes OFF.

| Mute | PV3 | PV2 | PV1 | PV0 | Att.    |

|------|-----|-----|-----|-----|---------|

| 0    | 0   | 0   | 0   | 0   | 0dB     |

| 0    | 0   | 0   | 0   | 1   | -3.0dB  |

| 0    | 0   | 0   | 1   | 0   | -6.0dB  |

|      |     |     |     |     |         |

| 0    | 1   | 1   | 1   | 1   | -45.0dB |

| 1    | Х   | Х   | Х   | Х   | Mute    |

■ Analog Mixer Input Gain Registers (Index 0Ch-18h)

The following table shows the relationship between bits and the gain/attenuation value. Attenuation step is 1.5dB with a range of +12dB to -34.5dB.

| Mute | Gx4 | Gx3 | Gx2 | Gx1 | Gx0 | Att.    |

|------|-----|-----|-----|-----|-----|---------|

| 0    | 0   | 0   | 0   | 0   | 0   | +12dB   |

| 0    | 0   | 0   | 0   | 0   | 1   | +10.5dB |

|      |     |     |     |     |     |         |

| 0    | 0   | 1   | 0   | 0   | 0   | 0 dB    |

| 0    | 0   | 1   | 0   | 0   | 1   | -1.5dB  |

|      |     |     |     |     |     |         |

| 0    | 1   | 1   | 1   | 1   | 0   | -33.0dB |

| 0    | 1   | 1   | 1   | 1   | 1   | -34.5dB |

| 1    | Х   | Х   | Х   | Х   | Х   | Mute    |

■ Record Select Control Register (Index 1Ah)

| SR2 | SR1 | SR0 | Att.           |

|-----|-----|-----|----------------|

| 0   | 0   | 0   | Mic            |

| 0   | 0   | 1   | CD In (R)      |

| 0   | 1   | 0   | Video In (R)   |

| 0   | 1   | 1   | Aux In (R)     |

| 1   | 0   | 0   | Line In (R)    |

| 1   | 0   | 1   | Stereo Mix (R) |

| 1   | 1   | 0   | Mono Mix       |

| 1   | 1   | 1   | Phone          |

| SR2 | SL1 | SL0 | Att.           |

|-----|-----|-----|----------------|

| 0   | 0   | 0   | Mic            |

| 0   | 0   | 1   | CD In (L)      |

| 0   | 1   | 0   | Video In (L)   |

| 0   | 1   | 1   | Aux In (L)     |

| 1   | 0   | 0   | Line In (L)    |

| 1   | 0   | 1   | Stereo Mix (L) |

| 1   | 1   | 0   | Mono Mix       |

| 1   | 1   | 1   | Phone          |

# ■ Record Gain Register (Index 1Ch)

| Mute | Gx3 | Gx2 | Gx1 | Gx0 | Gain    |

|------|-----|-----|-----|-----|---------|

| 0    | 0   | 0   | 0   | 0   | 0 dB    |

| 0    | 0   | 0   | 0   | 1   | 1.5 dB  |

| 0    | 0   | 0   | 1   | 0   | 3.0 dB  |

|      |     |     |     |     |         |

| 0    | 1   | 1   | 1   | 1   | 22.5 dB |

| 1    | Х   | Х   | Х   | Х   | Mute    |

# ■ General Purpose Register (Index 20h)

The following table indicates how to control several miscellaneous functions of the AK4543.

|      | Bit | Function                     |

|------|-----|------------------------------|

| POP  | D15 | PCM(DAC) Bypass 3D           |

|      |     | 0= Via 3D Path, 1= 3D Bypass |

| 3D   | D13 | 3D Stereo Enhancement        |

|      |     | 0=Off, 1=On                  |

| MIX  | D9  | Mono Output Select           |

|      |     | 0=Mix, 1=Mic                 |

| MS   | D8  | Mic Select                   |

|      |     | 0=Mic1, 1 =Mic2              |

| LPBK | D7  | ADC/DAC Loopback Mode        |

|      |     | 1= Loopback                  |

An active bit("1") in D15(POP) will pass DAC output to Line\_OUT or LNLVL\_OUT directly, while a "0" in D15 will put DAC output into Input Mixers or AKM's 3D enhancement circuit.

D13(3D) will activate the AKM's 3D enhancement.

LPBK(ADC/DAC Loopback Mode) bit enables loopback of the ADC output to slot3 &4 of DAC input for both the Primary codec and Secondary codec on the same AC-Link Generally done for system testing.

■ 3D Control Register (Index 22h)

The following table shows the relationship between the bit and depth of 3D enhancement.

| DP1 | DP0 | Depth | Recommended Application |

|-----|-----|-------|-------------------------|

| 0   | 0   | 0%    | Off                     |

| 0   | 1   | 50%   | Audio                   |

| 1   | 0   | 70%   | Audio                   |

| 1   | 1   | 100%  | Game                    |

#### ■ Powerdown Control/Status Register (Index 26h)

BitsD0 to D3 are read only status bits. Any write to these bits will not affect the operation of the AK4543. These bits are used as status bits to subsections of the AC'97 codec. A "1" indicates the subsection of the AK4543 is "ready" or that is capable of performing in normal operation.

|     | Bit | Function                           |

|-----|-----|------------------------------------|

| REF | D3  | Vref up to nominal state           |

|     |     | 0=NOT ready, 1=ready,              |

| ANL | D2  | Analog mixers, etc ready           |

|     |     | 0=NOT ready, 1=ready               |

| DAC | D1  | DAC section ready to accept data   |

|     |     | 0=NOT ready, 1=ready               |

| ADC | D0  | ADC section ready to transmit data |

|     |     | 0=NOT ready, 1=ready               |

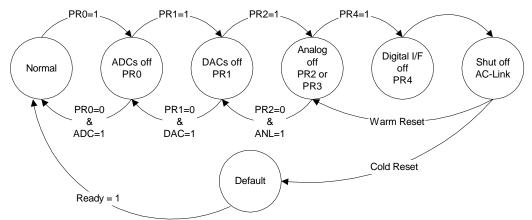

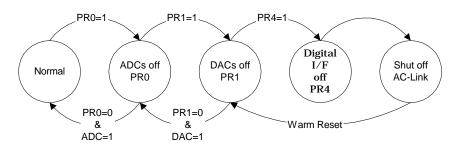

The power down modes are as follows.

|     | Bit | Function                               |

|-----|-----|----------------------------------------|

| PR0 | D8  | PCM in ADC's & Input Mux Powerdown     |

| PR1 | D9  | PCM out DACs Powerdown                 |

| PR2 | D10 | Analog Mixer Powerdown (Vref still on) |

| PR3 | D11 | Analog Mixer Powerdown (Vref off)      |

| PR4 | D12 | Digital Interface (AC-link) Powerdown  |

| PR5 | D13 | Internal Clk disable                   |

| PR6 | D14 | True Line Level Out Powerdown          |

| PR7 | D15 | EAPD(External Amplifier Powerdown)     |

When PR3 is set to "1", the ADC, DAC, Mixer, True Line Level Out, and VREF are powered down even if any PRx bit are "0". When PR3 bit is reset to "0", the AK4543 resumes the previous state by referencing previous PRx bit. In this case, the AK4543 outputs corresponding slot-x valid bits in the slot 0 as "0" until the AK4543 results in normal operation(Codec Ready).

EAPD(External Amplifier Power Down) bit controls an external audio amplifier. EAPD="0" places a "0"(L) on the output pin, enabling an external audio amplifier, EAPD="1"(H) shuts it down. Powered up default is EAPD="0"(external audio amplifier enabled).

## ■ Extended Audio ID(Index 28h)

The Extended Audio ID(28h) is a read only register. 2bits D15&D14 can be read for codec identification. D15,14 are automatically set with the codec ID1#(46pin) and ID0#(45pin). ID1# and ID0# can be strapped and adopt inverted polarity and default to 00=Primary(via internal pull up) when left floating. Depended on codec ID configuration, the AK4543 is assigned to Primary codec or Secondary codec. Note that codec ID configuration has to be fixed before Powering up of the device.

| ID1#(p     | in 46) | ID0#(pi    | n45)  | Configuration  |

|------------|--------|------------|-------|----------------|

| Physical   | Logic  | Physical   | Logic | (Codec ID)     |

| Connection | Value  | Connection | Value |                |

| NC         | 0      | NC         | 0     | Primary ID00   |

| NC         | 0      | GND        | 1     | Secondary ID01 |

| GND        | 1      | NC         | 0     | Secondary ID10 |

| GND        | 1      | GND        | 1     | Secondary ID11 |

The AMAP (bit D9 of this read only register) will always be set to "1" indicating that DAC input slot will follow to AC'97 recommendation as shown in next table.(CODEC ID is configured via ID1#m ID0# pins) The audio DAC mapping can be changed based on the codec ID configuration.

| Codec ID | AC-link Frame Data u                   | used for DACs | Comments                     |

|----------|----------------------------------------|---------------|------------------------------|

|          | PCM Left DAC uses PCM Right DAC        |               |                              |

|          | data from Slot# uses data from Slot# 1 |               | Expected use                 |

| 00       | 3                                      | 4             | Original Definition(Master)  |

| 01       | 3                                      | 4             | Original Definition(Docking) |

| 10       | 7                                      | 8             | Left/Right surround channels |

| 11       | 6                                      | 9             | Center/LFE channels          |

■ Vendor ID Registers (Index 7Ch, 7Eh)

This register is a read only register that is used to determine the specific vendor identification. The ID method is Microsoft Plug and Play Vendor ID code with upper byte of 7Ch register, the first character of that id, lower byte of 7Ch register, the second character and upper byte of 7Eh register the third character. These three characters are ASCII encoded. Lower byte of 7E register is for the Vendor Revision number.

AKM's vender ID is "AKM", and revision number is 02. As ASCII code "A" is 41h, "K" is 4Bh, and "M" is 4Dh, Vendor ID registers are 414Bh and 4D02h respectively.

<M0046-E-01>

- 22 -

[AK4543]

[ASAHI KASEI]

## ■Power Management/Low Power Modes

The AK4543 is capable of operating at multiple reduced power modes for when no activity is required. The state of power down is controlled by the Powerdown Register (26h). There are 8 separate commands for power down. See the table below for the different modes. As the AK4543 operates at static mode, the registers will not lose their values even if the master clock is stopped only upon power.

|         | ADC        | DAC          | Mixer      | VREF       | ACLINK     | Internal CLK | LNLVL_OUT  | EAPD       |

|---------|------------|--------------|------------|------------|------------|--------------|------------|------------|

| PR0="1" | PD         | don't care   | don't care | don't care | Don't care | don't care   | don't care | don't care |

| PR1="1" | don't care | PD           | don't care | don't care | Don't care | don't care   | don't care | don't care |

| PR2="1" | don't care | don't care   | PD         | don't care | Don't care | don't care   | PD         | don't care |

|         |            | (No DAC out) |            |            |            |              |            |            |

| PR3="1" | PD         | PD           | PD         | PD         | Don't care | don't care   | PD         | don't care |

| PR4="1" | PD         | PD           | don't care | don't care | PD         | don't care   | don't care | don't care |

| PR5="1" | PD         | PD           | don't care | don't care | PD         | PD           | don't care | don't care |

| PR6="1" | don't care | don't care   | don't care | don't care | Don't care | don't care   | PD         | don't care |

| PR7="1" | don't care | don't care   | don't care | don't care | Don't care | don't care   | don't care | PD         |

#### Powerdown Mode Truth Table

\*: PD means Powerdown .

\*: No DAC out means that there is no PCM out because mixer is disabled.