# Asahi **KASEI**

**ASAHI KASEI EMD**

# **AK4397**

# **High Performance Premium 32-Bit DAC**

#### 概要

AK4397は、DVD-Audioの192kHzサンプリングモードに対応した高性能プレミアム32ビットDACです。 ΔΣ変調器には新開発のアドバンスト・マルチビット方式を採用、従来のシングルビット方式の優れた低 歪特性に加えて、さらに広いダイナミックレンジを実現しています。内蔵のポストフィルタにはスイッチトキャパシタフィルタ(SCF)を採用し、クロックジッタによる精度の劣化を改善します。ディジタル入力は192kHzのPCM入力とDSD入力の両方に対応しており、DVD-Audio, SACD等のシステムに最適です。AK4397はAK4393/4/5/6と機能的な互換性を持ちかつ低消費電力を実現します

#### 特長

- 128倍オーバサンプリング

- サンプリングレート: 30kHz~216kHz

- 32ビット8倍ディジタルフィルタ(スローロールオフ オプション) 内蔵

- Ripple: ±0.005dB, Attenuation: 75dB

- ・強ジッタ耐力

- 低歪差動出力

- DSD入力対応

- 32, 44.1, 48kHz対応ディジタルディエンファシス内蔵

- ソフトミュート

- ディジタルATT(リニア 256ステップ)

- THD+N: -103dB

- DR, S/N: 120dB

- オーディオI/Fフォーマット: 24/32ビット前詰め, 16/20/24/32ビット後詰め, I<sup>2</sup>S, DSD

- マスタクロック 通常速: 256fs, 384fs, 512fs, 768fs or 1152fs

2倍速 : 128fs, 192fs, 256fs or 384fs

4倍速 : 128fs or 192fs DSD : 512fs or 768fs

- 電源電圧: 4.75 ~ 5.25V

- ディジタル入力レベル: TTL

- パッケージ: 44ピンLQFP

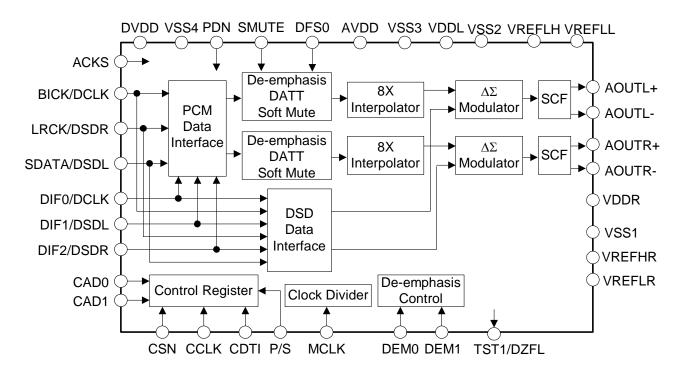

### ■ プロック図

Block Diagram

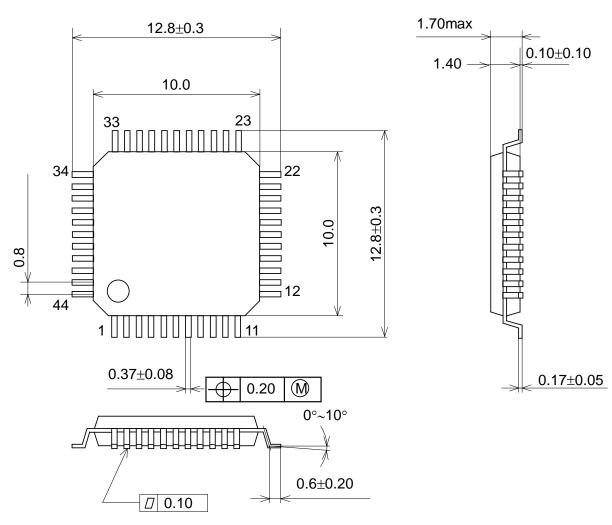

# ■ オーダリングガイド

AK4397EQ  $-10\sim +70^{\circ}$ C 44pin LQFP (0.8mm pitch) AKD4397 AK4397評価用ボード

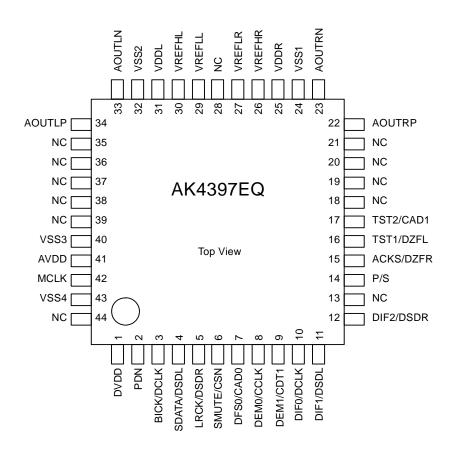

### ■ ピン配置

# ピン / 機能

| No. | Pin Name | I/O | Function                                                                 |  |  |  |  |  |

|-----|----------|-----|--------------------------------------------------------------------------|--|--|--|--|--|

| 1   | DVDD     | -   | Digital Power Supply Pin, 4.75 ~ 5.25V                                   |  |  |  |  |  |

|     |          |     | Power-Down Mode Pin                                                      |  |  |  |  |  |

| 2   | PDN      | I   | When at "L", the AK4397 is in power-down mode and is held in reset.      |  |  |  |  |  |

|     |          |     | The AK4397 should always be reset upon power-up.                         |  |  |  |  |  |

| 3   | BICK     | I   | Audio Serial Data Clock Pin in PCM Mode                                  |  |  |  |  |  |

| 3   | DCLK     | I   | DSD Clock Pin in DSD Mode                                                |  |  |  |  |  |

| 4   | SDATA    | I   | Audio Serial Data Input Pin in PCM Mode                                  |  |  |  |  |  |

| 4   | DSDL     | I   | DSD Lch Data Input Pin in DSD Mode                                       |  |  |  |  |  |

| 5   | LRCK     | I   | L/R Clock Pin in PCM Mode                                                |  |  |  |  |  |

| 3   | DSDR     | I   | DSD Rch Data Input Pin in DSD Mode                                       |  |  |  |  |  |

|     |          |     | Soft Mute Pin in Parallel Mode                                           |  |  |  |  |  |

| 6   | SMUTE    | I   | When this pin goes "H", soft mute cycle is initiated.                    |  |  |  |  |  |

| 0   |          |     | When returning "L", the output mute releases.                            |  |  |  |  |  |

|     | CSN      | I   | Chip Select Pin in Serial Mode                                           |  |  |  |  |  |

| 7   | DFS0     | I   | Sampling Speed Mode Select Pin in Parallel Mode (Internal pull-down pin) |  |  |  |  |  |

| /   | CAD0     | I   | Chip Address 0 Pin in Serial Mode (Internal pull-down pin)               |  |  |  |  |  |

| 8   | DEM0     | I   | De-emphasis Enable 0 Pin in parallel mode                                |  |  |  |  |  |

| 0   | CCLK     | I   | Control Data Clock Pin in serial mode                                    |  |  |  |  |  |

| 9   | DEM1     | I   | De-emphasis Enable 1 Pin in Parallel Mode                                |  |  |  |  |  |

| 9   | CDTI     | I   | Control Data Input Pin in Serial Mode                                    |  |  |  |  |  |

| 10  | DIF0     | I   | Digital Input Format 0 Pin in PCM Mode                                   |  |  |  |  |  |

| 10  | DCLK     | I   | DSD Clock Pin in DSD Mode                                                |  |  |  |  |  |

| 11  | DIF1     | I   | Digital Input Format 1 Pin in PCM Mode                                   |  |  |  |  |  |

| 11  | DSDL     | I   | DSD Lch Data Input Pin in DSD Mode                                       |  |  |  |  |  |

| 12  | DIF2     | I   | Digital Input Format 2 Pin in PCM Mode                                   |  |  |  |  |  |

| 12  | DSDR     | I   | DSD Rch Data Input Pin in DSD Mode                                       |  |  |  |  |  |

| 13  | NC       |     | No internal bonding.                                                     |  |  |  |  |  |

| 13  | NC       | •   | Connect to GND.                                                          |  |  |  |  |  |

Note: All input pins except internal pull-up/down pins should not be left floating.

|     |                |              | Parallel/Serial Select Pin                    | (Internal pull-up pin)   |  |  |  |  |

|-----|----------------|--------------|-----------------------------------------------|--------------------------|--|--|--|--|

| 14  | P/S            | I            | "L": Serial Mode, "H": Parallel Mode          | ( 1 11 /                 |  |  |  |  |

| 15  | ACKS           | I            | Master Clock Auto Setting Mode Pin in Paralle | l Mode                   |  |  |  |  |

| 13  | DZFR           | О            | Rch Zero Input Detect Pin in Serial Mode      |                          |  |  |  |  |

|     |                |              | Test 1 Pin in Parallel Mode                   |                          |  |  |  |  |

| 16  | TST1           | О            | Should be open.                               |                          |  |  |  |  |

|     | DZFL           | О            | Lch Zero Input Detect Pin in Serial Mode      |                          |  |  |  |  |

|     | TROTT <b>S</b> |              | Test 2 Pin in Parallel Mode                   | (Internal pull-down pin) |  |  |  |  |

| 17  | TST2           | I            | Connect to GND.                               |                          |  |  |  |  |

|     | CAD1           | I            | Chip Address 1 Pin in Serial Mode             | (Internal pull-down pin) |  |  |  |  |

| 1.0 | NG             |              | No internal bonding.                          |                          |  |  |  |  |

| 18  | NC             | _            | Connect to GND.                               |                          |  |  |  |  |

| 10  | NC             |              | No internal bonding.                          |                          |  |  |  |  |

| 19  | NC             | -            | Connect to GND.                               |                          |  |  |  |  |

| 20  | NC             |              | No internal bonding.                          |                          |  |  |  |  |

| 20  | IVC            | _            | Connect to GND.                               |                          |  |  |  |  |

| 21  | NC             | _            | No internal bonding.                          |                          |  |  |  |  |

|     |                |              | Connect to GND.                               |                          |  |  |  |  |

| 22  | AOUTRP         | О            | Rch Positive Analog Output Pin                |                          |  |  |  |  |

| 23  | AOUTRN         | О            | Rch Negative Analog Output Pin                |                          |  |  |  |  |

| 24  | VSS1           | -            | Ground Pin                                    |                          |  |  |  |  |

| 25  | VDDR           | -            | Rch Analog Power Supply Pin, 4.75 ~ 5.25V     |                          |  |  |  |  |

| 26  | VREFHR         | I            | Rch High Level Voltage Reference Input Pin    |                          |  |  |  |  |

| 27  | VREFLR         | I            | Rch Low Level Voltage Reference Input Pin     |                          |  |  |  |  |

| 28  | NC             |              | No internal bonding.                          |                          |  |  |  |  |

| 20  | INC            | -            | Connect to GND.                               |                          |  |  |  |  |

| 29  | VREFLL         | I            | Lch Low Level Voltage Reference Input Pin     |                          |  |  |  |  |

| 30  | VREFHL         | I            | Lch High Level Voltage Reference Input Pin    |                          |  |  |  |  |

| 31  | VDDL           | -            | Lch Analog Power Supply Pin, 4.75 ~ 5.25V     |                          |  |  |  |  |

| 32  | VSS2           | -            | Ground Pin                                    |                          |  |  |  |  |

| 33  | AOUTLN         | О            | Lch Negative Analog Output Pin                |                          |  |  |  |  |

| 34  | AOUTLP         | О            | Lch Positive Analog Output Pin                |                          |  |  |  |  |

| 2.5 | NC             |              | No internal bonding.                          |                          |  |  |  |  |

| 35  | NC             | -            | Connect to GND.                               |                          |  |  |  |  |

| 36  | NC             |              | No internal bonding.                          |                          |  |  |  |  |

| 50  | TVC            |              | Connect to GND.                               |                          |  |  |  |  |

| 37  | NC             | _            | No internal bonding.                          |                          |  |  |  |  |

|     |                |              | Connect to GND.                               |                          |  |  |  |  |

| 38  | NC             | -            | No internal bonding. Connect to GND.          |                          |  |  |  |  |

|     |                |              | No internal bonding.                          |                          |  |  |  |  |

| 39  | NC             | -            | Connect to GND.                               |                          |  |  |  |  |

| 40  | VSS3           | _            | Ground Pin                                    |                          |  |  |  |  |

| 41  | AVDD           | _            | Analog Power Supply Pin, 4.75 ~ 5.25V         |                          |  |  |  |  |

| 42  | MCLK           | I            | Master Clock Input Pin                        |                          |  |  |  |  |

| 43  | VSS4           | _            | Ground Pin                                    |                          |  |  |  |  |

| 43  |                | <del>-</del> | No internal bonding.                          |                          |  |  |  |  |

| 44  | NC             | -            | Connect to GND.                               |                          |  |  |  |  |

|     | I              | I            | Comitet to Grab.                              |                          |  |  |  |  |

Note: All input pins except internal pull-up/down pins should not be left floating.

# ■ 使用しないピンの処理について

使用しない入出力ピンは下記の設定を行い、適切に処理して下さい。

(1) パラレルモード (PCMモードのみ)

| 区分      | ピン名            | 設定      |

|---------|----------------|---------|

| Analog  | AOUTLP, AOUTLN | オープン    |

| Analog  | AOUTRP, AOUTRN | オープン    |

|         | SMUTE          | VSS4に接続 |

| Digital | TST1           | オープン    |

|         | TST2           | VSS4に接続 |

### (2) シリアルモード

#### 1. PCMモード

| 区分      | ピン名              | 設定      |

|---------|------------------|---------|

| Analog  | AOUTLP, AOUTLN   | オープン    |

| Analog  | AOUTRP, AOUTRN   | オープン    |

| Dicital | DIF2, DIF1, DIF0 | VSS4に接続 |

| Digital | DZFL, DZFR       | オープン    |

#### 2. DSDモード

・#3, #4, #5ピンのDCLK, DSDL, DSDRを使用する場合

| 区分      | ピン名                             | 設定      |

|---------|---------------------------------|---------|

| Analog  | AOUTLP, AOUTLN                  | オープン    |

| Analog  | AOUTRP, AOUTRN                  | オープン    |

| Digital | DCLK(#10), DSDL(#11), DSDR(#12) | VSS4に接続 |

| Digital | DZFL, DZFR                      | オープン    |

・#10, #11, #12ピンのDCLK, DSDL, DSDRを使用する場合

| 区分      | ピン名                          | 設定      |

|---------|------------------------------|---------|

| Analog  | AOUTLP, AOUTLN               | オープン    |

|         | AOUTRP, AOUTRN               | オープン    |

| Digital | DCLK(#3), DSDL(#4), DSDR(#5) | VSS4に接続 |

|         | DZFL, DZFR                   | オープン    |

|                      | 絶対最大定格 |  |

|----------------------|--------|--|

| (VSS1-4 =0V; Note 1) |        |  |

| Parameter                           |                                        | Symbol | min  | max      | Units |

|-------------------------------------|----------------------------------------|--------|------|----------|-------|

| Power Supplies:                     | Power Supplies: Analog                 |        | -0.3 | 6.0      | V     |

|                                     | Analog                                 | VDDL/R | -0.3 | 6.0      | V     |

|                                     | Digital                                | DVDD   | -0.3 | 6.0      | V     |

| Input Current, Any                  | Input Current, Any Pin Except Supplies |        | -    | ±10      | mA    |

| Digital Input Voltage               |                                        | VIND   | -0.3 | DVDD+0.3 | V     |

| Ambient Temperature (Power applied) |                                        | Та     | -10  | 70       | °C    |

| Storage Temperatu                   | are                                    | Tstg   | -65  | 150      | °C    |

Note 1. 電圧は全てグランドピンに対する値です。

Note 2. VSS1-4 は同じアナロググランドに接続して下さい。

注意:この値を超えた条件で使用した場合、デバイスを破壊することがあります。 また通常の動作は保証されません。

|                      | 推奨動作条件 |  |

|----------------------|--------|--|

| (VCC1 4 =0V: Note 1) |        |  |

(VSS1-4=0V; Note 1)

| Parameter      |                       | Symbol   | min      | typ | max  | Units |

|----------------|-----------------------|----------|----------|-----|------|-------|

| D C 1:         | Analog                | AVDD     | 4.75     | 5.0 | 5.25 | V     |

| Power Supplies | Analog                | VDDL/R   | 4.75     | 5.0 | 5.25 | V     |

| (Note 3)       | Digital               | DVDD     | 4.75     | 5.0 | 5.25 | V     |

| Voltage        | "H" voltage reference | VREFHL/R | AVDD-0.5 | -   | AVDD | V     |

| Reference      | "L" voltage reference | VREFLL/R | VSS      | -   | -    | V     |

| (Note 4)       | VREFH – VREFL         | ΔVREF    | 3.0      | -   | AVDD | V     |

Note 1. 電圧は全てグランドピンに対する値です。

Note 3. AVDD, VDDL/R, DVDDの電源立ち上げシーケンスを考慮する必要はありません。

Note 4. アナログ出力電圧は(VREFH - VREFL)の電圧に比例します。

AOUT (typ.@0dB) =  $(AOUT+) - (AOUT-) = \pm 2.8Vpp \times (VREFHL/R - VREFLL/R)/5$ .

注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので十分ご注意下さい。

#### アナログ特性

(Ta=25°C; AVDD=VDDL/R=DVDD=5.0V; VSS1-4 =0V; VREFHL/R=AVDD, VREFLL/R= VSS; Input data = 24bit;  $R_L \ge 1k\Omega$ ; BICK=64fs; Signal Frequency = 1kHz; Sampling Frequency = 44.1kHz; Measurement bandwidth = 20Hz ~ 20kHz; External Circuit: Figure 18; unless otherwise specified.)

| Parameter                      | Parameter                            |           |       |          |       | Units  |

|--------------------------------|--------------------------------------|-----------|-------|----------|-------|--------|

| Resolution                     | Resolution                           |           |       |          | 24    | Bits   |

| <b>Dynamic Characteristics</b> | Dynamic Characteristics (Note 5)     |           |       |          |       |        |

| THD+N                          | fs=44.1kHz                           | 0dBFS     | -     | -103     | -93   | dB     |

|                                | BW=20kHz                             | -60dBFS   | =     | -57      | -     | dB     |

|                                | fs=96kHz                             | 0dBFS     | =     | 100      | -     | dB     |

|                                | BW=40kHz                             | -60dBFS   | -     | -54      | -     | dB     |

|                                | fs=192kHz                            | 0dBFS     |       | 100      | -     | dB     |

|                                | BW=40kHz                             | -60dBFS   |       | -54      | -     | dB     |

|                                | BW=80kHz                             | -60dBFS   |       | -51      | -     | dB     |

| Dynamic Range (-60dBFS w       | ith A-weighted)                      | (Note 6)  | 114   | 120      |       | dB     |

| S/N (A-weighted)               |                                      | (Note 7)  | 114   | 120      |       | dB     |

| Interchannel Isolation (1kHz   | )                                    |           | 100   | 110      |       | dB     |

| DC Accuracy                    |                                      |           |       |          |       |        |

| Interchannel Gain Mismatch     |                                      |           | =     | 0.15     | 0.3   | dB     |

| Gain Drift                     |                                      | (Note 8)  | -     | 20       | -     | ppm/°C |

| Output Voltage                 |                                      | (Note 9)  | ±2.65 | ±2.8     | ±2.95 | Vpp    |

| Load Capacitance               |                                      |           | -     | -        | 25    | pF     |

| Load Resistance                |                                      | (Note 10) | 1     | -        | -     | kΩ     |

| Power Supplies                 |                                      |           |       |          |       |        |

| Power Supply Current           |                                      |           |       |          |       |        |

|                                | n (PDN pin = "H")                    |           |       |          |       |        |

| AVDD+                          | · VDDL/R                             |           | -     | 32<br>21 | 47    | mA     |

|                                | DVDD ( $fs \le 96kHz$ )              |           |       |          | -     | mA     |

|                                | DVDD (fs = 192kHz)                   |           |       |          | 41    | mA     |

|                                | Power down (PDN pin = "L") (Note 11) |           |       |          |       |        |

| l l                            | VDDL/R+DVDD                          |           | -     | 10       | 100   | μΑ     |

| Power Supply Rejection         |                                      | (Note 12) | -     | 50       | -     | dB     |

- Note 5. Audio Precision System Two使用。平均値測定。測定結果は評価ボードマニュアルを参照下さい。

- Note 6. Figure 18 (回路例2)使用時。101dB at 16bit data and 118dB at 20bit data.

- Note 7. Figure 18 (回路例2)使用時。S/N比は入力ビット長に依存しません。

- Note 8. (VREFH VREFL)の電圧は+5V一定。

- Note 9. フルスケール電圧(0dB)。出力電圧は(VREFHL/R VREFLL/R)の電圧に比例します。 AOUT (typ.@0dB) = (AOUT+) – (AOUT-) = ±2.8Vpp × (VREFHL/R – VREFLL/R)/5.

- Note 10. Load Resistanceについては、AC負荷(DCカット用コンデンサあり)に対して1k ohm (min)です。Figure 18を参照してください。DC負荷(DCカット用コンデンサなし)に対して1.5k ohm (min)です。Figure 17を参照してください。Load Resistanceはグランドに対する値です。アナログ特性は出力ピンに接続される容量性負荷に敏感なため、容量性負荷が極力小さくなるようにしてください。

- Note 11. パワーダウン時、P/S pin = DVDD、それ以外の外部クロック(MCLK, BICK, LRCK)を含む 全てのディジタル入力をVSS4に固定した場合の値です。

- Note 12. VREFHL/R pinを+5Vに固定して、AVDD, DVDDに1kHz, 100mVppの正弦波を重畳した場合の値です。

# シャープロールオフ・フィルタ特性(fs = 44.1kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; Normal Speed Mode; DEM=OFF; SLOW bit="0")

| Parameter            |               |           | Symbol | min  | typ   | max    | Units |

|----------------------|---------------|-----------|--------|------|-------|--------|-------|

| Digital Filter       |               |           |        |      |       |        |       |

| Passband             | (Note 13)     | ±0.01dB   | PB     | 0    |       | 20.0   | kHz   |

|                      |               | -6.0dB    |        | =    | 22.05 | =      | kHz   |

| Stopband             |               | (Note 13) | SB     | 24.1 |       |        | kHz   |

| Passband Ripple      |               |           | PR     |      |       | ±0.005 | dB    |

| Stopband Attenuation | on            |           | SA     | 75   |       |        | dB    |

| Group Delay          |               | (Note 14) | GD     | -    | 28    | -      | 1/fs  |

| Digital Filter + SCF |               |           |        |      |       |        |       |

| Frequency Respons    | e: 0 ~ 20.0kH | [z        |        | -    | ±0.2  | -      | dB    |

# シャープロールオフ・フィルタ特性(fs = 96kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; Double Speed Mode; DEM=OFF; SLOW bit="0")

| Parameter           |                             |           | Symbol | min  | typ  | max    | Units |

|---------------------|-----------------------------|-----------|--------|------|------|--------|-------|

| Digital Filter      |                             |           |        |      |      |        |       |

| Passband            | (Note 13)                   | ±0.01dB   | PB     | 0    |      | 43.5   | kHz   |

|                     |                             | -6.0dB    |        | -    | 48.0 | -      | kHz   |

| Stopband            |                             | (Note 13) | SB     | 52.5 |      |        | kHz   |

| Passband Ripple     |                             |           | PR     |      |      | ±0.005 | dB    |

| Stopband Attenuat   | ion                         |           | SA     | 75   |      |        | dB    |

| Group Delay         |                             | (Note 14) | GD     | -    | 28   | Ī      | 1/fs  |

| Digital Filter + So | CF                          |           |        |      |      |        |       |

| Frequency Respon    | se: $0 \sim 40.0 \text{kH}$ | z         |        | -    | ±0.3 | -      | dB    |

### シャープロールオフ・フィルタ特性(fs = 192kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; Quad Speed Mode; DEM=OFF; SLOW bit="0")

| Parameter        | Parameter        |           |    | min | typ   | max    | Units |

|------------------|------------------|-----------|----|-----|-------|--------|-------|

| Digital Filter   |                  |           |    |     |       |        |       |

| Passband         | (Note 13)        | ±0.01dB   | PB | 0   |       | 87.0   | kHz   |

|                  |                  | -6.0dB    |    | -   | 96.0  | -      | kHz   |

| Stopband         |                  | (Note 13) | SB | 105 |       |        | kHz   |

| Passband Ripple  | e                |           | PR |     |       | ±0.005 | dB    |

| Stopband Atten   | uation           |           | SA | 75  |       |        | dB    |

| Group Delay      |                  | (Note 14) | GD | -   | 28    | -      | 1/fs  |

| Digital Filter + | ·SCF             |           |    |     |       |        |       |

| Frequency Resp   | onse: 0 ~ 80.0kH | Iz        |    | -   | +0/-1 | -      | dB    |

Note 13.通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、 $PB = 0.4535 \times fs(@\pm 0.01dB)$ 、 $SB = 0.546 \times fs$ です。

Note 14. ディジタルフィルタによる演算遅延で、16/20/24ビットデータが入力レジスタにセットされてからアナログ信号が出力されるまでの時間です。

# スローロールオフ・フィルタ特性(fs = 44.1kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; Normal Speed Mode; DEM=OFF; SLOW bit="1")

| Parameter           |                             |           | Symbol | min  | typ   | max    | Units |

|---------------------|-----------------------------|-----------|--------|------|-------|--------|-------|

| Digital Filter      |                             |           |        |      |       |        |       |

| Passband            | (Note 15)                   | ±0.04dB   | PB     | 0    |       | 8.1    | kHz   |

|                     |                             | -3.0dB    |        | =    | 18.2  | -      | kHz   |

| Stopband            |                             | (Note 15) | SB     | 39.2 |       |        | kHz   |

| Passband Ripple     |                             |           | PR     |      |       | ±0.005 | dB    |

| Stopband Attenuat   | ion                         |           | SA     | 72   |       |        | dB    |

| Group Delay         |                             | (Note 14) | GD     | -    | 28    | -      | 1/fs  |

| Digital Filter + SO | CF                          |           |        |      |       |        |       |

| Frequency Respon    | se: $0 \sim 20.0 \text{kH}$ | [z        |        | -    | +0/-5 | -      | dB    |

# スローロールオフ・フィルタ特性(fs = 96kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; DEM=OFF; SLOW bit="1")

| Parameter          | Parameter              |           |    | min  | typ   | max    | Units |

|--------------------|------------------------|-----------|----|------|-------|--------|-------|

| Digital Filter     |                        |           |    |      |       |        |       |

| Passband           | (Note 15)              | ±0.04dB   | PB | 0    |       | 17.7   | kHz   |

|                    |                        | -3.0dB    |    | -    | 39.6  | -      | kHz   |

| Stopband           |                        | (Note 15) | SB | 85.3 |       |        | kHz   |

| Passband Ripple    |                        |           | PR |      |       | ±0.005 | dB    |

| Stopband Attenu    | ation                  |           | SA | 72   |       |        | dB    |

| Group Delay        |                        | (Note 14) | GD | -    | 28    | -      | 1/fs  |

| Digital Filter + S | SCF                    |           |    |      |       |        |       |

| Frequency Respo    | onse: $0 \sim 40.0$ kH | [z        |    | -    | +0/-4 | -      | dB    |

### スローロールオフ・フィルタ特性(fs = 192kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V; Quad Speed Mode; DEM=QFF; SLOW bit="1")

| Parameter        |                  |           | Symbol | min | typ   | max    | Units |

|------------------|------------------|-----------|--------|-----|-------|--------|-------|

| Digital Filter   |                  |           |        |     |       |        |       |

| Passband         | (Note 15)        | ±0.04dB   | PB     | 0   |       | 35.5   | kHz   |

|                  |                  | -3.0dB    |        | -   | 79.1  | -      | kHz   |

| Stopband         |                  | (Note 15) | SB     | 171 |       |        | kHz   |

| Passband Rippl   | e                |           | PR     |     |       | ±0.005 | dB    |

| Stopband Atten   | uation           |           | SA     | 72  |       |        | dB    |

| Group Delay      |                  | (Note 14) | GD     | _   | 28    | -      | 1/fs  |

| Digital Filter + | - SCF            |           | •      | •   |       |        |       |

| Frequency Resp   | onse: 0 ~ 80.0kH | [z        |        | -   | +0/-5 | _      | dB    |

Note 15.通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、 $PB = 0.185 \times fs$ (@±0.04dB)、 $SB = 0.888 \times fs$ です。

# DC特性

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V)

| Parameter                 |               | Symbol | min      | typ | max | Units |

|---------------------------|---------------|--------|----------|-----|-----|-------|

| High-Level Input Voltage  |               | VIH    | 2.4      | -   | -   | V     |

| Low-Level Input Voltage   |               | VIL    | -        | -   | 0.8 | V     |

| High-Level Output Voltage | (Iout=-100μA) | VOH    | DVDD-0.5 | -   | -   | V     |

| Low-Level Output Voltage  | (Iout=100µA)  | VOL    | -        | -   | 0.5 | V     |

| Input Leakage Current     | (Note 16)     | Iin    | -        | -   | ±10 | μA    |

Note 16. DFS0 pinは内部でプルダウン,またP/S pinは内部でプルアップされています。(typ. 100kΩ)このため、DFS0 pin, P/S pinは除きます。

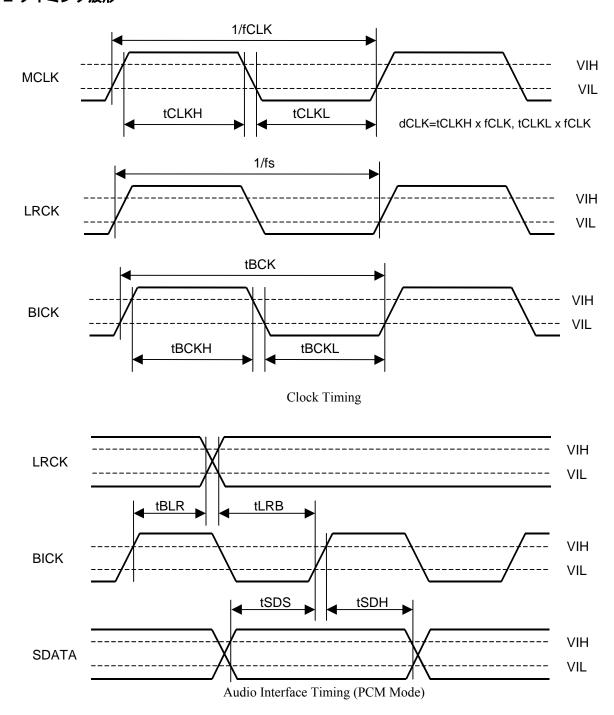

# スイッチング特性

(Ta=25°C; AVDD=VDDL/R=4.75 ~ 5.25V, DVDD=4.75 ~ 5.25V)

| Parameter                  |           | Symbol | min      | typ | max    | Units |

|----------------------------|-----------|--------|----------|-----|--------|-------|

| Master Clock Timing        |           |        |          |     |        |       |

| Frequency                  |           | fCLK   | 7.7      |     | 41.472 | MHz   |

| Duty Cycle                 |           | dCLK   | 40       |     | 60     | %     |

| LRCK Frequency             | (Note 17) |        |          |     |        |       |

| Normal Speed Mode          |           | fsn    | 30       |     | 54     | kHz   |

| Double Speed Mode          |           | fsd    | 54       |     | 108    | kHz   |

| Quad Speed Mode            |           | fsq    | 108      |     | 216    | kHz   |

| Duty Cycle                 |           | Duty   | 45       |     | 55     | %     |

| PCM Audio Interface Timing |           |        |          |     |        |       |

| BICK Period                |           |        |          |     |        |       |

| Normal Speed Mode          |           | tBCK   | 1/128fsn |     |        | ns    |

| Double Speed Mode          |           | tBCK   | 1/64fsd  |     |        | ns    |

| Quad Speed Mode            |           | tBCK   | 1/64fsq  |     |        | ns    |

| BICK Pulse Width Low       |           | tBCKL  | 30       |     |        | ns    |

| BICK Pulse Width High      |           | tBCKH  | 30       |     |        | ns    |

| BICK "↑" to LRCK Edge      | (Note 18) | tBLR   | 20       |     |        | ns    |

| LRCK Edge to BICK "↑"      | (Note 18) | tLRB   | 20       |     |        | ns    |

| SDATA Hold Time            |           | tSDH   | 20       |     |        | ns    |

| SDATA Setup Time           |           | tSDS   | 20       |     |        | ns    |

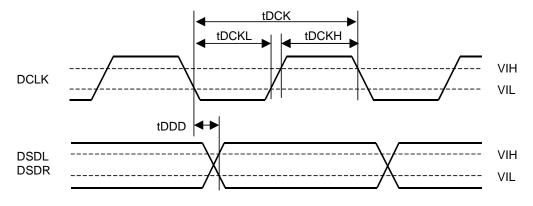

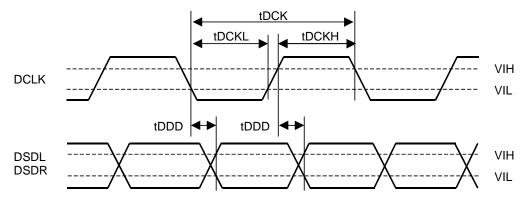

| DSD Audio Interface Timing |           |        |          |     |        |       |

| DCLK Period                |           | tDCK   | 1/64fs   |     |        | ns    |

| DCLK Pulse Width Low       |           | tDCKL  | 160      |     |        | ns    |

| DCLK Pulse Width High      |           | tDCKH  | 160      |     |        | ns    |

| DCLK Edge to DSDL/R        | (Note 19) | tDDD   | -20      |     | 20     | ns    |

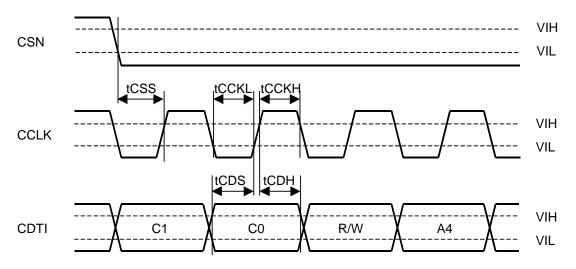

| Control Interface Timing   |           |        |          |     |        |       |

| CCLK Period                |           | tCCK   | 200      |     |        | ns    |

| CCLK Pulse Width Low       |           | tCCKL  | 80       |     |        | ns    |

| Pulse Width High           |           | tCCKH  | 80       |     |        | ns    |

| CDTI Setup Time            |           | tCDS   | 50       |     |        | ns    |

| CDTI Hold Time             |           | tCDH   | 50       |     |        | ns    |

| CSN High Time              |           | tCSW   | 150      |     |        | ns    |

| CSN "↓" to CCLK "↑"        |           | tCSS   | 50       |     |        | ns    |

| CCLK "↑" to CSN "↑"        |           | tCSH   | 50       |     |        | ns    |

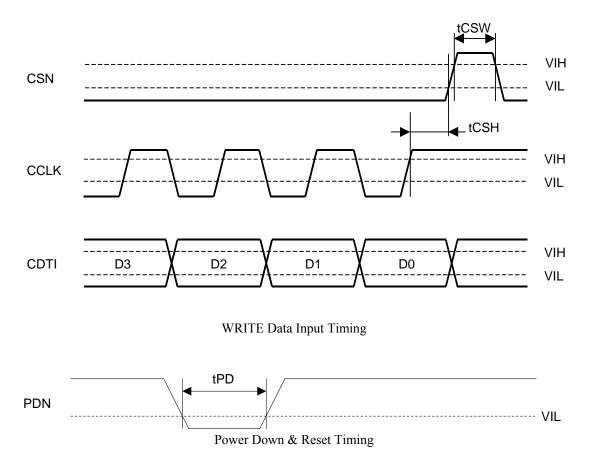

| Reset Timing               |           |        |          |     |        |       |

| PDN Pulse Width            | (Note 20) | tPD    | 150      |     |        | ns    |

- Note 17. 通常速モード、2倍速モード、4倍速モードを切り替えた場合はPDN pinまたはRSTN bitでリセットして下さい。

- Note 18. この規格値はLRCKのエッジとBICKの"↑"が重ならないように規定しています。

- Note 19. データ送信側に要求される値です。

- Note 20. 電源投入時はPDN pinを"L"から"H"にすることでリセットがかかります。DFS1-0 bitを切り替えた場合はRSTN bitでリセットして下さい。

# ■ タイミング波形

Audio Serial Interface Timing (DSD Normal Mode, DCKB bit = "0")

Audio Serial Interface Timing (DSD Phase Modulation Mode, DCKB bit = "0")

WRITE Command Input Timing

#### 動作説明

#### ■ D/A変換モード

AK4397はPCMデータとDSDデータの両方をD/A変換することが可能です。DSDモード時は、DCLK, DSDL, DSDRの各ピンからDSDデータを入力できます。PCMモードではBICK, LRCK, SDATAの各ピンからPCMデータを入力します。モード切り替えはD/P bitで行います。D/P bitでPCM/DSDモードを切り替えた場合はRSTN bit でリセットして下さい。切り替えには $2\sim3/\mathrm{fs}$ 程度かかります。パラレルモード時はPCMデータのみに対応します。

| D/P bit | Interface |

|---------|-----------|

| 0       | PCM       |

| 1       | DSD       |

Table 1. PCM/DSD Mode Control

#### ■ システムクロック

#### [1] PCMモード

AK4397に必要なクロックは、MCLK、BICK、LRCKです。MCLKとLRCKは同期する必要はありますが位相を合わせる必要はありません。MCLKはインターポレーションフィルタと $\Delta\Sigma$ 変調器に使用されます。クロックを切り替えた場合には、PDN pinでリセットするか、RSTN bitでリセットして下さい。

動作時(PDN pin = "H")は、外部クロック(MCLK, BICK, LRCK)を止めてはいけません。これらのクロックが供給されない場合、内部にダイナミックなロジックを使用しているため、過電流が流れ、動作が異常になる可能性があります。クロックを止める場合はパワーダウン状態(PDN pin = "L")またはリセット状態(RSTN bit = "0")にして下さい。電源ON等のリセット解除時(PDN pin = "L"  $\rightarrow$  "H")は、MCLKが入力されるまでパワーダウン状態です。

#### (1) パラレルモード (P/S pin = "H")

#### 1. Manual Setting Mode (ACKS pin = "L")

MCLK周波数は自動設定されますが、DFS0 pinでサンプリングスピードを設定します(Table 2)。各スピードでのMCLK周波数はTable 3で示される周波数を外部から供給して下さい。DFS1 bitは"0"に固定されます。DFS0 pinを切り替えた場合はPDN pinでリセットして下さい。このモードは、4倍速には対応していません。

| DFS0 pin | Sampling Rate (fs)              |                |  |  |  |  |

|----------|---------------------------------|----------------|--|--|--|--|

| L        | Normal Speed Mode 30kHz ~ 54kHz |                |  |  |  |  |

| Н        | Double Speed Mode               | 54kHz ~ 108kHz |  |  |  |  |

Table 2. Sampling Speed (Manual Setting Mode @Parallel Mode)

| LRCK    |         | MCLK (MHz) |         |         |         |         |         |           |  |

|---------|---------|------------|---------|---------|---------|---------|---------|-----------|--|

| fs      | 128fs   | 192fs      | 256fs   | 384fs   | 512fs   | 768fs   | 1152fs  | 64fs      |  |

| 32.0kHz | N/A     | N/A        | 8.1920  | 12.2880 | 16.3840 | 24.5760 | 36.8640 | 2.0480MHz |  |

| 44.1kHz | N/A     | N/A        | 11.2896 | 16.9344 | 22.5792 | 33.8688 | N/A     | 2.8224MHz |  |

| 48.0kHz | N/A     | N/A        | 12.2880 | 18.4320 | 24.5760 | 36.8640 | N/A     | 3.0720MHz |  |

| 88.2kHz | 11.2896 | 16.9344    | 22.5792 | 33.8688 | N/A     | N/A     | N/A     | 5.6448MHz |  |

| 96.0kHz | 12.2880 | 18.4320    | 24.5760 | 36.8640 | N/A     | N/A     | N/A     | 6.1440MHz |  |

Table 3. System Clock Example (Manual Setting Mode @Parallel Mode)

#### 2. Auto Setting Mode (ACKS pin = "H")

MCLK周波数とサンプリングスピードは自動検出(Table 4)されるため、DFS0 pinの設定は不要です。各スピードでのMCLK周波数はTable 5で示される周波数を外部から供給して下さい。DFS0 pinはVSS4またはDVDDに固定して下さい。

| MC    | CLK   | Sampling Speed    |  |  |

|-------|-------|-------------------|--|--|

| 115   | 52fs  | Normal (fs≤32kHz) |  |  |

| 512fs | 768fs | Normal            |  |  |

| 256fs | 384fs | Double            |  |  |

| 128fs | 192fs | Quad              |  |  |

Table 4. Sampling Speed (Auto Setting Mode @Parallel Mode)

| LRCK     |         | MCLK (MHz) |         |         |         |         |         |        |  |

|----------|---------|------------|---------|---------|---------|---------|---------|--------|--|

| fs       | 128fs   | 192fs      | 256fs   | 384fs   | 512fs   | 768fs   | 1152fs  | Speed  |  |

| 32.0kHz  | N/A     | N/A        | N/A     | N/A     | 16.3840 | 24.5760 | 36.8640 |        |  |

| 44.1kHz  | N/A     | N/A        | N/A     | N/A     | 22.5792 | 33.8688 | N/A     | Normal |  |

| 48.0kHz  | N/A     | N/A        | N/A     | N/A     | 24.5760 | 36.8640 | N/A     |        |  |

| 88.2kHz  | N/A     | N/A        | 22.5792 | 33.8688 | N/A     | N/A     | N/A     | Double |  |

| 96.0kHz  | N/A     | N/A        | 24.5760 | 36.8640 | N/A     | N/A     | N/A     | Double |  |

| 176.4kHz | 22.5792 | 33.8688    | N/A     | N/A     | N/A     | N/A     | N/A     | Ouad   |  |

| 192.0kHz | 24.5760 | 36.8640    | N/A     | N/A     | N/A     | N/A     | N/A     | Quad   |  |

Table 5. System Clock Example (Auto Setting Mode @Parallel Mode)

#### (2) シリアルモード (P/S pin = "L")

#### 1. Manual Setting Mode (ACKS bit = "0")

MCLK周波数は自動設定されますが、DFS1-0 bitでサンプリングスピードを設定します(Table 6)。各スピードでのMCLK周波数はTable 7で示される周波数を外部から供給して下さい。パワーダウン解除時(PDN pin = "L"  $\rightarrow$  "H")はManual Setting Modeに設定されます。DFS1-0 bitを切り替えた場合はRSTN bitでリセットして下さい。

| DFS1 bit | DFS0 bit | Sampling I        |                 |  |

|----------|----------|-------------------|-----------------|--|

| 0        | 0        | Normal Speed Mode | (default)       |  |

| 0        | 1        | Double Speed Mode |                 |  |

| 1        | 0        | Quad Speed Mode   | 120kHz ~ 216kHz |  |

Table 6. Sampling Speed (Manual Setting Mode @Serial Mode)

| LRCK     |         | MCLK (MHz) |         |         |         |         |         |            |  |  |

|----------|---------|------------|---------|---------|---------|---------|---------|------------|--|--|

| fs       | 128fs   | 192fs      | 256fs   | 384fs   | 512fs   | 768fs   | 1152fs  | 64fs       |  |  |

| 32.0kHz  | N/A     | N/A        | 8.1920  | 12.2880 | 16.3840 | 24.5760 | 36.8640 | 2.0480MHz  |  |  |

| 44.1kHz  | N/A     | N/A        | 11.2896 | 16.9344 | 22.5792 | 33.8688 | N/A     | 2.8224MHz  |  |  |

| 48.0kHz  | N/A     | N/A        | 12.2880 | 18.4320 | 24.5760 | 36.8640 | N/A     | 3.0720MHz  |  |  |

| 88.2kHz  | 11.2896 | 16.9344    | 22.5792 | 33.8688 | N/A     | N/A     | N/A     | 5.6448MHz  |  |  |

| 96.0kHz  | 12.2880 | 18.4320    | 24.5760 | 36.8640 | N/A     | N/A     | N/A     | 6.1440MHz  |  |  |

| 176.4kHz | 22.5792 | 33.8688    | N/A     | N/A     | N/A     | N/A     | N/A     | 11.2896MHz |  |  |

| 192.0kHz | 24.5760 | 36.8640    | N/A     | N/A     | N/A     | N/A     | N/A     | 12.2880MHz |  |  |

Table 7. System Clock Example (Manual Setting Mode @Serial Mode)

2. Auto Setting Mode (ACKS bit = "1")

MCLK周波数とサンプリングスピードは自動検出(Table 8)されるため、DFS1-0 bitの設定は不要です。各スピードでのMCLK周波数はTable 9で示される周波数を外部から供給して下さい。

| MC    | CLK   | Sampling Speed    |  |  |

|-------|-------|-------------------|--|--|

| 11:   | 52fs  | Normal (fs≤32kHz) |  |  |

| 512fs | 768fs | Normal            |  |  |

| 256fs | 384fs | Double            |  |  |

| 128fs | 192fs | Quad              |  |  |

Table 8. Sampling Speed (Auto Setting Mode @Serial Mode)

| LRCK     |         | MCLK (MHz) |         |         |         |         |         |        |  |

|----------|---------|------------|---------|---------|---------|---------|---------|--------|--|

| fs       | 128fs   | 192fs      | 256fs   | 384fs   | 512fs   | 768fs   | 1152fs  | Speed  |  |

| 32.0kHz  | N/A     | N/A        | N/A     | N/A     | 16.3840 | 24.5760 | 36.8640 |        |  |

| 44.1kHz  | N/A     | N/A        | N/A     | N/A     | 22.5792 | 33.8688 | N/A     | Normal |  |

| 48.0kHz  | N/A     | N/A        | N/A     | N/A     | 24.5760 | 36.8640 | N/A     |        |  |

| 88.2kHz  | N/A     | N/A        | 22.5792 | 33.8688 | N/A     | N/A     | N/A     | Double |  |

| 96.0kHz  | N/A     | N/A        | 24.5760 | 36.8640 | N/A     | N/A     | N/A     | Double |  |

| 176.4kHz | 22.5792 | 33.8688    | N/A     | N/A     | N/A     | N/A     | N/A     | Quad   |  |

| 192.0kHz | 24.5760 | 36.8640    | N/A     | N/A     | N/A     | N/A     | N/A     | Quau   |  |

Table 9. System Clock Example (Auto Setting Mode @Serial Mode)

#### [2] DSDモード

必要なクロックは、MCLK, DCLKです。MCLKとDCLKは同期する必要はありますが位相を合わせる必要はありません。MCLK周波数はDCKS bitで設定します。

動作時(PDN pin = "H")は、各外部クロック(MCLK, DCLK)を止めてはいけません。これらのクロックが供給されない場合、内部にダイナミックなロジックを使用しているため、過電流が流れ、動作が異常になる可能性があります。クロックを止める場合はパワーダウン状態(PDN pin = "L")にして下さい。電源ON等のリセット解除時(PDN pin = "L"  $\rightarrow$  "H")はMCLKが入力されるまでパワーダウン状態です。

| DCKS bit | MCLK Frequency | DCLK Frequency |           |

|----------|----------------|----------------|-----------|

| 0        | 512fs          | 64fs           | (default) |

| 1        | 768fs          | 64fs           |           |

Table 10. System Clock (DSD Mode)

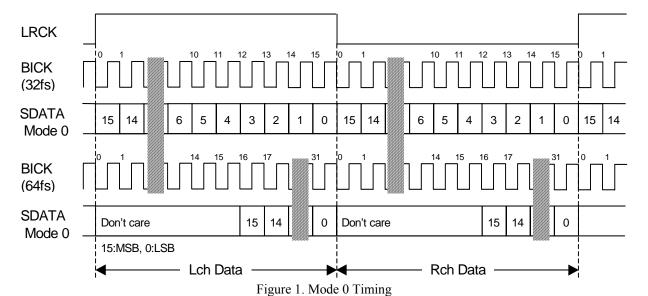

#### ■ オーディオインタフェースフォーマット

#### [1] PCMモード

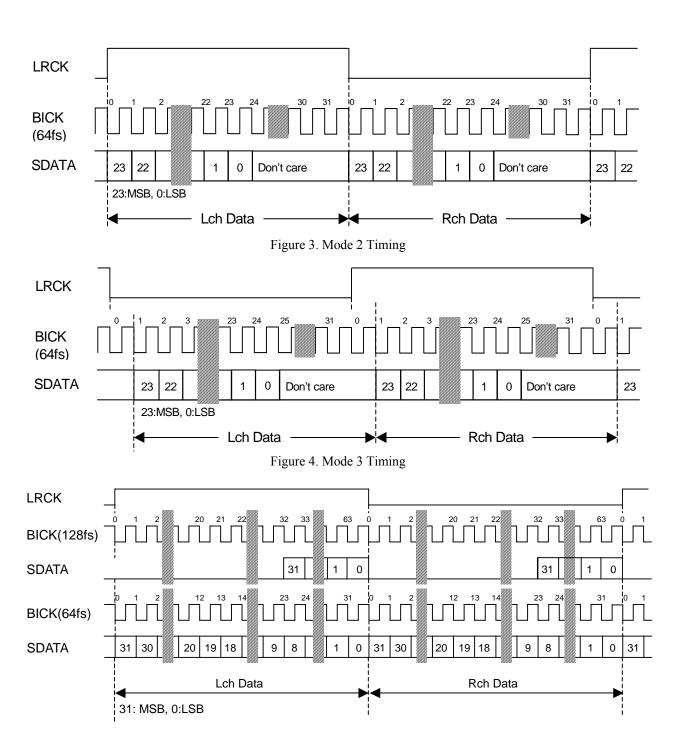

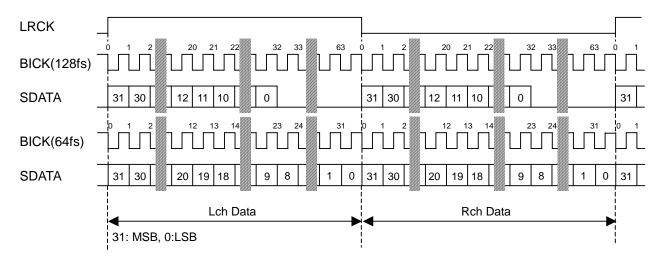

オーディオデータはBICKとLRCKを使ってSDATAから入力されます。5種類のデータフォーマット(Table 11) は、DIF2-0 pin (パラレルモード) または、DIF2-0 bit (シルアルモード) で選択できます。全モードともMSB ファースト、2'sコンプリメントのデータフォーマットでBICKの立ち上がりでラッチされます。 $Mode\ 2$ を16 ビット、20ビットで使った場合はデータのないLSBには"0"を入力して下さい。

| Mode | DIF2 | DIF1 | DIF0 | Input Format             | BICK   | Figure   | ]         |

|------|------|------|------|--------------------------|--------|----------|-----------|

| 0    | 0    | 0    | 0    | 16bit後詰め                 | ≥ 32fs | Figure 1 |           |

| 1    | 0    | 0    | 1    | 20bit後詰め                 | ≥ 48fs | Figure 2 |           |

| 2    | 0    | 1    | 0    | 24bit前詰め                 | ≥ 48fs | Figure 3 | (default) |

| 3    | 0    | 1    | 1    | 24bit I <sup>2</sup> S互換 | ≥ 48fs | Figure 4 |           |

| 4    | 1    | 0    | 0    | 24bit後詰め                 | ≥ 48fs | Figure 2 |           |

| 5    | 1    | 0    | 1    | 32bit後詰め                 | ≥ 64fs | Figure 5 |           |

| 6    | 1    | 1    | 0    | 32bit前詰め                 | ≥64fs  | Figure 6 |           |

| 7    | 1    | 1    | 1    | 32bit I <sup>2</sup> S互換 | ≥ 64fs | Figure 7 |           |

Table 11. Audio Interface Format

**LRCK** BICK (64fs) **SDATA** 19 0 0 Don't care Don't care 19 Mode 1 19:MSB, 0:LSB **SDATA** 22 21 20 0 0 Don't care 23 19 Don't care 23 22 21 20 19 Mode 4 23:MSB, 0:LSB Lch Data – Rch Data -

Figure 2. Mode 1/4 Timing

Figure 5. Mode 5 Timing

Figure 6. Mode 6 Timing

Figure 7. Mode 7 Timing

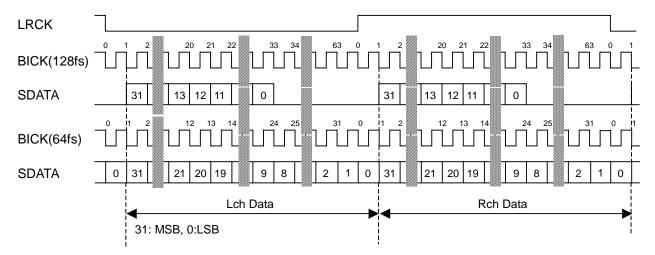

# [2] DSDモード

DSDデータ入力の場合は、DIF2-0 pin及びDIF2-0 bitは無効です。DCLK周波数は64fsに固定です。DCLKの極性はDCKB bitで反転することが可能です。

Figure 8. DSD Mode Timing

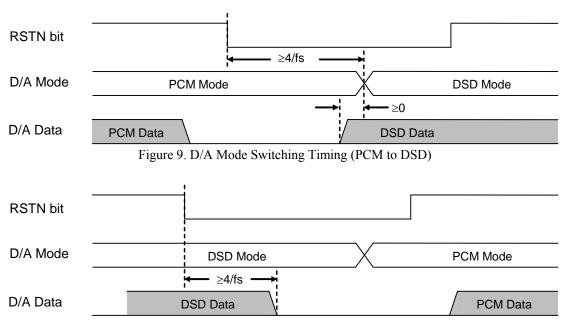

#### ■ D/A変換モード切り替えタイミング

Figure 10. D/A Mode Switching Timing (DSD to PCM)

Note. DSDモード時は25%から75%デューティを信号レンジとします。SACDフォーマットブック(Scarlet Book)では、DSD信号のピークレベルがこのデューティを越えることは推奨されていません。

# ■ ディエンファシスフィルタ

IIRフィルタによる3周波数(32kHz, 44.1kHz, 48kHz)対応のディエンファシスフィルタ( $50/15\mu s$ 特性)を内蔵しています。2倍速モード、4倍速モードの時にはディエンファシスフィルタはOFFです。DSDモード時にはDEM1-0bitは無効です。PCMモードとDSDモードを切り替えても設定値は保持されます。

| DEM1 | DEM0 | Mode    |           |

|------|------|---------|-----------|

| 0    | 0    | 44.1kHz |           |

| 0    | 1    | OFF     | (default) |

| 1    | 0    | 48kHz   |           |

| 1    | 1    | 32kHz   |           |

Table 12. De-emphasis Control (Normal Speed Mode)

#### ■ 出力ポリューム

AK4397はMUTEを含むリニアステップ、256レベルのチャネル独立ディジタル出力ボリューム(ATT)を内蔵しています。このボリュームはDACの前段にあり、入力データを0dBから-48dBまでアテネーション、またはミュートします。設定値間の遷移はソフト遷移です。従って、遷移中にスイッチングノイズは発生しません。1レベル変化した時の遷移時間と256レベル全体の遷移時間をTable 13に示します。

| Sampling Speed    | 遷移      | 時間       |

|-------------------|---------|----------|

| Sampling Speed    | 1 Level | 255 to 0 |

| Normal Speed Mode | 4LRCK   | 1020LRCK |

| Double Speed Mode | 8LRCK   | 2040LRCK |

| Quad Speed Mode   | 16LRCK  | 4080LRCK |

Table 13. ATT Transition Time

#### ■ ゼロ検出機能

AK4397はチャネル独立のゼロ検出機能を持ちます。各チャネルの入力データが8192回連続して"0"の場合、各チャネルのDZF pinが独立に"H"になります。その後、各チャネルの入力データが"0"でなくなると対応するチャネルのDZF pinが"L"になります。RSTN bitが"0"の場合、両チャネルのDZF pinが"H"になります。RSTN bitが"1"になった後、各チャネルの入力データが"0"でなくなると対応するチャネルのDZF pinが4 ~ 5LRCK後に"L"になります。また、DZFM bitを"1"にすると両チャネルの入力データが8192回連続して"0"の場合のみ、両チャネルのDZF pinが"H"になります。ゼロ検出機能はDZFE bitで無効にできます。この時、両チャネルのDZF pinは常に"L"です。DZF pinの極性はDZFB bitで反転することが可能です。

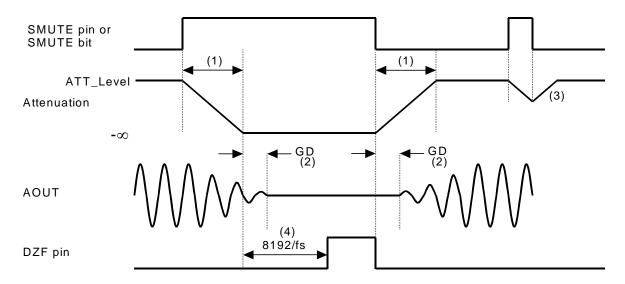

### ■ ソフトミュート機能

ソフトミュートはディジタル的に実行されます。SMUTE pinを"H"またはSMUTE bitを"1"にするとその時点の ATT設定値からATT設定値×ATT遷移時間(Table 13)で入力データが→∞ ("0")までアテネーションされます。 SMUTE pinを"L"またはSMUTE bitを"0"にすると→∞状態が解除され、→∞からATT設定値×ATT遷移時間で ATT設定値まで復帰します。ソフトミュート開始後、→∞までアテネーションされる前に解除されるとアテネーションが中断され、同じサイクルでATT設定値まで復帰します。ソフトミュート機能は信号を止めずに信号源を切り替える場合などに有効です。

#### 注:

- (1) ATT設定値 × ATT遷移時間(Table 13)。例えば、Normal Speed Mode時、ATT設定値が"255"の場合は 1020LRCKサイクルです。

- (2) ディジタル入力に対するアナログ出力は群遅延(GD)をもちます。

- (3) ソフトミュート開始後、-∞までアテネーションされる前に解除されるとアテネーションが中断され、同じサイクルでATT設定値まで復帰します。

- (4) 各チャネルの入力データが8192回連続して"0"の場合、各チャネルのDZF pinは"H"になります。その後、各チャネルの入力データが"0"でなくなると、対応するチャネルのDZF pinが"L"になります。

Figure 11. Soft Mute Function

#### ■ システムリセット

電源ON時には、PDN pinに一度"L"を入力してリセットして下さい。アナログ部はMCLK入力によりパワーダウン状態が解除され、ディジタル部は内部カウンタがMCLKを4/fsカウントした後、パワーダウン状態が解除されます。

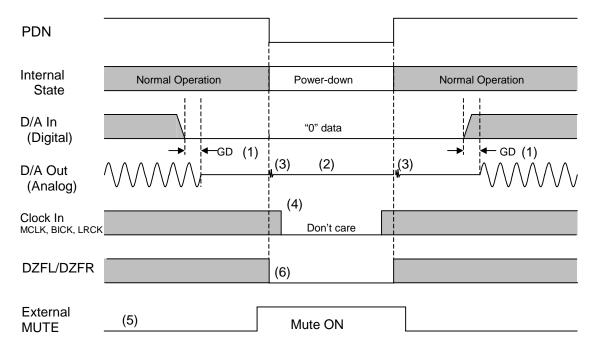

### ■ パワーダウン機能

PDN pinを"L"にするとパワーダウン状態になり、アナログ出力はフローティング状態(Hi-Z)になります。 Figure 12 にパワーダウン及びパワーアップ時のシステムタイミング例を示します。

#### 注:

- (1) ディジタル入力に対するアナログ出力は群遅延(GD)を持ちます。

- (2) パワーダウン時、アナログ出力はHi-Zです。

- (3) PDN信号のエッジ("↓↑")でクリックノイズが出力されます。このノイズはデータが"0"の場合でも出力されます。

- (4) パワーダウン状態(PDN pin = "L")では各クロック入力(MCLK, BICK, LRCK)を止めることができます。

- (5) クリックノイズ(3)が問題になる場合はアナログ出力を外部でミュートして下さい。タイミング例を示します。

- (6) パワーダウン状態(PDN pin = "L")では、DZF pinは"L"になります。

Figure 12. Power-down/up sequence example

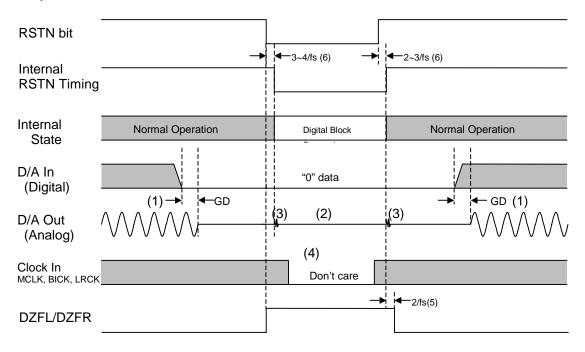

#### ■ リセット機能

RSTN bitを"0"にするとDACはリセットされますが、内部レジスタは初期化されません。この時、アナログ出力はAVDD/2電圧になり、DZFL/DZFR pinは"H"になります。Figure 13にRSTN bitによるリセットシーケンスを示します。

#### 注:

- (1) ディジタル入力に対してアナログ出力は群遅延(GD)を持ちます。

- (2) RSTN bit = "0"時、アナログ出力はAVDD/2です。

- (3) 内部RSTN信号のエッジ("↓↑")でクリックノイズが出力されます。このノイズはデータが"0"の場合でも出力されます。

- (4) リセット状態(RSTN bit = "0")では各クロック入力(MCLK, BICK, LRCK)を止めることができます。

- (5) DZF pinはRSTN bitの立ち下がりエッジで"H"になり、LSI内部のRSTN bitの立ち上がりエッジの2/fs 後、"L"になります。

- (6) RSTN bitを書き込んでからLSI内部のRSTN bitが変化するまでの立ち下がり時に3~4/fsかかります。 また、立ち上がり時に2~3/fsかります。

Figure 13. Reset sequence example

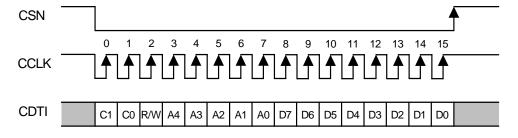

#### ■ レジスタコントロールインタフェース

AK4397のいくつかの機能はピン(パラレルモード)とレジスタ(シリアルモード)のどちらでも設定できますが、パラレルモード時にはレジスタ設定は無効、シリアルモード時にはピン設定は無効になります。P/S pin の設定を変更した場合は、PDN pinでAK4397をリセットして下さい。シリアルモードではP/S pinを"L"にすることによってイネーブルされます。このモードではP/S pinを"L"にすることによってイネーブルされます。このモードではP/S pinを"L"にすることによってイネーブルされます。このモードではP/S pinを"L"にすることによってイネーブルされます。P/S pinを"L"にすることによってイネーブルされます。P/S pinを"L"にすることによってイネーブルされます。P/S pinを"L"にすることによってイネーブルされます。P/S pin の設定を変更した場合は、PDN pinでAK4397をリセットして下さい。シリアルモードではP/S pin の設定を変更した場合は、P/S pin の設定を変更した。P/S pin の設定を変更した場合は、P/S pin の設定を変更した場合は、P/S pin の P/S pin の設定を変更した。P/S pin の P/S pin の

| Function               | Parallel Mode | Serial Mode |

|------------------------|---------------|-------------|

| Auto Setting Mode      | 0             | 0           |

| Manual Setting Mode    | 0             | O           |

| Audio Format           | 0             | O           |

| De-emphasis            | 0             | O           |

| SMUTE                  | 0             | O           |

| DSD Mode               | X             | O           |

| Slow roll-off Response | X             | O           |

| Digital Attenuator     | X             | O           |

Table 14. Function List (O: Available, X: Not available)

PDN pinを"L"にすると内部レジスタ値が初期化されます。また、シリアルモードではRSTN bitに"0"を書き込むと内部タイミング回路がリセットされます。但し、このときレジスタの内容は初期化されません。

C1-C0: Chip Address (C1=CAD1, C0=CAD0)

R/W: READ/WRITE (Fixed to "1", Write only)

A4-A0: Register Address D7-D0: Control Data

Figure 14. Control I/F Timing

<sup>\*</sup>AK4397はデータ読み出しをサポートしません。

<sup>\*</sup>PDN pin = "L"時、及びマスタクロックが供給されていない時は、コントロールレジスタへの書き込みはできません。

<sup>\*</sup>CSNが"L"期間中にCCLKの"个"が15回以下または17回以上の場合にはデータは書き込まれません。

#### ■ レジスタマップ

| Addr | Register Name | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0    |

|------|---------------|------|------|------|------|------|------|------|-------|

| 00H  | Control 1     | ACKS | 0    | 0    | 0    | DIF2 | DIF1 | DIF0 | RSTN  |

| 01H  | Control 2     | DZFE | DZFM | SLOW | DFS1 | DFS0 | DEM1 | DEM0 | SMUTE |

| 02H  | Control 3     | D/P  | DSDM | DCKS | DCKB | 0    | DZFB | 0    | 0     |

| 03H  | Lch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

| 04H  | Rch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

Note:

アドレス05H~1FHへの書き込みは禁止です。

PDN pinを"L"にするとレジスタの内容が初期化されます。

RSTN bitに"0"を書き込むと内部タイミング回路がリセットされますが、レジスタの内容は初期化されません。

P/S pinの設定を変更した場合は、PDN pinでAK4397をリセットして下さい。

### ■ 詳細説明

| Addr | Register Name | D7   | D6 | D5 | D4 | D3   | D2   | D1   | D0   |

|------|---------------|------|----|----|----|------|------|------|------|

| 00H  | Control 1     | ACKS | 0  | 0  | 0  | DIF2 | DIF1 | DIF0 | RSTN |

|      | Default       | 0    | 0  | 0  | 0  | 0    | 1    | 0    | 1    |

RSTN: Internal Timing Reset

0: Reset. All registers are not initialized.

1: Normal Operation (default)

"0"で内部タイミング回路がリセットされますが、レジスタの内容は初期化されません。

DIF2-0: Audio Data Interface Modes (Table 11)

初期値は"010" (Mode2: 24bit前詰め)です。

ACKS: Master Clock Frequency Auto Setting Mode Enable (PCM only)

0: Disable : Manual Setting Mode (default)

1: Enable : Auto Setting Mode

ACKS bitが"1"の時、サンプリング周波数とMCLK周波数は自動検出されます。

| Addr Register Name | D7   | D6   | i | D5   | D4   | D3   | D2   | D1   | D0    |

|--------------------|------|------|---|------|------|------|------|------|-------|

| 01H Control 2      | DZFE | DZFM | i | SLOW | DFS1 | DFS0 | DEM1 | DEM0 | SMUTE |

| Default            | 0    | 0    |   | 0    | 0    | 0    | 0    | 1    | 0     |

SMUTE: Soft Mute Enable

0: Normal Operation (default)1: DAC outputs soft-muted.

DEM1-0: De-emphasis Response (Table 12) 初期値は"01" (OFF)です。

DFS1-0: Sampling Speed Control (Table 6)

初期値は"00" (Normal Speed)です。DFS1-0 bitを切り替えた場合、クリックノイズが発生します。

SLOW: Slow Roll-off Filter Enable

0: Sharp roll-off filter (default)

1: Slow roll-off filter

DZFM: Data Zero Detect Mode

0: Channel Separated Mode (default)

1: Channel ANDed Mode

If the DZFM bit is set to "1", the DZF pins of both channels go to "H" only when the input data at both channels are continuously zeros for 8192 LRCK cycles.

DZFE: Data Zero Detect Enable

0: Disable (default)

1: Enable

Zero detect function can be disabled by DZFE bit "0". In this case, the DZF pins of both channels are always "L".

[AK4397]

| Addr Register Name | D7  | D6   | - | D5   | D4   | D3 | D2   | D1 | D0 |

|--------------------|-----|------|---|------|------|----|------|----|----|

| 02H Control 3      | D/P | DSDM | I | OCKS | DCKB | 0  | DZFB | 0  | 0  |

| Default            | 0   | 0    | ; | 0    | 0    | 0  | 0    | 0  | 0  |

DZFB: Inverting Enable of DZF

0: DZF pin goes "H" at Zero Detection (default)

1: DZF pin goes "L" at Zero Detection

DCKB: Polarity of DCLK (DSD Only)

0: DSD data is output from DCLK falling edge. (default)

1: DSD data is output from DCLK rising edge.

DCKS: Master Clock Frequency Select at DSD mode (DSD only)

0: 512fs (default)

1: 768fs

DSDM: DSD Input Select

0: Input pin: #5, 6, 7 (default)

1: Input pin: #12, 13, 14

DSDM bitの設定を変更した場合は、RSTN bitでAK4397をリセットして下さい。

D/P: DSD/PCM Mode Select

0: PCM Mode (default)

1: DSD Mode

D/P bitの設定を変更した場合は、RSTN bitでAK4397をリセットして下さい。

| Addr | Register Name | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|---------------|------|------|------|------|------|------|------|------|

| 03H  | Lch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0 |

| 04H  | Rch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0 |

|      | Default       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

ATT7-0: Attenuation Level

$ATT = 20 \log_{10}(ATT_DATA / 255) [dB]$

FFH: 0dB (default)

00H: Mute

[AK4397]

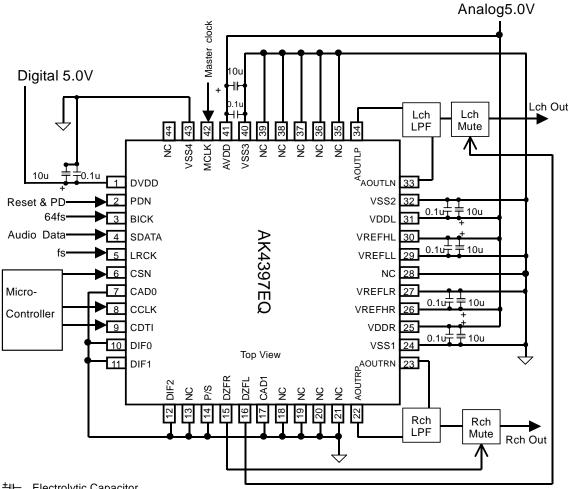

## システム設計

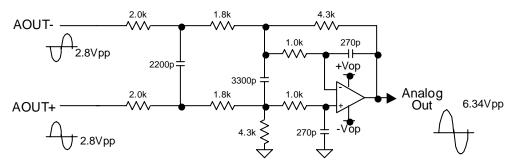

システム接続例をFigure 15、アナログ出力回路例をFigure 17, Figure 18とFigure 19に示します。具体的な回路と 測定例については評価ボード(AKD4397)を参照して下さい。

- **Electrolytic Capacitor**

- Ceramic Capacitor

#### 注:

- Chip Address = "00". BICK = 64fs, LRCK = fs

- AVDDとDVDDの配線はレギュレータ等からの低インピーダンス状態のまま分けて配線して下さい。

- VSS1-4 は同じアナロググランドに接続して下さい。

- AOUTが負荷容量を駆動する場合は直列に抵抗を入れて下さい。

- プルダウン/プルアップピン以外のディジタル入力ピンはオープンにしないで下さい。

Figure 15. Typical Connection Diagram (AVDD=VDDL/R=5V, DVDD=5V, Serial mode)

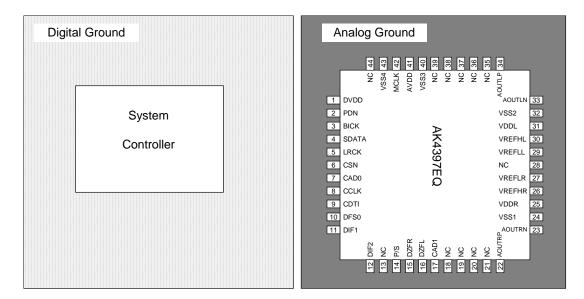

Figure 16. Ground Layout

#### 1. グランドと電源のデカップリング

AK4397ではディジタルノイズのカップリングを最小限に抑えるため、AVDD, VDDL/R とDVDDをデカップリングします。AVDD, VDDL/R にはシステムのアナログ電源を供給し、DVDDにはシステムのディジタル電源を供給して下さい。AVDD, VDDL/R とDVDDの配線はレギュレータ等からの低インピーダンス状態のまま分けて配線して下さい。その際、AVDD, VDDL/R とDVDDの立ち上げシーケンスを考慮する必要はありません。

VSS1-4 は同じアナロググランドに接続して下さい。デカップリングコンデンサ、特に小容量のセラミックコンデンサはAK4397にできるだけ近づけて接続します。

#### 2. 基準電圧

VREFHL/R pinとVREFLL/R pinに入力される電圧の差がアナログ出力のフルスケールを決定します。通常は VREFHL/R pinをAVDDに接続し、VREFLL/R pinをVSS に接続します。VREFHL/R pinとVREFLL/R pinとの間 に $0.1\mu$ Fのセラミックコンデンサを接続します。VREFHL/R pinには高周波ノイズを除去するために、 $10\mu$ F程度 の電解コンデンサと並列に $0.1\mu$ FのセラミックコンデンサをVSS との間に接続して下さい。特に、セラミックコンデンサはピンにできるだけ近づけて接続して下さい。ディジタル信号、特にクロックはAK4397へのカップリングを避けるためVREFHL/R, VREFLL/R pinからできるだけ離して下さい。

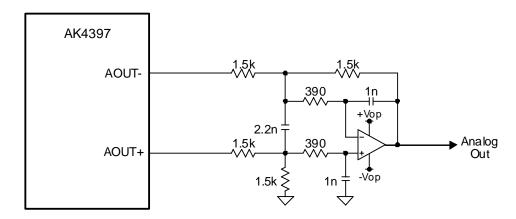

#### 3. アナログ出力

アナログ出力は完全差動出力になっており、出力レンジはAVDD/2を中心に2.8Vpp (typ, VREFHL/R – VREFLL/R = 5V)です。差動出力は外部で加算されます。AOUTL/R +, AOUTL/R –の加算電圧は $V_{AOUT}$  = (AOUT+)–(AOUT–)です。加算ゲインが 1 の場合、出力レンジは5.6Vpp (typ, VREFHL/R – VREFLL/R = 5V)です。外部加算回路のバイアス電圧は外部で供給します。入力コードのフォーマットは2's compliment (2の補数)で7FFFFFH(@24bit)に対しては正のフルスケール、800000H(@24bit)に対しては負のフルスケール、000000H(@24bit)での $V_{AOUT}$ の理想値はV電圧が出力されます。

内蔵の $\Delta\Sigma$ 変調器の帯域外ノイズ(シェーピングノイズ)は内蔵のスイッチトキャパシタフィルタ(SCF)で減衰されます。

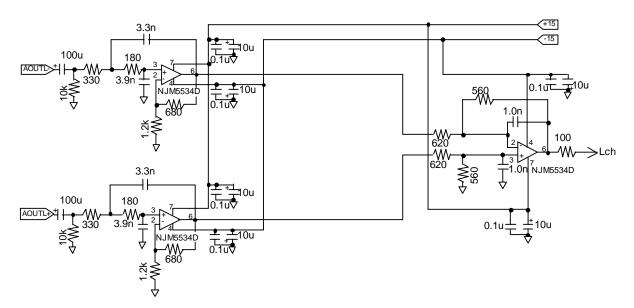

Figure 17は差動出力を1個のオペアンプで加算する外部LPF回路例です。Figure 18は差動出力の回路例及び3個のオペアンプを使った外部LPF回路例です。

Figure 17. External LPF Circuit Example 1 for PCM (fc = 99.2kHz, Q=0.704)

| Frequency Response | Gain     |

|--------------------|----------|

| 20kHz              | -0.011dB |

| 40kHz              | -0.127dB |

| 80kHz              | -1.571dB |

Table 15. Frequency Response of External LPF Circuit Example 1 for PCM

Figure 18. External LPF Circuit Example 2 for PCM

|                       |       |        | 2 <sup>nd</sup> Stage | Total    |  |

|-----------------------|-------|--------|-----------------------|----------|--|

| Cut-off Frequency     |       | 182kHz | 284kHz                | -        |  |

| Q                     |       | 0.637  | -                     | -        |  |

| Gain                  |       | +3.9dB | -0.88dB               | +3.02dB  |  |

| Fraguency             | 20kHz | -0.025 | -0.021                | -0.046dB |  |

| Frequency<br>Response | 40kHz | -0.106 | -0.085                | -0.191dB |  |

| Response              | 80kHz | -0.517 | -0.331                | -0.848dB |  |

Table 16. Frequency Response of External LPF Circuit Example 2 for PCM

SACDフォーマットブック(Scarlet Book)では、SACDの再生時のフィルタ特性として、カットオフ50kHz以下のスロープ-30dB/oct以上のフィルタが推奨されています。AK4397では内部フィルタ(Table 17)と外部アナログフィルタ(Figure 19)により、このフィルタ特性を実現可能です。

| Frequency | Gain    |

|-----------|---------|

| 20kHz     | -0.4dB  |

| 50kHz     | -2.8dB  |

| 100kHz    | -15.5dB |

Table 17. Internal Filter Response at DSD Mode

Figure 19. External 3rd Order LPF Circuit Example for DSD

| Frequency | Gain    |

|-----------|---------|

| 20kHz     | -0.05dB |

| 50kHz     | -0.51dB |

| 100kHz    | -16.8dB |

DC gain = 1.07dB

Table 18. 3rd Order LPF (Figure 19) Response

[AK4397]

# パッケージ

# 44pin LQFP (Unit: mm)

# ■ 材質・メッキ仕様

Package molding compound: **Epoxy** Lead frame material: Ĉu

Lead frame surface treatment: Solder (Pb free) plate

# マーキング

- 1) Pin #1 indication

- 2) AKM Logo

- 3) Date Code: XXXXXXX(7 digits)

- 4) Marking Code: AK4397

- 5) Audio 4 pro Logo

# 改訂履歴

| Date (YY/MM/DD) | Revision | Reason | Page | Contents                  |

|-----------------|----------|--------|------|---------------------------|

| 07/05/11        | 00       | 初版     |      |                           |

| 08/02/12        | 01       | 誤記訂正   | 25   | VCOM pin に関する記述の削除        |

|                 |          |        | 26   | $VCOM \rightarrow AVDD/2$ |

|                 |          |        | 32   | 2. 基準電圧                   |

|                 |          |        |      | VCOM pin に関する記述の削除        |

|                 |          |        |      | 3. アナログ出力                 |

|                 |          |        |      | $VCOM \rightarrow AVDD/2$ |

| 09/02/25        | 02       | 誤記訂正   | 33   | Figure 17 を変更             |

|                 |          |        |      | Table 15 を変更              |

#### 重要な注意事項 ―

- 本書に記載された製品、及び、製品の仕様につきましては、製品改善のために予告なく変更することがあります。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社特約店営業担当にご確認下さい。

- 本書に掲載された情報・図面の使用に起因した第三者の所有する特許権、工業所有権、その他の 権利に対する侵害につきましては、当社はその責任を負うものではありませんので、ご了承下さい。

- 本書記載製品が、外国為替及び、外国貿易管理法に定める戦略物資(役務を含む)に該当する場合、 輸出する際に同法に基づく輸出許可が必要です。

- 医療機器、安全装置、航空宇宙用機器、原子力制御用機器など、その装置・機器の故障や動作不良が、直接または間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を要求される用途に弊社製品を使用される場合は、必ず事前に弊社代表取締役の書面による同意をお取り下さい。

- この同意書を得ずにこうした用途に弊社製品を使用された場合、弊社は、その使用から生ずる損害 等の責任を一切負うものではありませんのでご了承下さい。

- お客様の転売等によりこの注意事項の存在を知らずに上記用途に弊社製品が使用され、その使用から損害等が生じた場合は全てお客様にてご負担または補償して頂きますのでご了承下さい。