**TDA1547**

#### **FEATURES**

- · Top-grade audio performance

- very low harmonic distortion

- high signal-to-noise ratio

- wide dynamic range of approximately 108 dB (not A-weighted)

- · High crosstalk immunity

- · Bitstream concept

- high over-sampling rate up to 192 f.

- pulse-density modulation

- inherently monotonic

- no zero-crossing distortion

#### GENERAL DESCRIPTION

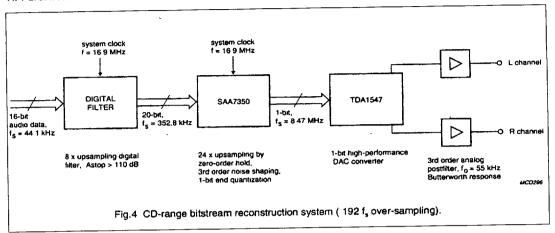

The TDA1547 is a dedicated one-bit digital-to-analog converter to facilitate a high fidelity sound reproduction of digital audio. The TDA1547 is extremely suitable for use in high quality audio systems such as Compact Disc and DAT players, or in digital amplifiers and digital signal processing systems. The TDA1547 is used in combination with the SAA7350 bitstream circuit, which includes the third-order noise shaper. The excellent performance of the SAA7350 and TDA1547 bitstream conversion system is obtained by separating the noise shaping circuit and the one-bit conversion circuit over two IC's, thereby reducing the crosstalk between the digital and analog parts. The TDA1547 one-bit converter is processed in BIMOS. In the digital logic and drivers bipolar transistors are used to optimize speed and to reduce digital noise generation. In the analog part the bipolar transistors are used to obtain high performance of the operational amplifiers. Special layout precautions have been taken to achieve a high crosstalk immunity. The layout of the TDA1547 has fully separated left and right channels

### ORDERING INFORMATION

| EXTENDED<br>TYPE NUMBER | PACKAGE |              |          |         |  |  |

|-------------------------|---------|--------------|----------|---------|--|--|

|                         | PINS    | PIN POSITION | MATERIAL | CODE    |  |  |

| TDA1547                 | 32      | SDIL         | plastic  | SOT232A |  |  |

and supply voltage lines between the digital and analog sections.

September 1991

825

7110826 0079158 03T ■

## TDA1547

### PINNING

| SYMBOL             | PIN | DESCRIPTION                                                                                                             |  |  |  |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DGND               | 1   | 0 V digital supply                                                                                                      |  |  |  |

| V <sub>DDD</sub>   | 2   | 5 V digital supply for both channels                                                                                    |  |  |  |

| N R                | 3   | serial one-bit data input for the right channel                                                                         |  |  |  |

| n.c.               | 4   | pin not connected; should preferably be connected to digital ground                                                     |  |  |  |

| CLK B              | 5   | clock input for the right channel                                                                                       |  |  |  |

| V <sub>000 R</sub> | 6   | 5 V digital supply for the right channel; this voltage determines the internal logic HIGH level in the right channel    |  |  |  |

| V <sub>SSO R</sub> | 7   | -3.5 V digital supply for the right channel; this voltage determines the internal logic LOW level in the right channel  |  |  |  |

| V <sub>rel B</sub> | 8   | -4 V reference voltage for the right channel switched capacitor DAC                                                     |  |  |  |

| AGNO DAC R         | 9   | 0 V reference voltage for the right channel switched capacitor DAC; this pin<br>should be connected to analog ground    |  |  |  |

| -DAC R             | 10  | output from the right negative switched capacitor DAC; feedback connection for the right negative operational amplifier |  |  |  |

| +DAC R             | 11  | output from the right positive switched capacitor DAC; feedback connection for the right positive operational amplifier |  |  |  |

| AGND R             | 12  | 0 V reference voltage for both right channel operational amplifiers                                                     |  |  |  |

| n.c.               | 13  | pin not connected; should preferably be connected to analog ground                                                      |  |  |  |

| +OUT R             | 14  | + output of the switched capacitor operational amplifier                                                                |  |  |  |

| -OUT R             | 15  | - output of the switched capacitor operational amplifier                                                                |  |  |  |

| V <sub>SSA</sub>   | 16  | -5 V analog supply                                                                                                      |  |  |  |

| V <sub>DDA</sub>   | 17  | 5 V analog supply                                                                                                       |  |  |  |

| -OUT L             | 18  | - output of the switched capacitor operational amplifier                                                                |  |  |  |

| +OUT L             | 19  | + output of the switched capacitor operational amplifier                                                                |  |  |  |

| n.c.               | 20  | pin not connected; should preferably be connected to analog ground                                                      |  |  |  |

| AGND L             | 21  | 0 V reference voltage for both left channel operational amplifiers                                                      |  |  |  |

| +DAC L             | 22  | output from the left positive switched capacitor DAC; feedback connection for the left positive operational amplifier   |  |  |  |

| -DAC L             | 23  | output from the left negative switched capacitor DAC; feedback connection for the left negative operational amplifier   |  |  |  |

| AGND DAC L         | 24  | 0 V reference voltage for the left channel switched capacitor DAC; this pin<br>should be connected to analog ground     |  |  |  |

| V <sub>ref L</sub> | 25  | -4 V reference voltage for the left channel switched capacitor DAC                                                      |  |  |  |

| V <sub>SSD L</sub> | 26  | -3.5 V digital supply for the left channel; this voltage determines the internal<br>logic LOW level in the left channel |  |  |  |

| V <sub>000</sub> L | 27  | 5 V digital supply for the left channel; this voltage determines the internal logic HIGH level in the left channel      |  |  |  |

September 1991

826

TDA1547

| SYMBOL           | PIN | DESCRIPTION                                                         |

|------------------|-----|---------------------------------------------------------------------|

| CLK L            | 28  | clock input for the left channel                                    |

| n.c.             | 29  | pin not connected; should preferably be connected to digital ground |

| IN L             | 30  | serial one-bit data input for the left channel                      |

| V <sub>SSD</sub> | 31  | -5 V digital supply for both channels                               |

| V <sub>SUB</sub> | 32  | -5 V substrate voltage                                              |

## QUICK REFERENCE DATA

| SYMBOL                | PARAMETER                                                            | CONDITION                                     | MIN         | TYP   | MAX  | UNIT |

|-----------------------|----------------------------------------------------------------------|-----------------------------------------------|-------------|-------|------|------|

| Supply volta          | ges                                                                  |                                               | <del></del> |       | 1    |      |

| V <sub>DDD L. A</sub> | positive digital supply voltage<br>for one channel;<br>pins 27 and 6 |                                               | 4.5         | 5.0   | 5.5  | V    |

| V <sub>DDD</sub>      | digital supply voltage for both channels; pin 2                      |                                               | 4.5         | 5.0   | 5.5  | V    |

| V <sub>SSD L</sub> A  | negative digital supply<br>voltage for one channel;<br>pins 26 and 7 |                                               | -4.0        | -3.5  | -3.0 | V    |

| V <sub>sso</sub>      | negative digital supply<br>voltage for both channels; pin<br>31      |                                               | -5.5        | -5.0  | -4.5 | V    |

| V <sub>DDA</sub>      | positive analog supply<br>voltage; pin 17                            |                                               | 4.5         | 5.0   | 6    | V    |

| V <sub>SSA</sub>      | negative analog supply voltage; pin 16                               |                                               | -6.0        | -5.0  | -4.5 | v    |

| Supply curre          | nt                                                                   |                                               |             |       |      | -L   |

| 000 L. A              | positive digital supply current<br>for one channel;<br>pins 27 and 6 |                                               | -           | 0.1   | •    | mA   |

| DDD                   | digital supply current for both channels; pin 2                      |                                               | -           | 29.0  | -    | mA   |

| SSO L R               | negative digital supply<br>current for one channel;<br>pins 26 and 7 |                                               | -           | -0.1  | -    | mA   |

| SSO                   | negative supply current for both channels; pin 31                    |                                               | -           | -28.0 | -    | mA   |

| DOA                   | positive analog supply current; pin 17                               |                                               | -           | 51.0  | -    | mA   |

| SSA                   | negative analog supply current; pin 16                               |                                               | -           | -51.0 |      | mA   |

| tot                   | total power dissipation                                              |                                               | -           | 800   |      | mW   |

| OUT(RMS)              | output voltage (RMS value)                                           | f <sub>CUK</sub> = 8.46 MHz;<br>notes 1 and 2 | 0.85        | 1.0   | 1.15 | V    |

September 1991

827

## TDA1547

| SYMBOL           | PARAMETER                            | CONDITION                      | MIN | TYP    | MAX    | UNIT |

|------------------|--------------------------------------|--------------------------------|-----|--------|--------|------|

| Supply currer    | nt                                   | · · ·                          |     |        |        |      |

| (THD + N)/S      | THD + Noise; 0 dB                    | 1 kHz;                         | -   | -101   | -96    | dB   |

| (1110 + 11)/6    |                                      | notes 2 and 3                  | 1-  | 0.0009 | 0.0016 | %    |

| (THD + N)/S      | THD + Noise; 0 dB                    | f = 20 Hz to 20                | -   | -101   | -      | dB   |

| (1110 1117       |                                      | kHz; notes 2 and 4             | Ī-  | 0.0009 | -      | %    |

| (THD + N)/S      | THD + Noise; -20 dB                  | f = 1 kHz;<br>notes 2 and 3    |     | -88    | -84    | dB   |

| (THD + N)/S      | THD + Noise; -60 dB                  | f = 1 kHz;<br>notes 2 and 3    | -   | -48    | -44    | d₿   |

| S/N              | signal-to-noise ratio                | pattern 0101;<br>notes 2 and 5 | 109 | 111    | -      | dB   |

| S/N              | signal-to-noise ratio; "A"-weighting | pattern 0101;<br>notes 2 and 5 | -   | 113    | -      | dB   |

| f <sub>cux</sub> | maximum clock frequency              |                                | 1-  | -      | 10     | MHz  |

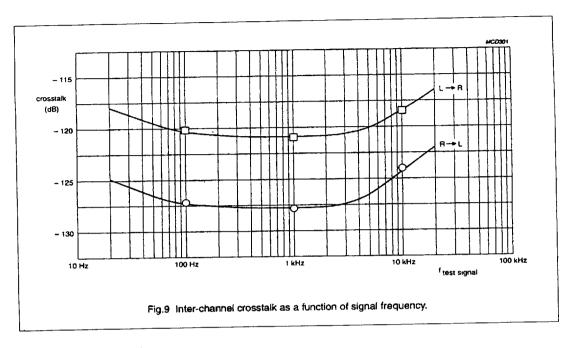

| α                | channel separation                   | f = 1 kHz                      | 101 | 115    | -      | dВ   |

| T <sub>amb</sub> | operating ambient temperature        |                                | -20 | -      | 70     | °C   |

## Notes to the quick reference data

- 1. Output level tracks linearly with both the clock frequency and the reference voltage (V, or V ref R)

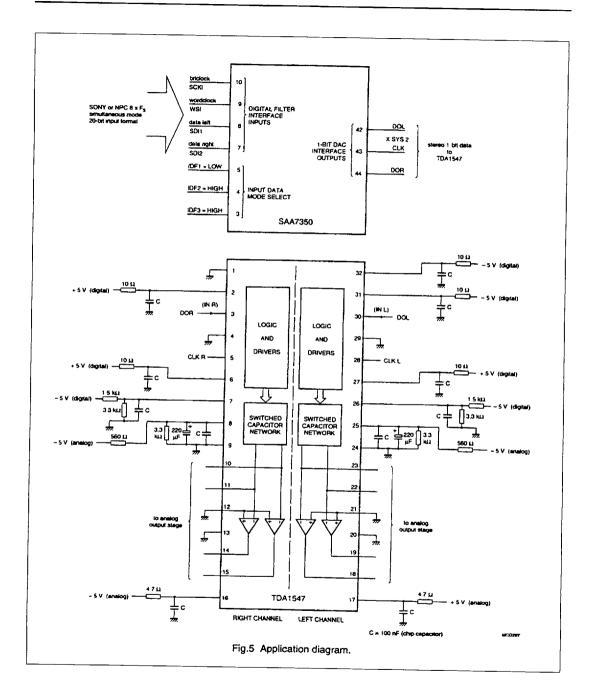

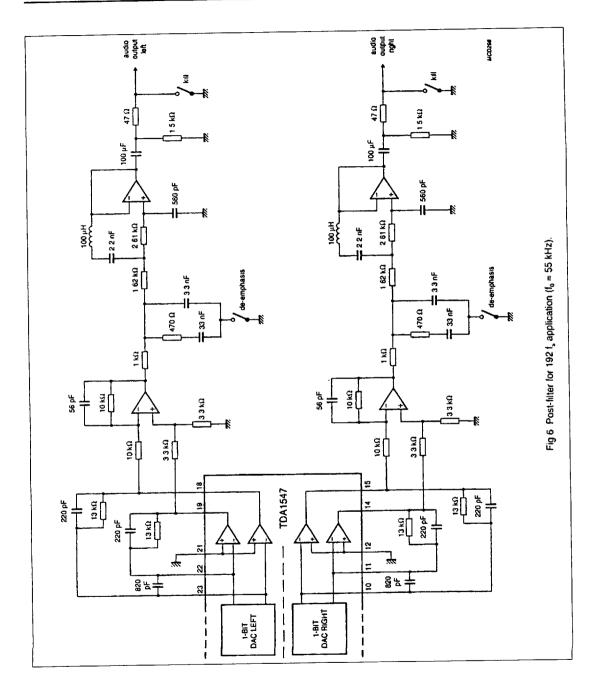

- 2. Device measured in differential mode with external components as shown in Fig.5.

- Measured with a one-bit data signal generated by the SAA7350 from an 8 f, (352.8 kHz), 20-bit, 1 kHz digital sinewave. Measured over a 20 Hz to 20 kHz bandwidth.

- Measured with a one-bit data signal generated by the SAA7350 from an 8 f<sub>s</sub> (352.8 kHz), 20-bit, 20 Hz to 20 kHz digital sinewave. Measured over a 20 Hz to 20 kHz bandwidth.

- 5. The specified signal-to-noise ratio includes noise introduced by the application components as shown in Fig.5.

#### **FUNCTIONAL DESCRIPTION**

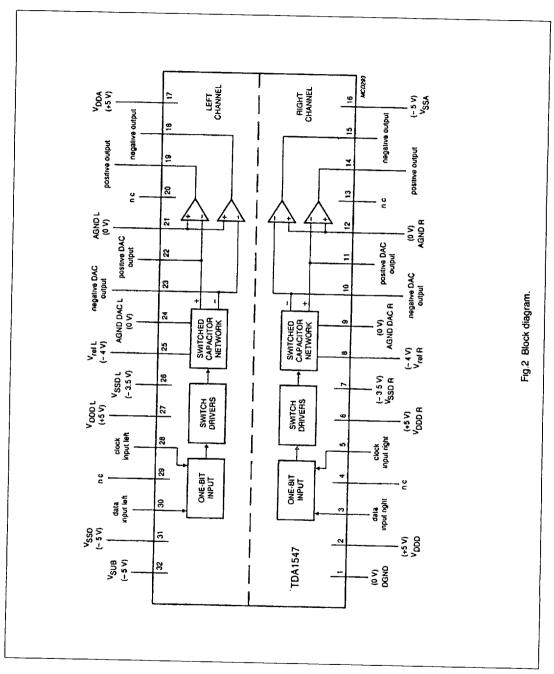

Both channels are completely separated to reach the desired high crosstalk suppression level. Each channel consists of the following functional parts:

- One-bit input, which latches the incoming data to the system clock.

- Switch driver circuit, which generates the non-overlapping clock- and data-signals that control the DAC switched capacitor networks.

- Switched capacitor network, this forms the actual DAC function, it supplies charge packets to the low-pass filter, under control of the incoming one-bit code.

- Two high performance operational amplifiers, that perform the charge packet to voltage conversion and deliver a differential output signal. The first pole of the low-pass filter is built around them.

#### THERMAL RESISTANCE

| SYMBOL             | PARAMETER                | MAX. | UNIT |  |

|--------------------|--------------------------|------|------|--|

| R <sub>th P4</sub> | from junction to ambient | 60   | KW   |  |

September 1991

828

| 7110826 0079161 624 📰

**TDA1547**

September 1991

829

**7110826 0079162 560**

**TDA1547**

### LIMITING VALUES

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL                                         | PARAMETER                                                   | CONDITIONS               | MIN  | MAX.                  | UNIT |

|------------------------------------------------|-------------------------------------------------------------|--------------------------|------|-----------------------|------|

| V <sub>SUB</sub>                               | negative substrate voltage; pin 32                          | note 1                   | -7.0 | <b></b>               |      |

| V <sub>OOD L. R</sub>                          | positive digital supply voltage;<br>pins 27 and 6           |                          | -    | 5.5                   | V    |

| V <sub>DOD</sub>                               | positive digital supply voltage;<br>pin 2                   |                          | -    | 5.5                   | V    |

| V <sub>SSO L. R</sub>                          | negative digital supply voltage;<br>pins 26 and 7           |                          | -4.0 | •                     | ٧    |

| V <sub>SSD</sub>                               | negative digital supply voltage;<br>pin 31                  |                          | -5.5 | -                     | V    |

| V <sub>DDA</sub>                               | positive analog supply voltage;<br>pin 17                   |                          | •    | 6.0                   | v    |

| V <sub>SSA</sub>                               | negative analog supply voltage;<br>pin 16                   |                          | 6.0  | •                     | V    |

| V <sub>DDO L R</sub> -<br>V <sub>SSD L R</sub> | supply voltage difference between pins 27, 6 and pins 26, 7 |                          | -    | 9.0                   | V    |

| P <sub>lot</sub>                               | total power dissipation                                     | T <sub>amb</sub> = 70 °C | ·    | 1300                  | mW   |

| V <sub>ref L R</sub>                           | input reference voltage; pins 25 and 8                      |                          | -6.0 |                       | V    |

| V <sub>CLK L. R</sub>                          | input voltage clock; pins 28 and 5                          |                          | -0.5 | V <sub>000</sub> +0.5 | V    |

| VIL                                            | input voltage channel; pin 30                               |                          | -0.5 | V <sub>000</sub> +0.5 | V    |

| V <sub>1 B</sub>                               | input voltage channel; pin 3                                |                          | -0.5 | V <sub>000</sub> +0.5 | V    |

| T <sub>amb</sub>                               | operating ambient temperature                               |                          | -20  | 70                    | °C   |

| T <sub>stg</sub>                               | storage temperature                                         |                          | -40  | 150                   | .€   |

| T <sub>XTAL</sub>                              | maximum crystal temperature                                 |                          | ·    | 150                   | °C   |

| V <sub>ES</sub>                                | electrostatic handling                                      | note 2                   | -    | 2000                  | V    |

## Notes to the limiting values

- 1. The substrate voltage must be lower than or equal to the lowest supply voltage.

- 2. Equivalent to discharging a 100 pF capacitor through a 1.5  $k\Omega$  series resistor.

September 1991

830

TDA1547

## CHARACTERISTICS

$V_{\text{DDO}}$ ,  $V_{\text{DDD}}$  L R,  $V_{\text{DDA}}$  = +5 V;  $V_{\text{SSO}}$ ,  $V_{\text{SSO}}$  L, R = -3.5 V;  $V_{\text{ref}}$  L R = -4 V;  $T_{\text{amb}}$  = 25°C;  $f_{\text{CLK}}$  = 8.46 MHz; unless otherwise specified

| SYMBOL                                           | PARAMETER                                                      | CONDITIONS                     | MIN           | TYP                                            | MAX          | UNI |

|--------------------------------------------------|----------------------------------------------------------------|--------------------------------|---------------|------------------------------------------------|--------------|-----|

| SUPPLY                                           |                                                                |                                |               |                                                |              |     |

| V <sub>sue</sub>                                 | negative substrate voltage;<br>pin 32                          | note 1                         | -7.0          | Ţ-                                             | -4.5         | ٧   |

| V <sub>DDD L R</sub>                             | positive digital supply voltage for one channel; pins 27 and 6 |                                | 4.5           | 5.0                                            | 5.5          | V   |

| V <sub>DDD</sub>                                 | digital supply voltage for both channels; pin 2                |                                | 4.5           | 5.0                                            | 5.5          | V   |

| V <sub>SSD L. R</sub>                            | negative digital supply voltage for one channel; pins 26 and 7 |                                | -4.0          | -3.5                                           | -3.0         | V   |

| V <sub>sso</sub>                                 | negative digital supply voltage for both channels; pin 31      |                                | -5.5          | -5.0                                           | -4.5         | V   |

| V <sub>DDA</sub>                                 | positive analog supply voltage; pin 17                         |                                | 4.5           | 5.0                                            | 6.0          | ·   |

| V <sub>SSA</sub>                                 | negative analog supply voltage; pin 16                         |                                | -6.0          | -5.0                                           | -4.5         | ·   |

| V <sub>DOD L. A</sub> -<br>V <sub>SSD L. R</sub> | supply voltage difference between pins 27, 6 and pins 26, 7    |                                | -             | -                                              | 9.0          | V   |

| V <sub>SSD L. R</sub> - V <sub>SSO</sub>         | pins 26, 7 and pin 31                                          |                                | 1.3           | -                                              | -            | V   |

| DOD L. R                                         | positive digital supply current for one channel; pins 27 and 6 |                                | -             | 0.1                                            | -            | mA  |

| DDD                                              | digital supply current for both channels; pin 2                |                                |               | 29.0                                           | 46           | mA  |

| SSO L. A                                         | negative digital supply current for one channel; pins 26 and 7 |                                | -             | -0.1                                           | -            | mA  |

| SSD                                              | negative supply current for both channels; pin 31              |                                | -45           | -28.0                                          | -            | mA  |

| DDA                                              | positive analog supply current; pin 17                         |                                | 1.            | 51.0                                           | 63           | mA  |

| SA                                               | negative analog supply current; pin 16                         |                                | -63.0         | -51.0                                          | -            | mA  |

| SSRI                                             | power supply rejection ratio                                   | V <sub>DDD L. B</sub> ; note 6 | 50            | -                                              | -            | dΒ  |

| SSR2                                             | power supply rejection ratio                                   | V <sub>DDD</sub> , note 6      | 50            | -                                              |              | dB  |

| SSR3                                             | power supply rejection ratio                                   | V <sub>SSD L R</sub> , note 6  | 60            | †                                              |              | dB  |

| SSR4                                             | power supply rejection ratio                                   | V <sub>sso</sub> ; note 6      | 50            | -                                              | -            | dB  |

| SSAS                                             | power supply rejection ratio                                   | V <sub>DDA</sub> ; note 6      | 60            | 1-                                             | <del> </del> | dΒ  |

| SSR6                                             | power supply rejection ratio                                   | V <sub>SSA</sub> ; note 6      | 60            | †-                                             | -            | dB  |

| 01                                               | total power dissipation                                        |                                | <del> -</del> | 800                                            | -            | mW  |

| lock - Input                                     |                                                                |                                |               | <u> Т.                                    </u> | <u> </u>     | L   |

| ι                                                | input voltage LOW                                              |                                | -             | 1.                                             | 0.5          | V   |

| H                                                | input voltage HIGH                                             |                                | 4.5           |                                                | -            | v   |

|                                                  | input current LOW                                              | V, = 0.5 V                     | -10           |                                                | 10           | μА  |

September 1991

831

**7110826 0079164 333**

TDA1547

| SYMBOL                | PARAMETER                                               | CONDITIONS                     | MIN  | ТҮР        | MAX            | UNIT       |

|-----------------------|---------------------------------------------------------|--------------------------------|------|------------|----------------|------------|

| Clock - Input         |                                                         |                                |      |            |                |            |

| th .                  | input current HIGH                                      | V, = 4.5 V                     | -10  | -          | 10             | μА         |

| C <sub>1</sub>        | clock input capacitance                                 |                                | -    | 5          |                | pF         |

| CLK                   | clock input frequency                                   |                                | •    | <u> </u>   | 10             | MHz        |

| Channel left/rig      | ht inputs                                               |                                |      |            |                |            |

| V <sub>IL</sub>       | input voltage LOW                                       |                                | -    |            | 0.5            | ٧          |

| V <sub>M</sub>        | input voltage HIGH                                      |                                | -    | 4.5        | -              | ٧          |

| I <sub>IL</sub>       | input current LOW                                       | V; = 0.5 V                     | -10  | -          | 10             | μА         |

| I <sub>IH</sub>       | input current HIGH                                      | V, = 4.5 V                     | 10   |            | 10             | μА         |

| C <sub>i</sub>        | channel input capacitance;<br>pins 3, 30                |                                | -    | 5          | -              | pF         |

| V <sub>ref</sub>      | reference input voltage;<br>pins 8, 25                  | note 2                         | •    | -4 ±0.4    | -              | \ <u>\</u> |

| Audio outputs         |                                                         |                                |      |            |                |            |

| V <sub>OUT(RMS)</sub> | output voltage (RMS value); pins<br>14, 19; pins 15, 18 | notes 2 and 3                  | 0.85 | 1.0        | 1.15           | ٧          |

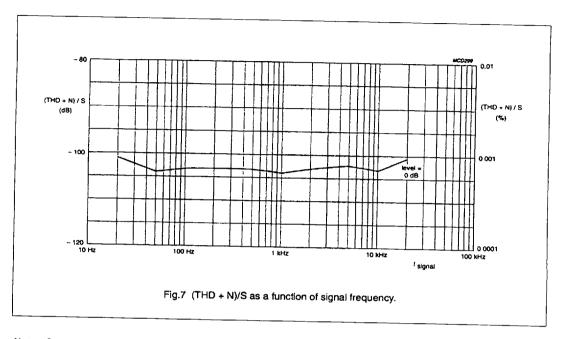

| (THD + N)/S           | THD + Noise; 0 dB                                       | f = 1 kHz;<br>notes 3 and 4    |      | -101       | -96            | dB         |

| (11.5 : 11,70         |                                                         |                                | -    | 0.0009     | 0.0016         | %          |

| (THD + N)/S           | THD + Noise; 0 dB                                       | 20 Hz - 20 kHz;                | •    | -101       | -              | dB         |

| (11.15                |                                                         | notes 3 and 5                  | ·    | 0.0009     | <u> -</u>      | %          |

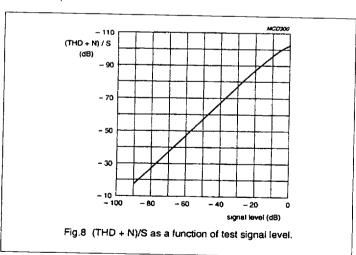

| (THD + N)/S           | THD + Noise; -20 dB                                     | f = 1 kHz;<br>notes 3 and 4    | -    | 88         | -84            | dB         |

| (THD + N)/S           | THD + Noise; -60 dB                                     | f = 1 kHz;<br>notes 3 and 4    | •    | -48        | <del>-44</del> | dB         |

| S/N                   | signal-to-noise ratio                                   | pattern 0101;<br>notes 3 and 7 | 109  | 111        | -              | dB         |

| S/N                   | signal-to-noise ratio; "A"-weighting                    | pattern 0101;<br>notes 3 and 7 | -    | 113        | -              | dB         |

| α                     | channel separation                                      | f = 1 kHz                      | 101  | 115        | <u> </u>       | dB         |

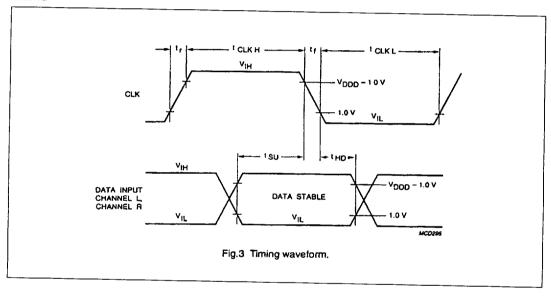

| Timing                |                                                         |                                |      |            |                |            |

| ţ.                    | rise time clock input                                   | C <sub>L</sub> = 20 pF         | -    | 5          | 10             | ns         |

| t                     | fall time clock input                                   | C <sub>L</sub> = 20 pF         | -    | 5          | 10             | ns         |

| t <sub>cux i</sub>    | clock input LOW time                                    |                                | 45   | - <u> </u> |                | ns         |

| t <sub>CLK H</sub>    | clock input HIGH time                                   |                                | 45   | -          | -              | ns         |

| t,                    | channel input rise time                                 | C <sub>L</sub> = 20 pF         | -    | 10         | 15             | ns         |

| 4                     | channel input fall time                                 | C <sub>L</sub> = 20 pF         | -    | 10         | 15             | ns         |

| t <sub>HD</sub>       | channel input hold time                                 |                                | 25   | -          | -              | ns         |

| t <sub>su</sub>       | channel input set-up time                               |                                | 0    | -          | -              | ns         |

September 1991

832

**7110826 0079165 277**

TDA1547

#### Notes to the characteristics

- 1. The substrate voltage must be lower than or to equal than the lowest supply voltage.

- 2. Output level tracks linearly with both the clock frequency and the reference voltage (V<sub>ref L</sub> or V<sub>ref R</sub>).

- 3. Device measured in differential mode with external components as shown in Fig.5.

- Measured with a one-bit data signal generated by the SAA7350 from an 8 f<sub>3</sub> (352.8 kHz), 20-bit, 1 kHz digital sinewave. Measured over a 20 Hz to 20 kHz bandwidth.

- Measured with a one-bit data signal generated by the SAA7350 from an 8 f<sub>s</sub> (352.8 kHz), 20-bit, 20 Hz to 20 kHz digital sinewave. Measured over a 20 Hz to 20 kHz bandwidth.

- 6. Power supply rejection ratio measured with  $f_{riople} = 1$  kHz and  $v_{riople} = 100$  mV.

- 7. The specified signal-to-noise ratio includes noise introduced by the application components as shown in Fig.5.

### TIMING

**TDA1547**

### APPLICATION INFORMATION

TDA1547

September 1991

835

■ 7110826 0079168 T89 ■

TDA1547

September 1991

836

**■ 7110826 0079169 915**

TDA1547

Note: Graph constructed from average measurements values of a small amount of engineering samples. No guarantee for typical values is implied.

Note: Graph constructed from average measurement values of a small amount of engineering samples. No guarantee for typical values is implied.

September 1991

837

■ 7110826 0079170 637 **■**

## **TDA1547**

Note: Graph constructed from average measurements values of a small amount of engineering samples. No guarantee for typical values is implied.

September 1991

838

| 7110826 0079171 573 **|**