# MOS INTEGRATED CIRCUIT $\mu$ PD75064, 75066, 75068, 75064(A), 75066(A), 75068(A)

# 4-BIT SINGLE-CHIP MICROCOMPUTER

The  $\mu$ PD75068 is a member of the 75X series of 4-bit single-chip microcomputers.

The minimum instruction execution time of the  $\mu$ PD75068's CPU is 0.95  $\mu$ s. In addition to this high-speed capability, the chip contains an A/D converter and furnishes high-performance functions such as the serial bus interface (SBI) function compliant with the NEC standard format, providing powerful features and high cost performance. The  $\mu$ PD75068(A) is a high-reliability version of the  $\mu$ PD75068.

NEC also provides PROM versions suitable for small-scale production or evaluation samples in system development. The  $\mu$ PD75P068 is the PROM version for the  $\mu$ PD75064, 75066, 75068, and the  $\mu$ PD75P068(A) is that for the  $\mu$ PD75064(A), 75066(A), 75068(A).

The detailed function descriptions are described in the document below. Please make sure to read this document before starting design.

**μPD75068 User's Manual: IEU-1366**

#### **FEATURES**

- · Variable instruction execution time advantageous to high-speed operation and power-saving:

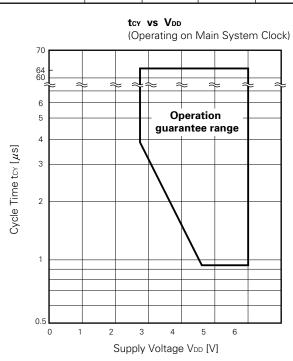

- 0.95  $\mu$ s, 1.91  $\mu$ s, or 15.3  $\mu$ s (at 4.19 MHz with the main system clock selected)

- 122 μs (at 32.768 kHz with the subsystem clock selected)

- A/D converter (8-bit resolution, successive approximation): 8 channels

- Capable of low-voltage operation: VDD = 2.7 to 6.0 V

- · Timer function: 3 channels

- · On-chip NEC standard serial bus interface (SBI)

- Very low-power watch operation enabled (5  $\mu$ A TYP. at 3 V)

- Pull-up resistor option allowed for 27 I/O lines

- The  $\mu$ PD75P068 and 75P068(A) (PROM versions) available: Capable of low-voltage operation (VDD = 2.7 to 6.0 V)

## **APPLICATIONS**

- $\mu$ PD75064, 75066, 75068 Home electronic appliances, air conditioners, cameras, and electronic measuring instruments

- μPD75064(A), 75066(A), 75068(A)

Automotive electronics

The information in this document is subject to change without notice.

Document No. IC-3140B ( O.D. No. IC-8629B) Date Published December 1994 P Printed in Japan The  $\mu$ PD75064, 75066, 75068 and  $\mu$ PD75064(A), 75066(A), 75068(A) differ only in their quality grade. Unless otherwise specified, this data sheet describes the  $\mu$ PD75068 as the representative product. For products with the suffix (A) attached, please make the following substitutions when reading:

$\mu$ PD75064 —>  $\mu$ PD75064(A)  $\mu$ PD75066 —>  $\mu$ PD75066(A)  $\mu$ PD75068 —>  $\mu$ PD75068(A)

# **ORDERING INFORMATION**

| Part number                | Package                             | Quality Grade |

|----------------------------|-------------------------------------|---------------|

| μPD75064CU-xxx             | 42-pin plastic shrink DIP (600 mil) | Standard      |

| $\mu$ PD75064GB-xxx-3B4    | 44-pin plastic QFP (10x10 mm)       | Standard      |

| μPD75066CU-xxx             | 42-pin plastic shrink DIP (600 mil) | Standard      |

| μPD75066GB-xxx-3B4         | 44-pin plastic QFP (10x10 mm)       | Standard      |

| $\mu$ PD75068CU-xxx        | 42-pin plastic shrink DIP (600 mil) | Standard      |

| $\mu$ PD75068GB-xxx-3B4    | 44-pin plastic QFP (10x10 mm)       | Standard      |

| $\mu$ PD75064CU(A)-xxx     | 42-pin plastic shrink DIP (600 mil) | Special       |

| μPD75064GB(A)-xxx-3B4      | 44-pin plastic QFP (10x10 mm)       | Special       |

| $\mu$ PD75066CU(A)-xxx     | 42-pin plastic shrink DIP (600 mil) | Special       |

| $\mu$ PD75066GB(A)-xxx-3B4 | 44-pin plastic QFP (10x10 mm)       | Special       |

| $\mu$ PD75068CU(A)-xxx     | 42-pin plastic shrink DIP (600 mil) | Special       |

| μPD75068GB(A)-xxx-3B4      | 44-pin plastic QFP (10x10 mm)       | Special       |

Remark xxx: ROM code suffix

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# **\star** DIFFERENCE BETWEEN $\mu$ PD7506x SUBSERIES AND $\mu$ PD7506x(A) SUBSERIES

| Part number   | μPD75064 | μPD75064(A) |

|---------------|----------|-------------|

|               | μPD75066 | μPD75066(A) |

| Parameter     | μPD75068 | μPD75068(A) |

| Quality grade | Standard | Special     |

# **FUNCTION OVERVIEW**

| ltem                                                                              |          | Function                                                                                                                        |                                                                                                                              |                                                                |                                                                                   |  |

|-----------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| Instruction execut                                                                | ion time | • Main system clock : 0.95 $\mu$ s, 1.91 $\mu$ s, 15.3 $\mu$ s (at 4.19 MHz)<br>• Subsystem clock : 122 $\mu$ s (at 32.768 kHz) |                                                                                                                              |                                                                |                                                                                   |  |

| Internal memory                                                                   | ROM      | • µ                                                                                                                             | PD750                                                                                                                        | 064: 4096 × 8 bits<br>066: 6016 × 8 bits<br>068: 8064 × 8 bits |                                                                                   |  |

|                                                                                   | RAM      | 512                                                                                                                             | 2 × 4 k                                                                                                                      | oits                                                           |                                                                                   |  |

| General register                                                                  |          |                                                                                                                                 |                                                                                                                              | operating in 4 bits: 8 operating in 8 bits: 4                  |                                                                                   |  |

| I/O port                                                                          |          | 32                                                                                                                              | 12                                                                                                                           | CMOS input                                                     | Of these, seven with software-specifiable on-chip pull-up resistors               |  |

|                                                                                   |          |                                                                                                                                 | 12                                                                                                                           | CMOS I/O                                                       | Software-specifiable on-chip pull-up resistors Four pins can directly drive LEDs. |  |

|                                                                                   |          |                                                                                                                                 | 8                                                                                                                            | N-ch open-drain I/O                                            | Breakdown voltage: 10 V                                                           |  |

|                                                                                   |          |                                                                                                                                 |                                                                                                                              |                                                                | Mask-option-specifiable on-chip pull-up resistors                                 |  |

|                                                                                   |          |                                                                                                                                 |                                                                                                                              |                                                                | Can directly drive LEDs.                                                          |  |

| Timer                                                                             |          | 3 с                                                                                                                             | • Timer/event counter     • Basic interval timer : Applicable to watchdog timer     • Watch timer : Capable of buzzer output |                                                                |                                                                                   |  |

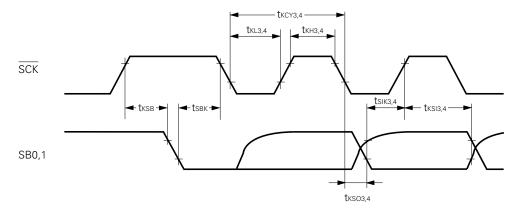

| Serial interface                                                                  |          | 3-wire serial I/O mode     2-wire serial I/O mode     SBI mode                                                                  |                                                                                                                              |                                                                |                                                                                   |  |

| Bit sequencial buf                                                                | fer      | 16                                                                                                                              | bits                                                                                                                         |                                                                |                                                                                   |  |

| Clock output func                                                                 | tion     | Φ,                                                                                                                              | fx/2 <sup>3</sup>                                                                                                            | , fx/2 <sup>4</sup> , fx/2 <sup>6</sup> (Main system           | clock: at 4.19 MHz operation)                                                     |  |

| A/D converter                                                                     |          |                                                                                                                                 |                                                                                                                              | esolution x 8 channels<br>ower operation possible :            | VDD = 2.7 to 6.0 V                                                                |  |

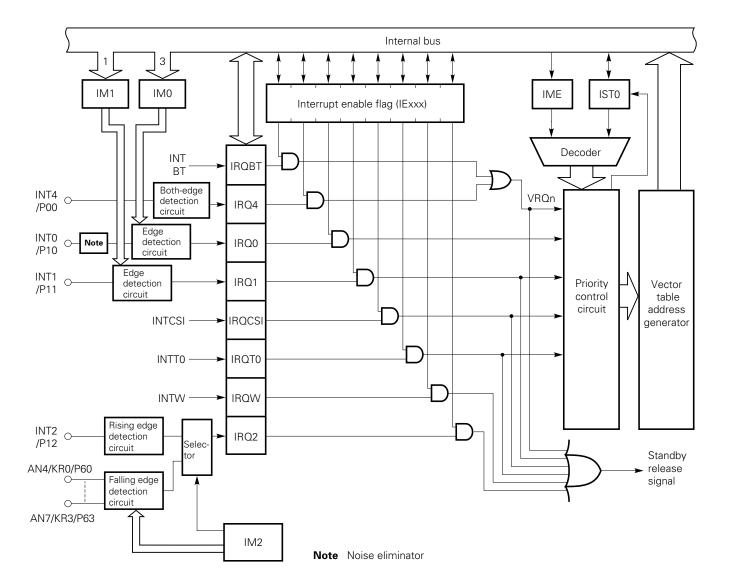

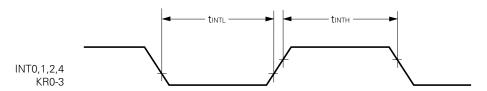

| Vectored interrupt                                                                | t        | Ext                                                                                                                             | ernal                                                                                                                        | : 3 , Internal : 3                                             |                                                                                   |  |

| Test input                                                                        |          | External: 1, Internal: 1                                                                                                        |                                                                                                                              |                                                                |                                                                                   |  |

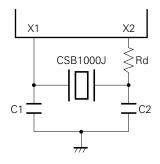

| System clock oscillator                                                           |          | Ceramic/crystal oscillator for main system clock     Crystal oscillator for subsystem clock                                     |                                                                                                                              |                                                                |                                                                                   |  |

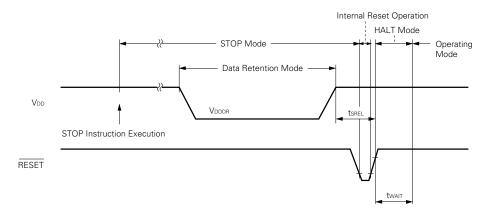

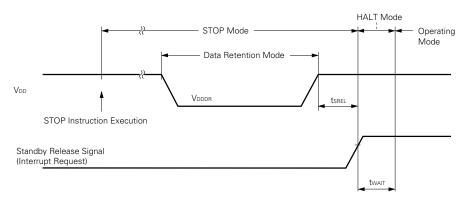

| Standby function                                                                  |          | ST                                                                                                                              | OP / F                                                                                                                       | IALT mode                                                      |                                                                                   |  |

| Operating ambien temperature                                                      |          |                                                                                                                                 |                                                                                                                              |                                                                |                                                                                   |  |

| Operating supply 2.7 to 6.0 V voltage                                             |          |                                                                                                                                 |                                                                                                                              |                                                                |                                                                                   |  |

| Package  • 42-pin plastic shrink DIP (600 mil)  • 44-pin plastic QFP (10 x 10 mm) |          |                                                                                                                                 | I)                                                                                                                           |                                                                |                                                                                   |  |

# **CONTENTS**

| 1. PIN CONFIGURATION (TOP VIEW)                | 5  |

|------------------------------------------------|----|

| 2. BLOCK DIAGRAM                               | 7  |

| 3. PIN FUNCTIONS                               | 8  |

| 3.1 Port Pins                                  | 8  |

| 3.2 Non-Port Pins                              | 9  |

| 3.3 Pin Input/Output Circuits                  | 10 |

| 3.4 Mask Option Selection                      | 12 |

| 3.5 Handling Unused Pins                       | 13 |

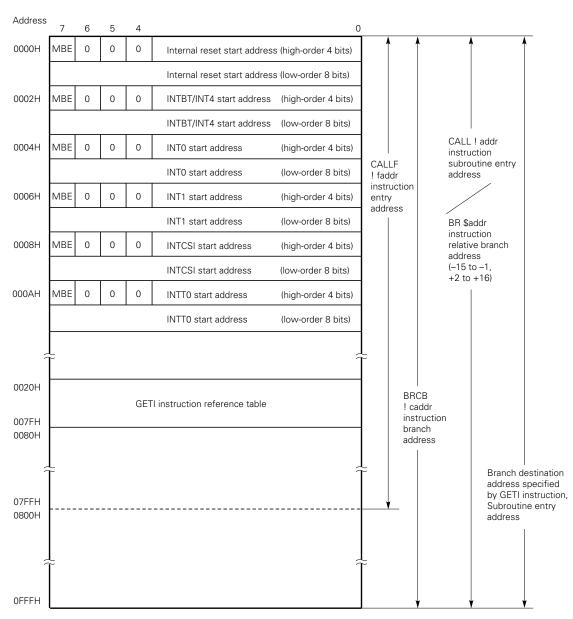

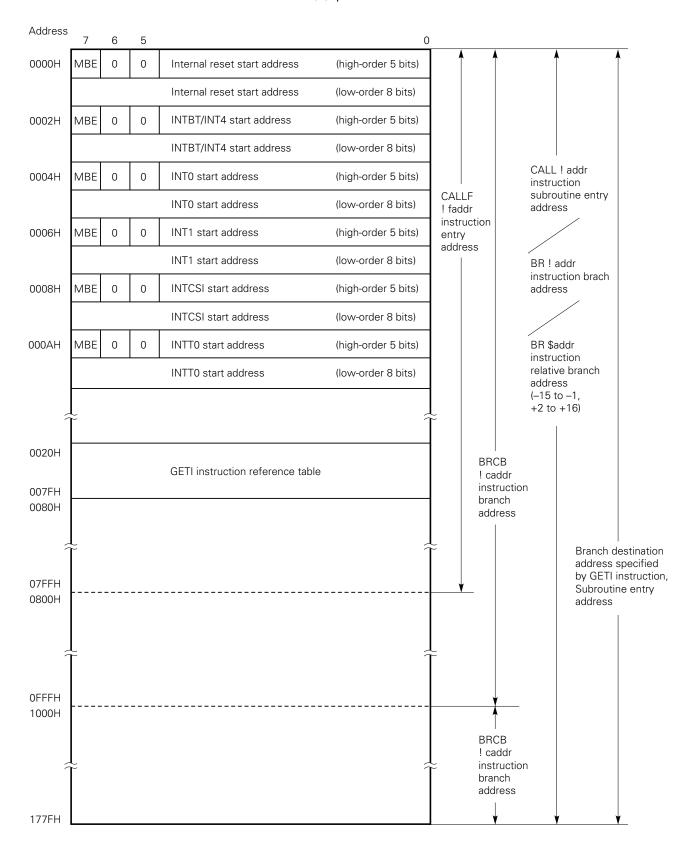

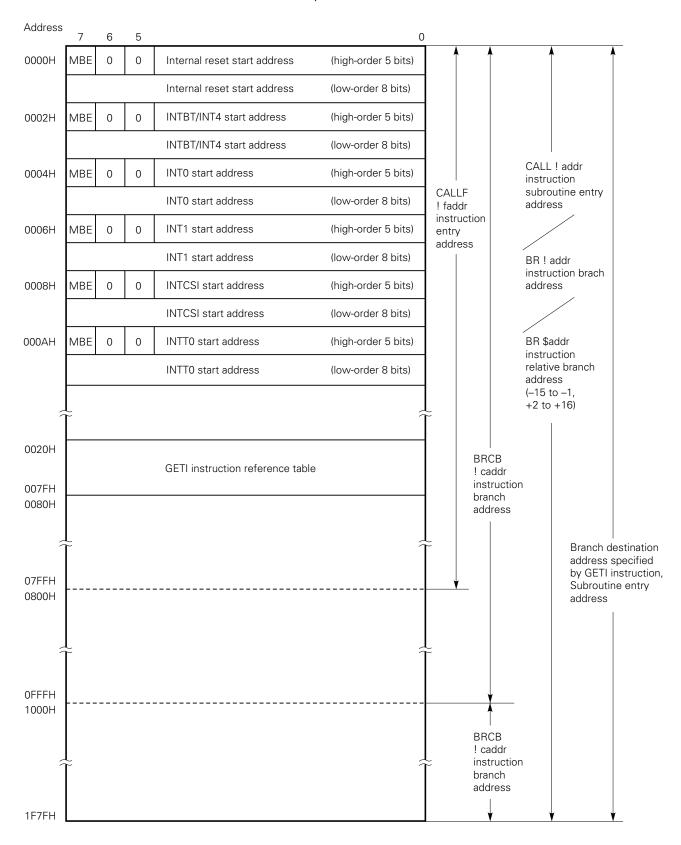

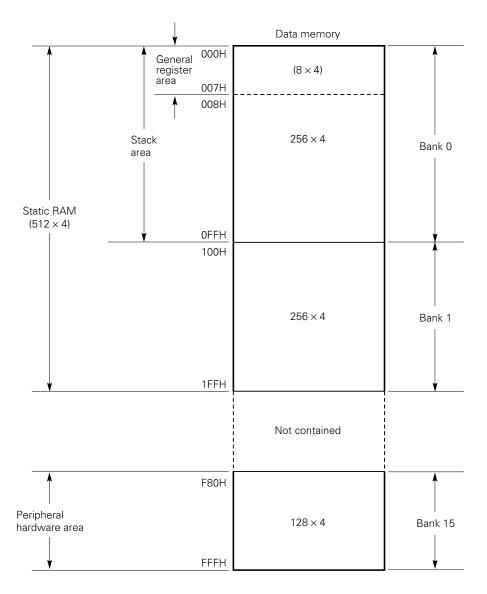

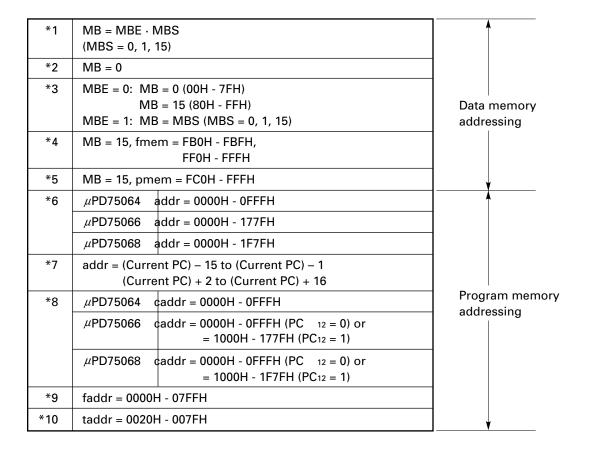

| 4. MEMORY CONFIGURATION                        | 14 |

| 5. PERIPHERAL HARDWARE FUNCTIONS               | 18 |

| 5.1 Ports                                      | 18 |

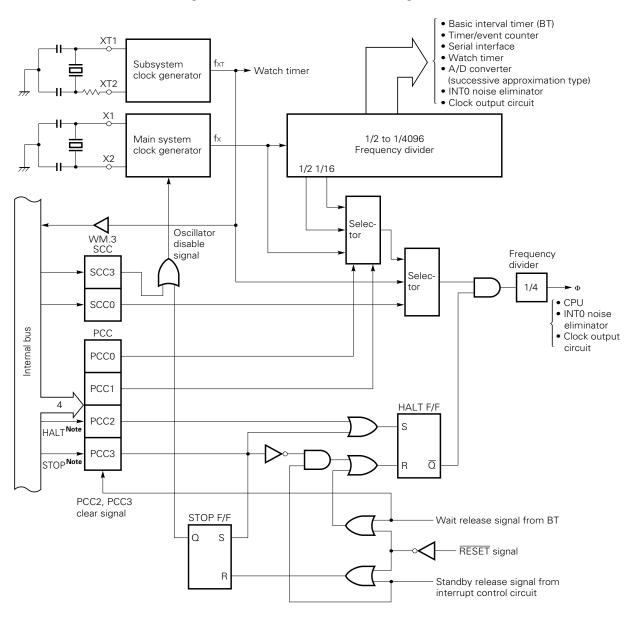

| 5.2 Clock Generator                            | 19 |

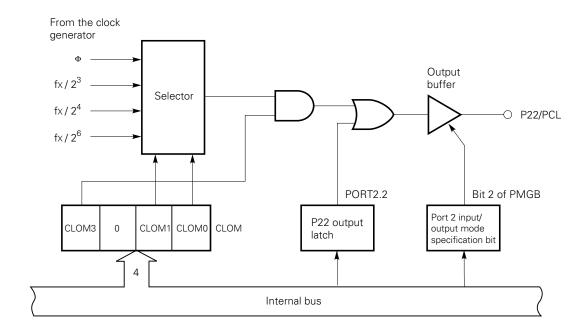

| 5.3 Clock Output Circuit                       | 20 |

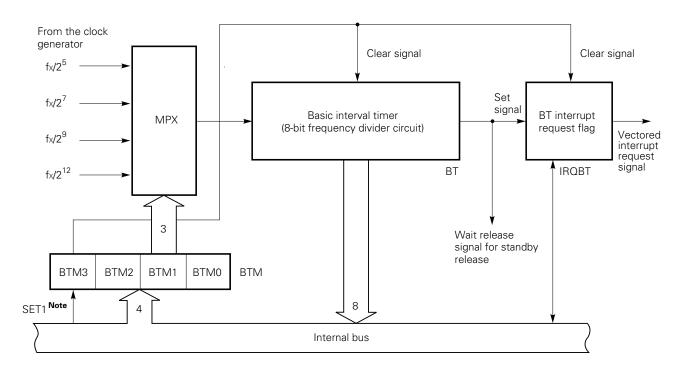

| 5.4 Basic Interval Timer                       | 21 |

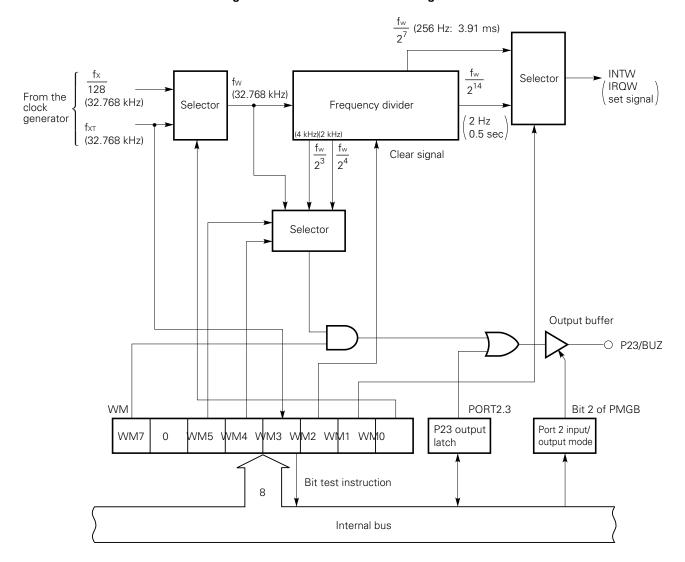

| 5.5 Watch Timer                                | 22 |

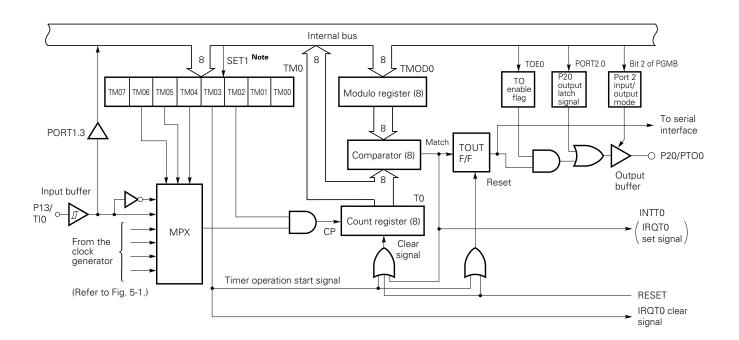

| 5.6 Timer/Event Counter                        | 23 |

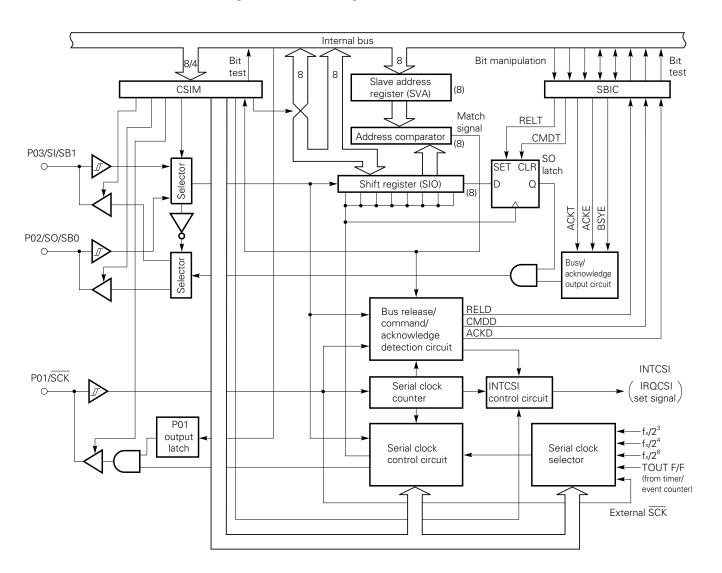

| 5.7 Serial Interface                           | 24 |

|                                                | 25 |

| 5.9 Bit Sequential Buffer                      | 26 |

| 6. INTERRUPT FUNCTIONS                         | 27 |

| 7. STANDBY FUNCTION                            | 29 |

| 8. RESET OPERATION                             | 30 |

| 9. INSTRUCTION SET                             | 32 |

| 10. ELECTRICAL SPECIFICATIONS                  | 40 |

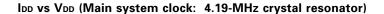

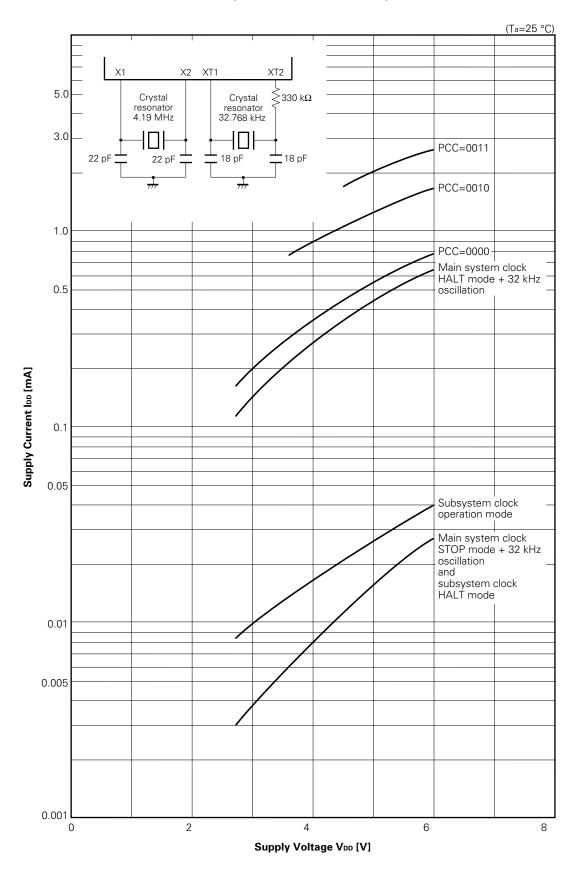

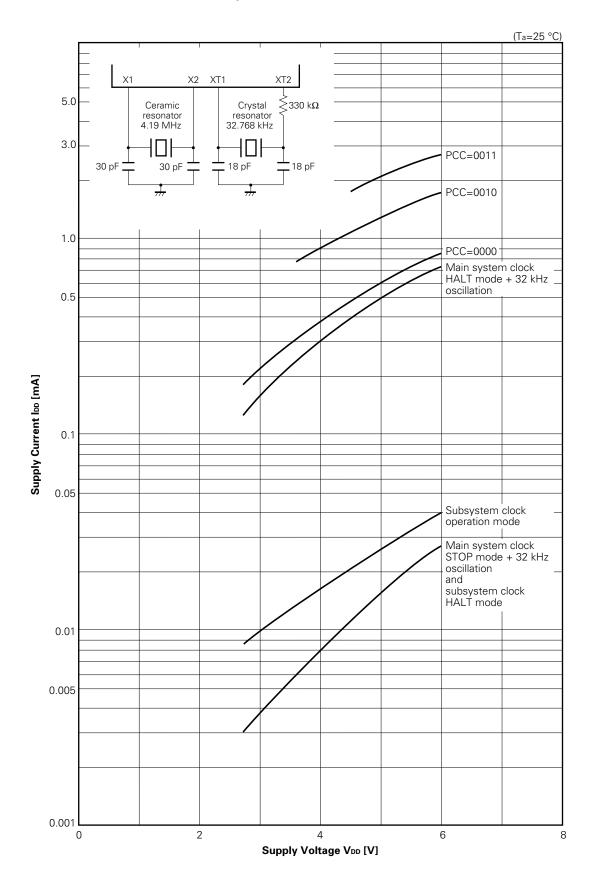

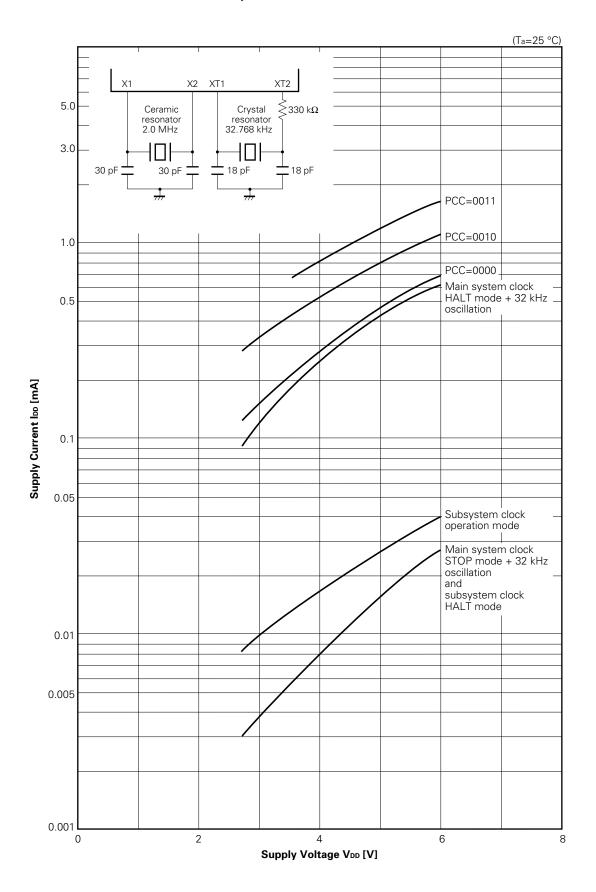

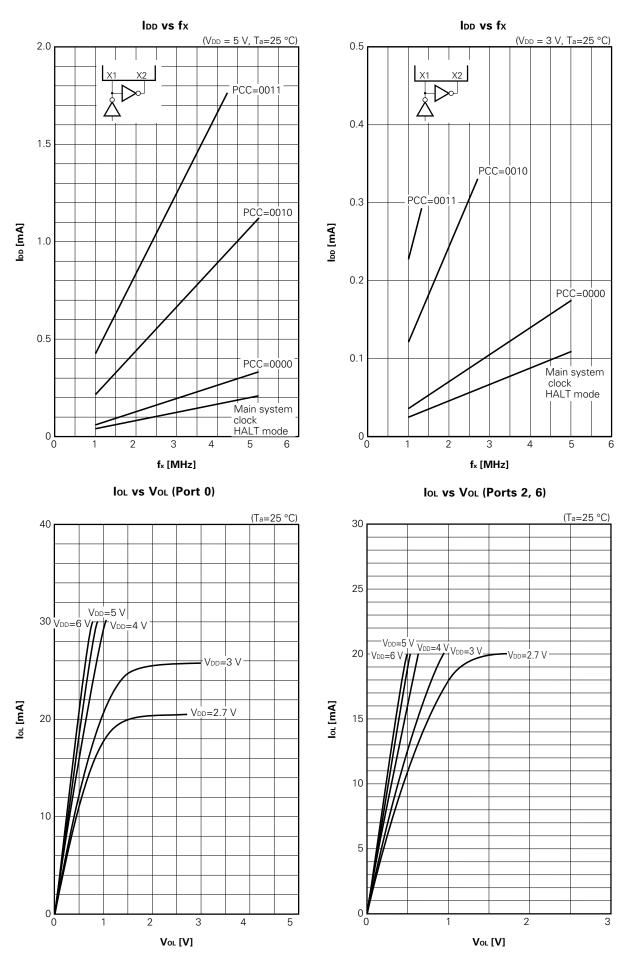

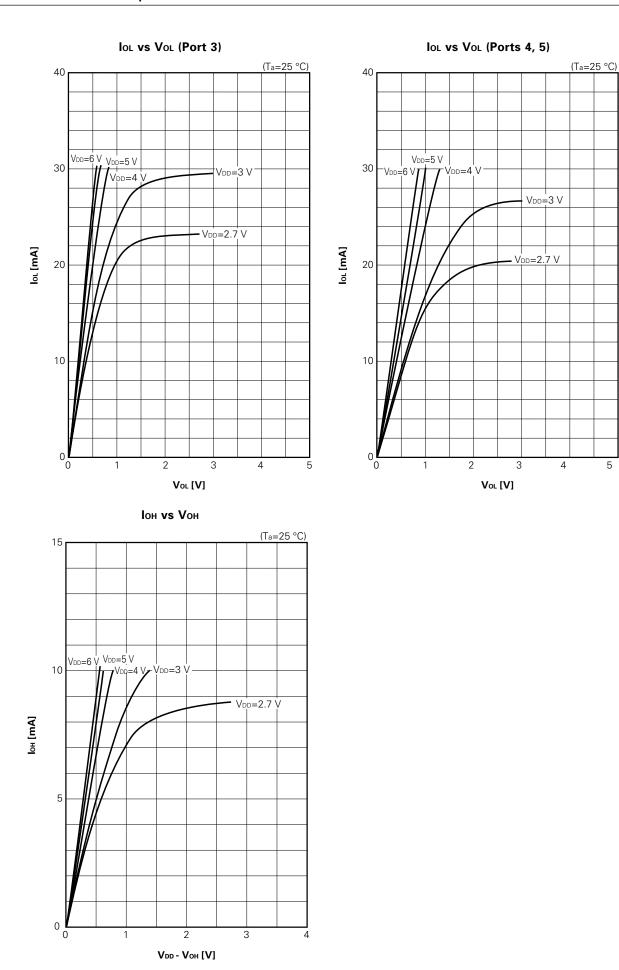

| 11. CHARACTERISTIC CURVES (FOR REFERENCE ONLY) | 54 |

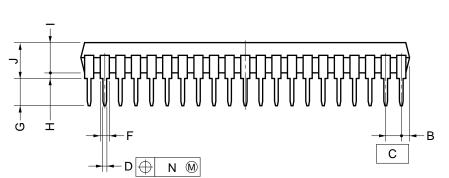

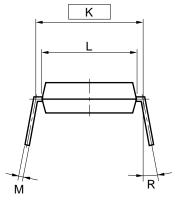

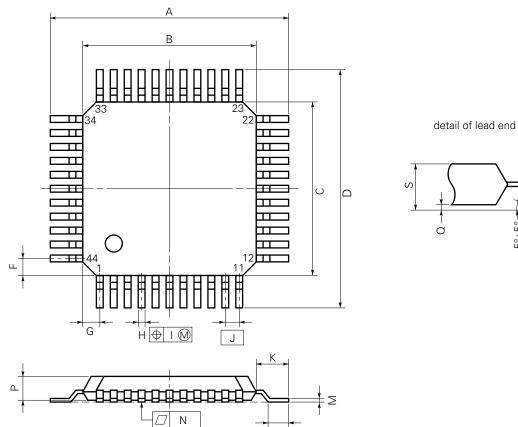

| 12. PACKAGE DRAWINGS                           | 60 |

| 13. RECOMMENDED SOLDERING CONDITIONS           | 62 |

| APPENDIX A. DEVELOPMENT TOOLS                  | 64 |

| APPENDIX B. RELATED DOCUMENTS                  | 65 |

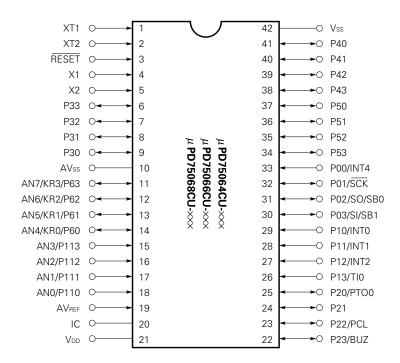

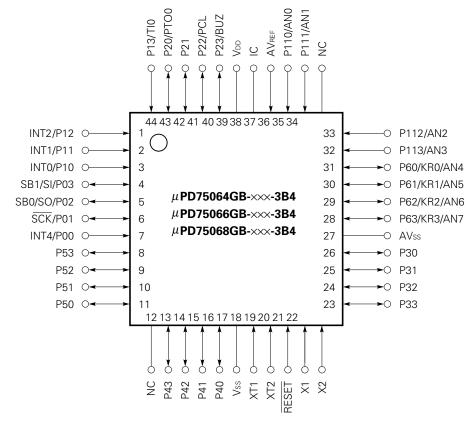

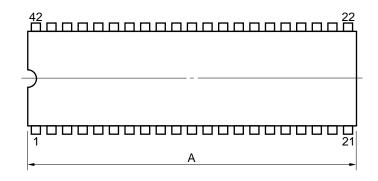

#### 1. PIN CONFIGURATION (TOP VIEW)

## · 42-pin plastic shrink DIP

## • 44-pin plastic QFP

IC : Internally Connected (This pin should be directly connected to VDD)

# PIN IDENTIFICATIONS

P00 - 03 : Port 0 P10 - 13 : Port 1 P20 - 23 : Port 2 P30 - 33 : Port 3 P40 - 43 : Port 4 P50 - 53 : Port 5 P60 - 63 : Port 6 P110 - 113: Port 11 KR0 - 3 : Key Return SCK : Serial Clock SI : Serial Input SO : Serial Output : Serial Bus 0, 1 SB0, 1 RESET : Reset Input TI0 : Timer Input 0

PTO0 : Programmable Timer Output 0

BUZ : Buzzer Clock

PCL : Programmable Clock

INTO, 1, 4: External Vectored Interrupt 0, 1, 4

INT2 : External Test Input 2

X1, 2 : Main System Clock Oscillation 1, 2XT1, 2 : Subsystem Clock Oscillation 1, 2

AN0 - 7 : Analog Input 0 - 7 AVREF : Analog Reference

AVss : Analog Vss

VDD : Positive Power Supply

Vss : Ground

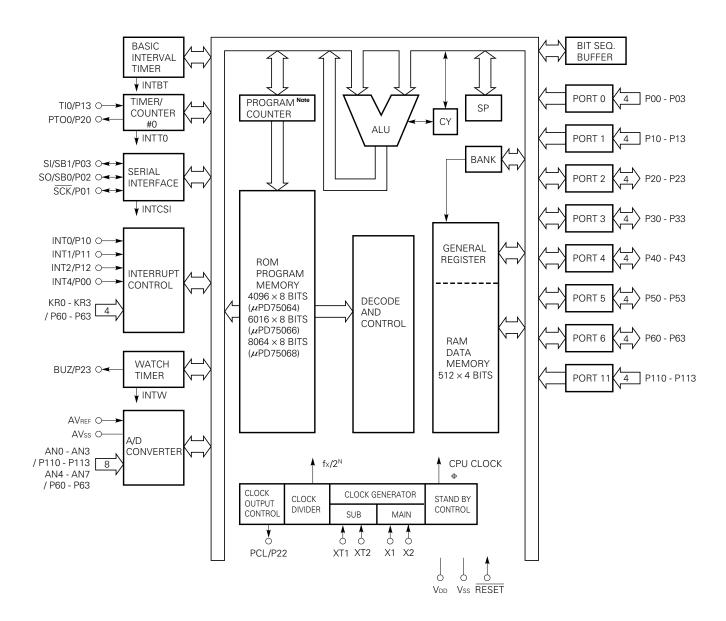

# 2. BLOCK DIAGRAM

**Note** The  $\mu$ PD75064 uses the program counter of a 12-bit configuration, the  $\mu$ PD75066 and  $\mu$ PD75068 use that of a 13-bit configuration.

# 3. PIN FUNCTIONS

# 3.1 Port Pins

| P00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin name        | Input/<br>output | Shared<br>with | Function                                                                                                                                                                                                                             |   | When reset                                              | I/O circuit<br>type <sup>Note 1</sup> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------|---------------------------------------|

| PO2   I/O   SO/SB0     PO3   I/O   SO/SB0     PO3   I/O   SV/SB1     P10   Input   INT0     P11   INT1   INT1     P12   P13     P20   P21   P21     P21   P22   P23     P33Note 2   P33Note 2   P33Note 2     P33Note 2   P40 - P43Note 2     P33Note 2   P60 - P53Note 2     P60   P60   P60   P60     P60   P60   P61     P66   P62   P62     P66   P63   P63     P66   P63   P63     P66   P63   P63     P110   P110     P110   P110     P110   P110     P110   P111     P111   P112     P110   P111     P111   P112     P110   P111     P111   P112     P111   P112     P111   P112     P112   P111     P112   P112     P110   P111     P111   P112     P110   P111     P111   P112     P110   P110   P110   P110     P110   P111   P112   P112     P110   P110   P110   P110   P110     P110   P111   P112   P112   P112     P110   P110   P110   P110   P110   P110     P110   P111   P112     | P00             | Input            | INT4           | 4-bit input port (PORT0).                                                                                                                                                                                                            |   | Input                                                   | B                                     |

| P02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P01             | I/O              | SCK            |                                                                                                                                                                                                                                      |   |                                                         | F-A                                   |

| P10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P02             | I/O              | SO/SB0         | provided by software in units of 3 bits.                                                                                                                                                                                             |   |                                                         | F-B                                   |

| P11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P03             | I/O              | SI/SB1         |                                                                                                                                                                                                                                      |   |                                                         | <b>M</b> -C                           |

| P12   P13   P14   P15   P16   P17   P17   P17   P17   P17   P18   P18   P19    | P10             | Input            | INT0           | With noise elimination function                                                                                                                                                                                                      | × | Input                                                   | B-C                                   |

| P20   P21   P22   PCL   PCL   BUZ   POgrammable 4-bit I/O port (PORT2).   P3Note 2   P3Note 2   P40 - P43Note 2   I/O   PCL   PCL   P3Note 2   P3O - P53Note 2   I/O   POSSNote 2   PSO - P53Note 2   I/O   POSSNote 2   PSO - P53Note 2   I/O   POSSNote 2   PSO - P63Note 2   I/O   POSSNote 2   I/O   P | P11             |                  | INT1           | 4-bit input port (PORT1).                                                                                                                                                                                                            |   |                                                         |                                       |

| P13   P20   P70   P70   P70   P10   P11    | P12             |                  | INT2           |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| P21   P22   PCL    | P13             |                  | TI0            | ware in units of 4 bits.                                                                                                                                                                                                             |   |                                                         |                                       |

| P21   P22   PCL   PCL   PCL   Ware in units of 4 bits.   PCL   P   | P20             | I/O              | PTO0           | 4-bit I/O port (PORT2).                                                                                                                                                                                                              | × | Input                                                   | E-B                                   |

| P30 Note 2 P33 Note 2 P33 Note 2 P40 - P43 Note 2 P50 - P53 Note 2 P50 - P53 Note 2 P60 P60 P61 P62 P63 P63 P63 P63 P63 P63 P66 P63 P66 P67 P67 P67 P67 P67 P67 P67 P67 P67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P21             |                  | -              | Pull-up resistors can be provided by soft-                                                                                                                                                                                           |   |                                                         |                                       |

| P30Note 2 P31Note 2 P32Note 2 P33Note 2 P33Note 2 P33Note 2 P33Note 2 P33Note 2 P33Note 2 P50 - P53Note 2 P60 P60 P60 P61 P61 P62 P63 P63 P63 P63 P63 P63 P63 P63 P63 P60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P22             |                  | PCL            | ware in units of 4 bits.                                                                                                                                                                                                             |   |                                                         |                                       |

| P31Note 2 P32Note 2 P33Note 2 P40 - P43Note 2 P50 - P53Note 2 P60 P60 P61 P62 P63 P63 P63 P110 Input PANOTE 2 P112 P112 Programmable 4-bit I/O port (PORT3). I/O can be specified bit by bit. Pull-up resistors can be provided by software in units of 4 bits.  Programmable 4-bit I/O port (PORT4). A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  P50 - P53Note 2 P60 P61 P62 P63 P63 P63 P63 P64 P67 P67 P67 P67 P67 P67 P67 P67 P68 P68 P69 P69 P69 P69 P69 P60 P60 P60 P60 P60 P61 P61 P61 P61 P62 P63 P63 P63 P63 P64 P65 P65 P65 P65 P65 P66 P67 P68 P68 P68 P68 P69 P69 P60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P23             |                  | BUZ            |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| P31Note 2   P32Note 2   P33Note 2   P33Note 2   P40 - P43Note 2   P40 - P43Note 2   P50 - P53Note 2   P60   P61   P62   P63   P63   P63   P63   P110   P112   P112   P112   P65   P110   P1112   P112   P65   P110   P111   P112   P65   P110   P111   P112   P65   P110   P111   P112   P65   P63   P63   P63   P65   P63   P65   P63   P65     | P30Note 2       | I/O              | _              | Programmable 4-bit I/O port (PORT3).                                                                                                                                                                                                 | × | Input                                                   | E-B                                   |

| P33Note 2 P40 - P43Note 2 P40 - P43Note 2 P50 - P53Note 2 P60 P60 P61 P62 P63 P110 P111 P112 P40 - P43Note 2 P110 P111 P112 P40 - P43Note 2 P50 - P53Note 2 P60 - P53Note 2 P50 - P53Note 2 P50 - P53Note 2 P50 - P53Note 2 P60 - P53Note 2 P6 | P31Note 2       |                  | -              | 1 .                                                                                                                                                                                                                                  |   |                                                         |                                       |

| P33Note 2  P40 - P43Note 2  P40 - P43Note 2  P50 - P53Note 2  P60 P60 P61 P62 P63 P63 P110 P110 P111 P112 P112 P3Note 2  P40 - P43Note 2 P50 - P43Note 2 P50 - P43Note 2 P50 - P53Note 2 P50 - | P32Note 2       |                  | -              |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  P50 - P53Note 2  I/O  P60  P61  P62  P63  P10  Input  AN0  AN1  AN1  AN1  AN2  A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain 4-bit I/O port (PORT5). A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  P60  KR0/AN4  KR1/AN5  KR2/AN6  KR3/AN7  AN0  AN1  AN1  AN2  A pull-up resistor can be provided for each bit I/O port (PORT5). A pull-up resistors are provided) or high impedance  Y-D  (when pull-up resistors are provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  Frogrammable 4-bit I/O port (PORT6). I/O can be specified bit by bit. Pull-up resistors can be provided by software in units of 4 bits.  X Input  Y-A  Input  Y-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P33Note 2       |                  | _              | units of 4 bits.                                                                                                                                                                                                                     |   |                                                         |                                       |

| A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  P60 I/O KR0/AN4 Programmable 4-bit I/O port (PORT6).   P61 KR1/AN5   KR2/AN6   KR2/AN6   KR3/AN7    P110 Input AN0 AN1 AN1 AN2    P112 A pull-up resistor can be provided for each bit (mask option). Breakdown voltage in up resistors are provided) or high impedance    V -D (when pull-up resistors are provided) or high impedance    X Input Y-D    Y-D (when pull-up resistors are provided) or high impedance    X Input Y-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P40 - P43Note 2 | I/O              | -              | A pull-up resistor can be provided for each bit (mask option). Breakdown voltage is 10 V in open-drain mode.  N-ch open-drain 4-bit I/O port (PORT5). A pull-up resistor can be provided for each bit (mask option). Breakdown volt- |   | (when pull-<br>up resistors<br>are provided)<br>or high | M                                     |

| Ped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P50 - P53Note 2 | I/O              | -              |                                                                                                                                                                                                                                      |   | (when pull-<br>up resistors<br>are provided)<br>or high | M                                     |

| P62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P60             | I/O              | KR0/AN4        | Programmable 4-bit I/O port (PORT6).                                                                                                                                                                                                 | × | Input                                                   | <b>(</b> Y)-D                         |

| P62         KR2/AN6         units of 4 bits.           P63         KR3/AN7         units of 4 bits.           P110         Input         AN0         4-bit input port (PORT11).         X         Input         Y-A           P111         AN1         AN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P61             |                  | KR1/AN5        |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| P63         KR3/AN7         ————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P62             | ]                | KR2/AN6        |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| P110 Input AN0 4-bit input port (POR111). Input Y-A P111 AN1 P112 AN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P63             |                  | KR3/AN7        | 2                                                                                                                                                                                                                                    |   |                                                         |                                       |

| P112 AN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P110            | Input            | AN0            | 4-bit input port (PORT11).                                                                                                                                                                                                           | × | Input                                                   | Y-A                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P111            | ]                | AN1            |                                                                                                                                                                                                                                      |   |                                                         |                                       |

| P113 AN3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P112            |                  | AN2            |                                                                                                                                                                                                                                      |   |                                                         |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P113            |                  | AN3            |                                                                                                                                                                                                                                      |   |                                                         |                                       |

Notes 1. The circle (  $\bigcirc$  ) indicates the Schmitt trigger input.

2. Can directly drive LEDs.

# 3.2 Non-Port Pins

| Pin name        | Input/<br>output | Shared<br>with          | Fund                                                                                                                                                                                                      | ction               |         | When reset | I/O circuit<br>type <sup>Note 1</sup> |

|-----------------|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------|---------------------------------------|

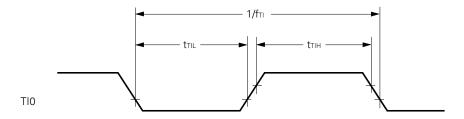

| TI0             | Input            | P13                     | Input for receiving extern                                                                                                                                                                                | nal event pulse sig | nal for | -          | B-C                                   |

| PTO0            | I/O              | P20                     | Timer/event counter out                                                                                                                                                                                   | tput                |         | Input      | E-B                                   |

| PCL             | I/O              | P22                     | Clock output                                                                                                                                                                                              |                     |         | Input      | E-B                                   |

| BUZ             | I/O              | P23                     | Output frequency select                                                                                                                                                                                   |                     | ng)     | Input      | E-B                                   |

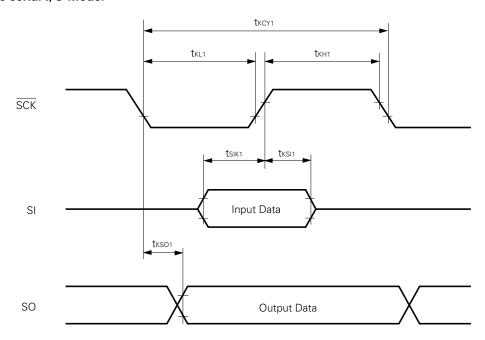

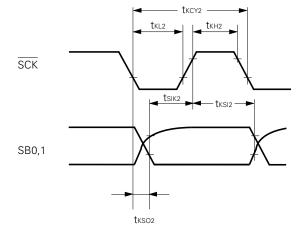

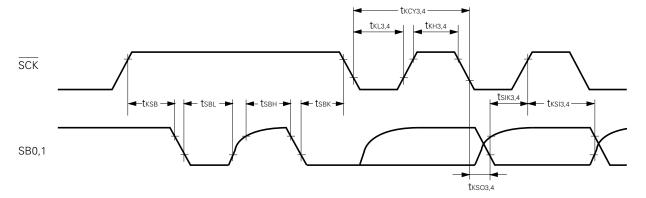

| SCK             | I/O              | P01                     | Serial clock I/O                                                                                                                                                                                          |                     |         | Input      | F-A                                   |

| SO/SB0          | I/O              | P02                     | Serial data output<br>Serial bus I/O                                                                                                                                                                      |                     |         | Input      | F-B                                   |

| SI/SB1          | I/O              | P03                     | Serial data input<br>Serial bus I/O                                                                                                                                                                       |                     |         | Input      | <b>M</b> -C                           |

| INT4            | Input            | P00                     | Edge-detective vectored (both rising and falling                                                                                                                                                          |                     |         | -          | B                                     |

| INT0            | Input            | P10                     | Edge-detective vectored                                                                                                                                                                                   | l interrupt input   | Note 2  | -          | B-C                                   |

| INT1            |                  | P11                     | (detection edge selectal                                                                                                                                                                                  | ole)                | Note 3  |            |                                       |

| INT2            | Input            | P12                     | Edge-detective testable (rising edge detection)                                                                                                                                                           | input               | Note 3  | -          | B-C                                   |

| KR0 - KR3       | I/O              | P60 - P63/<br>AN4 - AN7 | Parallel falling edge detection testable input                                                                                                                                                            |                     |         | Input      | Ý-D                                   |

| AN0 - AN3       | Input            | P110 - P113             | For A/D converter only                                                                                                                                                                                    | 8-bit analog inpu   | t       | Input      | Y-A                                   |

| AN4 - AN7       | I/O              | P60 - P63/<br>KR0 - KR3 |                                                                                                                                                                                                           |                     |         |            | <b>Ý</b> -D                           |

| AVREF           | Input            | -                       |                                                                                                                                                                                                           | Reference voltag    | e input | _          | Z                                     |

| AVss            | _                | _                       |                                                                                                                                                                                                           | GND potential       |         | _          | Z                                     |

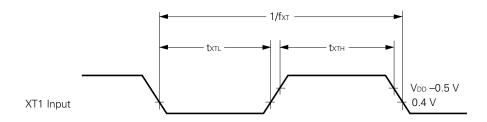

| X1, X2          | Input            | -                       | Crystal/ceramic connection for main system clock generation. When external clock signal is used, the signal should be applied to X1, and its reverse phase signal to X2.                                  |                     |         | -          | -                                     |

| XT1, XT2        | Input            | _                       | Crystal connection for subsystem clock generation. When external clock signal is used, the signal should be applied to XT1, and its reverse phase signal to XT2. XT1 can be used as a 1-bit input (test). |                     |         | -          | _                                     |

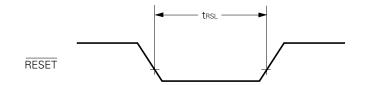

| RESET           | Input            | -                       | System reset input                                                                                                                                                                                        |                     |         | -          | B                                     |

| IC              | _                | -                       | Internally connected.                                                                                                                                                                                     |                     | -       | -          |                                       |

|                 |                  |                         | (Connect this pin directly to V <sub>DD</sub> )                                                                                                                                                           |                     |         |            |                                       |

| V <sub>DD</sub> | _                | _                       | Positive power supply                                                                                                                                                                                     |                     |         | -          | _                                     |

| Vss             | _                | _                       | GND potential                                                                                                                                                                                             |                     |         | -          | -                                     |

Notes 1. The circle (  $\bigcirc$  ) indicates the Schmitt trigger input.

- 2. Clock synchronous

- 3. Asynchronous

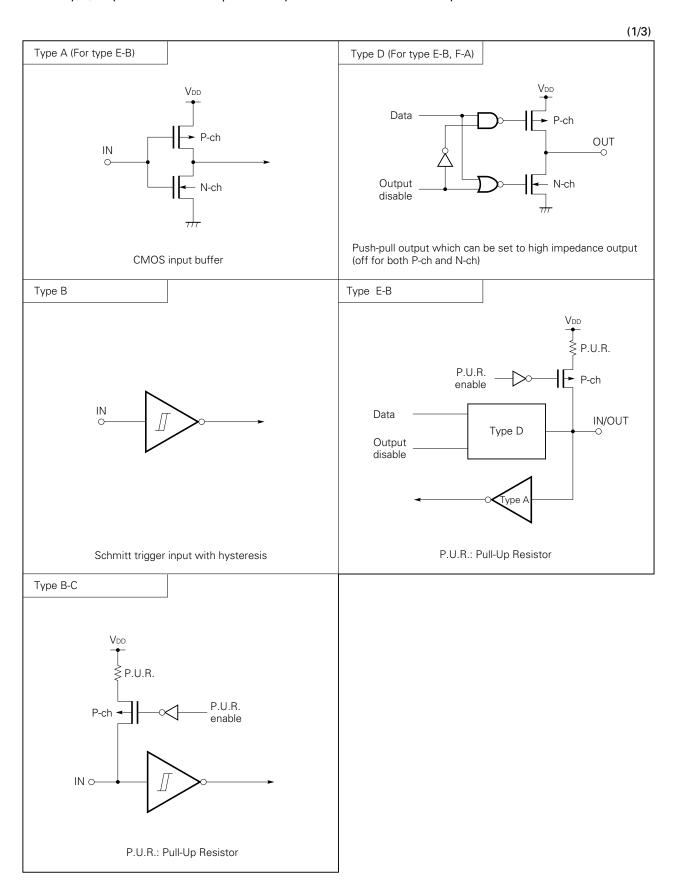

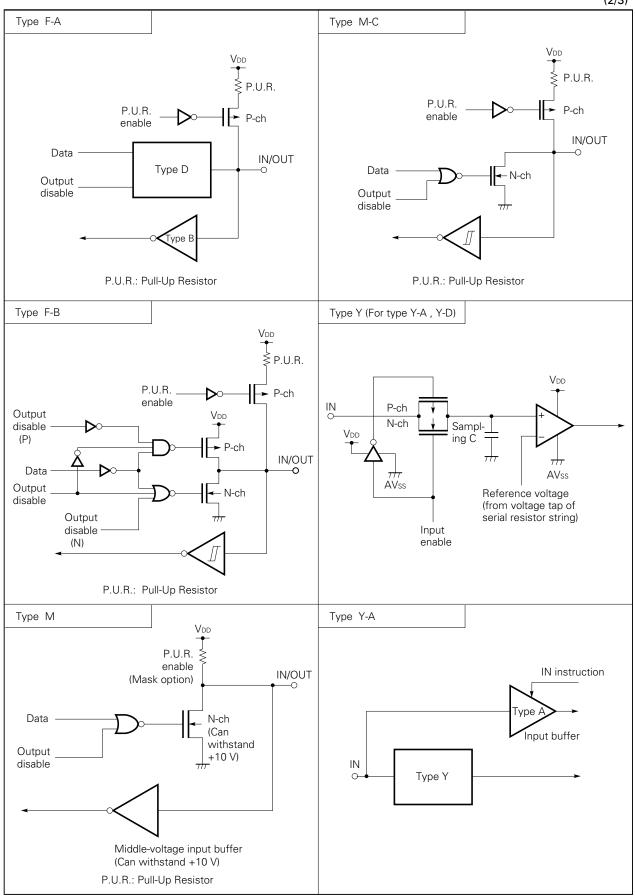

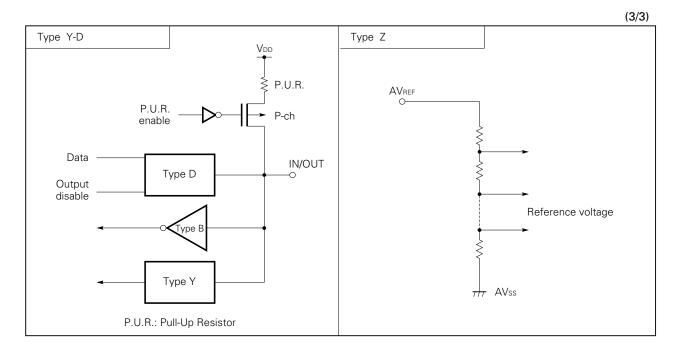

# 3.3 Pin Input/Output Circuits

The input/output circuit of each  $\mu$ PD75068 pin is shown below in a simplified manner.

(2/3)

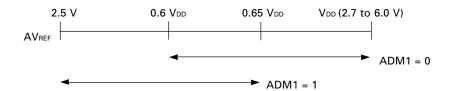

# 3.4 Mask Option Selection