## FAIRCHILD

SEMICONDUCTOR

## MM74HC04 Hex Inverter

#### **General Description**

The MM74HC04 inverters utilize advanced silicon-gate CMOS technology to achieve operating speeds similar to LS-TTL gates with the low power consumption of standard CMOS integrated circuits.

The MM74HC04 is a triple buffered inverter. It has high noise immunity and the ability to drive 10 LS-TTL loads. The 74HC logic family is functionally as well as pin-out compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to V<sub>CC</sub> and ground.

#### September 1983 Revised January 2005

#### Features

- Typical propagation delay: 8 ns

- Fan out of 10 LS-TTL loads

- Quiescent power consumption: 10 μW maximum at room temperature

- Low input current: 1 µA maximum

#### **Ordering Code:**

| Order Number   | Package<br>Number | Package Description                                                                    |  |  |  |  |

|----------------|-------------------|----------------------------------------------------------------------------------------|--|--|--|--|

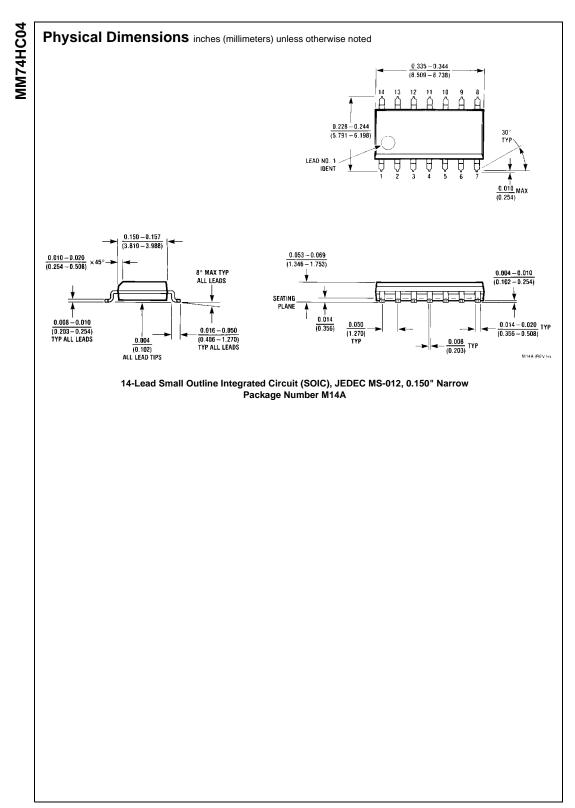

| MM74HC04M      | M14A              | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow           |  |  |  |  |

| MM74HC04M_NL   |                   | Pb-Free 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow   |  |  |  |  |

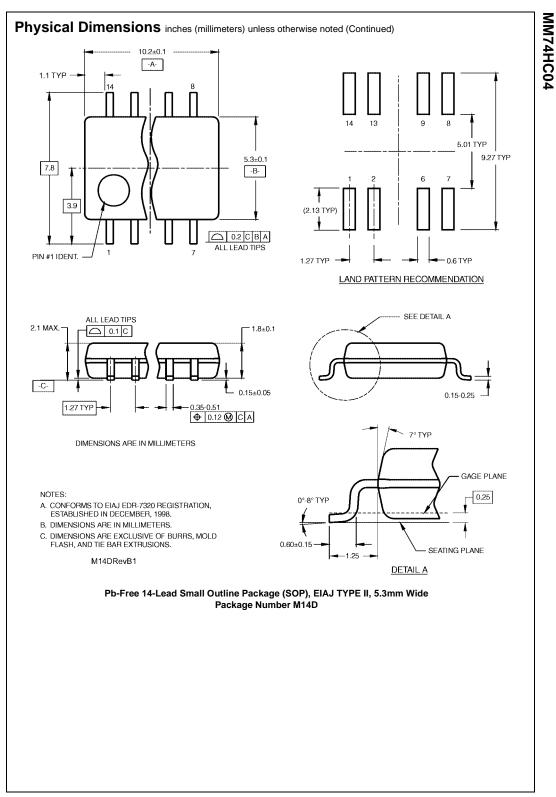

| MM74HC04SJ     | M14D              | Pb-Free 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide                  |  |  |  |  |

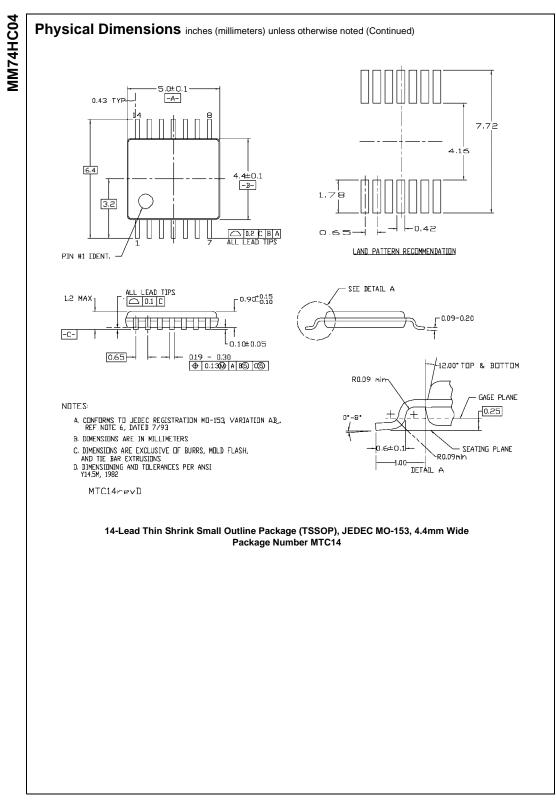

| MM74HC04MTC    | MTC14             | 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide            |  |  |  |  |

| MM74HC04MTC_NL | MTC14             | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm<br>Wide |  |  |  |  |

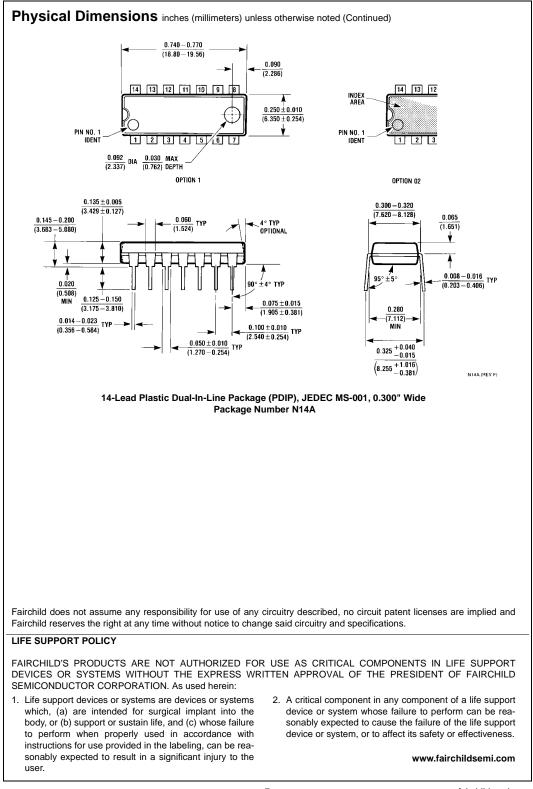

| MM74HC04N      | N14A              | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide                 |  |  |  |  |

| MM74HC04N_NL   | N14A              | Pb-Free 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide         |  |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

Pb-Free package per JEDEC J-STD-020B.

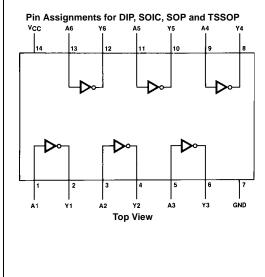

#### **Connection Diagram**

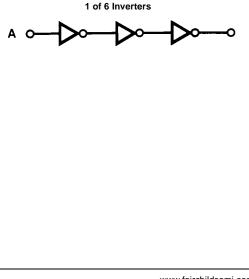

### Logic Diagram

© 2005 Fairchild Semiconductor Corporation DS005069

#### Absolute Maximum Ratings(Note 1) (Note 2)

| Supply Voltage (V <sub>CC</sub> )                        | -0.5 to +7.0V                 |

|----------------------------------------------------------|-------------------------------|

| DC Input Voltage (V <sub>IN</sub> )                      | –1.5 to V <sub>CC</sub> +1.5V |

| DC Output Voltage (V <sub>OUT</sub> )                    | –0.5 to $V_{CC}$ +0.5V        |

| Clamp Diode Current (I <sub>IK</sub> , I <sub>OK</sub> ) | ±20 mA                        |

| DC Output Current, per pin (I <sub>OUT</sub> )           | ±25 mA                        |

| DC $V_{CC}$ or GND Current, per pin (I_{CC})             | ±50 mA                        |

| Storage Temperature Range (T <sub>STG</sub> )            | -65°C to +150°C               |

| Power Dissipation (P <sub>D</sub> )                      |                               |

| (Note 3)                                                 | 600 mW                        |

| S.O. Package only                                        | 500 mW                        |

| Lead Temperature (T <sub>L</sub> )                       |                               |

| (Soldering 10 seconds)                                   | 260°C                         |

|                                                          |                               |

# Recommended Operating Conditions

|                                               | Min | Max      | Units |  |

|-----------------------------------------------|-----|----------|-------|--|

| Supply Voltage (V <sub>CC</sub> )             | 2   | 6        | V     |  |

| DC Input or Output Voltage                    | 0   | $V_{CC}$ | V     |  |

| (V <sub>IN</sub> , V <sub>OUT</sub> )         |     |          |       |  |

| Operating Temperature Range (T <sub>A</sub> ) | -40 | +85      | °C    |  |

| Input Rise or Fall Times                      |     |          |       |  |

| $(t_r, t_f) V_{CC} = 2.0V$                    |     | 1000     | ns    |  |

| $V_{CC} = 4.5V$                               |     | 500      | ns    |  |

| $V_{CC} = 6.0V$                               |     | 400      | ns    |  |

|                                               |     |          |       |  |

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground. Note 3: Power Dissipation temperature derating — plastic "N" package: – 12 mW/°C from 65°C to 85°C.

#### DC Electrical Characteristics (Note 4)

| Symbol          | Parameter          | Conditions                     | Vcc  | $T_A = 25^{\circ}C$ |      | $T_A{=}{-}40$ to $85^\circ C$ | $T_A=-55$ to $125^\circ C$ | Units |

|-----------------|--------------------|--------------------------------|------|---------------------|------|-------------------------------|----------------------------|-------|

| Symbol          |                    |                                | *cc  | Тур                 |      | Guaranteed L                  | imits                      | Units |

| VIH             | Minimum HIGH Level |                                | 2.0V |                     | 1.5  | 1.5                           | 1.5                        | V     |

|                 | Input Voltage      |                                | 4.5V |                     | 3.15 | 3.15                          | 3.15                       | V     |

|                 |                    |                                | 6.0V |                     | 4.2  | 4.2                           | 4.2                        | V     |

| VIL             | Maximum LOW Level  |                                | 2.0V |                     | 0.5  | 0.5                           | 0.5                        | V     |

|                 | Input Voltage      |                                | 4.5V |                     | 1.35 | 1.35                          | 1.35                       | V     |

|                 |                    |                                | 6.0V |                     | 1.8  | 1.8                           | 1.8                        | V     |

| V <sub>OH</sub> | Minimum HIGH Level | $V_{IN} = V_{IL}$              |      |                     |      |                               |                            |       |

|                 | Output Voltage     | I <sub>OUT</sub>   ≤ 20 μA     | 2.0V | 2.0                 | 1.9  | 1.9                           | 1.9                        | V     |

|                 |                    |                                | 4.5V | 4.5                 | 4.4  | 4.4                           | 4.4                        | V     |

|                 |                    |                                | 6.0V | 6.0                 | 5.9  | 5.9                           | 5.9                        | V     |

|                 |                    | $V_{IN} = V_{IL}$              |      |                     |      |                               |                            |       |

|                 |                    | I <sub>OUT</sub>   ≤ 4.0 mA    | 4.5V | 4.2                 | 3.98 | 3.84                          | 3.7                        | V     |

|                 |                    | I <sub>OUT</sub>   ≤ 5.2 mA    | 6.0V | 5.7                 | 5.48 | 5.34                          | 5.2                        | V     |

| V <sub>OL</sub> | Maximum LOW Level  | $V_{IN} = V_{IH}$              |      |                     |      |                               |                            |       |

|                 | Output Voltage     | I <sub>OUT</sub>   ≤ 20 μA     | 2.0V | 0                   | 0.1  | 0.1                           | 0.1                        | V     |

|                 |                    |                                | 4.5V | 0                   | 0.1  | 0.1                           | 0.1                        | V     |

|                 |                    |                                | 6.0V | 0                   | 0.1  | 0.1                           | 0.1                        | V     |

|                 |                    | $V_{IN} = V_{IH}$              |      |                     |      |                               |                            |       |

|                 |                    | $ I_{OUT}  \le 4.0 \text{ mA}$ | 4.5V | 0.2                 | 0.26 | 0.33                          | 0.4                        | V     |

|                 |                    | $ I_{OUT}  \le 5.2 \text{ mA}$ | 6.0V | 0.2                 | 0.26 | 0.33                          | 0.4                        | V     |

| I <sub>IN</sub> | Maximum Input      | $V_{IN} = V_{CC}$ or GND       | 6.0V |                     | ±0.1 | ±1.0                          | ±1.0                       | μA    |

|                 | Current            |                                |      |                     |      |                               |                            |       |

| I <sub>CC</sub> | Maximum Quiescent  | $V_{IN} = V_{CC}$ or GND       | 6.0V |                     | 2.0  | 20                            | 40                         | μA    |

|                 | Supply Current     | $I_{OUT} = 0 \ \mu A$          |      |                     |      |                               |                            |       |

Note 4: For a power supply of 5V  $\pm 10^{\circ}$  the worst case output voltages (V<sub>OH</sub>, and V<sub>OL</sub>) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case V<sub>IH</sub> and V<sub>IL</sub> occur at V<sub>CC</sub>=5.5V and 4.5V respectively. (The V<sub>IH</sub> value at 5.5V is 3.85V.) The worst case leakage current (I<sub>IN</sub>, I<sub>CC</sub>, and I<sub>O2</sub>) occur for CMOS at the higher voltage and so the 6.0V values should be used.

| Guaranteed<br>Limit | Units |

|---------------------|-------|

| 15                  | ns    |

|                     |       |

$V_{CC} = 2.0V$  to 6.0V,  $C_L = 50$  pF,  $t_r = t_f = 6$  ns (unless otherwise specified)

| Symbol                              | Parameter            | Conditions | v <sub>cc</sub> | $T_A = 25^{\circ}C$ |    | $T_A = -40$ to $85^\circ C$ | $T_A=-55$ to $125^\circ C$ | Units |

|-------------------------------------|----------------------|------------|-----------------|---------------------|----|-----------------------------|----------------------------|-------|

| Symbol                              | Falameter            |            |                 | Тур                 |    | Guaranteed Limits           |                            |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation  |            | 2.0V            | 55                  | 95 | 120                         | 145                        | ns    |

|                                     | Delay                |            | 4.5V            | 11                  | 19 | 24                          | 29                         | ns    |

|                                     |                      |            | 6.0V            | 9                   | 16 | 20                          | 24                         | ns    |

| t <sub>TLH</sub> , t <sub>THL</sub> | Maximum Output Rise  |            | 2.0V            | 30                  | 75 | 95                          | 110                        | ns    |

|                                     | and Fall Time        |            | 4.5V            | 8                   | 15 | 19                          | 22                         | ns    |

|                                     |                      |            | 6.0V            | 7                   | 13 | 16                          | 19                         | ns    |

| C <sub>PD</sub>                     | Power Dissipation    | (per gate) |                 | 20                  |    |                             |                            | pF    |

|                                     | Capacitance (Note 5) |            |                 |                     |    |                             |                            |       |

| CIN                                 | Maximum Input        |            |                 | 5                   | 10 | 10                          | 10                         | pF    |

|                                     | Capacitance          |            |                 |                     |    |                             |                            |       |

Note 5:  $C_{PD}$  determines the no load dynamic power consumption,  $P_D = C_{PD} V_{CC}^2 f + I_{CC} V_{CC}$ , and the no load dynamic current consumption,  $I_S = C_{PD} V_{CC} f + I_{CC}$ .

MM74HC04 Hex Inverter