National Semiconductor June 2004

135MHz

100MHz

#### LMH6503

## Wideband, Low Power, Linear Variable Gain Amplifier

#### **General Description**

The LMH™6503 is a wideband DC coupled differential input voltage controlled gain stage followed by a high-speed current feedback Op Amp which can directly drive a low impedance load. Gain adjustment range is more than 70dB for up to 10MHz.

Maximum gain is set by external components and the gain can be reduced all the way to cut-off. Power consumption is 370mW with a speed of 135MHz. Output referred DC offset voltage is less than 350mV over the entire gain control voltage range. Device-to-device Gain matching is within 0.7dB at maximum gain. Furthermore, gain at any  $V_{\rm G}$  is tested and the tolerance is guaranteed. The output current feedback Op Amp allows high frequency large signals (Slew Rate =  $1800V/\mu s$ ) and can also drive heavy load current (75mA). Differential inputs allow common mode rejection in low level amplification or in applications where signals are carried over relatively long wires. For single ended operation, the unused input can easily be tied to ground (or to a virtual half-supply in single supply application). Inverting or non-inverting gains could be obtained by choosing one input polarity or the other.

To further increase versatility when used in a single supply application, gain control range is set to be from -1V to +1V relative to pin 11 potential (ground pin). In single supply operation, this ground pin is tied to a "virtual" half supply. Gain control pin has high input impedance to simplify its drive requirement. Gain control is linear in V/V throughout the gain adjustment range. Maximum gain can be set to be anywhere between 1V/V to 100V/V or higher. For linear in dB gain control applications, see LMH6502 datasheet.

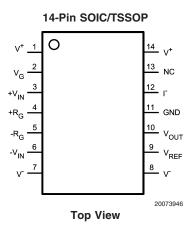

The LMH6503 is available in the SOIC-14 and TSSOP-14 package.

#### **Features**

■ -3dB BW

Gain control BW

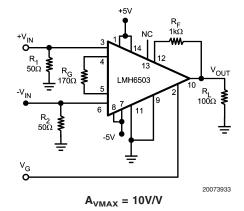

$V_S=\pm5V$ ,  $T_A=25^{\circ}C$ ,  $R_F=1k\Omega$ ,  $R_G=174\Omega$ ,  $R_L=100\Omega$ ,  $A_V=A_{V(MAX)}=10$ , Typical values unless specified.

| <ul><li>Adjustment range (typical over temp)</li></ul> | 70dB       |

|--------------------------------------------------------|------------|

| ■ Gain matching (limit)                                | ±0.7dB     |

| ■ Slew rate                                            | 1800V/μs   |

| ■ Supply current (no load)                             | 37mA       |

| ■ Linear output current                                | ±75mA      |

| ■ Output voltage (R <sub>L</sub> = 100Ω)               | ±3.2V      |

| ■ Input voltage noise                                  | 6.6nV/ √Hz |

| ■ Input current noise                                  | 2.4pA/ √Hz |

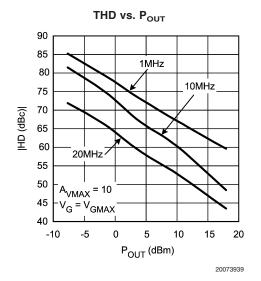

| ■ THD (20MHz, $R_L = 100\Omega$ , $V_O = 2V_{PP}$ )    | -57dBc     |

■ Replacement for CLC522

#### **Applications**

- Variable attenuator

- AGC

- Voltage controller filter

- Multiplier

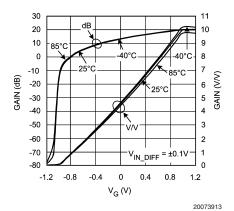

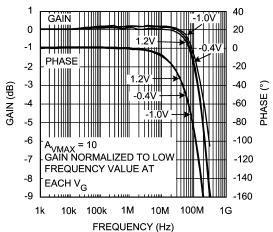

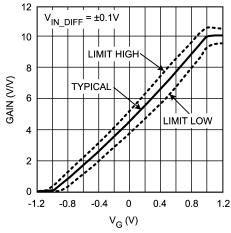

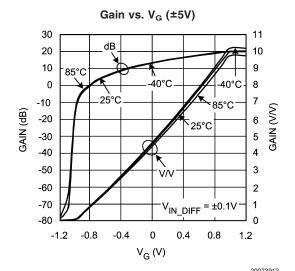

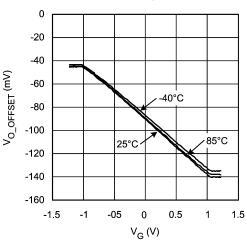

#### Gain vs. V<sub>G</sub> for Various Temperature

### **Typical Application**

LMH™ is a trademark of National Semiconductor Corporation

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance: (Note 4)

Human Body2KVMachine Model200VInput Current $\pm 10mA$  $V_{IN}$  Differential $\pm (V^+ - V^-)$ Output Current120mA (Note 3)Supply Voltages  $(V^+ - V^-)$ 12.6VVoltage at Input/ Output pins $V^+ + 0.8V, V^- - 0.8V$

Soldering Information:

Infrared or Convection (20 sec)  $235^{\circ}$ C Wave Soldering (10 sec)  $260^{\circ}$ C Storage Temperature Range  $-65^{\circ}$ C to  $+150^{\circ}$ C Junction Temperature  $+150^{\circ}$ C

#### **Operating Ratings** (Note 1)

Supply Voltages (V $^+$  - V $^-$ ) 5V to 12V Temperature Range  $-40^{\circ}$ C to  $+85^{\circ}$ C

Thermal Resistance:  $\theta_{JA}$   $\theta_{JC}$  14-Pin SOIC 138°C/W 45°C/W 14-Pin TSSOP 160°C/W 51°C/W

#### **Electrical Characteristics**(Note 2)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_S = \pm 5V$ ,  $A_{V(MAX)} = 10$ ,  $V_{CM} = 0V$ ,  $R_F = 1k\Omega$ ,  $R_G = 174\Omega$ ,  $V_{IN-DIFF} = \pm 0.1V$ ,  $R_L = 100\Omega$ ,  $V_G = +1V$ . **Boldface** limits apply at the temperature extremes.

|                |                                     |                                          | Min      | Тур      | Max      |         |  |

|----------------|-------------------------------------|------------------------------------------|----------|----------|----------|---------|--|

| Symbol         | Parameter                           | Conditions                               | (Note 6) | (Note 6) | (Note 6) | Units   |  |

| Frequency      | Domain Response                     |                                          |          |          |          |         |  |

| BW             | -3dB Bandwidth                      | $V_{OUT} < 0.5_{PP}$                     |          | 135      |          | MHz     |  |

|                |                                     | $V_{OUT} < 0.5_{PP}, A_{V(MAX)} = 100$   |          | 50       |          |         |  |

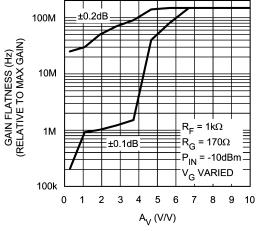

| GF             | Gain Flatness                       | $V_{OUT} < 0.5V_{PP}$                    |          | 40       |          | MHz     |  |

|                |                                     | $-1V < V_G < 1V, \pm 0.2dB$              |          |          |          |         |  |

| Att Range      | Flat Band (Relative to Max Gain)    | ±0.2dB Flatness, f < 30MHZ               |          | 20       |          | MHz     |  |

|                | Attenuation Range (Note 13)         | ±0.1dB, f < 30MHZ                        |          | 6.6      |          | IVITIZ  |  |

| BW             | Gain Control Bandwidth              | V <sub>G</sub> = 0V (Note 11)            |          | 100      |          | MHz     |  |

| Control        |                                     |                                          |          |          |          |         |  |

| PL             | Linear Phase Deviation              | DC to 60MHz                              |          | 1.6      |          | deg     |  |

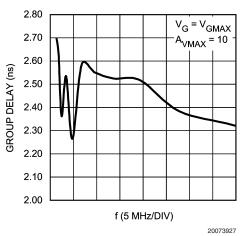

| G Delay        | Group Delay                         | DC to 130MHz                             |          | 2.6      |          | ns      |  |

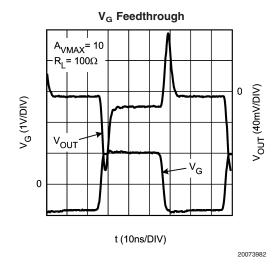

| CT (dB)        | Feed-through                        | $V_G = -1.2V$ , 30MHz (Output            |          | -48      |          | dB      |  |

|                |                                     | Referred)                                |          |          |          |         |  |

| GR             | Gain Adjustment Range               | f < 10MHz                                |          | 79       |          | dB      |  |

|                |                                     | f < 30MHz                                |          | 68       |          | ub      |  |

| Time Dom       | ain Response                        |                                          |          |          |          |         |  |

| $t_r$ , $t_f$  | Rise and Fall Time                  | 0.5V Step                                |          | 2.2      |          | ns      |  |

| OS%            | Overshoot                           | 0.5V Step                                |          | 10       |          | %       |  |

| SR             | Slew Rate                           | 4V Step (Note 5)                         |          | 1800     |          | V/µs    |  |

| ∆G Rate        | Gain Change Rate                    | $V_{IN} = 0.3V$ , 10%–90% of final       |          | 4.6      |          | dB/ns   |  |

|                |                                     | output                                   |          |          |          |         |  |

| Distortion     | & Noise performance                 |                                          |          |          |          |         |  |

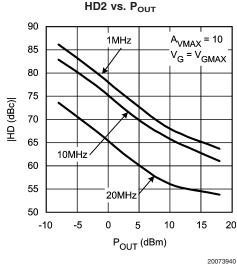

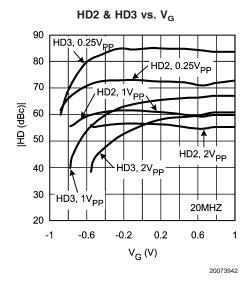

| HD2            | 2 <sup>nd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 20MHz                 |          | -60      |          | dBc     |  |

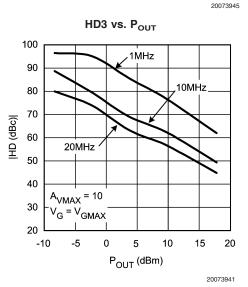

| HD3            | 3 <sup>rd</sup> Harmonic Distortion | 2V <sub>PP</sub> , 20MHz                 |          | -61      |          | dBc     |  |

| THD            | Total Harmonic Distortion           | 2V <sub>PP</sub> , 20MHz                 |          | -57      |          | dBc     |  |

| En tot         | Total Equivalent Input Noise        | 1MHz to 150MHz                           |          | 6.6      |          | nV/ √Hz |  |

| I <sub>n</sub> | Input Noise Current                 | 1MHz to 150MHz                           |          | 2.4      |          | pA/ √Hz |  |

| DG             | Differential Gain                   | $f = 4.43MHz$ , $R_L = 150\Omega$ , Neg. |          | 0.15     |          | %       |  |

|                |                                     | Sync                                     |          |          |          |         |  |

| DP             | Differential Phase                  | $f = 4.43MHz$ , $R_L = 150\Omega$ , Neg. |          | 0.22     |          | deg     |  |

|                |                                     | Sync                                     |          |          |          |         |  |

| Symbol              | Parameter                                     | Conditions                                            | Min<br>(Note 6) | Typ<br>(Note 6) | Max<br>(Note 6)   | Units    |

|---------------------|-----------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-------------------|----------|

| DC & Miso           | cellaneous Performance                        | •                                                     |                 | •               |                   |          |

| GACCU               | Gain Accuracy (see Application                | V <sub>G</sub> =1.0V                                  |                 | +0.25           | +0.9/-0.4         |          |

|                     | Notes)                                        | 0V < V <sub>G</sub> < 1V                              |                 | ±0.3            | +1.3/–1.5         | dB       |

|                     |                                               | $-0.7V < V_G < 1V$                                    |                 | ±0.4            | +4.4/-4.3         |          |

| G Match             | Gain Matching (see Application                | V <sub>G</sub> = 1.0                                  |                 | -               | ±0.7              |          |

|                     | Notes)                                        | 0 < V <sub>G</sub> < 1V                               |                 | _               | +1.7/–1.1         | dB       |

|                     |                                               | $-0.7V < V_G < 1V$                                    |                 | -               | +4.0/-4.7         |          |

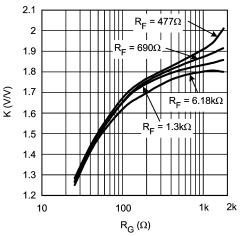

| K                   | Gain Multiplier (see Application              |                                                       | 1.58            | 1.72            | 1.87              | \//\/    |

|                     | Notes)                                        |                                                       | 1.58            |                 | 1.91              | V/V      |

| V <sub>CM</sub>     | Input Voltage Range                           | Pin 3 & 6 Common Mode,                                | ±2.0            | ±2.2            |                   | V        |

|                     |                                               | ICMRRI > 50dB (Note 9)                                | ±1.80           |                 |                   |          |

| $V_{IN\_DIFF}$      | Differential Input Voltage                    | Across pins 3 & 6                                     | ±0.34           | ±0.37           |                   | V        |

|                     |                                               |                                                       | ±0.28           |                 |                   | · ·      |

| $I_{RG\;MAX}$       | R <sub>G</sub> Current                        | Pins 4 & 5                                            | ±1.70           | ±2.30           |                   | mA       |

|                     |                                               |                                                       | ±1.60           |                 |                   |          |

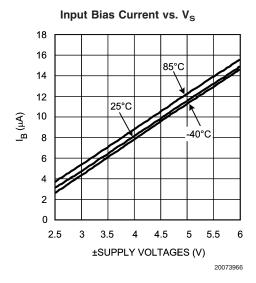

| I <sub>BIAS</sub>   | Bias Current                                  | Pins 3 & 6 (Note 7)                                   |                 | 11              | 18                |          |

|                     |                                               |                                                       |                 |                 | 20                | μΑ       |

|                     |                                               | Pins 3 & 6 (Note 7),                                  |                 | 3               | 10                | <b>I</b> |

|                     |                                               | V <sub>S</sub> = ±2.5V                                |                 |                 | 13                |          |

| TC <sub>BIAS</sub>  | Bias Current Drift                            | Pin 3 & 6 (Note 8)                                    |                 | 100             |                   | nA/°C    |

| OFF                 | Offset Current                                | Pin 3 & 6                                             |                 | 0.01            | 2.0<br><b>2.5</b> | μΑ       |

| TC I <sub>OFF</sub> | Offset Current Drift                          | (Note 8)                                              |                 | 5               |                   | nA/°C    |

| R <sub>IN</sub>     | Input Resistance                              | Pin 3 & 6                                             |                 | 750             |                   | kΩ       |

| C <sub>IN</sub>     | Input Capacitance                             | Pin 3 & 6                                             |                 | 5               |                   | pF       |

| V <sub>G</sub>      | V <sub>G</sub> Bias Current                   | Pin 2, V <sub>G</sub> = 1.4V(Note 7)                  |                 | 45              |                   | μΑ       |

| TC IV <sub>G</sub>  | V <sub>G</sub> Bias Drift                     | Pin 2 (Note 8)                                        |                 | 20              |                   | nA/°C    |

| R V <sub>G</sub>    | V <sub>G</sub> Input Resistance               | Pin 2                                                 |                 | 70              |                   | ΚΩ       |

| C V <sub>G</sub>    | V <sub>G</sub> Input Capacitance              | Pin 2                                                 |                 | 1.3             |                   | pF       |

| V <sub>OUT</sub>    | Output Voltage Range                          | $R_L = 100\Omega$                                     | ±3.00<br>±2.97  | ±3.20           |                   |          |

|                     |                                               | R <sub>L</sub> Open                                   | ±3.95<br>±3.90  | ±4.05           |                   | V        |

| R <sub>OUT</sub>    | Output Impedance                              | DC                                                    |                 | 0.1             |                   | Ω        |

| I <sub>OUT</sub>    | Output Current                                | V <sub>OUT</sub> ±4V from Rails                       | ±75             | ±90             |                   | mA       |

| 001                 | ,                                             | 001                                                   | ±70             |                 |                   |          |

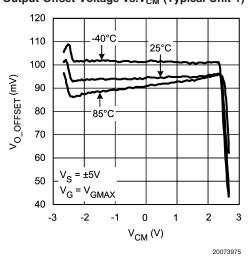

| V <sub>O</sub>      | Output Offset Voltage                         | -1V < V <sub>G</sub> < 1V                             |                 | ±80             | ±350<br>±380      | mV       |

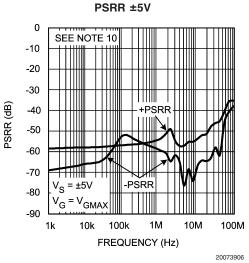

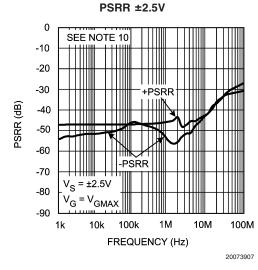

| +PSRR               | +Power Supply Rejection Ratio                 | Input Referred, 1V change,                            |                 | -80             | -58               | dB       |

| DCDD                | (see (Note 10))                               | V <sub>G</sub> = 1.4V                                 |                 | 07              | -56<br>57         | 40       |

| -PSRR               | -Power Supply Rejection Ratio (see (Note 10)) | Input Referred, 1V change, V <sub>G</sub> = 1.4V      |                 | -67             | −57<br><b>−51</b> | dB       |

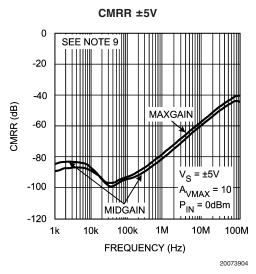

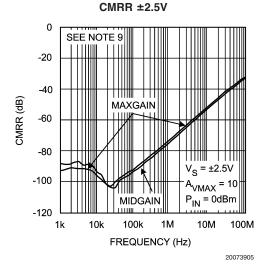

| CMRR                | Common Mode Rejection Ratio (see (Note 9))    | Input Referred, $V_G = 1V$<br>-1.8V < $V_{CM} < 1.8V$ |                 | -67             |                   | dB       |

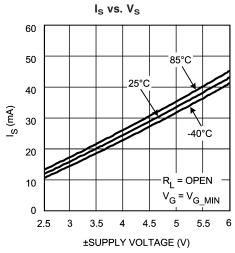

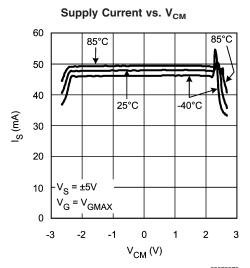

| s                   | Supply Current                                | R <sub>L</sub> = Open                                 |                 | 37              | 50<br><b>53</b>   |          |

|                     |                                               | $R_L$ = Open, $V_S$ = ±2.5V                           |                 | 12              | 20<br><b>23</b>   | mA       |

#### Electrical Characteristics(Note 2) (Continued)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

**Note 2:** Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_{i,l} = T_{A}$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_{i,l} > T_{A}$ .

Note 3: The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations or value specified, whichever is lower.

Note 4: Human body model:  $1.5k\Omega$  in series with 100pF. Machine model:  $0\Omega$  in series with 200pF.

Note 5: Slew Rate is the average of the rising and falling rates.

Note 6: Typical values represent the most likely parametric norm. Bold numbers refer to over temperature limits.

Note 7: Positive current correspondes to current flowing in the device.

Note 8: Drift determined by dividing the change in parameter distribution at temperature extremes by the total temperature change.

Note 9: CMRR definition:  $[I\Delta V_{OUT}/\Delta V_{CM}|/A_V]$  with 0.1V differential input voltage.  $\Delta V_{OUT}$  is the change in output voltage with offset shift subtracted out.

Note 10: +PSRR definition: [ $|\Delta V_{OUT}/\Delta V^+|/A_V$ ], -PSRR definition: [ $|\Delta V_{OUT}/\Delta V^-|/A_V$ ] with 0.1V differential input voltage.  $\Delta V_{OUT}$  is the change in output voltage with offset shift subtracted out.

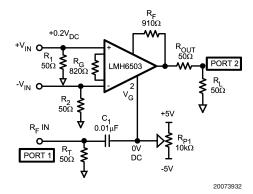

Note 11: Gain Control Frequency Response Schematic:

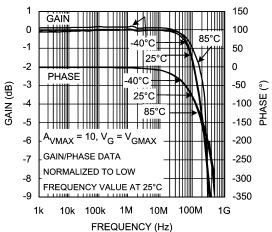

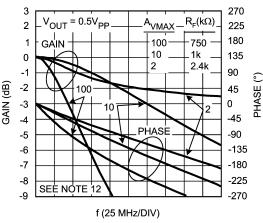

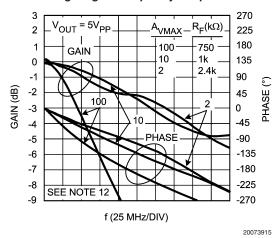

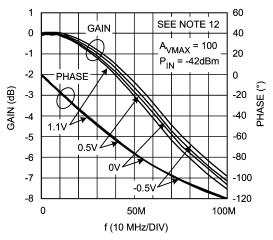

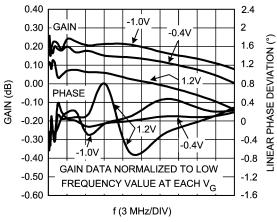

Note 12: Gain/Phase normalized to low frequency value at each  $A_V$ .

Note 13: Flat Band Attenuation (Relative To Max Gain) Range Definition: Specified as the attenuation range from maximum which allows gain flatness specified (either ±0.2dB or ±0.1dB), relative to A<sub>VMAX</sub> gain. For example, for f<30MHz, here are the Flat Band Attenuation ranges:

$\pm 0.2$ dB: 10V/V down to 1V/V=20dB range  $\pm 0.1$ dB: 10V/V down to 4.7V/V=6.5dB range

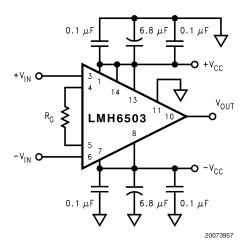

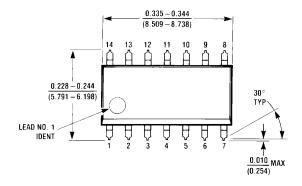

### **Connection Diagram**

### **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media          | NSC Drawing |  |

|--------------|-------------|-----------------|--------------------------|-------------|--|

| 14-pin SOIC  | LMH6503MA   | LMH6503MA       | 55 Units/Rail            | M14A        |  |

|              | LMH6503MAX  |                 | 2.5k Units Tape and Reel |             |  |

| LMH6503MT    |             | LMH6503MT       | 94 Units/Rail            | MTC14       |  |

| 14-Pin TSSOP | LMH6503MTX  | LIVIHOSUSIVI I  | 2.5k Units Tape and Reel | WITC14      |  |

#

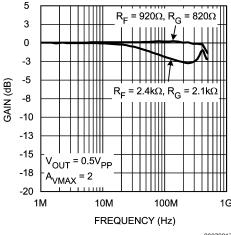

#### Small Signal Frequency Response $(A_V = 2)$

#### Frequency Response over Temperature ( $A_V = 10$ )

20073919

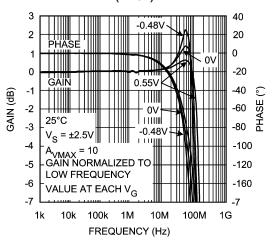

#### Frequency Response for Various $V_G$ (A<sub>VMAX</sub> = 10) $(\pm 2.5V)$

20073930

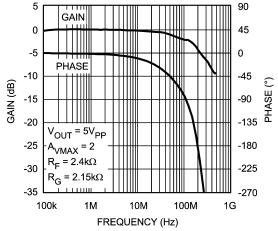

#### Large Signal Frequency Response $(A_V = 2)$

20073916

#### Frequency Response for Various $V_G$ (A<sub>VMAX</sub> = 10)

20073920

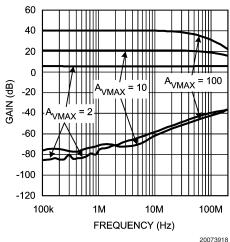

#### **Small Signal Frequency Response**

20073914

#### Large Signal Frequency Response

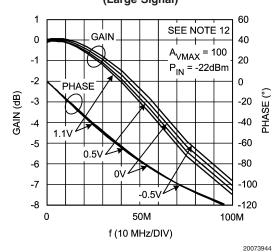

# Frequency Response for Various $V_G$ (A<sub>VMAX</sub> = 100) (Large Signal)

$I_{\text{S}}$  vs.  $V_{\text{S}}$ 60 85°C 50 25°C 40 -40°C I<sub>S</sub> (mA) 30 20 R<sub>L</sub> = OPEN 10  $V_G = V_{G\_MAX}$ 0 2.5 3 3.5 4 4.5 5 5.5 ±SUPPLY VOLTAGE (V)

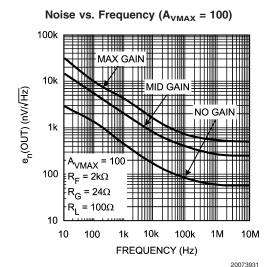

## Frequency Response for Various $V_G$ (A<sub>VMAX</sub> = 100) (Small Signal)

20073943

#### **Gain Control Frequency Response**

2007396

20073971

28

26

20073972

24 22  $I_{S}$  (mA) 20 18 16 14 V<sub>S</sub> = ±2.5V 12  $V_G = V_{GMAX}$ 10 -1.5 -1 -0.5 0 0.5 1.5

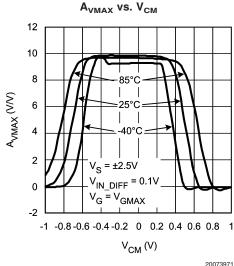

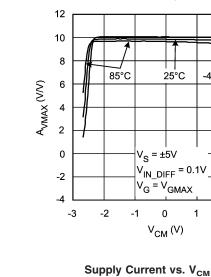

$\mathbf{A}_{\mathrm{VMAX}}$  vs.  $\mathbf{V}_{\mathrm{CM}}$

25°C

$V_S = \pm 5V$

V<sub>IN\_DIFF</sub> = 0.1V

$V_{CM}(V)$

-40°C

85°C

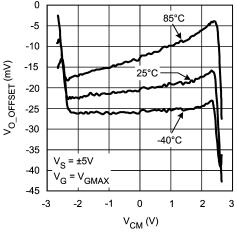

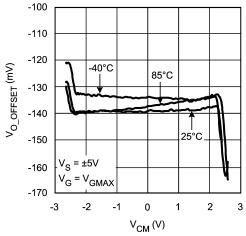

Output Offset Voltage vs.V<sub>CM</sub> (Typical Unit 1)

Output Offset Voltage vs.V<sub>CM</sub> (Typical Unit 2)

$V_{CM}(V)$

20073976

20073974

#### Output Offset Voltage vs.V<sub>CM</sub> (Typical Unit 3)

20073977

#### **Gain Flatness and Linear Phase Deviation**

20073921

#### Group Delay vs. Frequency

Feed through Isolation

#### Gain Flatness Frequency vs. Gain (Note 13)

20073924

#### K Factor vs. R<sub>G</sub>

20073901

20073912

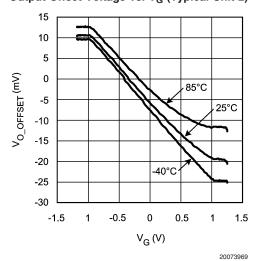

Output Offset Voltage vs. V<sub>G</sub> (Typical Unit 2)

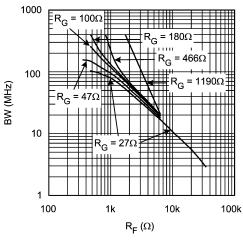

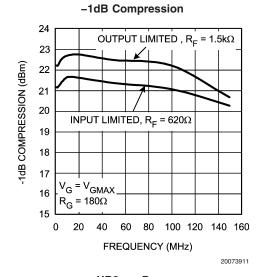

BW vs. R<sub>F</sub> for Various R<sub>G</sub>

20073903

#### Output Offset Voltage vs. V<sub>G</sub> (Typical Unit 1)

20072069

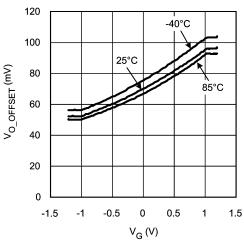

#### Output Offset Voltage vs. V<sub>G</sub> (Typical Unit 3)

20073970

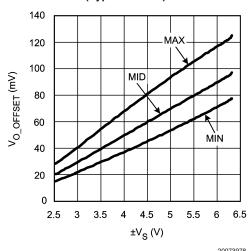

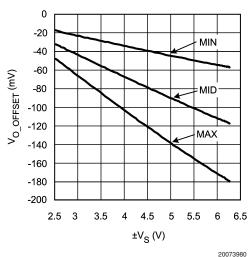

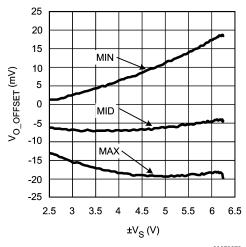

#### Output Offset Voltage vs. $\pm V_S$ for Various $V_G$ (Typical Unit 1)

# Output Offset Voltage vs. $\pm V_S$ for Various $V_G$ (Typical Unit 3)

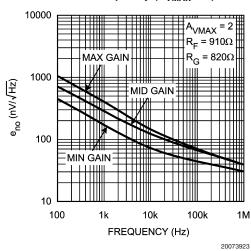

#### Noise vs. Frequency $(A_{VMAX} = 2)$

# Output Offset Voltage vs. $\pm V_S$ for Various $V_G$ (Typical Unit 2)

20073979

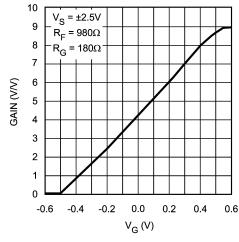

#### Gain vs. V<sub>G</sub> (±2.5V)

20073929

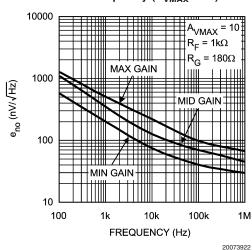

#### Noise vs. Frequency $(A_{VMAX} = 10)$

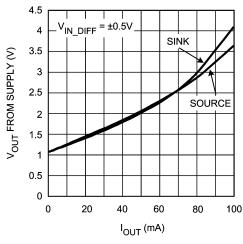

Output Voltage vs. Output Current

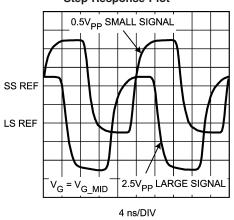

Step Response Plot

0.5V<sub>PP</sub> SMALL SIGNAL

SS REF

LS REF

5V<sub>PP</sub> LARGE SIGNAL

4 ns/DIV

Step Response Plot

20073937

20073963

Gain vs. V<sub>G</sub> Step  $V_{IN} = 0.3V$ A<sub>VMAX</sub>= 10 0.9  $R_L = 100\Omega$ 0.6 0.3 GAIN (V/V) 0 -0.3 GAIN -0.6 3 2 -0.9 -1.2 -1.5 t (10ns/DIV)

20073981

20073962

#### Application Information

#### THEORY OF OPERATION

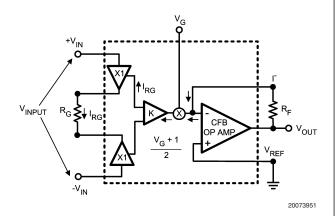

The LMH6503 is a linear wideband variable-gain amplifier as illustrated in Figure 1. A voltage input signal may be applied differentially between the two inputs (+V<sub>IN</sub>, -V<sub>IN</sub>), or singleendedly by grounding one of the two unused inputs. The LMH6503 input buffers convert the input voltage to a current  $(I_{BG})$  that is a function of the differential input voltage  $(V_{INPUT})$ =  $(+V_{IN})$  -  $(-V_{IN})$ ) and the value of the gain setting resistor  $(\ensuremath{\mbox{R}_{\mbox{\scriptsize G}}}).$  This current  $(\ensuremath{\mbox{I}_{\mbox{\scriptsize RG}}})$  is then mirrored to a gain stage with a current gain of K (1.72 nominal). The voltage controlled two-quadrant multiplier attenuates this current which is then converted to a voltage via the output amplifier. This output amplifier is a current feedback op amp configured as a Transimpedance amplifier. Its Transimpedance gain is the feedback resistor (R<sub>F</sub>). The input signal, output, and gain control are all voltages. The output voltage can easily be calculated as shown in Equation 1:

$$V_{OUT} = I_{RG} \times K \times \left[ \frac{V_{G} + 1}{2} \right] \times R_{F} \quad FOR -1 < V_{G} < +1$$

(1)

Where K = 1.72 (Nominal) since:

$$I_{RG} = \frac{V_{INPUT}}{R_{G}}$$

The gain of the LMH6503 is therefore a function of three external variables:  $R_{\rm G},\,R_{\rm F},\,{\rm and}\,\,{\rm V}_{\rm G}$  as expressed in Equation 2.

$$A_V = \frac{R_F}{R_G} \times 1.72 \times \left[ \frac{V_G + 1}{2} \right]$$

(2)

The gain control voltage ( $V_G$ ) has an ideal input range of  $-1V < V_G < +1V$ . At  $V_G = +1V$ , the gain of the LMH6503 is at its maximum as expressed in Equation 3:

$$A_{V} = 1.72 \frac{R_{F}}{R_{G}}$$

(3)

Notice also that Equation 3 holds for both differential and single ended operation.

FIGURE 1. LMH6503 Functional Block Diagram

#### CHOOSING $R_F$ AND $R_G$

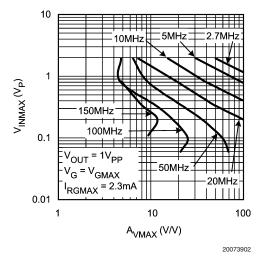

$R_{\text{G}}$  is calculated from Equation 4.  $V_{\text{INPUTMAX}}$  is the maximum peak

$$R_{G} = \frac{V_{INPUT_{MAX}}}{I_{R_{GMAX}}}$$

(4)

input voltage ( $V_{pk}$ ) determined by the application.  $I_{RGMAX}$  is the maximum allowable current through  $R_G$  and is typically 2.3mA. Once  $A_{VMAX}$  is determined from the minimum input and desired output voltages,  $R_F$  is then determined using Equation 5. These values of  $R_F$  and  $R_G$  are

#### **Application Information** (Continued)

$$R_{F} = \frac{1}{K} * R_{G} * A_{VMAX}$$

(5)

the minimum possible values that meet the input voltage and maximum gain constraints. Scaling the resistor values will decrease bandwidth and improve stability.

Figure 2 illustrates the resulting LMH6503 bandwidths as a function of the maximum ( y axis) and minimum (related to x axis) input voltages when  $V_{OUT}$  is held constant at  $1V_{PP}$ .

FIGURE 2. Bandwidth vs. VINMAX and AVMAX

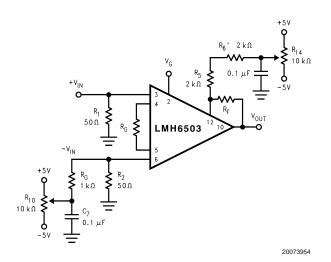

#### **ADJUSTING OFFSETS**

Treating the offsets introduced by the input and output stages of the LMH6503 is accomplished with a two step process. The offset voltage of the output stage is treated by first applying -1.1V on  $V_G$ , which effectively isolates the input stage and multiplier core from the output stage. As illustrated in *Figure 3*, the trim pot located at R14 on the LMH6503 Evaluation Board (CLC730033) should then be adjusted in order to null the offset voltage seen at the LMH6503's output (pin 10).

FIGURE 3. Nulling the Output Offset Voltage

Once this is accomplished, the offset errors introduced by the input stage and multiplier core can then be treated. The second step requires the absence of an input signal and matched source impedances on the two input pins in order to cancel the bias current errors. This done, then +1.1V should be applied to  $V_{\rm G}$  and the trim pot located at  $R_{\rm 10}$  adjusted in order to null the offset voltage seen at the LMH6503's output. If a more limited gain range is anticipated, the above adjustments should be made at these operating points. These steps will minimize the output offset voltage. However, since the offset term itself varies with the gain setting, the correction is not perfect and some residual output offset will remain.

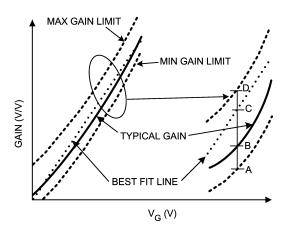

#### **GAIN ACCURACY**

Defined as the ratio of measured gain (V/V), at a certain  $V_G$ , to the best fit line drawn through the typical gain (V/V) distribution for  $-1V < V_G < 1V$  (results expressed in dB) (See *Figure 4*). The best fit gain (A<sub>V</sub>) is given by:

$$A_V \; (V/V) = 4.87 V_G + 4.61 \eqno(6)$$

For:  $-1V \le V_G \le + 1V, \; R_F = 1k\Omega, \; R_G = 174\Omega$

For a  $V_{\rm G}$  range, the value specified in the tables represents the worst case accuracy over the entire range. The "Typical" value would be the worst case ratio between the "Typical Gain" and the best fit line. The "Max" value would be the worst case between the max/min gain limit and the best fit line

#### **GAIN MATCHING**

Defined as the limit on gain variation at a certain  $V_{\rm G}$  (expressed in dB) (See *Figure 4*). Specified as "Max" only (no "Typical"). For a  $V_{\rm G}$  range, the value specified represents the worst case matching over the entire range. The "Max" value would be the worst case ratio between the max/min gain limit and the typical gain.

PARAMETER:

GAIN ACCURACY (TYPICAL) = B/C (dB)

GAIN ACCURACY (+ & - LIMIT) = D/C & A/C (dB)

GAIN MATCHING (+ & - LIMIT) = D/B & A/B (dB)

20073955

FIGURE 4. Gain Accuracy and Gain Matching

Parameters Defined

#### Application Information (Continued)

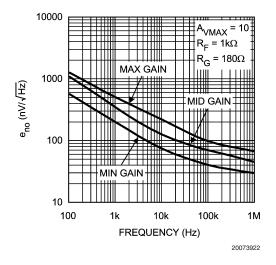

#### NOISE

Figure 5 describes the LMH6503's output-referred spot noise density as a function of frequency with  $A_{VMAX} = 10V/V$ . The plot includes all the noise contributing terms. However, with both inputs terminated in  $50\Omega$ , the input noise contribution is minimal. At  $A_{VMAX} = 10V/V$ , the LMH6503 has a typical flat-band input-referred spot noise density (e<sub>in</sub>) of 6.6nV/ $\sqrt{\text{Hz}}$ . For applications with –3dB BW extending well into the flat-band region, the input RMS voltage noise can be determined from the following single-pole model:

$$V_{RMS} = e_{in} * \sqrt{1.57 * (-3dB BANDWIDTH)}$$

(7)

FIGURE 5. Output Referred Voltage Noise vs. Frequency

#### **CIRCUIT LAYOUT CONSIDERATIONS**

Good high-frequency operation requires all of the decoupling capacitors shown in *Figure 6* to be placed as close as possible to the power supply pins in order to insure a proper high-frequency low-impedance bypass. Adequate ground plane and low inductive power returns are also

FIGURE 6. Required Power Supply Decoupling

required of the layout. Minimizing the parasitic capacitances at pins 3, 4, 5, 6, 9, 10 and 12 will assure best high frequency performance. The parasitic inductance of component leads or traces to pins 4, 5 and 9 should also be kept to a minimum. Parasitic or load capacitance,  $C_{\rm L}$ , on the output (pin 10) degrades phase margin and can lead to frequency response peaking or circuit oscillation. The LMH6503 is fully stable when driving a  $100\Omega$  load. With reduced load (e.g.  $1 \mathrm{k}\Omega$ ) there is a possibility of instability at very high frequencies beyond 400MHz especially with a capacitive load. When the LMH6503 is connected to a light load as such, it is recommended to add a snubber network to the output (e.g.  $100\Omega$  and  $39\mathrm{pF}$  in series tied between the LMH6503 output and ground).  $C_{\rm L}$  can also be isolated from the output by placing a small resistor in series with the output (pin 10).

Component parasitics also influence high frequency results. Therefore it is recommended to use metal film resistors such as RN55D or leadless components such as surface mount devices. High profile sockets are not recommended.

National Semiconductor suggests the following evaluation board as a guide for high frequency layout and as an aid in device testing and characterization:

| Device    | Package  | Evaluation Board Part<br>Number |

|-----------|----------|---------------------------------|

| LMH6503MA | SOIC-14  | CLC730033                       |

| LMH6503MT | TSSOP-14 | CLC730146                       |

The evaluation board is shipped when a device sample request is placed with National Semiconductor.

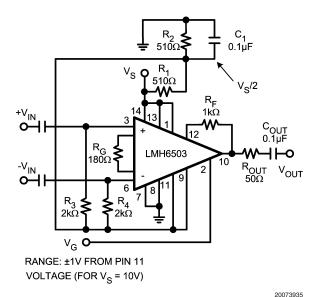

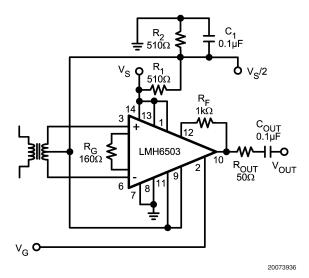

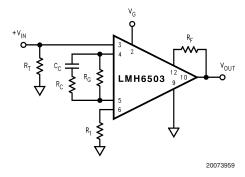

#### SINGLE SUPPLY OPERATION

It is possible to operate the LMH6503 with a single supply. To do so, tie pin 11 (GND) to a potential about mid point between  $V^+$  and  $V^-$ . Two examples are shown in Figure 7 & Figure 8.

FIGURE 7. AC Coupled Single Supply VGA

#### **Application Information** (Continued)

FIGURE 8. Transformer Coupled Single Supply VGA

#### **OPERATING AT LOWER SUPPLY VOLTAGES**

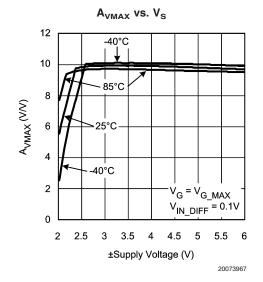

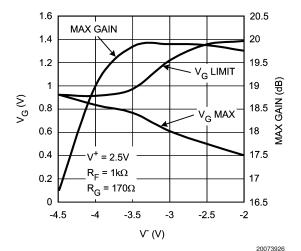

The LMH6503 is rated for operation down to 5V supplies (V $^+$  - V $^-$ ). There are some specifications shown for operation at  $\pm 2.5$ V within the data sheet (i.e. Frequency Response, CMRR, PSRR, Gain vs. V $_{\rm G}$ , etc.). Compared to  $\pm 5$ V operation, at lower supplies:

a) V $_{\rm G}$  range constricts. Referring to Figure 9, note that V $_{\rm G\_MAX}$  (V $_{\rm G}$  voltage required to get maximum gain) is 0.5V (V $_{\rm S}$  =  $\pm 2.5$ V) compared to 1.0V for V $_{\rm S}$  =  $\pm 5$ V. At the same time, gain cut-off (V $_{\rm G\_MIN}$ ) would shift to -0.5V from - 1V with V $_{\rm S}$  =  $\pm 5$ V.

Table 1 shows the approximate expressions for various  $V_G$  voltages as a function of  $V^{\text{-}}$ :

Table 1: V<sub>G</sub> Definition Based on V<sup>-</sup>

| V <sub>G</sub>     | Definition           | Expression (V)        |

|--------------------|----------------------|-----------------------|

| $V_{G\_MIN}$       | Gain Cut-off         | 0.2 x V <sup>-</sup>  |

| $V_{G\_MID}$       | A <sub>VMAX</sub> /2 | 0                     |

| V <sub>G MAX</sub> | A <sub>VMAX</sub>    | −0.2 x V <sup>−</sup> |

b) V<sub>G\_LIMIT</sub> (maximum permissible voltage on V<sub>G</sub>) is reduced. This is due to limitations within the device arising from transistor headroom. Beyond this limit, device performance will be affected (non-destructive). Referring to Figure 9, note that with V<sup>+</sup> = 2.5V, and V<sup>-</sup> = -4V, V<sub>G\_LIMIT</sub> is approaching V<sub>G\_MAX</sub> and already "Max gain" is reduced by 1dB. This means that operating under these conditions has reduced the maximum permissible voltage on V<sub>G</sub> to a level below what is needed to get Max gain. If supply voltages are asymmetrical, reference Figure 9 and

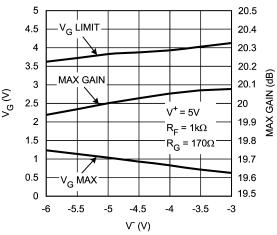

Figure 10 plots to make sure the region of operation is not overly restricted by the "pinching" of  $V_{G\_LIMIT}$ , and  $V_{G^-}$  MAX curves.

c) "Max\_gain" reduces. There is an intrinsic reduction in max gain when the total supply voltage is reduced (see Typical Performance Characteristics plots for Gain vs.  $V_G$  ( $V_S = \pm 2.5 V$ ). In addition, there is the more drastic mechanism described in "b" above and shown in *Figure*

Similar plots for  $V^+ = 5V$  operation are shown in *Figure 10* for comparison and reference.

FIGURE 9.  $V_{G\_MAX}$ ,  $V_{G\_LIMIT}$ , & Max-gain vs.  $V^-$ ( $V^+ = 2.5V$ )

20073925

FIGURE 10.  $V_{G\_MAX}$ ,  $V_{G\_LIMIT}$ , & Max-gain vs.  $V^-$ ( $V^+ = 5V$ )

#### **Application Circuits**

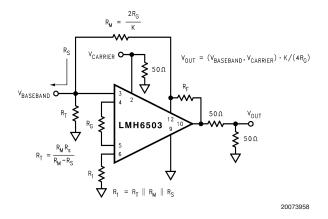

#### FOUR-QUADRANT MULTIPLIER

Applications requiring multiplication, squaring or other nonlinear functions can be implemented with four-quadrant multipliers. The LMH6503 implements a four-quadrant multiplier as illustrated in *Figure 11*:

FIGURE 11. Four Quadrant Multiplier

#### FREQUENCY SHAPING

Frequency shaping and bandwidth extension of the LMH6503 can be accomplished using parallel networks connected across the  $R_{\rm G}$  ports. The network shown in the Figure 12 schematic will effectively extend the LMH6503's bandwidth.

FIGURE 12. Frequency Shaping

#### 2<sup>nd</sup> ORDER TUNABLE BANDPASS FILTER

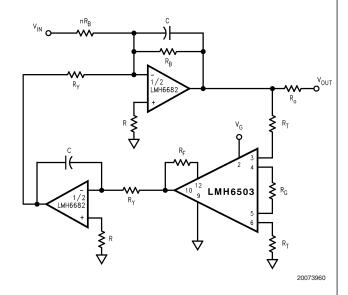

The LMH6503 Variable-Gain Amplifier placed into a feedback loop provides signal processing function such as in a 2nd order tunable bandpass filter. The center frequency of the 2nd order bandpass shown in *Figure 13* is adjusted through the use of the LMH6503's gain control voltage,  $V_{\rm G}$ . The integrators implemented with two sections of a LMH6682, provide the coefficients for the transfer function.

$$\frac{V_O}{V_{IN}} = \left[ -\frac{1}{n} \right] \frac{s \frac{1}{CR_B}}{s^2 + s \frac{1}{CR_B} + \frac{p}{C^2 R_Y^2}}$$

$$p = 1.72 \frac{R_F}{R_Y}$$

,  $Q = \frac{\sqrt{pR_B}}{R_Y}$ ,  $\omega_0 = \frac{\sqrt{p}}{CR_Y}$

FIGURE 13. Tunable Bandpass Filter

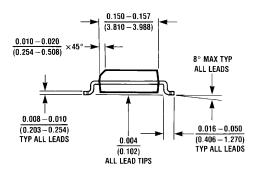

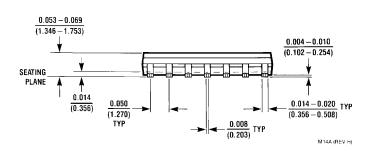

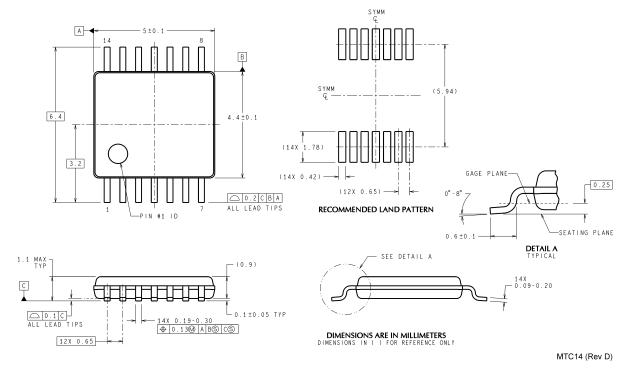

#### Physical Dimensions inches (millimeters) unless otherwise noted

14-Pin SOIC NS Package Number M14A

14-Pin TSSOP NS Package Number MTC14

#### **Notes**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560