May 1999

**Typical**

# LM6118/LM6218 Fast Settling Dual Operational Amplifiers

# **General Description**

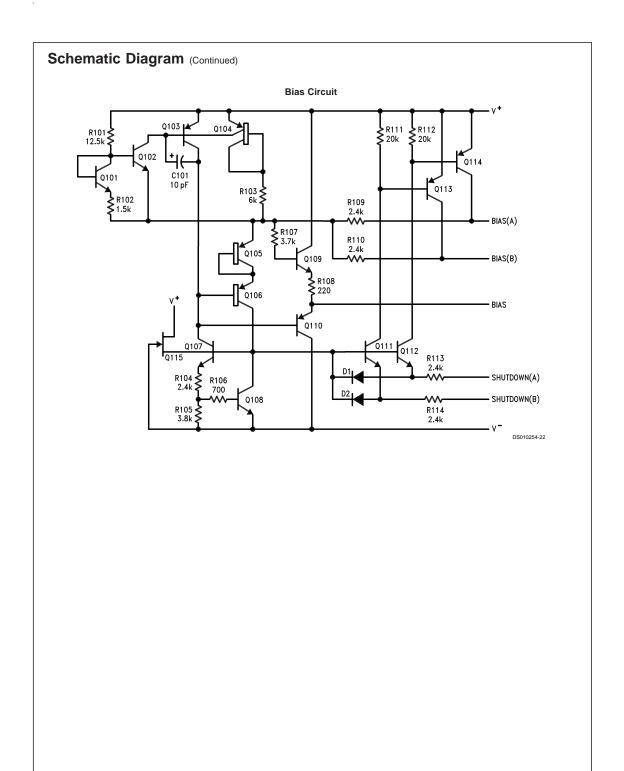

The LM6118/LM6218 are monolithic fast-settling unity-gain-compensated dual operational amplifiers with  $\pm 20$  mA output drive capability. The PNP input stage has a typical bias current of 200 nA, and the operating supply voltage is  $\pm 5 \text{V}$  to  $\pm 20 \text{V}$ .

These dual op amps use slew enhancement with special mirror circuitry to achieve fast response and high gain with low total supply current.

The amplifiers are built on a junction-isolated VIP $^{\text{TM}}$  (Vertically Integrated PNP) process which produces fast PNP's that complement the standard NPN's.

### **Features**

| ■ Low offset voltage:            | 0.2 m\   |

|----------------------------------|----------|

| ■ 0.01% settling time:           | 400 ns   |

| ■ Slew rate A <sub>v</sub> = -1: | 140 V/µs |

| ■ Slew rate A <sub>v</sub> = +1: | 75 V/µs  |

| ■ Gain bandwidth:                | 17 MH    |

| ■ Total supply current:          | 5.5 mA   |

| ■ Output drives 50Ω load (±1V)   |          |

# **Applications**

- D/A converters

- Fast integrators

- Active filters

# **Connection Diagrams and Order Information**

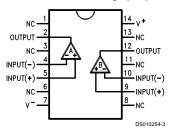

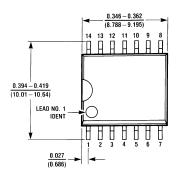

#### Small Outline Package (WM)

Top View Order Number LM6218WM See NS Package Number M14B

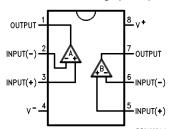

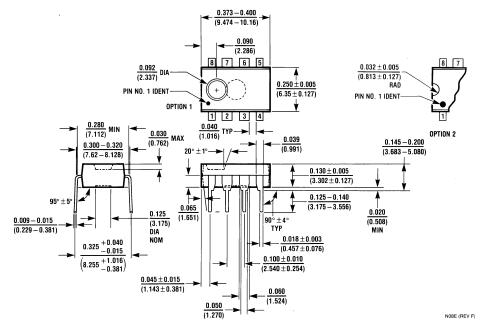

### Dual-In-Line Package (J or N)

Top View Order Number LM6118N, LM6218AN or LM6218N See NS Package Number N08E

VIP™ is a trademark of National Semiconductor Corporation

# **Typical Applications**

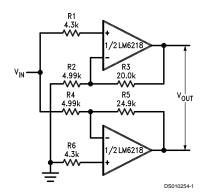

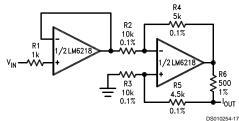

Single ended input to differential output  $A_V = 10$ , BW = 3.2 MHz 40 Vpp Response = 1.4 MHz  $\text{V}_S = \pm 15 \text{V}$

Wide-Band, Fast-Settling 40 V<sub>PP</sub> Amplifier

www.national.com

**Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Total Supply Voltage 42V

Input Voltage (Note 2)

Differential Input Current (Note 3) ±10 mA

Output Current (Note 4) Internally Limited

Power Dissipation (Note 5) 500 mW

ESD Tolerance

$(C = 100 \text{ pF}, R = 1.5 \text{ k}\Omega)$  ±2 kV

Junction Temperature 150°C

Storage Temperature Range -65°C to +150°C

Lead Temperature

(Soldering, 10 sec.)

ing, 10 sec.) 300°C

# **Operating Temp. Range**

# **Electrical Characteristics**

$\pm 5\text{V} \le \text{V}_{\text{S}} \le \pm 20\text{V}$ ,  $\text{V}_{\text{CM}} = 0\text{V}$ ,  $\text{V}_{\text{OUT}} = 0\text{V}$ ,  $\text{I}_{\text{OUT}} = 0\text{A}$ , unless otherwise specified. Limits with standard type face are for  $\text{T}_{\text{J}} = 25^{\circ}\text{C}$ , and **Bold Face Type** are for **Temperature Extremes**.

|                               |                                                                        | Тур  | LM6118   | LM6218A  | LM6218   |            |

|-------------------------------|------------------------------------------------------------------------|------|----------|----------|----------|------------|

| Parameter                     | Conditions                                                             | 25°C | Limits   | Limits   | Limits   | Units      |

|                               |                                                                        |      | (Note 6) | (Note 6) | (Note 6) |            |

| Input Offset Voltage          | V <sub>S</sub> = ±15V                                                  | 0.2  | 1        | 1        | 3        | mV (max)   |

|                               |                                                                        |      | 2        | 2        | 4        |            |

| Input Offset Voltage          | $V- + 3V \le V_{CM} \le V+ - 3.5V$                                     | 0.3  | 1.5      | 1.5      | 3.5      | mV (max)   |

|                               |                                                                        |      | 2.5      | 2.5      | 4.5      |            |

| Input Offset Current          | $V- + 3V \le V_{CM} \le V+ - 3.5V$                                     | 20   | 50       | 50       | 100      | nA (max)   |

|                               |                                                                        |      | 250      | 100      | 200      |            |

| Input Bias Current            | $V- + 3V \le V_{CM} \le V+ - 3.5V$                                     | 200  | 350      | 350      | 500      | nA (max)   |

|                               |                                                                        |      | 950      | 950      | 1250     |            |

| Input Common Mode             | $V- + 3V \le V_{CM} \le V+ - 3.5V$                                     | 100  | 90       | 90       | 80       | dB (min)   |

| Rejection Ratio               | V <sub>S</sub> = ±20V                                                  |      | 85       | 85       | 75       |            |

| Positive Power Supply         | V- = -15V                                                              | 100  | 90       | 90       | 80       | dB (min)   |

| Rejection Ratio               | 5V ≤ V+ ≤ 20V                                                          |      | 85       | 85       | 75       |            |

| Negative Power Supply         | V+ = 15V                                                               | 100  | 90       | 90       | 80       | dB (min)   |

| Rejection Ratio               | -20V ≤ V- ≤ -5V                                                        |      | 85       | 85       | 75       |            |

| Large Signal                  | $V_{out} = \pm 15V$ $R_L = 10k$                                        | 500  | 150      | 150      | 100      | V/mV (min) |

| Voltage Gain                  | V <sub>S</sub> = ±20V                                                  |      | 100      | 100      | 70       |            |

|                               | $V_{out} = \pm 10V$ $R_L = 500$                                        | 200  | 50       | 50       | 40       | V/mV (min) |

|                               | $V_S = \pm 15V$ (±20 mA)                                               |      | 30       | 30       | 25       |            |

| V <sub>O</sub> Output Voltage | Supply = $\pm 20V$ R <sub>L</sub> = $10k$                              | 17.3 | ±17      | ±17      | ±17      | V (min)    |

| Swing                         |                                                                        |      |          |          |          |            |

| Total Supply Current          | $V_S = \pm 15V$                                                        | 5.5  | 7        | 7        | 7        | mA (max)   |

|                               |                                                                        |      | 7.5      | 7.5      | 7.5      |            |

| Output Current Limit          | $V_S = \pm 15V$ , Pulsed                                               | 65   | 100      | 100      | 100      | mA (max)   |

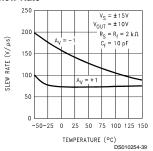

| Slew Rate, Av = −1            | $V_S = \pm 15V, V_{out} = \pm 10V$                                     | 140  | 100      | 100      | 100      | V/µs (min) |

|                               | $R_S = R_f = 2k, C_f = 10 pF$                                          |      | 50       | 50       | 50       |            |

| Slew Rate, Av = +1            | V <sub>S</sub> = ±15V, V <sub>out</sub> = ±10V                         | 75   | 50       | 50       | 50       | V/µs (min) |

|                               | $R_S = R_f = 2k, C_f = 10 pF$                                          |      | 30       | 30       | 30       |            |

| Gain-Bandwidth Product        | $V_S = \pm 15V, f_o = 200 \text{ kHz}$                                 | 17   | 14       | 14       | 13       | MHz (min)  |

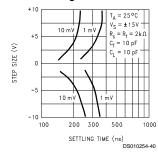

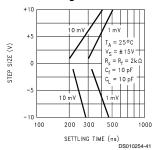

| 0.01% Settling Time           | $\Delta V_{\text{out}} = 10 \text{V}, V_{\text{S}} = \pm 15 \text{V},$ | 400  |          |          |          | ns         |

| $A_{V} = -1$                  | $R_S = R_f = 2k, C_f = 10 pF$                                          | 400  |          |          |          |            |

| Input Capacitance             | Inverter                                                               | 5    |          |          |          | pF         |

|                               | Follower                                                               | 3    |          |          |          | pF         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 2: Input voltage range is  $(V^+ - 1V)$  to  $(V^-)$ .

### **Electrical Characteristics** (Continued)

Note 3: The inputs are shunted with three series-connected diodes back-to-back for input differential clamping. Therefore differential input voltages greater than about 1.8V will cause excessive current to flow unless limited to less than 10 mA.

Note 4: Current limiting protects the output from a short to ground or any voltage less than the supplies. With a continuous overload, the package dissipation must be taken into account and heat sinking provided when necessary.

Note 5: Devices must be derated using a thermal resistance of 90°C/W for the N and WM packages.

Note 6: Limits are guaranteed by testing or correlation.

# **Typical Performance Characteristics**

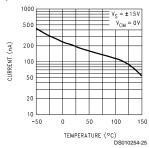

#### Input Bias Current

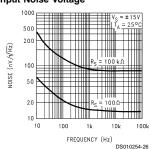

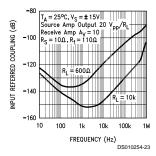

#### Input Noise Voltage

#### **Common Mode Limits**

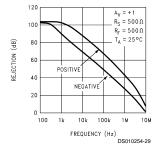

#### **Common Mode Rejection**

#### **Power Supply Rejection**

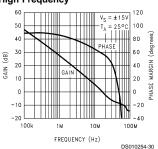

# Frequency Response High Frequency

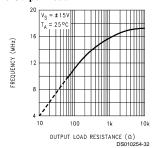

## Unity Gain Bandwidth

# Unity Gain Bandwidth vs Output Load

# Large Signal Response (Sine Wave)

# **Typical Performance Characteristics** (Continued)

#### **Total Harmonic Distortion**

# Output Impedance

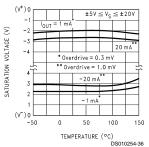

### **Output Saturation**

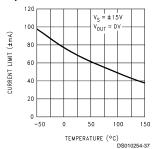

#### **Output Current Limit**

# Supply Current (Both Amplifiers)

#### Slew Rate

#### Inverter Settling Time

### Follower Settling Time

#### Typical Stability Range

www.national.com

# **Typical Performance Characteristics** (Continued)

#### **Amplifier to Amplifier Coupling**

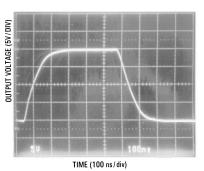

# Settling Time, Vs = ±15V

DS010254-7

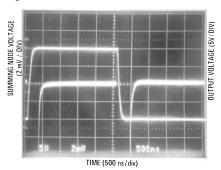

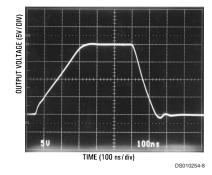

Step Response, Av = +1,  $Vs = \pm 15V$

Step Response, Av = -1,  $Vs = \pm 15V$

DS010254-

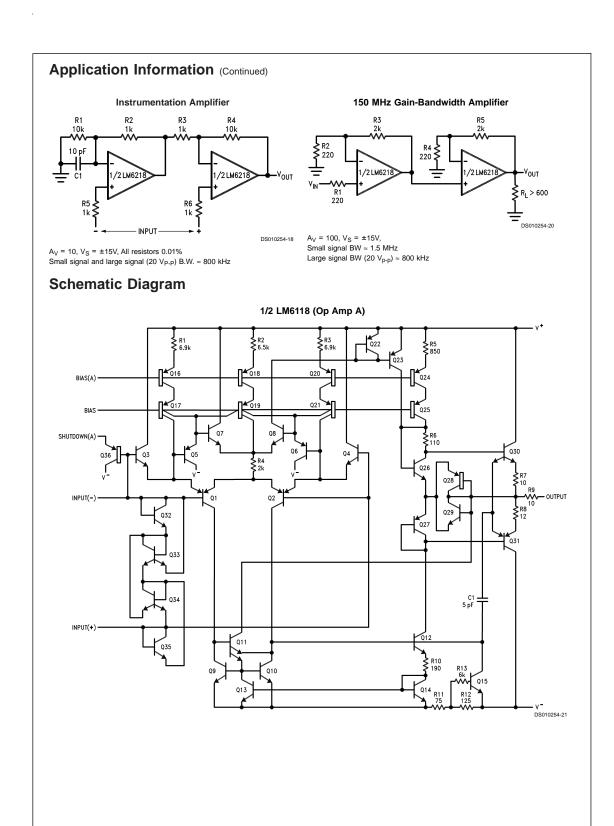

# **Application Information**

#### General

The LM6118/LM6218 are high-speed, fast-settling dual op-amps. To insure maximum performance, circuit board layout is very important. Minimizing stray capacitance at the inputs and reducing coupling between the amplifier's input and output will minimize problems.

#### **Supply Bypassing**

To assure stability, it is recommended that each power supply pin be bypassed with a 0.1  $\mu F$  low inductance capacitor near the device. If high frequency spikes from digital circuits or switching supplies are present, additional filtering is recommended. To prevent these spikes from appearing at the output, R-C filtering of the supplies near the device may be necessary.

# Power Dissipation

These amplifiers are specified to 20 mA output current. If accompanied with high supply voltages, relatively high power dissipation in the device will occur, resulting in high junction temperatures. In these cases the package thermal resistance must be taken into consideration. (See Note 5 under Electrical Characteristics.) For high dissipation, an N package with large areas of copper on the pc board is recommended.

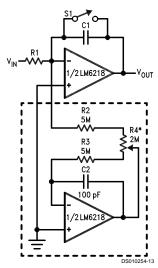

#### Amplifier Shut Down

If one of the amplifiers is not used, it can be shut down by connecting both the inverting and non-inverting inputs to the V– pin. This will reduce the power supply current by approximately 25%.

#### **Capacitive Loading**

Maximum capacitive loading is about 50 pF for a closed-loop gain of +1, before the amplifier exhibits excessive ringing and becomes unstable. A curve showing maximum capacitive loads, with different closed-loop gains, is shown in the Typical Performance Characteristics section.

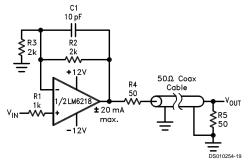

To drive larger capacitive loads at low closed-loop gains, isolate the amplifier output from the capacitive load with  $50\Omega$ . Connect a small capacitor directly from the amplifier output to the inverting input. The feedback loop is closed from the isolated output with a series resistor to the inverting input.

# Application Information (Continued)

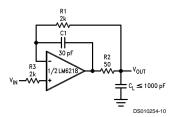

# Voltage Follower

For  $C_L$  = 1000 pF, Small signal BW = 5 MHz 20  $V_{p-p}$  BW = 500 kHz

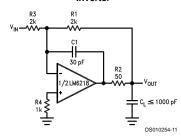

#### Inverter

Settling time to 0.01%, 10V Step For  $C_L$  = 1000 pF, settling time  $\approx$  1500 ns For  $C_L$  = 300 pF, settling time  $\approx$  500 ns

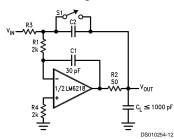

#### Integrator

Examples of unity gain connections for a voltage follower, Inverter, and integrator driving capacitive loads up to 1000 pF are shown here. Different R1–C1 time constants and capacitive loads will have an effect on settling times.

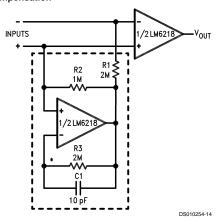

#### Input Bias Current Compensation

Input bias current of the first op amp can be reduced or balanced out by the second op amp. Both amplifiers are laid out in mirror image fashion and in close proximity to each other, thus both input bias currents will be nearly identical and will track with temperature. With both op amp inputs at the same potential, a second op amp can be used to convert bias current to voltage, and then back to current feeding the first op amp using large value resistors to reduce the bias current to the level of the offset current.

Examples are shown here for an inverting application, (a) where the inputs are at ground potential, and a second circuit (b) for compensating bias currents for both inputs.

# **Application Information** (Continued)

### **Bias Current Compensation**

\*mount resistor close to input pin to minimize stray capacitance

### (b) Compensation to Both Inputs

\*adjust for zero integrator drift

# (a) Inverting Input Bias Compensation for Integrator Application

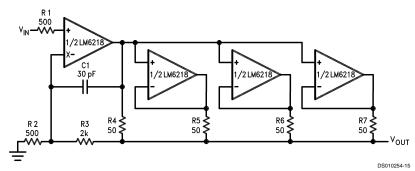

#### Amplifier/Parallel Buffer

$A_V$  = +5,  $I_{OUT}$   $\leq$  80 mA  $V_S$  = ±15V,  $C_L \leq$  0.01  $\mu F$  Large and small signal B.W. = 1.3 MHz (THD = 3%)

# Application Information (Continued)

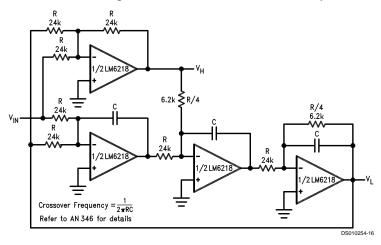

### Constant-Voltage Crossover Network With 12 dB/Octave Slope

#### **Bilateral Current Source**

$V_S = \pm 15V$ ,  $-10 \le V_{IN} \le 10V$

$$\frac{I_{OUT}}{V_{IN}} = \frac{R4}{R2 R6} = \frac{1 mA}{1V}$$

Output dynamic range = 10V - R6  $|I_{OUT}|$  R<sub>L</sub> = 500 $\Omega$ , small signal BW = 6 MHz Large signal response = 800 kHz

$$C_{out}$$

equiv. =  $\frac{R2 + R4}{2\pi f_0 R2 R6} = 32 pF (f_0 = 15 MHz)$

#### Coaxial Cable Driver

Small signal (200 mV  $_{p\text{-}p})$  BW  $\approx 5$  MHz

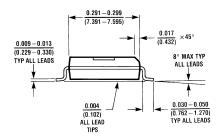

# Physical Dimensions inches (millimeters) unless otherwise noted

8-Lead Molded Small Outline Package (M) Order Number LM6218AWM or LM6218WM NS Package Number M14B

www.national.com 1

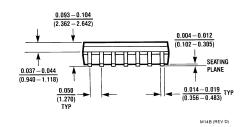

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

8-Lead Molded Dual-In-Line Package (N) Order Number LM6118N, LM6218AN or LM6218N NS Package Number N08E

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

Fax: 449 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: 449 (0) 1 80-530 85 85

English Tel: 449 (0) 1 80-532 78 32

Français Tel: 449 (0) 1 80-532 93 58

Italiano Tel: 449 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507