#### **PRELIMINARY**

August 2005

### **DS90C363B**

# +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link -65 MHz

#### **General Description**

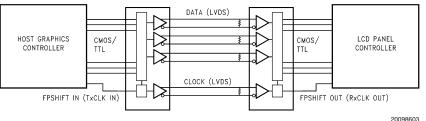

The DS90C363B transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fourth LVDS link. Every cycle of the transmit clock 21 bits of input data are sampled and transmitted. At a transmit clock frequency of 65 MHz, 18 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 455 Mbps per LVDS data channel. Using a 65 MHz clock, the data throughput is 170 Mbytes/sec. The DS90C363B transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge or Falling edge strobe Receiver (DS90CF366) without any translation logic.

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high speed TTL interfaces.

#### **Features**

- No special start-up sequence required between clock/data and /PD pins. Input signal (clock and data) can be applied either before or after the device is powered.

- Support Spread Spectrum Clocking up to 100kHz frequency modulation & deviations of ±2.5% center spread or -5% down spread.

- "Input Clock Detection" feature will pull all LVDS pairs to logic low when input clock is missing and when /PD pin is logic high.

- 18 to 68 MHz shift clock support

- Best-in-Class Set & Hold Times on TxINPUTs

- Tx power consumption < 130 mW (typ) @65MHz Grayscale

- 40% Less Power Dissipation than BiCMOS Alternatives

- Tx Power-down mode < 37µW (typ)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA.

- Narrow bus reduces cable size and cost

- Up to 1.3 Gbps throughput

- Up to 170 Megabytes/sec bandwidth

- 345 mV (typ) swing LVDS devices for low EMI

- PLL requires no external components

- Compatible with TIA/EIA-644 LVDS standard

- Low profile 48-lead TSSOP package

- Improved replacement for: SN75LVDS84, DS90C363A

## **Block Diagram**

Order Number DS90C363BMT See NS Package Number MTD48

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$\begin{array}{lll} \text{Supply Voltage (V$_{\rm CC}$)} & -0.3 \text{V to } +4 \text{V} \\ \text{CMOS/TTL Input Voltage} & -0.3 \text{V to (V$_{\rm CC}$} + 0.3 \text{V)} \\ \text{LVDS Driver Output Voltage} & -0.3 \text{V to (V$_{\rm CC}$} + 0.3 \text{V)} \\ \end{array}$

LVDS Output Short Circuit

$\begin{array}{ll} \text{Duration} & \text{Continuous} \\ \text{Junction Temperature} & +150\,^{\circ}\text{C} \\ \text{Storage Temperature} & -65\,^{\circ}\text{C to } +150\,^{\circ}\text{C} \\ \end{array}$

Lead Temperature

(Soldering, 4 sec) +260°C

Maximum Package Power Dissipation Capacity @ 25°C

MTD48 (TSSOP) Package:

DS90C363B 1.98 W

Package Derating:

DS90C363B 16 mW/°C above +25°C

**ESD** Rating

(HBM, 1.5 kΩ, 100 pF) 7 kV (EIAJ, 0Ω, 200 pF) 500V

## Recommended Operating Conditions

|                                   | Min | Nom | Max | Units               |

|-----------------------------------|-----|-----|-----|---------------------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0 | 3.3 | 3.6 | V                   |

| Operating Free Air                |     |     |     |                     |

| Temperature (T <sub>A</sub> )     | -10 | +25 | +70 | °C                  |

| Supply Noise Voltage              |     |     | 200 | ${\rm mV}_{\rm PP}$ |

| (V <sub>CC</sub> )                |     |     |     |                     |

| TxCLKIN frequency                 | 18  |     | 68  | MHz                 |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                                                     | Conditio                                                                     | Conditions |      | Тур   | Max             | Units |

|-----------------|---------------------------------------------------------------|------------------------------------------------------------------------------|------------|------|-------|-----------------|-------|

| CMOS/TT         | L DC SPECIFICATIONS                                           |                                                                              |            | •    |       |                 |       |

| V <sub>IH</sub> | High Level Input Voltage                                      |                                                                              |            | 2.0  |       | V <sub>CC</sub> | V     |

| V <sub>IL</sub> | Low Level Input Voltage                                       |                                                                              |            | GND  |       | 0.8             | V     |

| V <sub>CL</sub> | Input Clamp Voltage                                           | I <sub>CL</sub> = -18 mA                                                     |            |      | -0.79 | -1.5            | V     |

| I <sub>IN</sub> | Input Current                                                 | $V_{IN} = 0.4V, 2.5V \text{ or } V_{CC}$                                     |            |      | +1.8  | +10             | μA    |

|                 |                                                               | V <sub>IN</sub> = GND                                                        |            | -10  | 0     |                 | μA    |

| LVDS DC         | SPECIFICATIONS                                                |                                                                              |            |      |       |                 |       |

| $V_{OD}$        | Differential Output Voltage                                   | $R_L = 100\Omega$                                                            |            | 250  | 345   | 450             | mV    |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between complimentary output states |                                                                              |            |      |       | 35              | mV    |

| Vos             | Offset Voltage (Note 4)                                       |                                                                              |            | 1.13 | 1.25  | 1.38            | V     |

| $\Delta V_{OS}$ | Change in V <sub>OS</sub> between complimentary output states |                                                                              |            |      |       | 35              | mV    |

| I <sub>os</sub> | Output Short Circuit Current                                  | $V_{OUT} = 0V, R_L = 100\Omega$                                              |            |      | -3.5  | -5              | mA    |

| l <sub>oz</sub> | Output TRI-STATE® Current                                     | Power Down = 0V,<br>V <sub>OUT</sub> = 0V or V <sub>CC</sub>                 | · ·        |      | ±1    | ±10             | μA    |

| TRANSM          | ITTER SUPPLY CURRENT                                          | 001                                                                          |            |      |       |                 |       |

| ICCTW           | Transmitter Supply Current<br>Worst Case                      | $R_L = 100\Omega$ ,<br>$C_L = 5 \text{ pF}$ ,<br>Worst Case Pattern          | f = 25MHz  |      | 29    | 40              | mA    |

|                 |                                                               | (Figures 1, 4) " Typ " values are given for V cc = 3.6V and T <sub>A</sub> = | f = 40 MHz |      | 34    | 45              | mA    |

|                 |                                                               | +25°C, " Max " values are given for V $_{CC}$ = 3.6V and T $_{A}$ = -10°C    | f = 65 MHz |      | 42    | 55              | mA    |

## **Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                | Condition                                                                       | ons         | Min | Тур | Max | Units |

|--------|------------------------------------------|---------------------------------------------------------------------------------|-------------|-----|-----|-----|-------|

| TRANSM | ITTER SUPPLY CURRENT                     |                                                                                 |             |     |     |     |       |

| ICCTG  | Transmitter Supply Current 16 Grayscale  | $R_L = 100\Omega$ ,<br>$C_L = 5 pF$ ,<br>16 Grayscale Pattern                   | f = 25 MHz  |     | 28  | 40  | mA    |

|        |                                          | (Figures 2, 4) " Typ " values are given for V $cc = 3.6V$ and T $_A =$          | f = 40 MHz  |     | 32  | 45  | mA    |

|        |                                          | +25°C, " Max " values<br>are given for V $_{CC}$ =<br>3.6V and T $_{A}$ = -10°C | f = 65 MHz  |     | 39  | 50  | mA    |

| ICCTZ  | Transmitter Supply Current<br>Power Down | Power Down = Low<br>Driver Outputs in TRI-S'<br>Power Down Mode                 | TATE® under |     | 11  | 150 | μА    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

#### **Recommended Transmitter Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter Min Typ                             |       |      |       |    |  |

|--------|-----------------------------------------------|-------|------|-------|----|--|

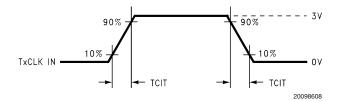

| TCIT   | TxCLK IN Transition Time (Figure 5) 5         |       |      | 5     | ns |  |

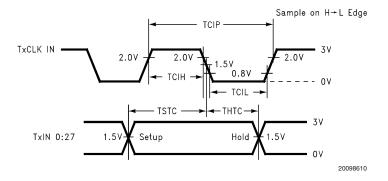

| TCIP   | TxCLK IN Period (Figure 6)                    | 14.7  | Т    | 50    | ns |  |

| TCIH   | TxCLK IN High Time (Figure 6)                 | 0.35T | 0.5T | 0.65T | ns |  |

| TCIL   | TxCLK IN Low Time (Figure 6)                  | 0.35T | 0.5T | 0.65T | ns |  |

| TXIT   | TxIN, and Power Down pin transition Time      | 1.5   |      | 6.0   | ns |  |

| TXPD   | Minimum pulse width for Power Down pin signal | 1     |      |       | us |  |

### **Transmitter Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                                         | Min    | Тур   | Max   | Units |    |

|--------|-------------------------------------------------------------------|--------|-------|-------|-------|----|

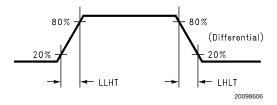

| LLHT   | LVDS Low-to-High Transition Time (Figure 4)                       |        | 0.75  | 1.4   | ns    |    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 4)                       |        |       | 0.75  | 1.4   | ns |

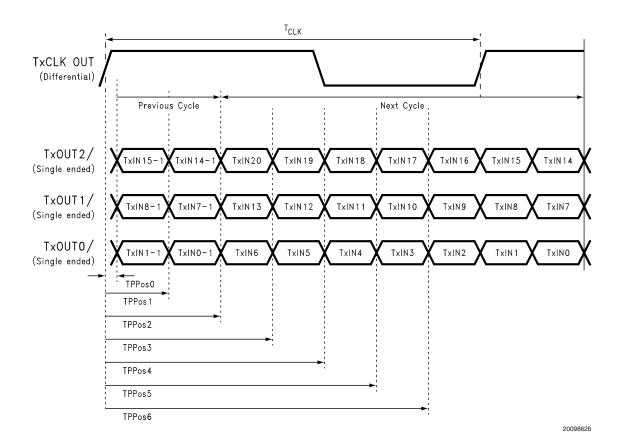

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 11 ) (Note 5) | f = 65 | -0.20 | 0     | 0.20  | ns |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                       | MHz    | 2.00  | 2.20  | 2.40  | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                       |        | 4.20  | 4.40  | 4.60  | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                       |        | 6.39  | 6.59  | 6.79  | ns |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                       |        | 8.59  | 8.79  | 8.99  | ns |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                       |        | 10.79 | 10.99 | 11.19 | ns |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                       |        | 12.99 | 13.19 | 13.39 | ns |

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 11 ) (Note 5) | f = 40 | -0.25 | 0     | 0.25  | ns |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                       | MHz    | 3.32  | 3.57  | 3.82  | ns |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                       |        | 6.89  | 7.14  | 7.39  | ns |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                       |        | 10.46 | 10.71 | 10.96 | ns |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                       |        | 14.04 | 14.29 | 14.54 | ns |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                       |        | 17.61 | 17.86 | 18.11 | ns |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                       |        | 21.18 | 21.43 | 21.68 | ns |

|        |                                                                   |        |       |       |       |    |

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and T  $_A$  = +25  $^{\circ}C$  unless specified otherwise.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

Note 4:  $V_{OS}$  previously referred as  $V_{CM}$ .

## **Transmitter Switching Characteristics** (Continued) Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol | Parameter                                                                                         |        | Min    | Тур      | Max    | Units |

|--------|---------------------------------------------------------------------------------------------------|--------|--------|----------|--------|-------|

| TPPos0 | Transmitter Output Pulse Position for Bit 0 (Figure 11 ) (Note 5)                                 | f = 25 | -0.450 | 0        | +0.450 | ns    |

| TPPos1 | Transmitter Output Pulse Position for Bit 1                                                       | MHz    | 5.26   | 5.71     | 6.16   | ns    |

| TPPos2 | Transmitter Output Pulse Position for Bit 2                                                       |        | 10.98  | 11.43    | 11.83  | ns    |

| TPPos3 | Transmitter Output Pulse Position for Bit 3                                                       |        | 16.69  | 17.14    | 17.54  | ns    |

| TPPos4 | Transmitter Output Pulse Position for Bit 4                                                       |        | 22.41  | 22.86    | 23.26  | ns    |

| TPPos5 | Transmitter Output Pulse Position for Bit 5                                                       |        | 28.12  | 28.57    | 28.97  | ns    |

| TPPos6 | Transmitter Output Pulse Position for Bit 6                                                       |        | 33.84  | 34.29    | 34.69  | ns    |

| TSTC   | TxIN Setup to TxCLK IN (Figure 6)                                                                 |        | 2.5    |          |        | ns    |

| THTC   | TxIN Hold to TxCLK IN (Figure 6)                                                                  |        | 0.5    |          |        | ns    |

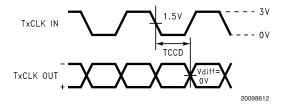

| TCCD   | TxCLK IN to TxCLK OUT Delay (Figure 7 ) 50% duty cycle input                                      |        | 3.340  |          | 7.211  | ns    |

|        | clock is assumed, T $_{A}$ = -10 $^{\circ}$ C, and 65MHz for " Min ", T $_{A}$ = 70 $^{\circ}$ C, |        |        |          |        |       |

|        | and 25MHz for " Max ", $V_{CC}$ = 3.6V, $R_FB = V_{CC}$                                           |        |        |          |        |       |

|        | TxCLK IN to TxCLK OUT Delay (Figure 7) 50% duty cycle input                                       |        | 3.011  |          | 6.062  | ns    |

|        | clock is assumed, T $_{A}$ = -10 $^{\circ}$ C, and 65MHz for " Min ", T $_{A}$ = 70 $^{\circ}$ C, |        |        |          |        |       |

|        | and 25MHz for " Max ", V <sub>CC</sub> = 3.6V, R_FB = GND                                         |        |        |          |        |       |

| SSCG   | Spread Spectrum Clock support; Modulation frequency with a                                        | f = 25 |        | 100kHz ± |        |       |

|        | linear profile (Note 6)                                                                           | MHz    |        | 2.5%/–5% |        |       |

|        |                                                                                                   | f = 40 |        | 100kHz ± |        |       |

|        |                                                                                                   | MHz    |        | 2.5%/–5% |        |       |

|        |                                                                                                   | f = 65 |        | 100kHz ± |        |       |

|        |                                                                                                   | MHz    |        | 2.5%/–5% |        |       |

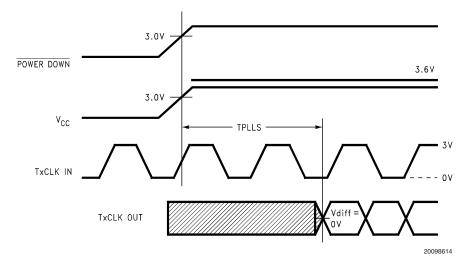

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 8)                                                        |        |        |          | 10     | ms    |

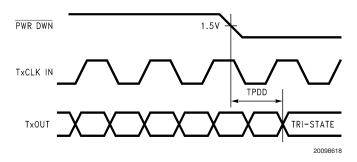

| TPDD   | Transmitter Power Down Delay (Figure 10)                                                          |        |        |          | 100    | ns    |

Note 5: The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temperature ranges. This parameter is functionality tested only on Automatic Test Equipment (ATE).

Note 6: Care must be taken to ensure TSTC and THTC are met so input data are sampling correctly. This SSCG parameter only shows the performance of tracking Spread Spectrum Clock applied to TxCLK IN pin, and reflects the result on TxCLKOUT+ and TxCLK- pins.

## **AC Timing Diagrams**

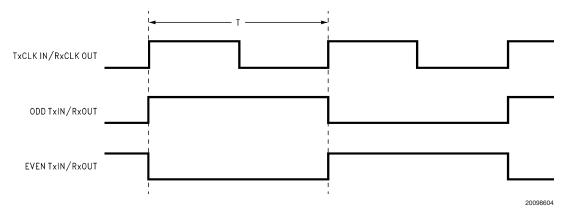

FIGURE 1. "Worst Case" Test Pattern

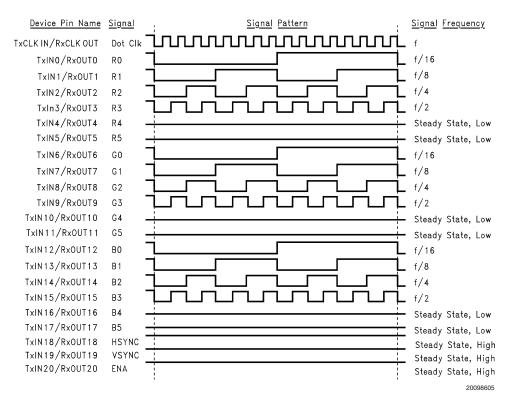

FIGURE 2. "16 Grayscale" Test Pattern (Notes 7, 8, 9, 10)

Note 7: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Note 8: The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

Note 9: Figures 1, 2 show a falling edge data strobe (TxCLK IN/RxCLK OUT).

Note 10: Recommended pin to signal mapping. Customer may choose to define differently.

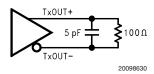

FIGURE 3. DS90C363B (Transmitter) LVDS Output Load

FIGURE 4. DS90C363B (Transmitter) LVDS Transition Times

FIGURE 5. DS90C363B (Transmitter) Input Clock Transition Time

FIGURE 6. DS90C363B (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

FIGURE 7. DS90C363B (Transmitter) Clock In to Clock Out Delay (Falling Edge Strobe)

FIGURE 8. DS90C363B (Transmitter) Phase Lock Loop Set Time

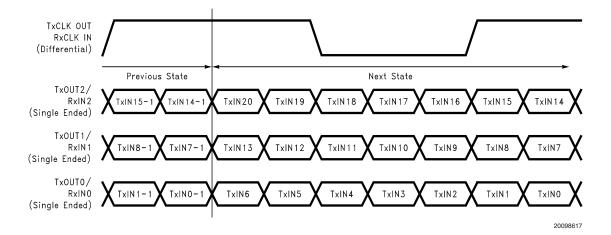

FIGURE 9. 21 Parallel TTL Data Inputs Mapped to LVDS Outputs

FIGURE 10. Transmitter Power Down Delay

FIGURE 11. Transmitter LVDS Output Pulse Position Measurement

## DS90C363B Pin Descriptions — FPD Link Transmitter

| Pin Name             | I/O | No. | Description                                                                                  |

|----------------------|-----|-----|----------------------------------------------------------------------------------------------|

| TxIN                 | I   | 21  | TTL level input. This includes: 6 Red, 6 Green, 6 Blue, and 3 control lines—FPLINE,          |

|                      |     |     | FPFRAME and DRDY (also referred to as HSYNC, VSYNC, Data Enable).                            |

| TxOUT+               | 0   | 3   | Positive LVDS differential data output.                                                      |

| TxOUT-               | 0   | 3   | Negative LVDS differential data output.                                                      |

| FPSHIFT IN           | 1   | 1   | TTL level clock input. The falling edge acts as data strobe. Pin name TxCLK IN.              |

| R_FB                 | 1   | 1   | Programmable strobe select (See Table 1).                                                    |

| TxCLK OUT+           | 0   | 1   | Positive LVDS differential clock output.                                                     |

| TxCLK OUT-           | 0   | 1   | Negative LVDS differential clock output.                                                     |

| PWR DOWN             | 1   | 1   | TTL level input. Assertion (low input) TRI-STATES the outputs, ensuring low current at power |

|                      |     |     | down. See Applications Information section.                                                  |

| V <sub>CC</sub>      | 1   | 3   | Power supply pins for TTL inputs.                                                            |

| GND                  | I   | 4   | Ground pins for TTL inputs.                                                                  |

| PLL V <sub>CC</sub>  | I   | 1   | Power supply pin for PLL.                                                                    |

| PLL GND              | I   | 2   | Ground pins for PLL.                                                                         |

| LVDS V <sub>CC</sub> | 1   | 1   | Power supply pin for LVDS outputs.                                                           |

| LVDS GND             | I   | 3   | Ground pins for LVDS outputs.                                                                |

| NC                   |     | 1   | No connect                                                                                   |

#### **Applications Information**

The DS90C363B are backward compatible with the DS90C363/DS90CF363, DS90C363A/DS90CF363A and are a pin-for-pin replacement.

This device may also be used as a replacement for the DS90CF563 (5V, 65MHz) and DS90CF561 (5V, 40MHz) FPD-Link Transmitters with certain considerations/modifications:

- 1. Change 5V power supply to 3.3V. Provide this supply to the  $V_{CC}$ , LVDS  $V_{CC}$  and PLL  $V_{CC}$  of the transmitter.

- To implement a falling edge device for the DS90C363B, the R\_FB pin (pin 14) may be tied to ground OR left unconnected (an internal pull-down resistor biases this pin low). Biasing this pin to Vcc implements a rising edge device.

#### TRANSMITTER INPUT PINS

The DS90C363B transmitter input and control inputs accept 3.3V LVTTL/LVCMOS levels. They are not 5V tolerant.

#### TRANSMITTER INPUT CLOCK/DATA SEQUENCING

The DS90C363B does not require any special requirement for sequencing of the input clock/data and PD (PowerDown) signal. The DS90C363B offers a more robust input sequencing feature where the input clock/data can be inserted after the release of the PD signal. In the case where the clock/data is stopped and reapplied, such as changing video mode within Graphics Controller, it is not necessary to cycle the PD

signal. However, there are in certain cases where the PD may need to be asserted during these mode changes. In cases where the source (Graphics Source) may be supplying an unstable clock or spurious noisy clock output to the LVDS transmitter, the LVDS Transmitter may attempt to lock onto this unstable clock signal but is unable to do so due the instability or quality of the clock source. The PD signal in these cases should then be asserted once a stable clock is applied to the LVDS transmitter. Asserting the PWR DOWN pin will effectively place the device in reset and disable the PLL, enabling the LVDS Transmitter into a power saving standby mode. However, it is still generally a good practice to assert the PWR DOWN pin or reset the LVDS transmitter whenever the clock/data is stopped and reapplied but it is not mandatory for the DS90C363B.

#### SPREAD SPECTRUM CLOCK SUPPORT

The DS90C363B can support Spread Spectrum Clocking signal type inputs. The DS90C383B outputs will accurately track Spread Spectrum Clock/Data inputs with modulation frequencies of up to 100kHz (max.)with either center spread of  $\pm 2.5\%$  or down spread -5% deviations.

#### **POWER SOURCES SEQUENCE**

In typical applications, it is recommended to have  $V_{\rm CC}$ , LVDS  $V_{\rm CC}$  and PLL  $V_{\rm CC}$  from the same power source with three separate de-coupling bypass capacitor groups. There is no requirement on which VCC entering the device first.

#### Pin Diagram

#### DS90C363B TxIN4 <u>48</u> TxIN3 47 TxIN2 $V_{CC}$ 46 GND TxIN5 45 TxIN1 TxIN6 44 TXINO GND . 43 N/C TxIN7 42 LVDS GND TxIN8 41 Tx0UT0- $V_{\rm CC}$ 40 TxOUTO+ TxIN9 TxIN 10 10 39 Tx0UT1-GND 11 38 TxOUT1+ 37 LVDS V<sub>CC</sub> 36 LVDS GND TxIN11 TxIN 12 13 R\_FB 14 35 Tx0UT2-34 Tx0UT2+ 33 TxCLK OUT-TxIN14 GND 17 32 TxCLK OUT+ TxIN15 18 31 LVDS GND 30 PLL GND TxIN16 29 PLL GND 28 PLL V<sub>CC</sub> TxIN 17 20 V<sub>CC</sub> 21 TxIN18 22 27 PWR DWN TxIN19 23 26 TxCLK IN 25 TxIN20 20098623

#### **Typical Application**

## Pin Diagram (Continued)

TABLE 1. Programmable Transmitter (DS90C363B)

| Pin  | Condition        | Strobe Status       |

|------|------------------|---------------------|

| R_FB | $R_FB = V_{CC}$  | Rising edge strobe  |

| R_FB | R_FB = GND or NC | Falling edge strobe |

MTD48 (Rev E)

##

48-Lead Molded Thin Shrink Small Outline Package, JEDEC Order Number DS90C363BMT NS Package Number MTD48

DETAIL A

| National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| the right at any time without notice to change said circuitry and specifications.                                                            |

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560