🗙 National Semiconductor

# **CLC5506** Gain Trim Amplifier (GTA)

# **General Description**

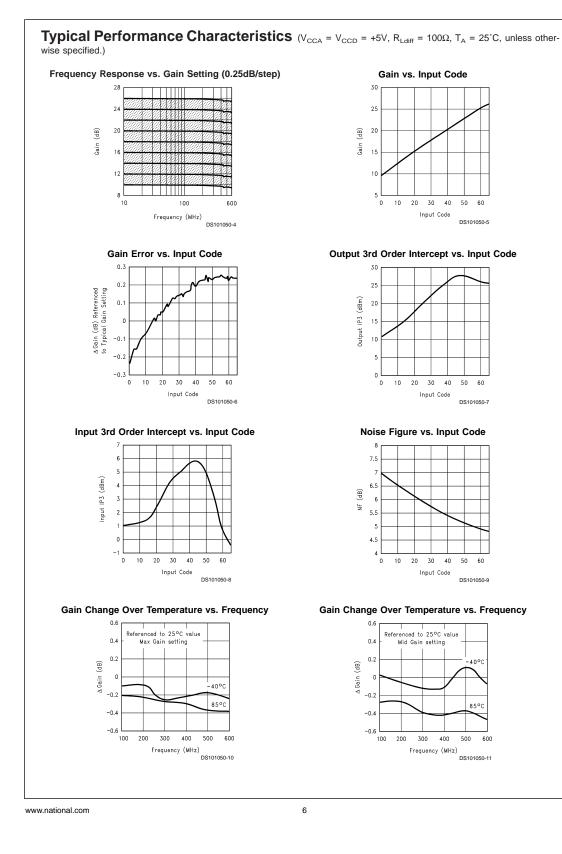

The CLC5506 is a low-noise amplifier with programmable gain for use in cellular base stations, WLL, radar and RF/IF subsystems where gain-control is required to increase the dynamic range. The CLC5506 allows designers to compensate for manufacturing component tolerances and temperature variations in receiver front ends. Maximum amplifier gain is set at 26dB . A three-line MICROWIRE serial interface allows 16dB of attenuation from the max gain setting in precise 0.25dB steps.

The CLC5506 uses a differential input and output, allowing large output swings on a single 5V rail. The differential output is well suited for impedance matching networks driving SAW filters or directly driving differential input analog to digital converters (ADC). The differential output also makes it possible to drive transformers allowing designers the ability to match a wide variety of transmission lines. The output amplifier has excellent output drive with low distortion.

Digital control of the CLC5506 is accomplished using MI-CROWIRE Interface. Data Out and a Load Enable are incorporated so that more than one CLC5506/channel may be programmed per system.

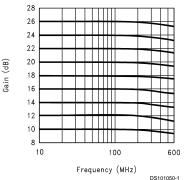

The CLC5506 maintains a 600MHz performance bandwidth over its entire gain and attenuation range from +10dB to +26dB. Gain control is divided into 64 equal steps of 0.25dB and is dB-linear. Output drive and distortion performance are excellent; In a 50Ω system, the third-order output intercept point is +22dBm at nominal gain of 18dB at 25°C. The CLC5506 operates over the industrial temperature range of -40°C to +85°C.

## Features

- 600MHz bandwidth

- 26dB maximum gain @ 150MHz

- 16dB gain control range

- Attenuation step size: 0.25dB

- 4.8dB noise figure @ 26dB

- +22dBm output IP3 @ 18dB gain Digital "dB Linear" gain control

- Supply voltage: 5V

- Supply current: 75mA Supply shutdown: 35µA

- Package: SOIC-14 Typical at 25°C

# Applications

- Cellular base-stations

- Base station repeater

- Wireless Local Loop

- Radar

- Receivers

- IF amplifiers

- Digital IF receiver

- Software radio

- Satellite communications

#### Frequency Response vs. Gain Setting

MICROWIRE<sup>11</sup>

www.national.com

September 1999

| Conne                                                                                                                                                                                                                             | Connection Diagram |                                                                                                                             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLC5506 Pin Diagram                                                                                                                                                                                                               |                    |                                                                                                                             |  |  |  |

| NC $\begin{bmatrix} 1 \bullet & 14 \\ GND_A \end{bmatrix}$ V <sub>CCA</sub><br>GND_A 2 13 GND_A<br>In+ 3 12 Out+<br>In- 4 11 Out-<br>LE 5 10 V <sub>CCD</sub><br>Clock 6 9 GND <sub>D</sub><br>Data In 7 8 Data Out<br>DS101050-3 |                    |                                                                                                                             |  |  |  |

| Top View Pin # Pin Name Description                                                                                                                                                                                               |                    |                                                                                                                             |  |  |  |

| 1                                                                                                                                                                                                                                 | NC                 | No connection                                                                                                               |  |  |  |

| 2                                                                                                                                                                                                                                 | GND <sub>A</sub>   | Analog ground                                                                                                               |  |  |  |

| 3                                                                                                                                                                                                                                 | In+                | Positive differential input                                                                                                 |  |  |  |

| 4                                                                                                                                                                                                                                 | In–                | Negative differential input                                                                                                 |  |  |  |

| 5                                                                                                                                                                                                                                 | LE                 | MICROWIRE load enable input. High impedance CMOS input with Schmitt trigger                                                 |  |  |  |

| 6                                                                                                                                                                                                                                 | Clock              | MICROWIRE clock input. High impedance CMOS input with Schmitt trigger.<br>Data is clocked in on the rising edge of clock.   |  |  |  |

| 7                                                                                                                                                                                                                                 | Data In            | MICROWIRE data input. High impedance CMOS input with Schmitt trigger.<br>Binary serial data. Data entered Power Down first. |  |  |  |

| 8                                                                                                                                                                                                                                 | Data Out           | MICROWIRE data output. High impedance CMOS input with Schmitt trigger.                                                      |  |  |  |

| 9                                                                                                                                                                                                                                 | GND <sub>D</sub>   | Digital ground                                                                                                              |  |  |  |

# **Ordering Information**

V<sub>CCD</sub> Out-

Out+

$\mathsf{GND}_\mathsf{A}$

$V_{\rm CCA}$

10 11

12

13

14

| Package | Temperature Range<br>-40°C to +85°C | Transport Media          | NSC Drawing                   |

|---------|-------------------------------------|--------------------------|-------------------------------|

| SO-14   | CLC5506IM                           | Rails                    | M14a                          |

|         | CLC5506IMX                          | 2.5k Units Tape and Reel |                               |

|         | CLC5506PCASM                        |                          | Fully loaded evaluation board |

Digital supply voltage

Analog supply voltage

Analog ground

Negative differential Output

Positive differential output

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD tolerance(Note 2)           |                       |

|---------------------------------|-----------------------|

| Human body model                | 2.5KV                 |

| Machine model                   | 250V                  |

| Differential input voltage      | +/-1V                 |

| Supply voltage                  | -0.3 to +6V           |

| Digital input voltage           | –0.3V to $V_{\rm CC}$ |

| Analog input voltage            | –0.3V to $V_{\rm CC}$ |

| Output short circuit duration   | Infinite              |

| Lead temperature (soldering, 10 |                       |

| sec)                            | +300°C                |

|                                 |                       |

–65°C to 150°C Storage temperature range 155°C Junction temperature Differential voltage between any <200mV two inputs **Operating Ratings** (Note 1)

| Supply voltage (pins 10 and 14)           | 5V +/- 10%      |

|-------------------------------------------|-----------------|

| Ambient temperature range                 | -40°C to +85°C  |

| Junction Temperature Range                | -40°C to +150°C |

| Package thermal resistance, $\theta_{JA}$ | 127°C/W         |

# **Electrical Characteristics**

These conditions apply unless otherwise specified: T  $_{\rm J}$  = 25°C, V<sub>CCA</sub> = V<sub>CCD</sub> = +5V: Gain = 25.75dB, R<sub>Ldiff</sub> = 100 $\Omega$ , Pin = -30dBm (Note 6),(Note 7).

| Symbol     | Parameter                                 | Conditions                                                      | Typ<br>(Note 3) | Limit<br>(Note 4) | Units      |

|------------|-------------------------------------------|-----------------------------------------------------------------|-----------------|-------------------|------------|

| Analog I/C | Response/Distortion/No                    |                                                                 |                 |                   |            |

| riequency  | upper –3dB bandwidth                      | All Gain Codes                                                  | 600             |                   | MHz        |

|            | upper –1dB bandwidth                      | All Gain Codes                                                  | 000             | 400               | MHz        |

|            | gain flatness in any<br>1MHz band         | 10MHz < f < 600MHz, All Gain<br>Codes                           | 0.003           |                   | dB         |

|            | group delay                               | 50MHz < f < 600MHz                                              | 1.5             |                   | nsec       |

|            | group delay ripple                        | 50MHz < f < 600MHz                                              | 0.5             |                   | nsec       |

|            | output third order<br>intercept point     | 18dB Gain, f = 110MHz                                           | 22              |                   | dBm        |

|            | noise figure                              | Gain = 25.75dB, (Note 6)                                        | 4.8             |                   | dB         |

|            |                                           | Gain = 18dB, (Note 6)                                           | 5.7             |                   | dB         |

|            |                                           | Gain = 10dB, (Note 6)                                           | 7.0             |                   | dB         |

|            | 1dB output<br>compression point           | 150MHz                                                          | 4.0             |                   | dBm        |

|            | 2 <sup>nd</sup> harmonic distortion       | Pin = -30 dBm, fc = 200MHz<br>@ Gain = 25.75dB<br>@ Gain = 10dB | 46<br>46        |                   | dBc<br>dBc |

|            | 3 <sup>rd</sup> harmonic distortion       | Pin = -30 dBm, fc = 200MHz<br>@ Gain = 25.75dB<br>@ Gain = 10dB | 49<br>56        |                   | dBc<br>dBc |

|            | Input/Output Isolation<br>power down mode | Full frequency band                                             | 45              |                   | dB         |

| Gain Para  | meters: (Note 5)                          |                                                                 |                 |                   |            |

|            | maximum gain                              | Full temperature range                                          | 25.75           |                   | dB         |

|            | minimum gain                              | Full temperature range                                          | 10              |                   | dB         |

|            | gain step size                            | Full temperature range                                          | 0.25            |                   | dB         |

|            | accuracy of gain setting                  | @ 25°C                                                          | ±0.05           |                   | dB         |

|            | gain variation over temperature           | Full temperature range                                          | ±0.5            |                   | dB         |

| Input/Outp | out Characteristics:                      |                                                                 |                 |                   |            |

|            | input resistance                          | Differential                                                    | 200             |                   | Ω          |

|            | input capacitance                         | Differential                                                    | 0.5             |                   | pF         |

| out<br>out<br>Logic I/O<br>clor<br>dat                                              | tharacteristics:<br>tput resistance<br>tput capacitance<br>ck speed                  | Differential<br>Differential<br>Maximum                                                                          | (Note 3)<br>5K<br>0.5 | (Note 4) | Ω<br>pF |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------|

| out<br>out<br>.ogic I/O<br>clor<br>dat                                              | tput resistance<br>tput capacitance                                                  | Differential                                                                                                     |                       |          |         |

| .ogic I/O<br>cloudat                                                                |                                                                                      |                                                                                                                  | 0.5                   |          | pF      |

| clo<br>dat                                                                          | ck speed                                                                             | Movimum                                                                                                          | I                     |          |         |

| dat                                                                                 | ck speed                                                                             | Movimum                                                                                                          |                       |          |         |

|                                                                                     |                                                                                      | IVIAXIIIIUIII                                                                                                    | 1                     |          | MHz     |

| un                                                                                  | ta to clock setup<br>ie, T <sub>CS</sub>                                             | Minimum                                                                                                          | 50                    |          | nsec    |

|                                                                                     | ta to clock hold<br>ie, T <sub>CH</sub>                                              | Minimum                                                                                                          | 10                    |          | nsec    |

|                                                                                     | ck pulse width high,                                                                 | Minimum                                                                                                          | 50                    |          | nsec    |

|                                                                                     | ck pulse width low,                                                                  | Minimum                                                                                                          | 50                    |          | nsec    |

| clo                                                                                 | to load enable                                                                       | Minimum                                                                                                          | 50                    |          | nsec    |

|                                                                                     | h level input<br>tage                                                                |                                                                                                                  | 0.7 V <sub>CCD</sub>  |          | V       |

| low                                                                                 | v level input voltage                                                                |                                                                                                                  | 0.3 V <sub>CCD</sub>  |          | V       |

| -                                                                                   | gh level input<br>rrent                                                              |                                                                                                                  | ±1.0                  |          | μΑ      |

| low                                                                                 | v level input current                                                                |                                                                                                                  | ±1.0                  |          | μA      |

| -                                                                                   | h level output<br>tage                                                               | Isource = 0.5mA                                                                                                  | V <sub>CCD</sub> -0.8 |          | V       |

|                                                                                     | v level output<br>tage                                                               | Isink = 0.5mA                                                                                                    | 0.4                   |          | V       |

| OC Characteris                                                                      | stics:                                                                               |                                                                                                                  |                       |          |         |

| Su                                                                                  | pply current                                                                         |                                                                                                                  | 75                    | 95       | mA      |

| Su                                                                                  | pply current in                                                                      |                                                                                                                  | 35                    | 100      | μΑ      |

|                                                                                     | wer down mode                                                                        | limits beyond which damage to the device                                                                         |                       |          |         |

| Note 3: Typical va<br>Note 4: All limits<br>Note 5: AC test p<br>Note 6: Refer to t | alues represent the most lil<br>are guaranteed by testing operformed at 400MHz unles | or statistical analysis, unless otherwise not<br>s otherwise noted.<br>of transformers is excluded from the meas | ed.                   |          |         |

# **APPLICATION NOTE**

### Description

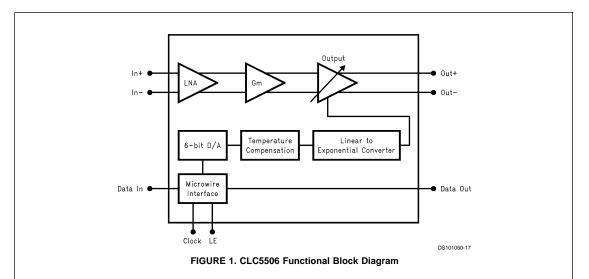

Figure 1 above shows the CLC5506 functional block diagram overview.

The LNA (Low Noise Amplifier) is responsible for maintaining a nominal input impedance of 200 $\Omega$  with minimum noise contribution and some finite and fixed amount of gain (-4). Exceptional Noise Figure (NF) performance of 4.8dB (@ Gain = 25.75dB) is achieved by utilizing an active impedance matching circuit technique which overcomes the inevitable 3dB NF penalty when using passive shunt matching.

The LNA stage is immediately followed by a transconductance stage (Gm) which then converts the LNA's voltage output into a differential current output with fixed gain.

The 6-bit D/A converter, which processes the digital code read into the device using the MICROWIRE interface, consists of a 6-bit R2R ladder. In order to achieve true "Linear in dB" gain control at the output, the D/A converter output is processed by a "Linear to Exponential" converter block be-

fore being used to set the gain of the input signal. The "Linear to Exponential" block and the "Temperature Compensation" blocks work in conjunction to achieve gain stability over the temperature range. Finally, the output stage consists of a variable gain cell with open Collector output. This variable gain cell sets the signal channel gain in accordance with the value of the digital code.

#### Gain Control

The CLC5506 minimum gain is at 10dB nominal. There are a total of 64 distinct gain control codes possible (serial data input through Data In pin) at 0.25dB/code resulting in a maximum nominal gain of 25.75dB.

Therefore, the overall gain can be written as:

Gain (dB) = 10dB +  $N_{\rm code}$  \* 0.25 (dB/code) where  $N_{\rm code}$  refers to the decimal equivalent of the 6-bit gain control code.

| Gain | Typical Gain Setting (dB) | Note                 |

|------|---------------------------|----------------------|

| 0    | 10                        | Minimum Gain Setting |

| 1    | 10.25                     |                      |

| 2    | 10.5                      |                      |

| ***  | ***                       |                      |

| К    | 10 + 0.25 <sup>*</sup> K  |                      |

| ***  | ***                       |                      |

| 62   | 25.50                     |                      |

| 63   | 25.75                     | Maximum Gain Setting |

TABLE 1.

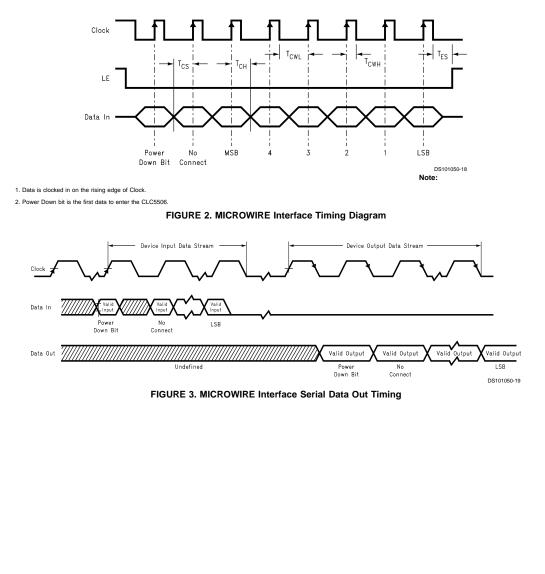

#### Power Down

The CLC5506 is able to go to a Power Down mode in order to minimize its power consumption to a fraction of its nominal value. The Power Down mode is activated through the MI-CROWIRE interface by clocking in a "1" into the Power Down shift register prior to allowing LE (pin 5) to go high. Refer to *Figure 2* and *Figure 3* for more information.

In Power Down mode, the CLC5506 sinks less than  $35\mu$ A. The CLC5506 will wake up to the requested gain level specified by Data In through the MICROWIRE interface.

When  $V_{\rm CC}$  is first applied, the device is configured such that it would always "wake up" with a nominal gain of 17.75dB ( $N_{\rm code}$  = 3).

# APPLICATION NOTE (Continued)

#### MICROWIRE<sup>™</sup> Interface

Data In along with the Clock, LE, and Data Out, is used for the following purposes:

Setting the 6-bit gain control code

Putting the device into a Power Up/Down mode to minimize power consumption

Daisy chain several CLC5506 or other MICROWIRE Interface devices through the Data Out pin

The MICROWIRE interface timing diagram along with the bit assignment of all 8 bits is shown in *Figure 2*. The interface is active only when LE (pin 5) is low; otherwise, the interface is inactive (Clock and Data In are ignored) and the CLC5506 gain is the current content of the 6 bits already read into the device.

With LE low, each successive positive transition of Clock will read the value of the Data In into a series of 8 single bit shift registers. In order to load all 8 registers, 8 Clock transitions are required after which, when LE is allowed to go High, the new values in the shift registers are latched to determine the device gain setting (or Power Down state). New data can be shifted into the device with the present gain setting not affected as long as LE is held low.

Data from the last register in the chain is clocked out on Data Out pin on the negative transitions of Clock as shown in *Figure 3*. This enables several MICROWIRE Interface devices to be daisy chained and controlled from a single bus master. The maximum clock frequency (Clock pin) is 1MHz.

# APPLICATION NOTE (Continued)

#### Differential Input and Output Considerations

The CLC5506 typical application requires DC blocking capacitors for both inputs and outputs to main internal DC biasing points.

The input impedance between the differential inputs (IN+, IN-) is 200 $\Omega$ //0.5pF. Since the 0.5pF capacitance can be neglected in the VHF band, a 1:4 impedance ratio balun can be used to transform a 50 $\Omega$  source to the 200 $\Omega$  differential inputs of CLC5506 for wide band design.

The CLC5506 has a pair of open collector differential outputs (OUT+, OUT-). DC biasing is achieved through an RF inductor. The RF inductor acts as a choke to block RF leakage and interference. An external resistor across the differential out-

puts is used to set the output resistance of CLC5506. Wideband output matching to an unbalanced 50 $\Omega$  load can be achieved by using a 1:n balun. A 1:4 impedance ratio balun is used when a 200 $\Omega$  external resistor is used in a 50 $\Omega$  system.

Although the CLC5506 can be used as a single-ended device by grounding one of the inputs through a capacitor, the noise figure would be severely degraded by 6dB.

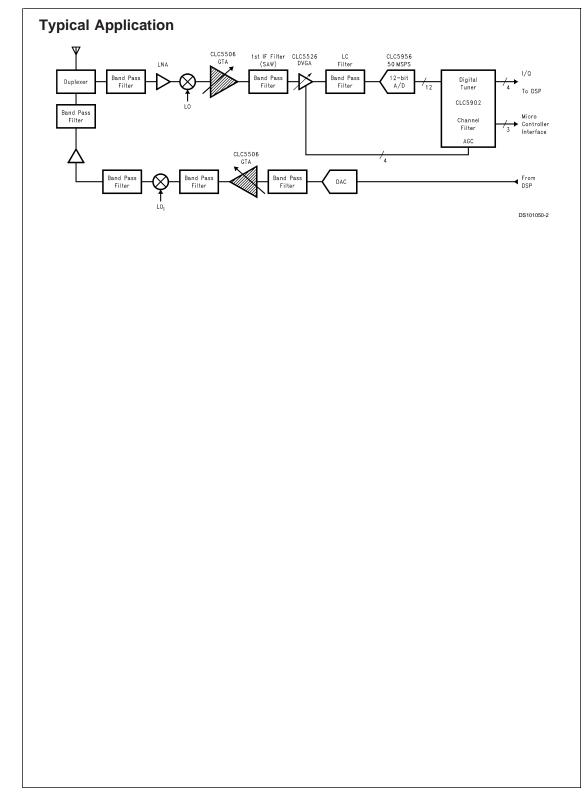

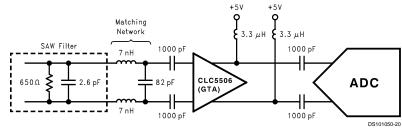

The CLC5506 can also directly interface to balanced devices, like SAW filters and ADCs. Narrowband design example with ADC CLC5956 and SAW filter is provided below. The component values of matching inductors and capacitors depend on the actual input/output impedance of the SAW filter, ADC, PWB properties, layout and frequency band.

FIGURE 4. Narrow band design example with balanced SAW filter and ADC

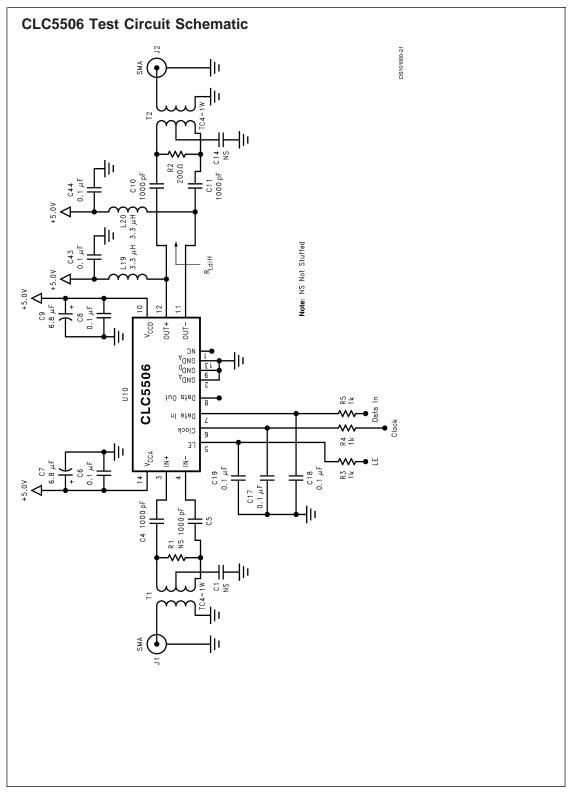

#### **CLC5506 Evaluation Board**

A proper printed circuit layout is essential for achieving high frequency performance. To expedite evaluation, an assembled and tested evaluation kit CLC5506PCASM is available for sale. See application note AN-1138 for technical details of evaluation kit. Order information and application note is available on the Web at http://www.national.com