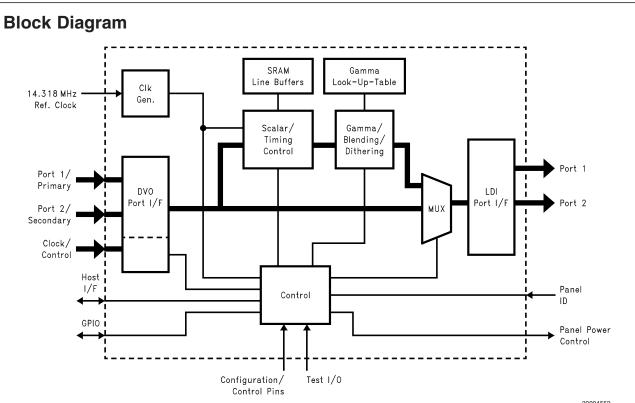

### DS90C2501 Transmitter with built-in scaler for LVDS Display Interface (LDI) **General Description** Features

The DS90C2501 is a highly integrated scaling IC with LVDS transmitter with a scaled resolution up to SXGA+ for single pixel input. The DS90C2501 is a video controller hub designed to be compatible with Graphic Memory Controller Hub (GMCH). The input interface can be single or dual DVO port (12 pin per port). The high quality cubic zoom engine scales the input graphics into the desired/optimal output resolution up to 1400x1050 resolution. Advanced video digital signal processing provides gamma correction, and dithering for the display output. A two-wire serial interface is used to communicate with the host system. The dual high speed LVDS channels supports single pixel in-single pixel out, single pixel in-dual pixel out, and dual pixel in-dual pixel out transmission modes. The DS90C2501 complies to Open LDI standard, and can be paired up with DS90CF388 receiver or FPD8531x/FPD8731x series integrated timing controller or FPDLink LVDS receivers such as DS90CF364/ DS90CF384A/DS90CF384/DS90CF384A. The LVDS output is similar to DS90C387 and DS90C387R. Thus, this transmitter can be paired up with DS90CF388, receiver of 112MHz LDI chipset or FPD-Link Receivers in non-DC Balance mode operation which provides GUI/LCD panel/mother board vendors a wide choice of inter-operation with LVDS based TFT panels.

This chip is an ideal solution to solve EMI and cable size problems for high-resolution flat panel applications. It provides a reliable industry standard interface based on LVDS technology that delivers the bandwidth needed for highresolution panels while maximizing bit times, and keeping clock rates low to reduce EMI and shielding requirements. For more details, please refer to the "Applications Information" section of this datasheet.

- Complies with Open LDI and GMCH DVO specification for digital display interfaces

- 25 to 65 MHz clock in single pixel in to single pixel out operation.

- 50 to 130 MHz clock in single pixel in to dual pixel out operation.

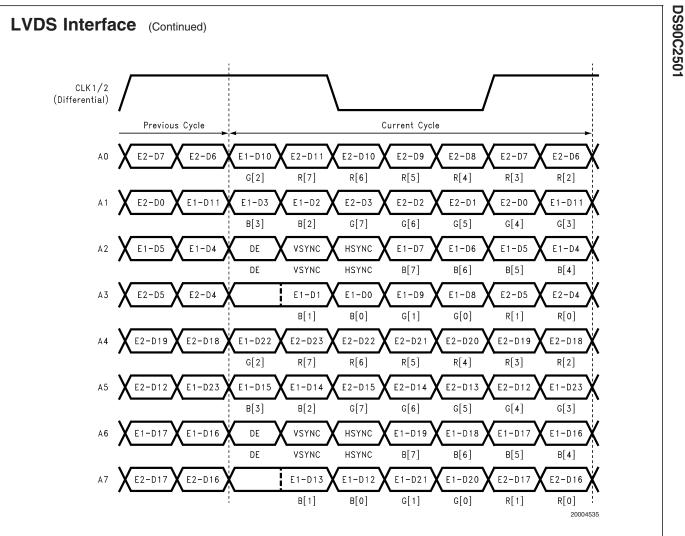

- Support 24bit/48bit color TFT LCD with Conventional and Non-Conventional Color Mappings.

- Support 16bit/32bit color TFT LCD.

- Single pixel transmitter inputs support single pixel GUI interface.

- Up scaling/panel fitting supports VGA to SXGA+ output in single pixel input mode at 640x480@60Hz, 800x600@60Hz, 1024x768@60Hz, 1280x1024@60Hz, 1400x1050@60Hz.

- Independent horizontal and vertical scaling.

- Support dithering (available for 6-bit color only), programmable smoothing and anti-aliasing filter.

- Programmable digital sharpness, edge enhancement and contrast control via gamma correction.

- Allow 2% at 200KHz spread spectrum clocking, rejects cycle-to-cycle jitter (+/- 20% of input data bit time).

- Programmable LCD panel power sequencing.

- Support low voltage swing signal level (1V to 1.8V), 2.5V and 3.3V LVTTL level on CLKINP, CLKINM, D0 to D23, DE, HSYNC and VSYNC pins

- Support 2.5V/3.3V LVTTL level on configuration pins

- Support 3.3V LVTTL level on GPIO pins

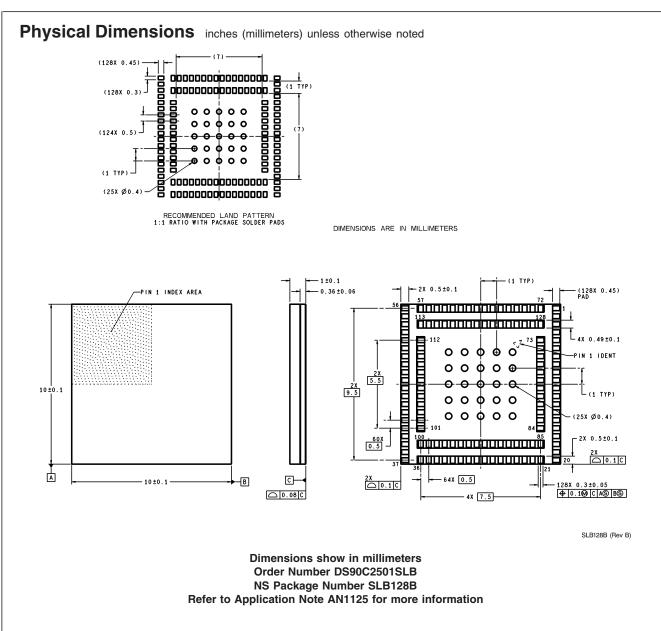

- Available in 10mm x 10mm x 1mm 128pin thermally enhanced CSP package.

- Two-wire serial communication interface is active during normal as well as power down mode and support data rates up to 400KHz.

- TIA/EIA-644, Open LDI, DVO compliance.

TRI-STATE® is a registered trademark of National Semiconductor Corporation DVO is a registered trademark of Intel Corporation AGP or 4x AGP is a registered trademark of Intel Corporation.

### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage ( $V_{CC}$ )         | -0.3V to +2.8V                    |

|-------------------------------------|-----------------------------------|

| Supply Voltage (V <sub>CC3V</sub> ) | -0.3V to +3.6V                    |

| CMOS/TTL Input Voltage              | –0.3V to $V_{\text{CC3V}}$        |

| CMOS/TTL Output                     |                                   |

| Voltage                             | –0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Driver Output                  |                                   |

| Voltage                             | –0.3V to (V <sub>CC</sub> + 0.3V) |

| LVDS Output Short                   |                                   |

| Circuit Duration                    | Continuous                        |

| Junction Temperature                | +150°C                            |

| Storage Temperature                 | −65°C to +150°C                   |

| Lead Temperature                    |                                   |

| (Soldering, 4 sec.)                 | +260°C                            |

|                                     |                                   |

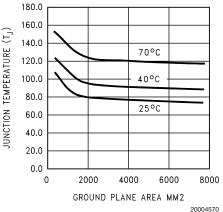

| Typical Package Power Dissipation Capacity @ 70°C |   |

|---------------------------------------------------|---|

| and Max V <sub>CC</sub>                           |   |

| 128 CSP Package:                                  |   |

| DS00C2501 1 8M                                    | 1 |

DS90C2501 1.8W Maximum Operating Case Temperature: 97°C (measured at top center of package) ESD Rating: DS90C2501 (HBM, 1.5kΩ, 100pF) > 2 kV (EIAJ, 0Ω, 200pF) > 250 V

### Recommended Operating Conditions

|                                         | Min   | Nom | Мах   | Units      |

|-----------------------------------------|-------|-----|-------|------------|

| All Supply Voltage except               | 2.250 | 2.5 | 2.750 | V          |

| (V <sub>CC3V</sub> )                    |       |     |       |            |

| V <sub>CC3V</sub> Supply Voltage        | 3.0   | 3.3 | 3.6   | V          |

| Operating Free Air                      |       |     |       |            |

| Temperature (T <sub>A</sub> )           | 0     | +25 | +70   | °C         |

| Supply Noise Voltage (V <sub>CC</sub> ) |       |     | 100   | $mV_{P-P}$ |

| up to 33Mhz                             |       |     |       |            |

### **DC** Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol               | Parameter                                                             | Conditions                         | Min                   | Тур                | Max                                              | Unite |

|----------------------|-----------------------------------------------------------------------|------------------------------------|-----------------------|--------------------|--------------------------------------------------|-------|

| LVCMOS/L             | VTTL DC SPECIFICATIONS (                                              | All input pins when operate in L   | VTTL level except [   | OUAL pin. I        | Note: On ID0,                                    | ID1   |

| pins have            | typical 30K ohm internal pull                                         | down, and ID2 and ID3 pins hav     | e typical 3K ohm ir   | nternal pull       | -down.)                                          |       |

| V <sub>IH</sub>      | High Level Input Voltage                                              | $V_{\text{REF}} = V_{\text{CC3V}}$ | 2.0                   |                    | V <sub>CC3V</sub>                                | V     |

| V <sub>IL</sub>      | Low Level Input Voltage                                               | $V_{\text{REF}} = V_{\text{CC3V}}$ | -0.3                  |                    | 0.8                                              | V     |

| V <sub>CL</sub>      | Input Clamp Voltage                                                   | I <sub>CL</sub> = 18 mA            |                       | -0.9               | -1.5                                             | V     |

| I <sub>IN</sub>      | Input Current                                                         | $V_{IN} = 0.4V$ , or $V_{CC}$      |                       | +1.8               | +15                                              | μA    |

|                      |                                                                       | V <sub>IN</sub> = GND              | -15                   | 0                  |                                                  | μA    |

| LVCMOS/L             | VTTL DC SPECIFICATIONS f                                              | or DUAL pin, pin35                 |                       |                    |                                                  |       |

| V <sub>IH</sub> DUAL | High Level Input Voltage (for<br>dual pixel in to dual pixel<br>out). | PD = V <sub>CC3V</sub>             | 2.0                   |                    | V <sub>cc</sub>                                  | V     |

| V <sub>IM</sub> DUAL | High Level Input Voltage (for single pixel in to dual pixel out).     | $\overline{PD} = V_{CC3V}$         | ½V <sub>CC</sub> −0.1 | ¹⁄₂V <sub>CC</sub> | <sup>1</sup> / <sub>2</sub> V <sub>CC</sub> +0.1 | V     |

| V <sub>IL</sub> DUAL | High Level Input Voltage (for single pixel in to single pixel out).   | $\overline{PD} = V_{CC3V}$         | 0                     |                    | 0.4                                              | V     |

| V <sub>CL</sub>      | Input Clamp Voltage                                                   | I <sub>CL</sub> = 18 mA            |                       | -0.9               | -1.5                                             | V     |

| I <sub>IN</sub>      | Input Current                                                         | $V_{IN} = 0.4V, V_{CC}$            |                       | 1.8                | 15                                               | μA    |

|                      |                                                                       | V <sub>IN</sub> = Gnd              | -15                   | 0                  |                                                  | μA    |

| LVCMOS/L             | VTTL DC SPECIFICATIONS f                                              | or MSEN, pin 98                    |                       |                    |                                                  |       |

| V <sub>OL</sub>      | Low level Open Drain Output<br>Voltage                                | I <sub>OL</sub> = 2 mA             |                       | 0.1                | 0.3                                              | V     |

| LVCMOS/L             | VTTL DC SPECIFICATIONS (                                              | Pin 62 to pin 69 when operate in   | 3.3V LVTTL level)     |                    | · · ·                                            |       |

| V <sub>OH</sub>      | High Level Input Voltage                                              | I <sub>OL</sub> = 2 mA             | 2.2                   | 2.95               |                                                  | V     |

| V <sub>OL</sub>      | Low Level Input Voltage                                               |                                    |                       | 0.055              | 0.4                                              | V     |

| l <sub>os</sub>      | Output Short Circuit Current                                          | V <sub>OUT</sub> = 0V              |                       | -50                | -120                                             | mA    |

| Symbol            | Parameter                                                                                | Cond                                                                                                        | itions                                      | Min                         | Тур                 | Мах                         | Units |

|-------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------|---------------------|-----------------------------|-------|

| Low Volta         | ge Level DC SPECIFICATIONS                                                               | 6 (pins D0 to D23,                                                                                          | CLKINP, CLKINM,                             | DE, HSYNC,V                 | SYNC)               |                             | 1     |

| V <sub>DDQ</sub>  | Low Swing Voltage                                                                        | from GMCH                                                                                                   |                                             | 1                           |                     | +1.8                        | V     |

| V <sub>ILSH</sub> | Low Swing High Level Input<br>Voltage                                                    |                                                                                                             |                                             | V <sub>REF</sub> +<br>100mV |                     | $V_{DDQ}$                   | V     |

| V <sub>ILSL</sub> | Low Swing Low Level Input<br>Voltage                                                     |                                                                                                             |                                             | 0                           |                     | V <sub>REF</sub> -<br>100mV | V     |

| V <sub>REF</sub>  | Differential Input Reference<br>Voltage                                                  |                                                                                                             |                                             | 0.475                       | 1/2V <sub>DDQ</sub> | 0.945                       | V     |

| LVDS DRI          | VER DC SPECIFICATIONS (O                                                                 | utput pins AnP, An                                                                                          | M, CLKnP and CL                             | KnM)                        | 1                   |                             | 1     |

| V <sub>OD</sub>   | Differential Output Voltage                                                              | R <sub>L</sub> = 100Ω                                                                                       |                                             | 250                         | 345                 | 450                         | mV    |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between<br>Complimentary Output<br>States                      |                                                                                                             |                                             |                             | 3                   | 35                          | mV    |

| Vos               | Offset Voltage                                                                           |                                                                                                             |                                             | 1.125                       | 1.32                | 1.475                       | V     |

| $\Delta V_{OS}$   | Change in V <sub>OS</sub> between<br>Complimentary Output<br>States                      |                                                                                                             |                                             |                             | 1.5                 | 35                          | mV    |

| l <sub>os</sub>   | Output Short Circuit Current                                                             | $V_{OUT} = 0V$                                                                                              |                                             | 0                           | -8.5                | -15                         | mA    |

| l <sub>oz</sub>   | Output TRI-STATE Current                                                                 | $\overline{PD} = 0V, V_{OUT} = 0$                                                                           | 0V or V <sub>CC</sub>                       |                             | ±0.1                | ±10                         | μA    |

| SUPPLY C          | URRENT                                                                                   |                                                                                                             |                                             |                             |                     |                             |       |

| I <sub>cc</sub> 1 | Transmitter Supply Current<br>when data input and clock<br>input are at Low Swing level. | $R_L = 100\Omega, C_L =$<br>5 pF, DUAL pin<br>= GND, BAL =                                                  | f = 65MHz,<br>scaler off, 2.75V<br>supply   |                             | 70                  | 120                         | mA    |

|                   |                                                                                          | GND, one 12bit<br>input, Pattern<br><i>Figure 1</i>                                                         | f = 65 MHz,<br>scaler off, 3.6V<br>supply   |                             | 38                  | 90                          | mA    |

| I <sub>cc</sub> 2 | Transmitter Supply Current<br>when data input and clock<br>input are at Low Swing level. | $R_L = 100Ω, C_L =$<br>5 pF, DUAL pin<br>= ½ VCC, BAL =                                                     | f = 108MHz,<br>scaler off, 2.75V<br>supply  |                             | 85                  | 130                         | mA    |

|                   |                                                                                          | GND, one 12bit<br>input, Pattern<br><i>Figure 1</i>                                                         | f = 108 MHz,<br>scaler off, 3.6V<br>supply. |                             | 75                  | 130                         | mA    |

| I <sub>CC</sub> 3 | Transmitter Supply Current<br>when data input and clock<br>input are at Low Swing level. | $R_{L} = 100\Omega, C_{L} = 5 \text{ pF, DUAL pin} = \text{GND, BAL} = \text{GND, one 12bit} \text{ input}$ | f = 65 MHz,<br>scaler on, 2.75V<br>supply   |                             | 330                 | 415                         | mA    |

| I <sub>cc</sub> 4 | Transmitter Supply Current<br>when data input and clock<br>input are at Low Swing level. | $R_L = 100Ω$ , $C_L = 5$ pF, DUAL pin<br>= ½V <sub>CC</sub> , BAL = GND, one 12bit<br>input                 | f = 108 MHz,<br>scaler on, 2.75V<br>supply  |                             | 483                 | 610                         | mA    |

| ICCTZ             | Transmitter Supply Current<br>Power Down                                                 |                                                                                                             |                                             |                             | 75                  |                             | μA    |

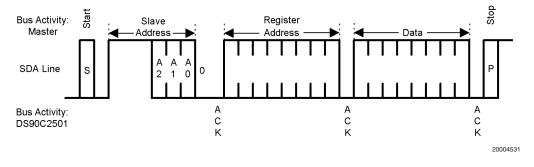

### **Two-Wire Serial Communication Interface**

Unless otherwise noted, below specifications apply for  $V_{\rm CC} 3V$  pin = 3.0V to 3.6V.

| Symbol              | Parameter                           | Conditions            | Min | Тур  | Max | Units |

|---------------------|-------------------------------------|-----------------------|-----|------|-----|-------|

| V <sub>IN</sub> (1) | Logical " 1 " input voltage         |                       | 2.1 |      |     | V     |

| V <sub>IN</sub> (0) | Logical " 0 " input voltage         |                       |     |      | 0.8 | V     |

| V <sub>OL</sub>     | Serial Bus Low level output voltage | I <sub>OL</sub> = 3mA |     | 0.1  | 0.4 | V     |

|                     |                                     | $I_{OL} = 6mA$        |     | 0.15 | 0.6 | V     |

### **Recommended DVO Port Input Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                             |            | Min   | Тур  | Max   | Units |

|--------|---------------------------------------|------------|-------|------|-------|-------|

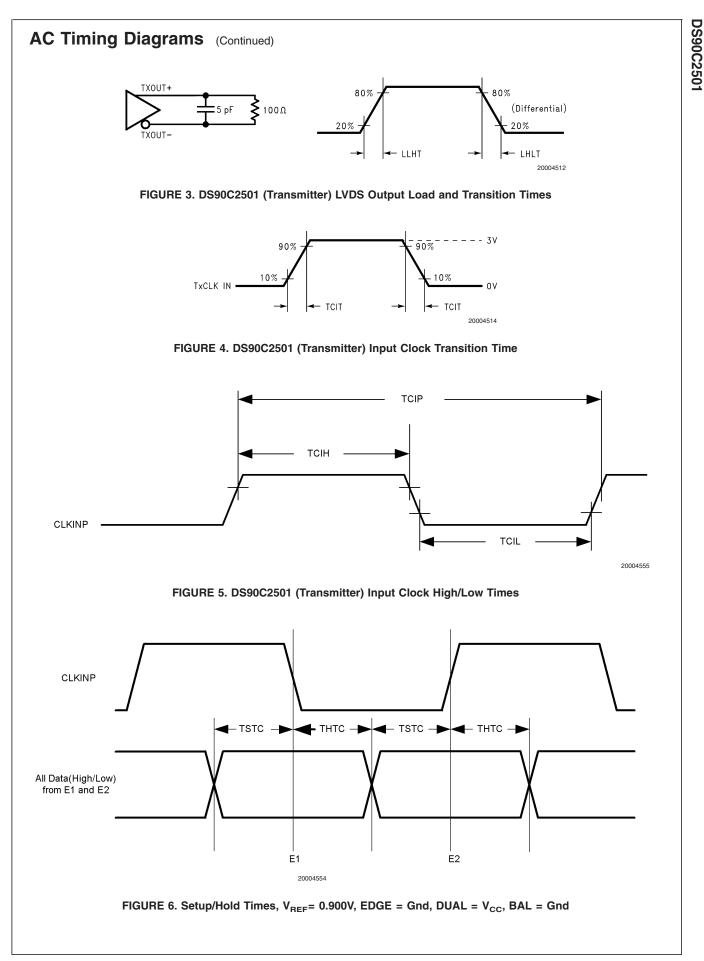

| TCIT   | TxCLK IN Transition Time (Figure 4)   | DUAL = Gnd | 0.8   | 1.2  | 2.4   | ns    |

| TCIP   | TxCLK IN Period (Figure 5)            | DUAL = Gnd | 5.9   | Т    | 40    | ns    |

| TCIH   | TxCLK in High Time (Figure 5)         |            | 0.35T | 0.5T | 0.65T | ns    |

| TCIL   | TxCLK in Low Time (Figure 5)          |            | 0.35T | 0.5T | 0.65T | ns    |

| TXIT   | D0 to D23 Transition Time             |            |       | 1    |       | ns    |

| VDDQ   | Low Swing Voltage Amplitude from GMCH |            | 1.0   |      | 1.8   | V     |

AC Switching Characteristics Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol | Parameter                                                                                           |                                      | Min                | Тур              | Max                | Units |

|--------|-----------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|------------------|--------------------|-------|

| LLHT   | LVDS Low-to-High Transition Time (Figure 3                                                          | 3). (Note 7)                         |                    | 0.14             | 0.8                | ns    |

| LHLT   | LVDS High-to-Low Transition Time (Figure 3                                                          | 3). (Note 7)                         |                    | 0.11             | 0.8                | ns    |

| TBIT   | Transmitter Output Bit Width                                                                        | DUAL pin = V <sub>CC</sub> or<br>Gnd |                    | 1/7 TCIP         |                    | ns    |

|        |                                                                                                     | DUAL pin = $\frac{1}{2}V_{CC}$       |                    | 2/7 TCIP         |                    | ns    |

| TCCS   | TxOUT Channel to Channel Skew                                                                       |                                      |                    | 100              |                    | ps    |

| TPPOS0 | Transmitter Output Pulse Position for Bit 0<br>(previous cycle) from CLK1P rising edge<br>(Note 7). | f = 65  MHz, DUAL pin<br>= $V_{CC}$  | -0.49              | 0                | +0.49              | ns    |

| TPPOS1 | Transmitter Output Pulse Position for Bit1<br>(previous cycle) from CLK1P rising edge.<br>(Note 7)  | f = 65  MHz, DUAL pin<br>= $V_{CC}$  | (1/7)TCIP<br>-0.49 | (1/7)TCIP        | (1/7)TCIP<br>+0.49 | ns    |

| TPPOS2 | Transmitter Output Pulse Position for Bit2<br>from CLK1P rising edge. (Note 7)                      | f = 65 MHz, DUAL pin<br>= $V_{CC}$   | (2/7)TCIP<br>-0.49 | (2/7)TCIP        | (2/7)TCIP<br>+0.49 | ns    |

| TPPOS3 | Transmitter Output Pulse Position for Bit3 from CLK1P rising edge. (Note 7)                         | f = 65 MHz, DUAL pin<br>= $V_{CC}$   | (3/7)TCIP<br>-0.49 | (3/7)TCIP        | (3/7)TCIP<br>+0.49 | ns    |

| TPPOS4 | Transmitter Output Pulse Position for Bit4 from CLK1P rising edge. (Note 7)                         | f = 65 MHz, DUAL pin<br>= $V_{CC}$   | (4/7)TCIP<br>-0.49 | (4/7)TCIP        | (4/7)TCIP<br>+0.49 | ns    |

| TPPOS5 | Transmitter Output Pulse Position for Bit5 from CLK1P rising edge. (Note 7)                         | f = 65 MHz, DUAL pin<br>= $V_{CC}$   | (5/7)TCIP<br>-0.49 | (5/7)TCIP        | (5/7)TCIP<br>+0.49 | ns    |

| TPPOS6 | Transmitter Output Pulse Position for Bit6<br>from CLK1P rising edge. (Note 7)                      | f = 65 MHz, DUAL pin<br>= $V_{CC}$   | (6/7)TCIP<br>-0.49 | (6/7)TCIP        | (6/7)TCIP<br>+0.49 | ns    |

| TSTC   | DxIN Setup to CLKINP (Figure 6) (Note 7)                                                            |                                      | 0.8                |                  |                    | ns    |

| ТНТС   | DxIN Hold to CLKINP (Figure 6) (Note 7)                                                             |                                      | 0.8                |                  |                    | ns    |

| TJCC   | Transmitter Jitter Cycle-to-cycle (Note 4)                                                          | f = 85 MHz, DUAL pin<br>= Gnd        |                    | 114              |                    | ps    |

|        |                                                                                                     | f = 54 MHz, DUAL pin<br>= $V_{CC}$   |                    | 114              |                    | ps    |

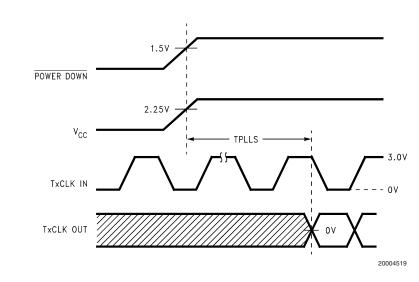

| TPLLS  | Transmitter Phase Lock Loop Set (Figure 7)                                                          | (Note 7)                             |                    |                  | 10                 | ms    |

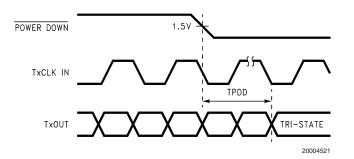

| TPDD   | Transmitter Powerdown Delay (Figure 8) (No                                                          | ote 7)                               |                    |                  | 100                | ns    |

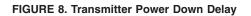

|        | Transmitter Input to Output Latency for single in-to-dual out mode. Figure 9                        | f = 170 MHz (Note 6)                 |                    | 1.5 TCIP<br>+4.1 |                    | ns    |

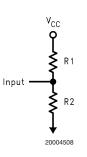

### Two-Wire Serial Communication Interface Switching Characteristics

Unless otherwise noted, below specifications apply for  $V_{CC}3V$  pin = +3.3V, load capacitance on output lines = 80 pF. Load capacitance on output lines can be up to 400pF provided that external pull-up is on board. The following parameters are the timing relationship between SCL and SDA signals related to the DS90C2501.

| Symbol         | Parameter                                          | Min | Тур | Max              | Units |

|----------------|----------------------------------------------------|-----|-----|------------------|-------|

| t <sub>1</sub> | SCL (Clock) Period                                 | 2.5 |     | 2000<br>(Note 7) | μs    |

| t <sub>2</sub> | Data in Set-Up Time to SCL High                    | 100 |     |                  | ns    |

| t <sub>3</sub> | Data Out Stable after SCL Low                      | 0   |     |                  | ns    |

| t <sub>4</sub> | SDA Low Set-Up Time to SCL Low (Start Condition)   | 100 |     |                  | ns    |

| t <sub>5</sub> | SDA High Hold Time after SCL High (Stop Condition) | 100 |     |                  | ns    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" specify conditions for device operation.

Note 2: Typical values are given for V\_{CC} = 2.5V and V\_{CC3V} = 3.3V at T\_A = +25 ^{\circ}C.

Note 3: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ).

**Note 4:** The limits are based on bench characterization of the device's jitter response over the power supply voltage range. Output clock jitter is measured with a cycle-to-cycle jitter of ± 20% data input bit time applied to the input clock signal while data inputs are switching (see figures 11 and 12). This parameter is used when calculating system margin as described in AN-1059.

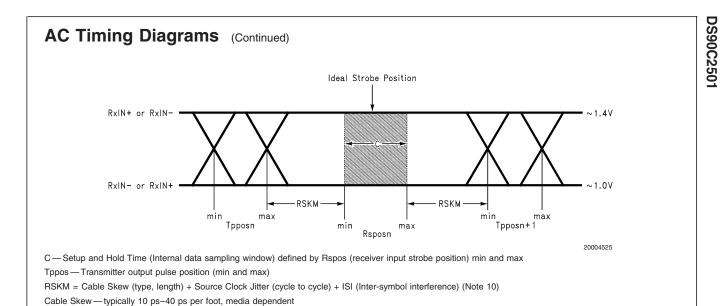

Note 5: Receiver Skew Margin is defined as the valid data sampling region at the receiver inputs. This margin takes into account transmitter output pulse positions (min and max) and the receiver input setup and hold time (internal data sampling window - RSPOS). This margin allows for LVDS interconnect skew, inter-symbol interference (both dependent on type/length of cable) and clock jitter.

$\mathsf{RSKM} \ge \mathsf{cable}$  skew (type, length) + source clock jitter (cycle to cycle).

Note 6: From V = 1.25V of CLKINP to  $V_{DIFF}$  = 0V of CLK1P when EDGE pin = Gnd, DUAL pin = Gnd or  $V_{CC}$  or  $\frac{1}{2}V_{CC}$ , BAL pin= Gnd. Note 7: Guaranteed by Design

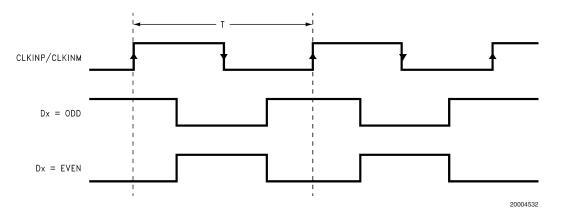

### **AC Timing Diagrams**

FIGURE 1. "Alternate High/Low" Test Pattern in 12-bit Input Mode (Note 8)

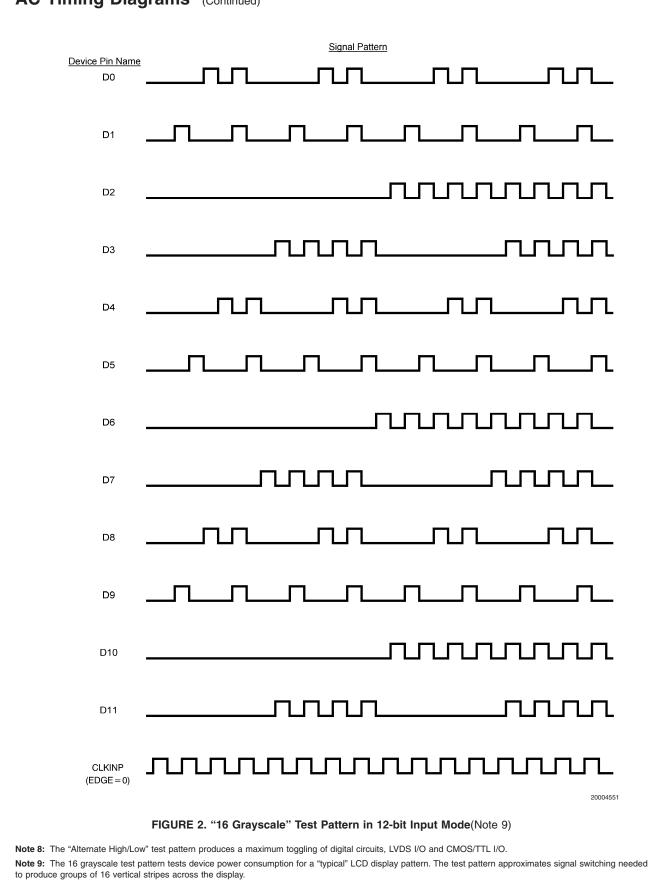

#### AC Timing Diagrams (Continued)

DS90C2501

### AC Timing Diagrams (Continued)

FIGURE 7. DS90C2501 (Transmitter) Phase Lock Loop Set Time

FIGURE 9. Transmitter Input to Output Lantency

Note 10: ISI is dependent on interconnect length; may be zero

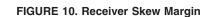

FIGURE 11. Resistor Network for "DUAL" pin input - recommend using R1=R2=10k $\Omega$  ±1% for single to dual mode

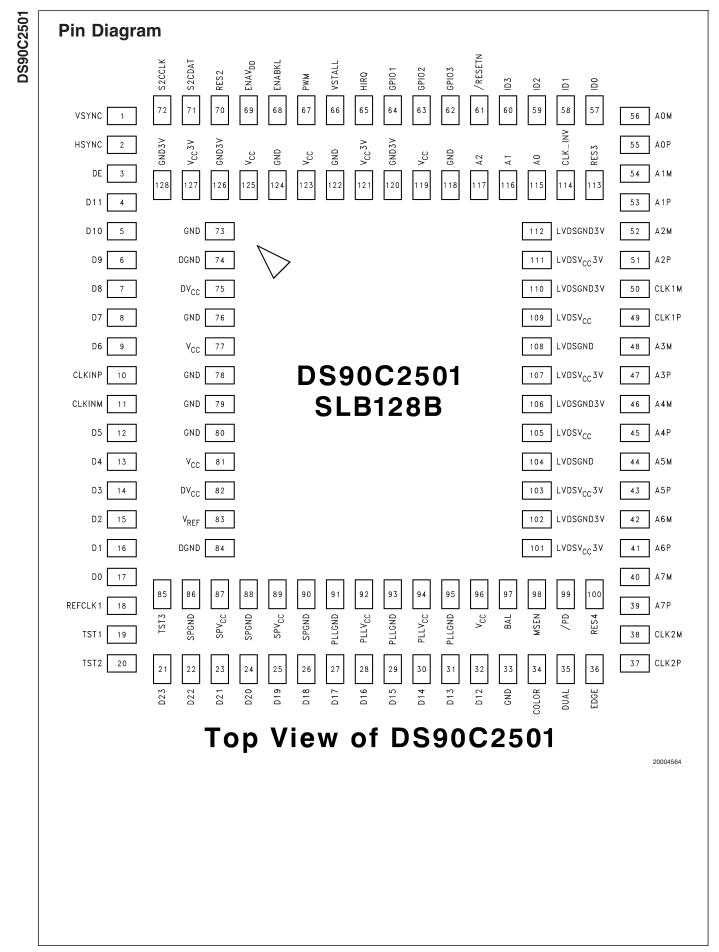

### DS90C2501 Pin Description

| Pin Name   | Pin No.                                                                                                             | I/O Type                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVO INTERF | ACE                                                                                                                 |                                                                                                                     | · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D0-D23     | 17, 16,<br>15, 14,<br>13, 12, 9,<br>8, 7, 6, 5,<br>4, 32, 31,<br>30, 29,<br>28, 27,<br>26, 25,<br>24, 23,<br>22, 21 | I-LVTTL/ Low<br>Swing (See<br>V <sub>REF</sub> signal<br>description<br>for more<br>information<br>on Low<br>Swing) | <ul> <li>DVO Port RGB input data</li> <li>When DUAL pin = GND inputs D0-D11 correspond to LVDS ports A0-A3.</li> <li>When DUAL pin = ½V<sub>CC</sub>, 1st pixel from D0-D11 corresponds to LVDS ports A0-A3, 2nd pixel from D0-D11 corresponds to LVDS ports A4-A7.</li> <li>When DUAL pin = V<sub>CC</sub>, 1st pixel from D0-D11 corresponds to LVDS ports A0-A3, 2nd pixel from D12-D23 corresponds to LVDS ports A4-A7.</li> <li>Note: Ports refer to the corresponding differential LVDS pin pairs. The port A nomenclature should n be confused with the serial interface slave address pins A0-A2.</li> </ul>                                                                                                                                                                                                   |

| DE         | 3                                                                                                                   | I-LVTTL/ Low<br>Swing                                                                                               | Display Data Enable. When High, input pixel data is valid to DS90C2501<br>when R_FDE bit = High (default). See RFDE register field for more<br>information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HSYNC      | 2                                                                                                                   | I-LVTTL/ Low<br>Swing                                                                                               | Display Horizontal Sync input control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSYNC      | 1                                                                                                                   | I-LVTTL/ Low<br>Swing                                                                                               | Display Vertical Sync input control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLKINP     | 10                                                                                                                  | I-LVTTL/ Low<br>Swing<br>Differential                                                                               | "Positive" differential pixel clock input. A differential clock is recommended fo<br>applications 65 MHz or higher.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKINM     | 11                                                                                                                  | I-LVTTL/ Low<br>Swing<br>Differential                                                                               | "Minus" differential pixel clock input. A differential clock is recommended for applications 65 MHz or higher.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HOST INTER | ACE                                                                                                                 | 1                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESETN     | 61                                                                                                                  | I-LVTTL 2.5                                                                                                         | Active low RESET signal. Asserting RESETN will reset all internal logic and clear the Host Interface registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| S2CCLK     | 72                                                                                                                  | I-LVTTL3V                                                                                                           | This is the clock line for the two-wire serial communication interface. Normal a pull-up resistor is required in the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S2CDAT     | 71                                                                                                                  | I/O-LVTTL3V                                                                                                         | This is the data line for two-wire serial communication interface. A Pull-up resistor is normally required in the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MSEN       | 98                                                                                                                  | O-LVTTL 2.5                                                                                                         | Interrupt signal. This is an open drain output, a pull-up resistor is required.<br>Please refer to MDI, RSEN, TSEL and MSEL register fields in Register Field<br>Definitions for more information. This signal requires support from host<br>software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PD         | 99                                                                                                                  | I-LVTTL 2.5                                                                                                         | Power Down Signal. A logic "0" will place the device in power down mode per<br><i>Table 1</i> below.<br>When maximum power savings is desired, the PD pin or soft power down bit<br>(Reg 08h bit 0) should be used to power down the DS90C2501.<br>LVDS outputs of the device will be in TRI-STATE.<br>Scaling engine will be powered down, and retain all register values.<br>PLL will be powered down.<br>All data input pads will be powered down. $V_{REF}$ circuit is powered down. The<br>two-wire serial communication interface remains active and all register<br>contents will be retained.<br>All GPIO pins will be disabled (tri-state if programmed as an output).<br>ENAVDD, ENABKL, PWM, VSTALL and HIRQ pins remain active and can be<br>accessed through the two-wire serial communication interface. |

| CLOCK      |                                                                                                                     | 1                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REFCLK1    | 18                                                                                                                  | I-LVTTL3V                                                                                                           | Reference clock, —A 3V, 14.318 MHz clock is required for internal control and timing. This clock must be stable when the DS90C2501 is powered-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Name    | Pin No.   | I/O Type    | Description                                                                                                                                                       |

|-------------|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTION SELE | CTION     |             |                                                                                                                                                                   |

| BAL         | 97        | I-LVTTL 2.5 | Tie this pin to GND.                                                                                                                                              |

| DUAL        | 35        | I-LVTTL 2.5 | LVTTL level input.                                                                                                                                                |

|             |           |             | Input = GND for single pixel in-to-single pixel out mode. LVDS output                                                                                             |

|             |           |             | channels A0 to A3 are enabled, A4 to A7 are CLK2 are disable.                                                                                                     |

|             |           |             | Input = $V_{CC}$ for dual pixel in-to-dual pixel out mode. LVDS output channel A0                                                                                 |

|             |           |             | to A7, CLK1 and CLK2 are enable. Use a 10K typ. pull-up resistor.                                                                                                 |

|             |           |             | Input = $\frac{1}{2}V_{CC}$ for single pixel in-to-dual pixel out mode. LVDS output channel                                                                       |

|             |           |             | A0 to A7, CLK1 and CLK2 are enabled. See register CFG1 (08h) BPASS field                                                                                          |

|             |           |             | for more information.                                                                                                                                             |

|             |           |             | See <i>Figure 11</i> for example interface circuit.                                                                                                               |

| COLOR       | 34        | I-LVTTL 2.5 | LVTTL level input to select RGB to LVDS color mapping.                                                                                                            |

|             |           |             | Tie to GND for 18-bit/36-bit LCD.                                                                                                                                 |

|             |           |             | Tie to GND to select conventional color mapping for 24-bit/48-bit LCD.<br>Tie to Logic "1" to select non-conventional color mapping for 24-bit/48-bit             |

|             |           |             |                                                                                                                                                                   |

| A0, A1, A2  | 115, 116, | I-LVTTL 2.5 | These are input pins to select the 2-wire Serial Communication Slave Device                                                                                       |

| ,           | 117       |             | Address Lower Bits.                                                                                                                                               |

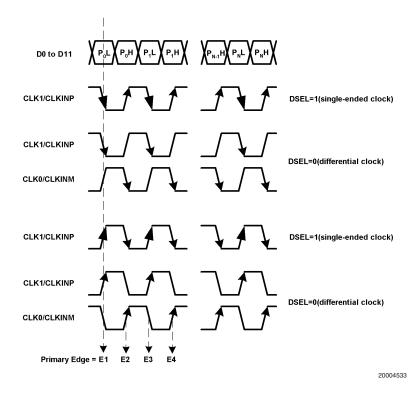

| EDGE        | 36        | I-LVTTL 2.5 | Selects primary clock edge E1.                                                                                                                                    |

|             |           |             | Tie to Logic "1" to select Rising edge for E1.                                                                                                                    |

|             |           |             | Tie to ground to select Falling edge for E1.                                                                                                                      |

| PANEL INTER | FACE      | I           |                                                                                                                                                                   |

| A0P, A1P,   | 55, 53,   | O-LVDS      | Positive LVDS differential data output.                                                                                                                           |

| A2P, A3P    | 51, 47    |             | When DUAL pin = GND, input to $D0-D11$ will be coming out of A0P to A3P.                                                                                          |

|             |           |             | For 6-bit color application, no connect for channel A3P.                                                                                                          |

|             |           |             | When DUAL pin = $\frac{1}{2}V_{CC}$ , the first pixel going in D0–D11 will be coming out                                                                          |

|             |           |             | of A0P to A3P, and the second pixel going in D0-D11 will come out of A4P to                                                                                       |

|             |           |             | A7P. For 6-bit color application, no connect for channels A3P and A7P.                                                                                            |

|             |           |             | When DUAL pin = $V_{CC}$ , the first pixel going in D0–D11 will be coming out of                                                                                  |

|             |           |             | A0P to A3P, the second pixel going in D12–D23 will be coming out of A4P to                                                                                        |

|             |           |             | A7P. For 6-bit color application, no connect for channels A3P and A7P.                                                                                            |

| AOM, A1M,   | 56, 54,   | O-LVDS      | Negative LVDS differential data output.                                                                                                                           |

| A2M, A3M    | 52, 48    |             | When DUAL pin = GND, input to $D0-D11$ will be coming out of A0M to A3M.                                                                                          |

|             |           |             | For 6-bit color application, no connect for channel A3M.<br>When $PLAL$ pin = 14V, the first pixel going in $P0$ , $P11$ will be coming out                       |

|             |           |             | When DUAL pin = $\frac{1}{2}V_{CC}$ , the first pixel going in D0–D11 will be coming out of A0M to A3M, and the second pixel going in D0–D11 will come out of A4M |

|             |           |             | to A7M. For 6-bit color application, no connect for channels A3M and A7M.                                                                                         |

|             |           |             | When DUAL pin = $V_{CC}$ , the first pixel going in D0–D11 will be coming out of                                                                                  |

|             |           |             | A0M to A3M, the second pixel going in D12–D23 will be coming out of A4M                                                                                           |

|             |           |             | to A7M. For 6-bit color application, no connect for channels A3M and A7M.                                                                                         |

| A4P, A5P,   | 45, 43,   | O-LVDS      | Positive LVDS differential data output for second pixel.                                                                                                          |

| A6P, A7P    | 41, 39    |             | When DUAL pin = GND, input to $D0-D11$ will be coming out of A0P to A3P.                                                                                          |

|             |           |             | For 6-bit color application, no connect for channel A3P.                                                                                                          |

|             |           |             | When DUAL pin = $\frac{1}{2}V_{CC}$ , the first pixel going in D0–D11 will be coming out                                                                          |

|             |           |             | of A0P to A3P, and the second pixel going in D0-D11 will come out of A4P to                                                                                       |

|             |           |             | A7P. For 6-bit color application, no connect for channels A3P and A7P.                                                                                            |

|             |           |             | When DUAL pin = $V_{CC}$ , the first pixel going in D0–D11 will be coming out of                                                                                  |

|             |           |             | A0P to A3P, the second pixel going in D12–D23 will be coming out of A4P to                                                                                        |

|             |           |             | A7P. For 6-bit color application, no connect for channels A3P and A7P.                                                                                            |

| Pin Name                  | Pin No.           | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTION SELEC              |                   |              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A4M, A5M,<br>A6M, A7M     | 46, 44,<br>42, 40 | O-LVDS       | Negative LVDS differential data output for second pixel.<br>When DUAL pin = GND, input to D0–D11 will be coming out of A0M to A3M.<br>For 6-bit color application, no connect for channel A3M.<br>When DUAL pin = $\frac{1}{2}V_{CC}$ , the first pixel going in D0–D11 will be coming out of A0M to A3M, and the second pixel going in D0–D11 will come out of A4M to A7M. For 6-bit color application, no connect for channels A3M and A7M.<br>When DUAL pin = $V_{CC}$ , the first pixel going in D0–D11 will be coming out of A4M to A7M. For 6-bit color application, no connect for channels A3M and A7M.<br>When DUAL pin = $V_{CC}$ , the first pixel going in D0–D11 will be coming out of A0M to A3M, the second pixel going in D12–D23 will be coming out of A4M to A7M. For 6-bit color application, no connect for channels A3M and A7M. |

| CLK1P                     | 49                | O-LVDS       | Positive LVDS differential clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CLK1M                     | 50                | O-LVDS       | Negative LVDS differential clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CLK2P                     | 37                | O-LVDS       | Additional positive LVDS differential clock output pin. Identical to CLK1P. No connect if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK2M                     | 38                | O-LVDS       | Additional negative LVDS differential clock output pin. Identical to CLK1M. No connect if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ID0, ID1, ID2,<br>ID3     | 57, 58,<br>59, 60 | I-LVTTL 2.5  | These four pins are used to select one out of 16 pre-determined LCD display<br>timing information. The values are from 0 to 15. This function requires support<br>from VBIOS or display driver. Tie these pins to GND when not in use. Tie<br>these four pins [ID3, ID2, ID1, ID0] to High or Low for selecting LCD panel.<br>ID0 is the LSB, and ID3 is the MSB. For example: 1000 will select the 9th<br>LCD panel.<br>A 4-bit register field [3:0] will be used to store the selected value for the host<br>to read. See PANEL field for more information.                                                                                                                                                                                                                                                                                         |

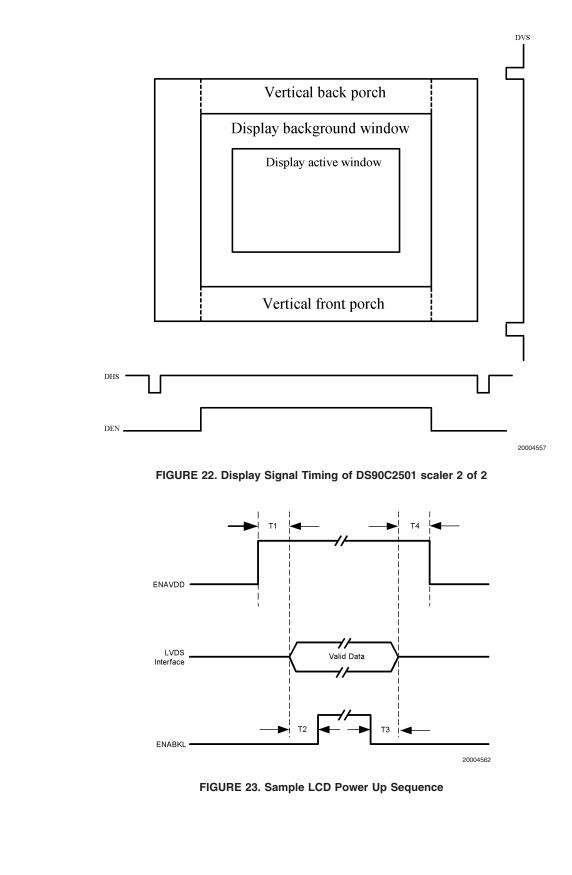

| ENAVDD                    | 69                | O-LVTTL 2.5  | Output to control LCD panel power under software control. Typically, this output is used with a power switch such as a FET circuit to control LCD panel $V_{CC}$ (Note 11).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ENABKL                    | 68                | O-LVTTL 2.5  | Output to control LCD panel back light power under software control.<br>Typically, this output is used to control the enable on a backlight inverter<br>(Note 11).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MISCELLANEC               | US/TEST           |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| gpio1,<br>gpio2,<br>gpio3 | 64, 63, 62        | I/O-LVTTL 3V | General purpose inputs or outputs referenced to GND.<br>When the device is powered up, this pin defaults to an input.<br>When the scaler is in the power down state these signals are tri-state if<br>programmed as outputs (Note 11).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLK_INV                   | 114               | I-LVTTL 2.5  | This pin is used to invert the polarity of the incoming pixel CLK (CLKINP/CLKINM). A logic 0 = Normal, Logic 1 = Invert.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RES2                      | 70                | I-LVTTL 2.5  | This pin is used in production testing and should be tied to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RES3                      | 113               | I-LVTTL 2.5  | This pin is used in production testing and should be tied to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RES4                      | 100               | I-LVTTL 2.5  | This pin is used in production testing and should be tied to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PWM                       | 67                | O-LVTTL 3V   | This signal was provided for legacy support and is no longer required. This pin should be left open in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSTALL                    | 66                | O-LVTTL 3V   | This signal was provided for legacy support and is no longer required. This pin should be left open in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HIRQ                      | 65                | O-LVTTL 3V   | This signal was provided for legacy support and is no longer required. This pin should be left open in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin Name                          | Pin No.                                                      | I/O Type        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|--------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTION SELE                       | CTION                                                        |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>REF</sub>                  | 83                                                           | I-ANALOG        | This pin is never to be left floating and never tie to GND.<br>For LVTTL level data input, tie $V_{REF}$ to $V_{CC}$ 3V. When $V_{REF} > 1.8V$ , input data<br>is set to LVTTL level.<br>For low voltage swing level data input, tie $V_{REF}$ to $\frac{1}{2}V_{DDQ}$ ( $V_{DDQ}$ provided by<br>host interface) $V_{DDQ}$ is from the host. When $V_{REF} <=1.0V$ , indicates input<br>data is in low voltage swing mode.<br>Input data = logic High = $V_{REF} + 100$ mV in low voltage swing level. |

| TST1, TST2,<br>TST3               | 19, 20, 85                                                   | I-LVTTL 2.5     | Input data = logic Low = V <sub>REF</sub> –100 mV in low voltage swing level.<br>These pins are used in production testing and should be tied to GND in normal operation.                                                                                                                                                                                                                                                                                                                               |

|                                   | Application Inf                                              | ormation for po | wer supply decoupling requirements)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |