# PowerPC<sup>™</sup> MPC801

## Integrated Microprocessor for Embedded Systems User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application here personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended for unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola and (M) are negarding the design or manufacture of the part. Motorola and (M) are registred trademarks of Motorola, Inc. Motorola, Inc. Motorola, Inc.

© 1997 Motorola, Inc. All Rights Reserved.

PowerQUICC<sup>™</sup> is a registered trademark of Motorola, Inc. PowerPC<sup>™</sup> is a registered trademark of IBM Corp. and is used by Motorola under license from IBM Corp. I<sup>2</sup>C is a trademark of Philips Corp. All other trademarks are the property of their respective owners.

## TABLE OF CONTENTS

### Paragraph Number

### Title

Page Number

### Section 1 Introduction

| 1.1   | Features                                   | 1-1 |

|-------|--------------------------------------------|-----|

| 1.2   | MPC801 Architecture                        | 1-4 |

| 1.2.1 | The Embedded PowerPC Core                  | 1-5 |

| 1.2.2 | The System Interface Unit                  | 1-6 |

| 1.2.3 | The UART Controller                        |     |

| 1.2.4 | The I <sup>2</sup> C Controller            | 1-7 |

| 1.2.5 | The Serial Peripheral Interface Controller | 1-7 |

| 1.3   | Power Management                           |     |

| 1.4   | MPC801 Applications                        |     |

| 1.5   | Differences Between the MPC801 and MPC860  |     |

| 1.6   | MPC801 Glueless System Design              | 1-8 |

### Section 2 External Signals

| 2.1 | The System Bue Signale | <b>•</b> • • |

|-----|------------------------|--------------|

| 2.1 | The System bus Signals |              |

### Section 3 Memory Map

#### Section 4 Reset

| 4.1     | Types of Reset4-1          |

|---------|----------------------------|

| 4.1.1   | Power-On Reset4-2          |

| 4.1.2   | External Hard Reset4-2     |

| 4.1.3   | Internal Hard Reset4-3     |

| 4.1.3.1 | Loss of Lock4-3            |

| 4.1.3.2 | Software Watchdog Reset4-3 |

| 4.1.3.3 | Checkstop Reset4-3         |

| 4.1.3.4 | Debug Port Hard Reset4-3   |

| 4.1.3.5 | JTAG Reset4-3              |

| 4.1.4   | External Soft Reset4-3     |

| 4.1.5   | Internal Soft Reset4-4     |

| 4.1.5.1 | Debug Port Soft Reset4-4   |

| Paragraph<br>Number | Title                  | Page<br>Number |

|---------------------|------------------------|----------------|

| 4.2                 | Reset Status Register  | 4-4            |

| 4.3                 | How to Configure Reset |                |

| 4.3.1               | Hard Reset             |                |

| 4.3.2               | Soft Reset             | 4-11           |

### Section 5 Clocks and Power Control

| 5.1    | The Clock Module                             |      |

|--------|----------------------------------------------|------|

| 5.2    | On-Chip Oscillators and External Clock Input |      |

| 5.3    | The System Phase-Locked Loop                 |      |

| 5.3.1  | Multiplying the Frequency                    |      |

| 5.3.2  | Eliminating Skew                             |      |

| 5.3.3  | Operating the PLL Block                      |      |

| 5.4    | The Low-Power Divider                        |      |

| 5.5    | Internal Clock Signals                       |      |

| 5.5.1  | The General System Clocks                    |      |

| 5.5.2  | The Baud Rate Generator Clock                | 5-11 |

| 5.5.3  | The Synchronization Clocks                   | 5-11 |

| 5.6    | The Phase-Locked Loop Pins                   |      |

| 5.7    | Controlling The System Clock                 | 5-13 |

| 5.8    | PLL Low-Power and Reset Control Register     | 5-16 |

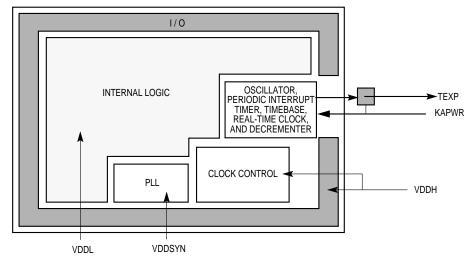

| 5.9    | Basic Power Structure                        |      |

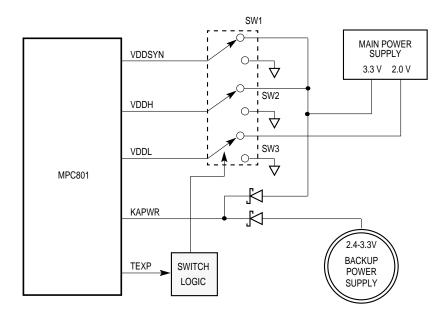

| 5.10   | Keep Alive Power                             | 5-23 |

| 5.10.1 | Configuration                                |      |

| 5.10.2 | The Key Mechanism                            | 5-24 |

|        |                                              |      |

### Section 6 The PowerPC Core

| 6.1   | Features                               | 6-1  |

|-------|----------------------------------------|------|

| 6.1.1 | Basic Structure of the Core            | 6-2  |

| 6.1.2 | Instruction Flow Within the Core       | 6-2  |

| 6.1.3 | Basic Instruction Pipeline             | 6-4  |

| 6.2   | The Sequencer Unit                     |      |

| 6.2.1 | Flow Control                           | 6-4  |

| 6.2.2 | Issuing Instructions                   | 6-6  |

| 6.2.3 | Interrupts                             | 6-6  |

| 6.2.4 | Precise Exception Model Implementation | 6-8  |

| 6.2.5 | Processing An Interrupt                | 6-11 |

| 6.2.6 | Serialization                          | 6-12 |

| 6.2.7 | The External Interrupt                 | 6-13 |

| Paragraph<br>Number | Title                                   | Page<br>Number |

|---------------------|-----------------------------------------|----------------|

| 6.2.7.1             | Latency                                 | 6-13           |

| 6.2.8               | Interrupt Ordering                      | 6-13           |

| 6.3                 | The Register Unit                       | 6-15           |

| 6.3.1               | The Control Registers                   | 6-15           |

| 6.3.1.1             | Physical Location of Special Registers  | 6-19           |

| 6.3.1.2             | Bit Assignment of the Control Registers | 6-20           |

| 6.3.1.3             | Initializing the Control Registers      | 6-24           |

| 6.4                 | The Fixed-Point Unit                    | 6-24           |

| 6.4.1               | Updating XER with Divide Instructions   | 6-24           |

| 6.5                 | The Load/Store Unit                     |                |

| 6.5.1               | Load/Store Instruction                  | 6-26           |

| 6.5.2               | Synchronizing Load/Store Instructions   | 6-27           |

| 6.5.3               | Instructions Issued to the Data Cache   | 6-27           |

| 6.5.4               | Issuing Store Instruction               |                |

| 6.5.5               | Nonspeculative Load Instructions        | 6-28           |

| 6.5.6               | Executing Unaligned Instructions        | 6-28           |

| 6.5.7               | Little-Endian Mode Support              | 6-29           |

| 6.5.8               | Atomic Update Primitives                | 6-29           |

| 6.5.9               | Instruction Timing                      | 6-29           |

| 6.5.10              | Stalling Storage Control Instructions   | 6-30           |

| 6.5.11              | Accessing Off-Core Special Registers    | 6-30           |

| 6.5.12              | Storage Control Instructions            | 6-30           |

| 6.5.13              | Exception Processing                    |                |

| 6.5.13.1            | Using DAR, DSISR, and BAR               | 6-31           |

### Section 7 PowerPC Architecture Compliance

| 7.1     | PowerPC User Instruction Set Architecture (Book I) | 7-1 |

|---------|----------------------------------------------------|-----|

| 7.1.1   | Computation Modes                                  | 7-1 |

| 7.1.2   | Reserved Fields                                    |     |

| 7.1.3   | Classes of Instructions                            | 7-1 |

| 7.1.4   | Exceptions                                         | 7-2 |

| 7.1.5   | The Branch Processor                               | 7-2 |

| 7.1.6   | Fetching Instructions                              | 7-2 |

| 7.1.7   | Branch Instructions                                | 7-2 |

| 7.1.7.1 | Invalid Branch Instruction Forms                   | 7-2 |

| 7.1.7.2 | Branch Prediction                                  | 7-2 |

| 7.1.8   | The Fixed-Point Processor                          | 7-2 |

| 7.1.8.1 | Move To/From System Register Instructions          | 7-3 |

| 7.1.8.2 | Fixed-Point Arithmetic Instructions                | 7-3 |

| 7.1.9   | The Load/Store Processor                           | 7-3 |

|         |                                                    |     |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 7.1.9.1             | Fixed-Point Load and Store With Update Instructions   | s7-3           |

| 7.1.9.2             | Fixed-Point Load and Store Multiple Instructions      | 7-3            |

| 7.1.9.3             | Fixed-Point Load String Instructions                  |                |

| 7.1.9.4             | Storage Synchronization Instructions                  | 7-3            |

| 7.1.9.5             | Optional Instructions                                 |                |

| 7.1.9.6             | Little-Endian Byte Ordering                           |                |

| 7.2                 | PowerPC Virtual Environment Architecture (Book II)    | 7-4            |

| 7.2.1               | Storage Model                                         |                |

| 7.2.1.1             | Memory Coherence                                      | 7-4            |

| 7.2.1.2             | Atomic Update Primitives                              |                |

| 7.2.2               | The Effect of Operand Placement on Performance        | 7-4            |

| 7.2.3               | The Storage Control Instructions                      |                |

| 7.2.3.1             | Instruction Cache Block Invalidate (icbi)             |                |

| 7.2.3.2             | Instruction Synchronize (isync)                       | 7-5            |

| 7.2.3.3             | Data Cache Block Touch (dcbt)                         |                |

| 7.2.3.4             | Data Cache Block Touch for Store (dcbtst)             | 7-5            |

| 7.2.3.5             | Data Cache Block Set to Zero (dcbz)                   | 7-5            |

| 7.2.3.6             | Data Cache Block Store (dcbst)                        | 7-5            |

| 7.2.3.7             | Data Cache Block Invalidate (dcbi)                    | 7-5            |

| 7.2.3.8             | Data Cache Block Flush (dcbf)                         | 7-5            |

| 7.2.3.9             | Enforce In-Order Execution of I/O (eieio)             | 7-6            |

| 7.2.4               | Timebase                                              | 7-6            |

| 7.3                 | PowerPC Operating Environment Architecture (Book III) | 7-6            |

| 7.3.1               | The Branch Processor                                  | 7-6            |

| 7.3.1.1             | Branch Processor Registers                            | 7-6            |

| 7.3.1.2             | Branch Processor Instructions                         | 7-6            |

| 7.3.2               | The Fixed-Point Processor                             |                |

| 7.3.2.1             | Special-Purpose Registers                             | 7-6            |

| 7.3.3               | Storage Model                                         | 7-7            |

| 7.3.3.1             | Address Translation                                   |                |

| 7.3.4               | Reference and Change Bits                             |                |

| 7.3.5               | Storage Protection                                    | 7-7            |

| 7.3.6               | Storage Control Instructions                          |                |

| 7.3.6.1             | Data Cache Block Invalidate (dcbi)                    |                |

| 7.3.6.2             | TLB Invalidate Entry (tlbie)                          |                |

| 7.3.6.3             | TLB Invalidate All (tlbia)                            |                |

| 7.3.6.4             | TLB Synchronize (tlbsync)                             | 7-8            |

| Paragraph<br>Number | Title                                | Page<br>Number |

|---------------------|--------------------------------------|----------------|

| 7.3.7               | Interrupts                           | 7-8            |

| 7.3.7.1             | Classes                              | 7-8            |

| 7.3.7.2             | Processing                           | 7-8            |

| 7.3.7.3             | Definitions                          | 7-8            |

| 7.3.7.4             | Partially Executed Instructions      | 7-17           |

| 7.3.8               | Timer Facilities                     | 7-17           |

| 7.3.9               | Optional Facilities and Instructions | 7-17           |

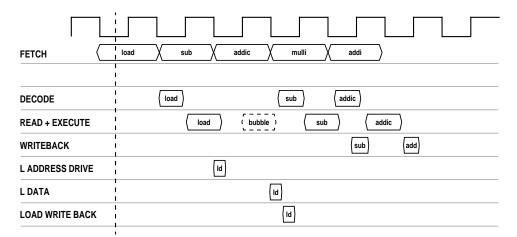

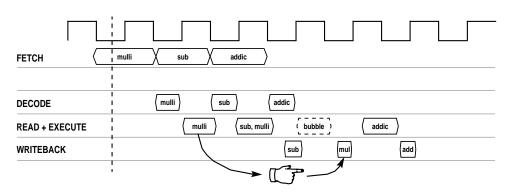

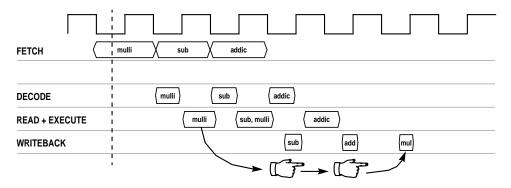

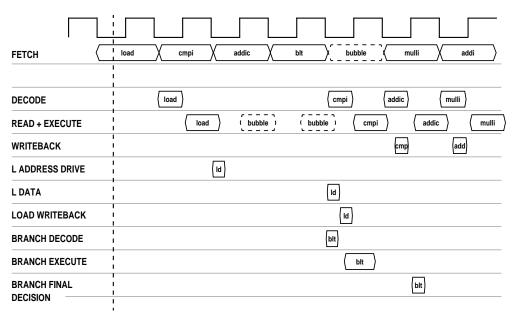

## Section 8 Instruction Execution Timing

| Instruction Execution Timing Examples    | 8-4                                                                                                                                                                  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Cache Load                          |                                                                                                                                                                      |

| Writeback                                | 8-5                                                                                                                                                                  |

| Writeback Arbitration                    | 8-5                                                                                                                                                                  |

| Private Writeback Bus Dedicated for Load | 8-6                                                                                                                                                                  |

| Fastest External Load (Data Cache Miss)  | 8-7                                                                                                                                                                  |

| A Full History Buffer                    | 8-8                                                                                                                                                                  |

| Branch Folding                           | 8-9                                                                                                                                                                  |

| Branch Prediction                        |                                                                                                                                                                      |

|                                          | Writeback<br>Writeback Arbitration<br>Private Writeback Bus Dedicated for Load<br>Fastest External Load (Data Cache Miss)<br>A Full History Buffer<br>Branch Folding |

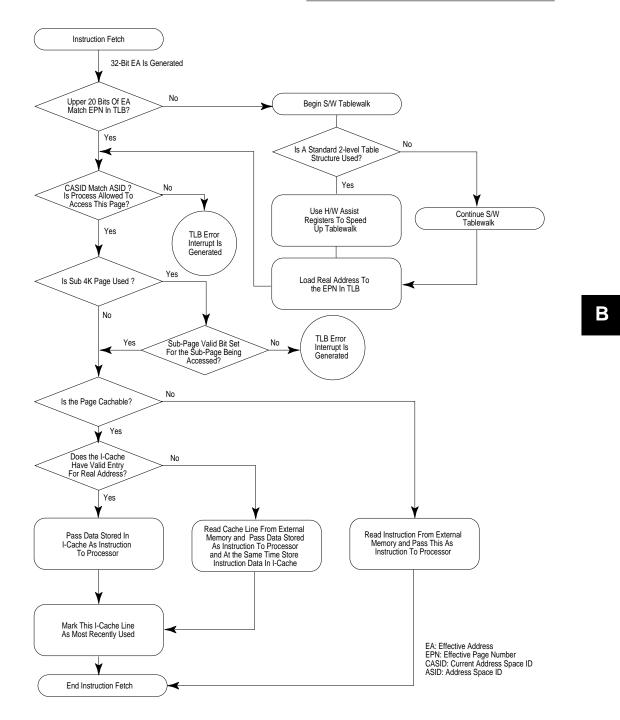

### Section 9 Instruction Cache

| 9.1   | Features                                      | 9-1  |

|-------|-----------------------------------------------|------|

| 9.2   | Programming the Instruction Cache             | 9-4  |

| 9.2.1 | Instruction Cache Control and Status Register | 9-4  |

| 9.2.2 | Instruction Cache Address Register            | 9-5  |

| 9.2.3 | Instruction Cache Data Port Register          | 9-6  |

| 9.3   | How the Instruction Cache Works               |      |

| 9.3.1 | Instruction Cache Hit                         | 9-6  |

| 9.3.2 | Instruction Cache Miss                        | 9-6  |

| 9.3.3 | Instruction Fetch On A Predicted Path         | 9-7  |

| 9.4   | Instruction Cache Commands                    | 9-7  |

| 9.4.1 | Instruction Cache Block Invalidate            |      |

| 9.4.2 | Invalidate All Instruction Cache              | 9-8  |

| 9.4.3 | Load & Lock                                   | 9-8  |

| 9.4.4 | Unlock Line                                   | 9-9  |

| 9.4.5 | Unlock All                                    | 9-9  |

| 9.4.6 | Instruction Cache Inhibit                     | 9-9  |

| 9.4.7 | Instruction Cache Read                        | 9-10 |

| 9.4.8 | Instruction Cache Write                       | 9-11 |

|       |                                               |      |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 9.5                 | Restrictions                                    | 9-11           |

| 9.6                 | Instruction Cache Coherency                     | 9-11           |

| 9.7                 | Updating Code And Memory Region Attributes      | 9-11           |

| 9.8                 | Reset Sequence                                  | 9-12           |

| 9.9                 | Debug Support                                   | 9-12           |

| 9.9.1               | Fetching Instructions From the Development Port |                |

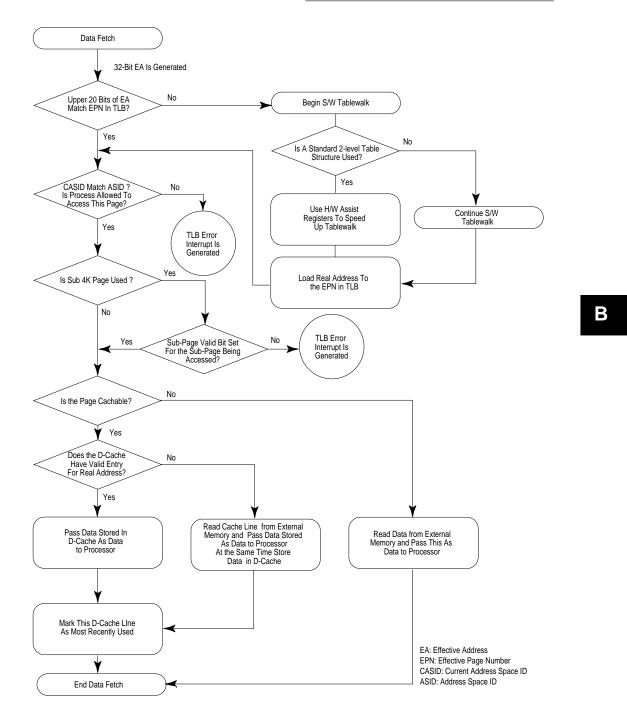

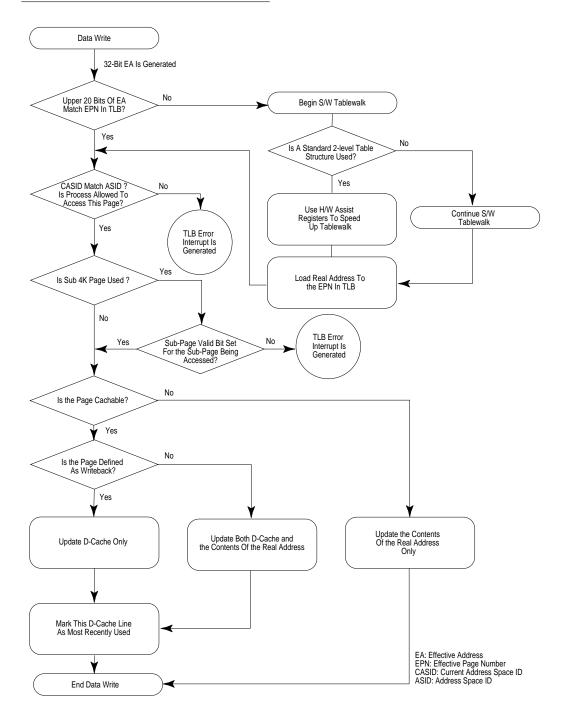

### Section 10 Data Cache

| 10.1     | Features                                       |       |

|----------|------------------------------------------------|-------|

| 10.2     | Organization of the Data Cache                 |       |

| 10.3     | Programming the Data Cache                     |       |

| 10.3.1   | PowerPC Architecture Instructions              |       |

| 10.3.1.1 | PowerPC User Instruction Set Architecture      |       |

| 10.3.1.2 | PowerPC Virtual Environment Architecture       |       |

| 10.3.1.3 | PowerPC Operating Environment Architecture     | 10-3  |

| 10.3.2   | Implementation Specific Operations             |       |

| 10.3.3   | Special Registers of the Data Cache            |       |

| 10.3.3.1 | Data Cache Control and Status Register         |       |

| 10.3.3.2 | Data Cache Address Register                    |       |

| 10.3.3.3 | Reading the Cache Structures                   |       |

| 10.3.3.4 | Data Cache Data Register                       |       |

| 10.4     | Operating the Data Cache                       |       |

| 10.4.1   | Data Cache Read                                |       |

| 10.4.2   | Data Cache Write                               |       |

| 10.4.2.1 | Copyback Mode                                  |       |

| 10.4.2.2 | Writethrough Mode                              |       |

| 10.4.3   | Data Cache-Inhibited Accesses                  |       |

| 10.4.4   | Data Cache Freeze                              |       |

| 10.4.5   | Data Cache Coherency                           |       |

| 10.5     | Controlling the Data Cache                     |       |

| 10.5.1   | Flushing and Invalidating                      |       |

| 10.5.2   | Disabling                                      |       |

| 10.5.3   | Locking                                        |       |

| 10.5.4   | Storage Control Instructions in the Data Cache | 10-11 |

| 10.5.4.1 | dcbi, dcbst, dcbf And dcbz Instructions        | 10-11 |

| 10.5.4.2 | Touch                                          | 10-11 |

| 10.5.4.3 | Storage Synchronization and Reservation        | 10-11 |

| 10.5.5   | Reading the Data Cache Structures              | 10-11 |

### Paragraph Number

Title

### Page Number

### Section 11 Memory Management Unit

| 11.1     | Features11-1                                       |

|----------|----------------------------------------------------|

| 11.2     | Address Translation11-2                            |

| 11.2.1   | Translation Lookaside Buffer Operation11-2         |

| 11.3     | Protection11-3                                     |

| 11.4     | Storage Attributes                                 |

| 11.4.1   | Reference and Change Bit Updates11-4               |

| 11.4.2   | Storage Control11-4                                |

| 11.5     | Translation Table Structure                        |

| 11.5.1   | Level One Descriptor11-8                           |

| 11.5.2   | Level Two Descriptor11-9                           |

| 11.6     | Memory Management Unit Programming Model           |

| 11.6.1   | Configuration Registers11-10                       |

| 11.6.1.1 | Instruction MMU Control Register                   |

| 11.6.1.2 | MI_AP Register11-11                                |

| 11.6.1.3 | Data MMU Control Register                          |

| 11.6.1.4 | MD_AP Register11-13                                |

| 11.6.1.5 | CASID Register11-14                                |

| 11.6.2   | Tablewalk Registers11-14                           |

| 11.6.2.1 | M_TWB Register11-14                                |

| 11.6.2.2 | M_TW Register11-15                                 |

| 11.6.2.3 | MI_EPN Register11-15                               |

| 11.6.2.4 | MI_TWC Register11-16                               |

| 11.6.2.5 | MI_RPN Register11-17                               |

| 11.6.2.6 | MD_EPN Register11-18                               |

| 11.6.2.7 | Data MMU Tablewalk Control Register                |

| 11.6.2.8 | MD_RPN Register11-20                               |

| 11.6.3   | Instruction Debug Registers11-22                   |

| 11.6.3.1 | MI_DCAM Register11-22                              |

| 11.6.3.2 | MI_DRAM0 Register11-23                             |

| 11.6.3.3 | MI_DRAM1 Register11-24                             |

| 11.6.4   | Data Debug Registers11-25                          |

| 11.6.4.1 | MD_DCAM Register11-25                              |

| 11.6.4.2 | MD_DRAM0 Register11-26                             |

| 11.6.4.3 | MD_DRAM1 Register11-27                             |

| 11.7     | Interrupts11-29                                    |

| 11.7.1   | Implementation Specific Instruction TLB Miss11-29  |

| 11.7.2   | Implementation Specific Data TLB Miss11-29         |

| 11.7.3   | Implementation Specific Instruction TLB Error11-29 |

| 11.7.4   | Implementation Specific Data TLB Error             |

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

| 11.8                | Manipulating the TLB                             | 11-30          |

| 11.8.1              | Reloading the TLB                                | 11-30          |

| 11.8.1.1            | Translation Reload Examples                      | 11-31          |

| 11.8.2              | Controlling the TLB Replacement Counter          | 11-32          |

| 11.8.3              | Invalidating the TLB                             | 11-32          |

| 11.8.4              | Loading the Reserved TLB Entries                 | 11-32          |

| 11.9                | Requirements For Accessing The Memory Management |                |

|                     | Unit Control Registers                           | 11-32          |

### Section 12 System Interface Unit

| 12.1      | Features                                      |  |

|-----------|-----------------------------------------------|--|

| 12.2      | System Configuration and Protection           |  |

| 12.3      | Configuring the System                        |  |

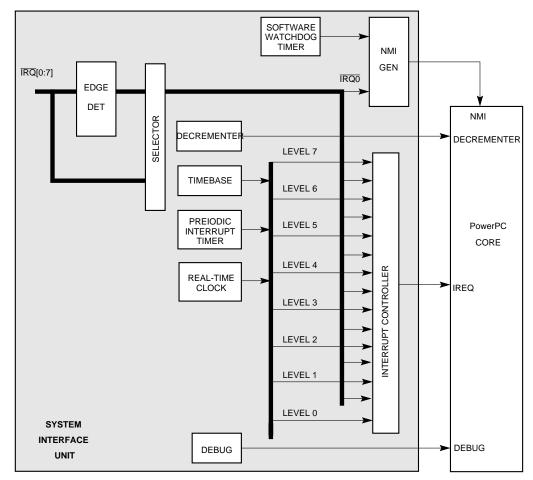

| 12.3.1    | Configuring the Interrupt                     |  |

| 12.3.2    | Priority of the Interrupt Sources             |  |

| 12.3.2.1  | Programming the Interrupt Controller          |  |

| 12.3.2.2  | SIU Interrupt Mask Register                   |  |

| 12.3.2.3  | SIU Interrupt Edge Level Mask Register        |  |

| 12.3.2.4  | SIU Interrupt Vector Register                 |  |

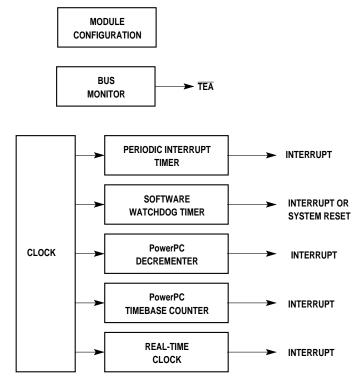

| 12.4      | The Bus Monitor                               |  |

| 12.5      | The PowerPC Decrementer                       |  |

| 12.6      | The PowerPC Timebase                          |  |

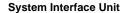

| 12.7      | The Real-Time Clock                           |  |

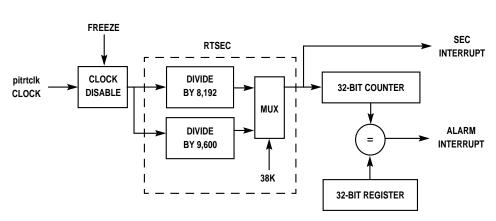

| 12.8      | The Periodic Interrupt Timer                  |  |

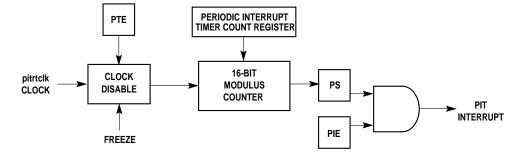

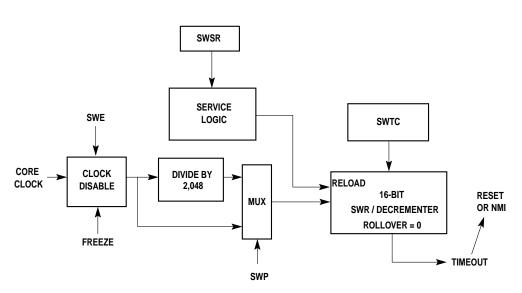

| 12.9      | The Software Watchdog Timer                   |  |

| 12.10     | Freeze Operation                              |  |

| 12.10.1   | Low-Power Stop Operation                      |  |

| 12.11     | Multiplexing the System Interface Unit Pins   |  |

| 12.12     | Programming the System Interface Unit         |  |

| 12.12.1   | System Configuration and Protection Registers |  |

| 12.12.1.1 | SIU Module Configuration Register             |  |

| 12.12.1.2 | Internal Memory Map Register                  |  |

| 12.12.1.3 | System Protection Control Register            |  |

| 12.12.1.4 | Software Service Register                     |  |

| 12.12.1.5 | Transfer Error Status Register                |  |

| 12.12.2   | System Timer Registers                        |  |

| 12.12.2.1 | Decrementer Register                          |  |

| 12.12.2.2 | Timebase Register                             |  |

| 12.12.2.3 | Timebase Reference Register                   |  |

| 12.12.2.4 | Timebase Control and Status Register          |  |

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 12.12.2.5           | Real-Time Clock Status and Control Register   | 12-26          |

| 12.12.2.6           | Real-Time Clock Register                      | 12-27          |

| 12.12.2.7           | Real-Time Clock Alarm Register                | 12-27          |

| 12.12.2.8           | Periodic Interupt Status and Control Register | 12-27          |

| 12.12.2.9           | Periodic Interrupt Timer Count Register       | 12-28          |

| 12.12.2.10          | Periodic Interrupt Timer Register             | 12-29          |

### Section 13 External Bus Interface

| 13.1      | Features                               |  |

|-----------|----------------------------------------|--|

| 13.2      | Transfer Signals                       |  |

| 13.2.1    | Control Signals                        |  |

| 13.3      | Signal Descriptions                    |  |

| 13.4      | Operations on the Bus                  |  |

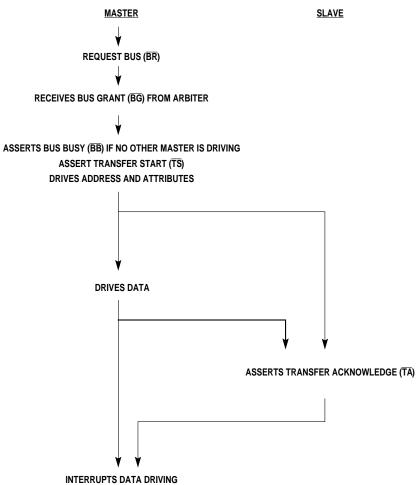

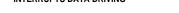

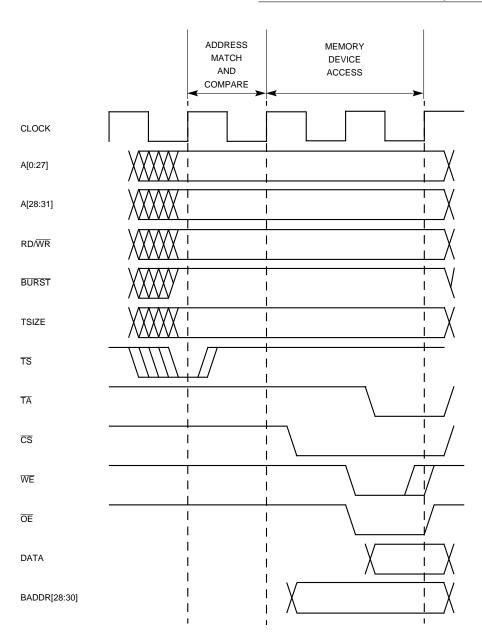

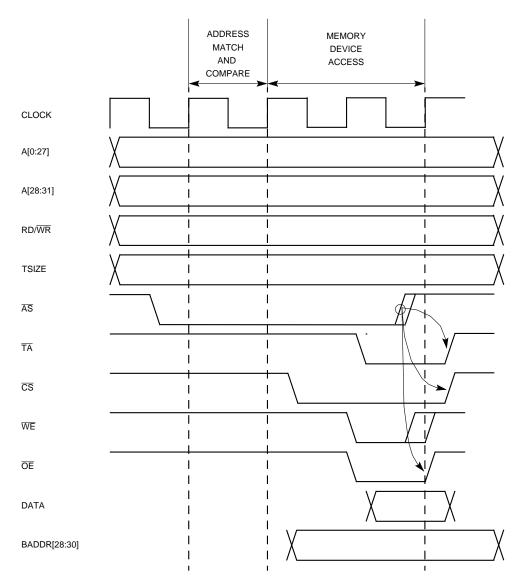

| 13.4.1    | Basic Transfer Protocol                |  |

| 13.4.2    | Single Beat Transfers                  |  |

| 13.4.2.1  | Single Beat Read Flow                  |  |

| 13.4.2.2  | Single Beat Write Flow                 |  |

| 13.4.3    | Burst Transfers                        |  |

| 13.4.4    | The Burst Mechanism                    |  |

| 13.4.5    | Transfer Alignment and Packaging       |  |

| 13.4.6    | Arbitration Phase Signals              |  |

| 13.4.6.1  | Bus Request                            |  |

| 13.4.6.2  | Bus Grant                              |  |

| 13.4.6.3  | Bus Busy                               |  |

| 13.4.7    | Address Transfer Phase-Related Signals |  |

| 13.4.7.1  | Transfer Start                         |  |

| 13.4.7.2  | Address Bus                            |  |

| 13.4.7.3  | Transfer Attributes                    |  |

| 13.4.8    | Termination Signals                    |  |

| 13.4.8.1  | Transfer Acknowledge                   |  |

| 13.4.8.2  | Burst Inhibit                          |  |

| 13.4.8.3  | Transfer Error Acknowledge             |  |

| 13.4.8.4  | Protocol for Termination Signals       |  |

| 13.4.9    | Storage Reservation Protocol           |  |

| 13.4.10   | Exception Control Cycles               |  |

| 13.4.10.1 | RETRY                                  |  |

| Paragraph<br>Number | Title | Page<br>Number |

|---------------------|-------|----------------|

|                     |       |                |

### Section 14 Endian Modes

| 14.1 | Little-Endian System Features         | 14-2 |

|------|---------------------------------------|------|

| 14.2 | Big-Endian System Features            | 14-4 |

| 14.3 | PowerPC Little-Endian System Features | 14-4 |

| 14.4 | Setting the Endian Mode Of Operation  | 14-5 |

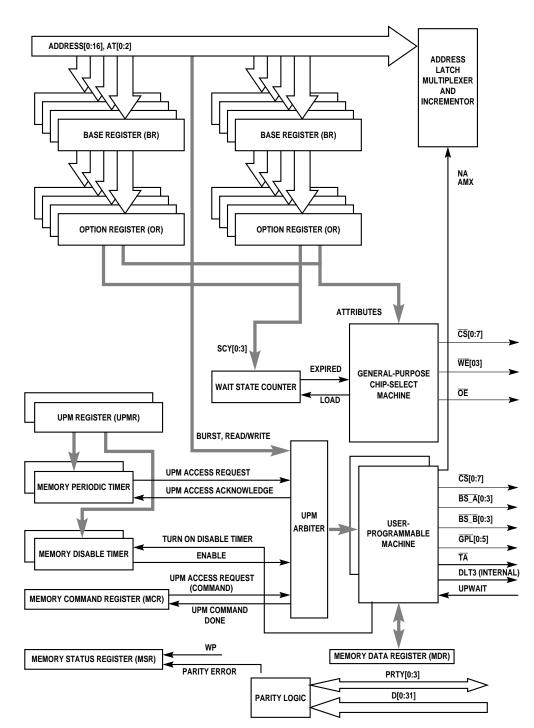

#### Section 15 Memory Controller

| Features                  | <br>15-1 |

|---------------------------|----------|

| <b>Basic Architecture</b> | <br>15-3 |

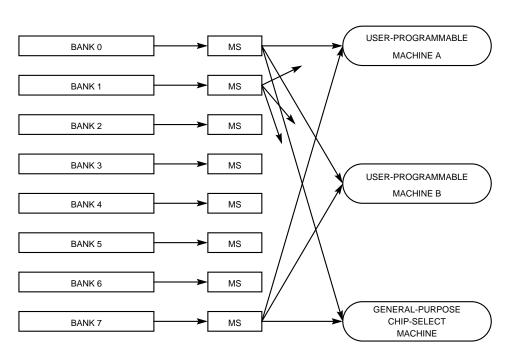

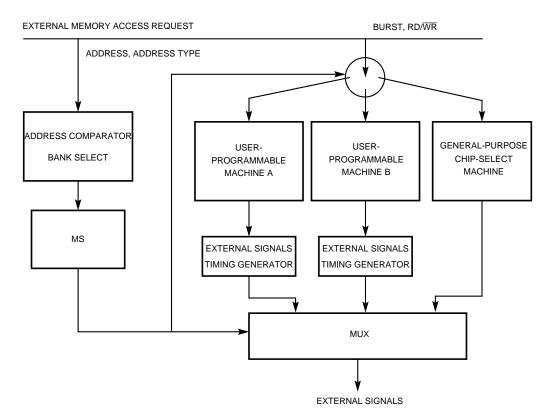

| 15.2      | Basic Architecture15-3                             |

|-----------|----------------------------------------------------|

| 15.2.1    | Registers Associated with the Memory Controller    |

| 15.2.1.1  | 8-, 16-, and 32-Bit Port Size Configuration        |

| 15.2.1.2  | Write-Protect Configuration                        |

| 15.2.1.3  | Address and Address Space Checking                 |

| 15.2.1.4  | Parity Generation and Checking 15-7                |

| 15.2.1.5  | Transfer Error Acknowledge Generation              |

| 15.2.2    | The General-Purpose Chip-Select Machine            |

| 15.2.2.1  | Programmable Wait State configuration              |

| 15.2.2.2  | Extended Hold Time on Read Accesses                |

| 15.2.2.3  | Global Chip-Select Operation                       |

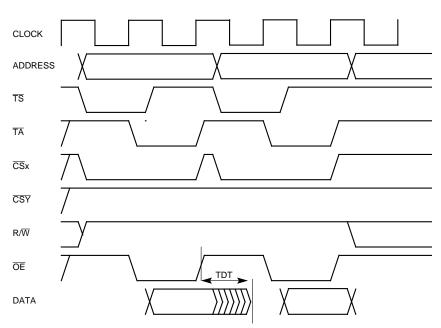

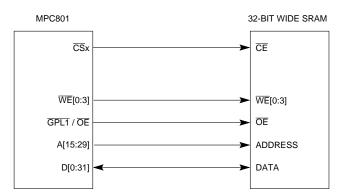

| 15.2.2.4  | SRAM interface15-16                                |

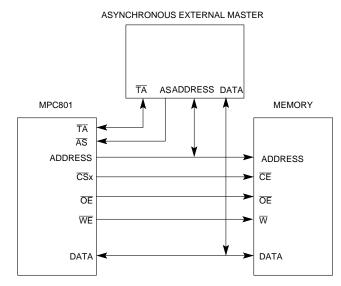

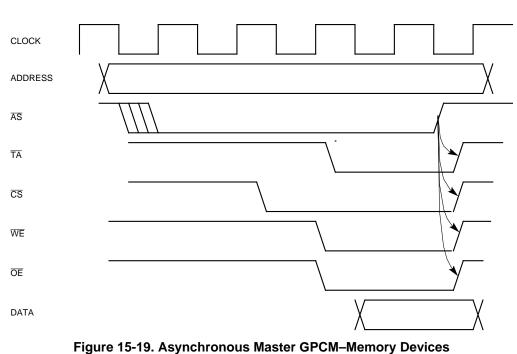

| 15.2.2.5  | GPCM External Asynchronous Master Support 15-17    |

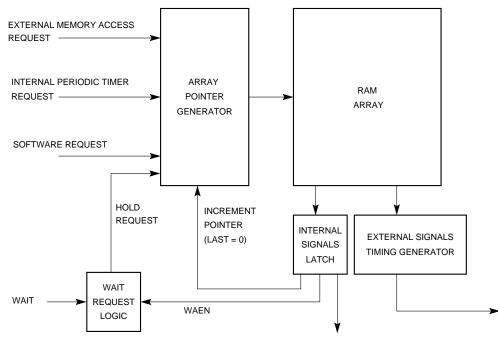

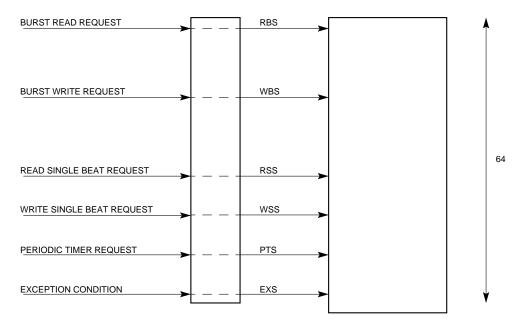

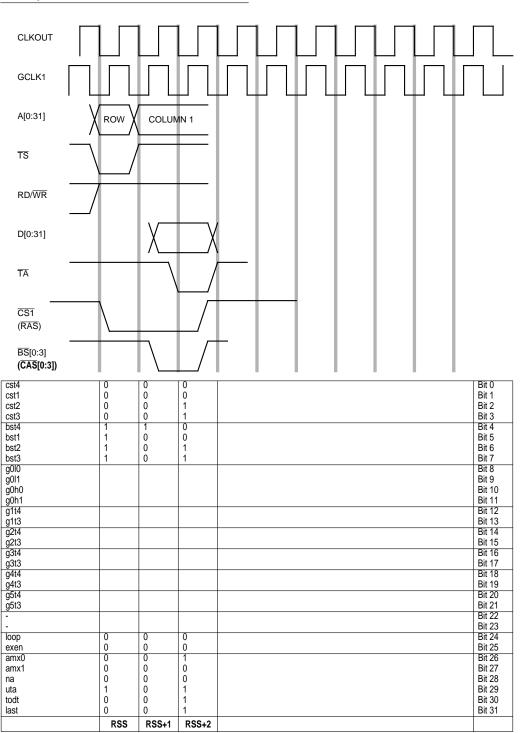

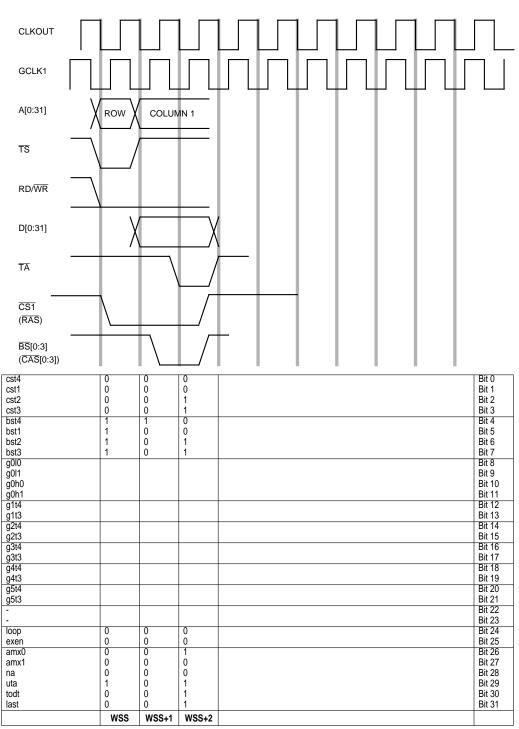

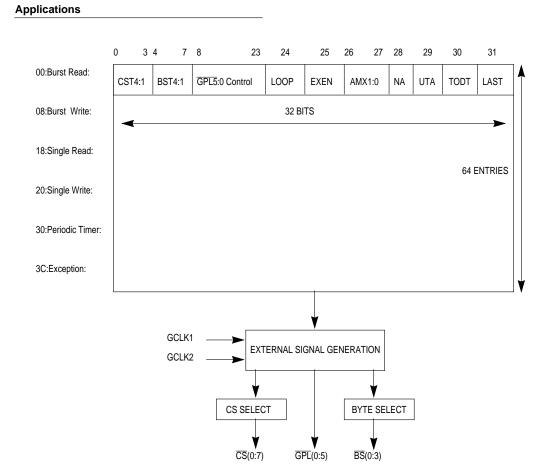

| 15.2.3    | User-Programmable Machines15-19                    |

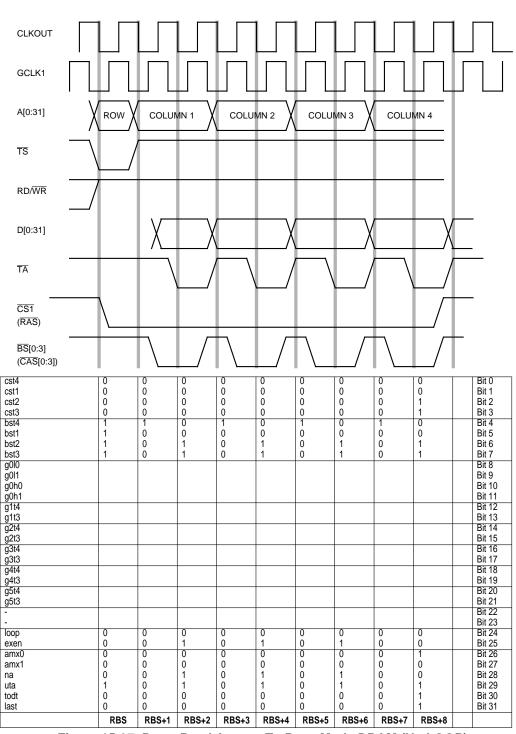

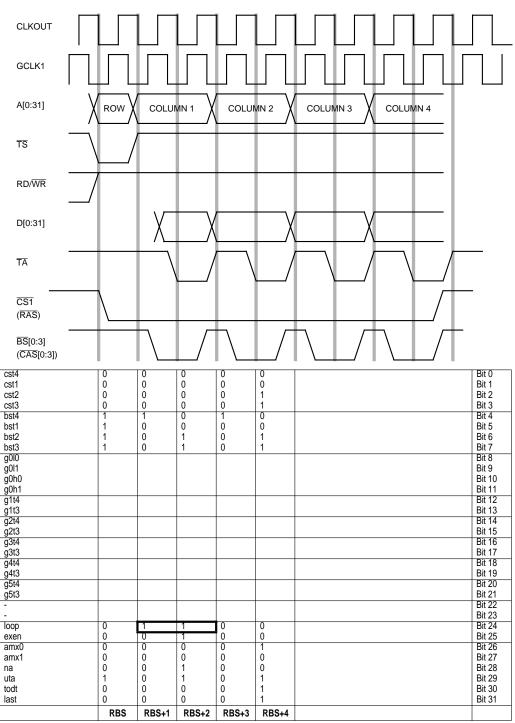

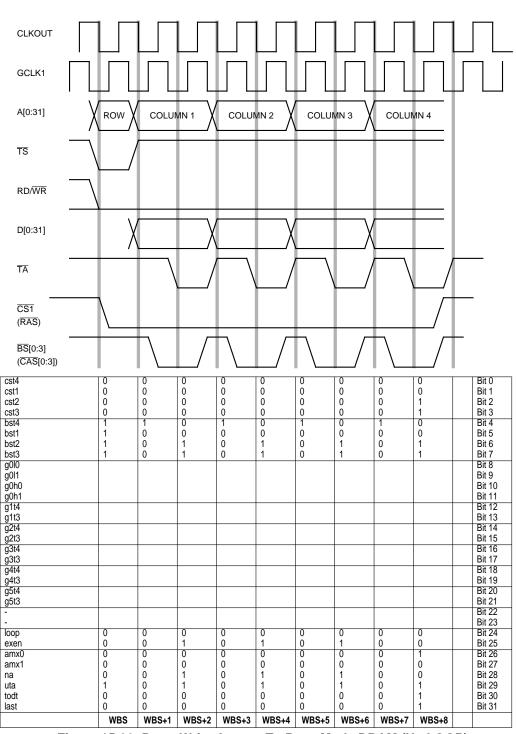

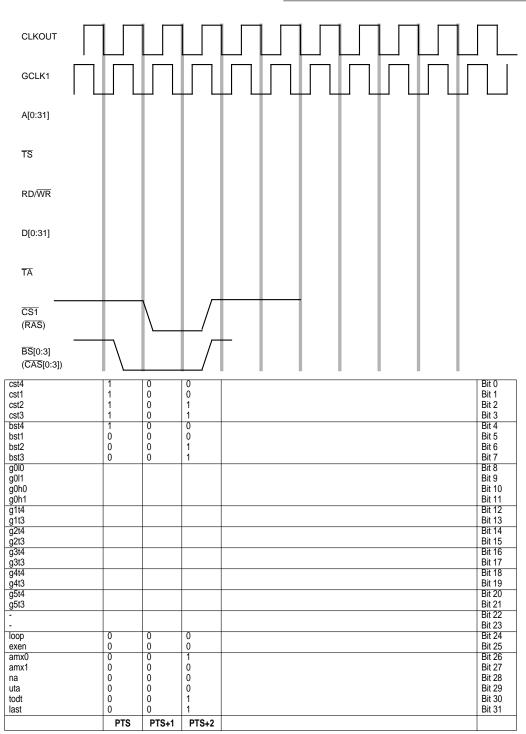

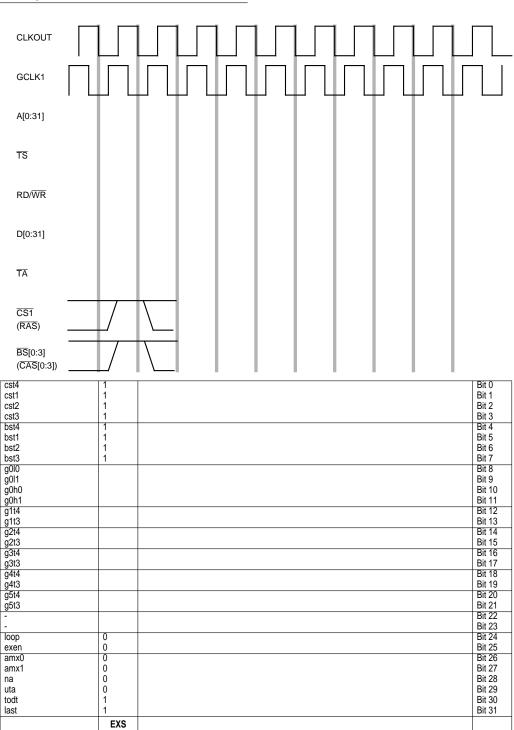

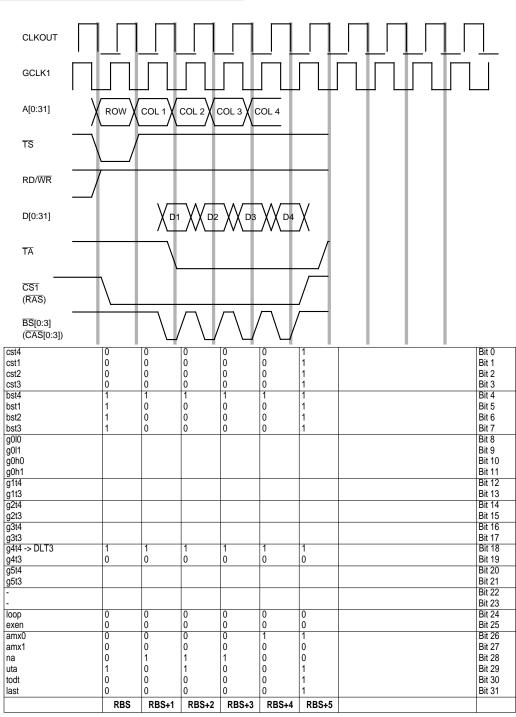

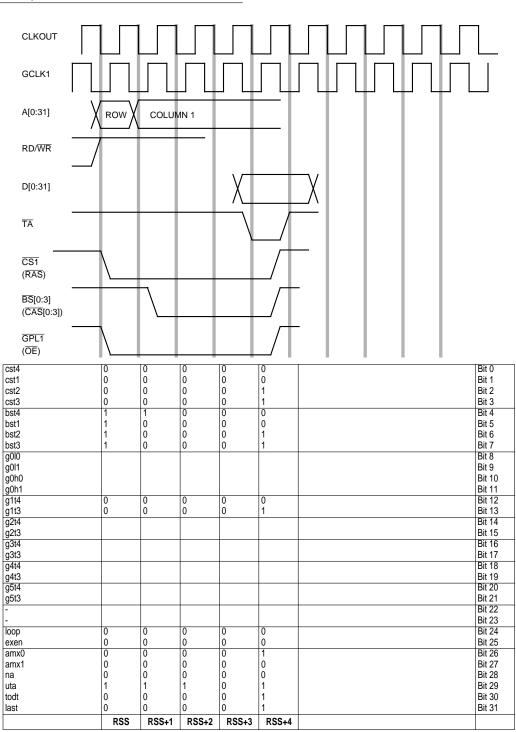

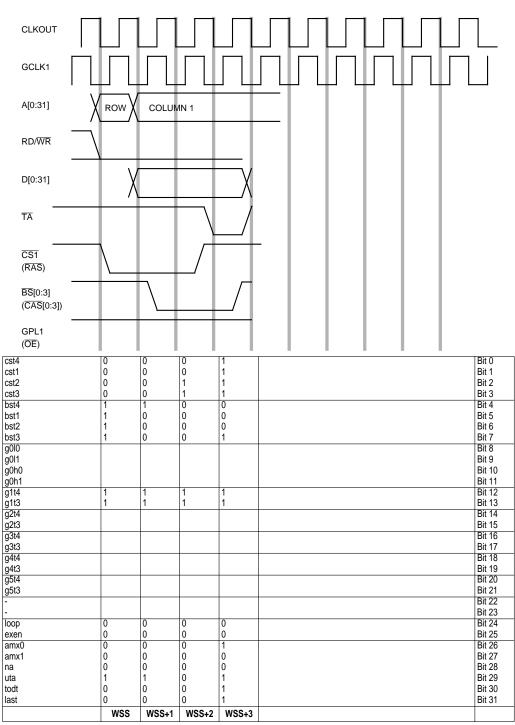

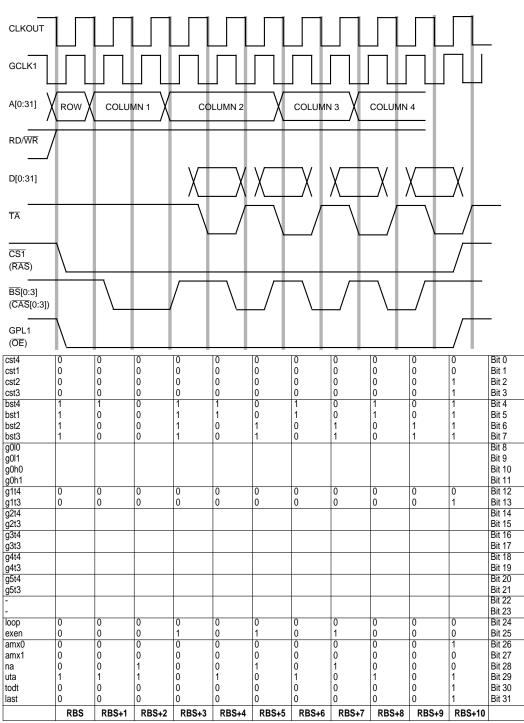

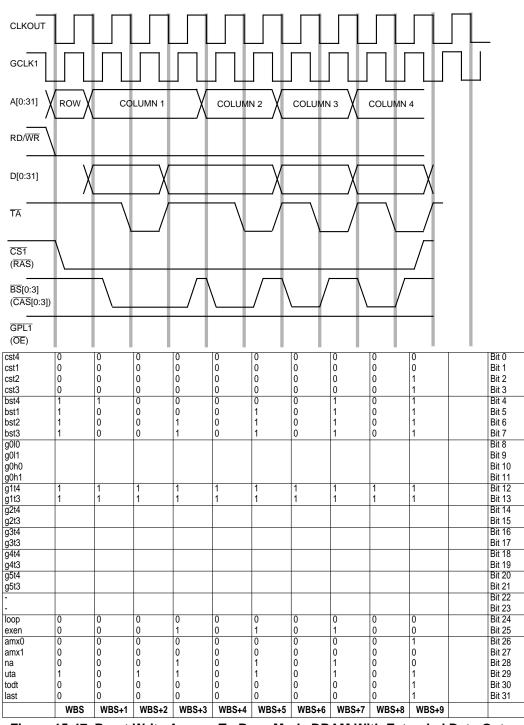

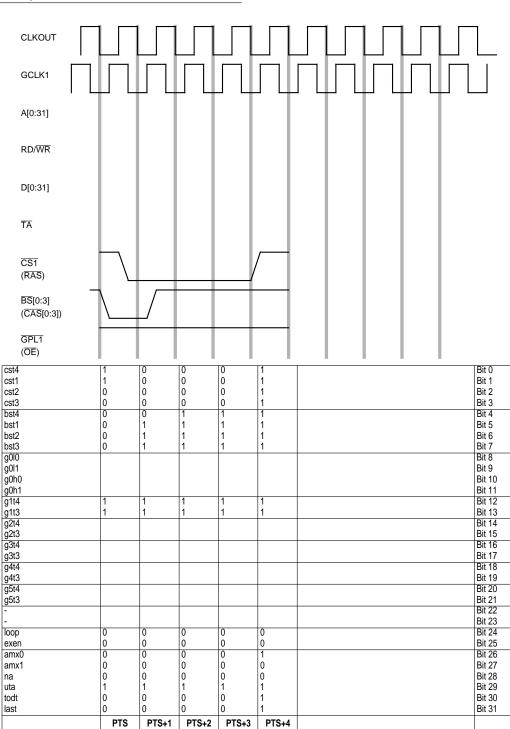

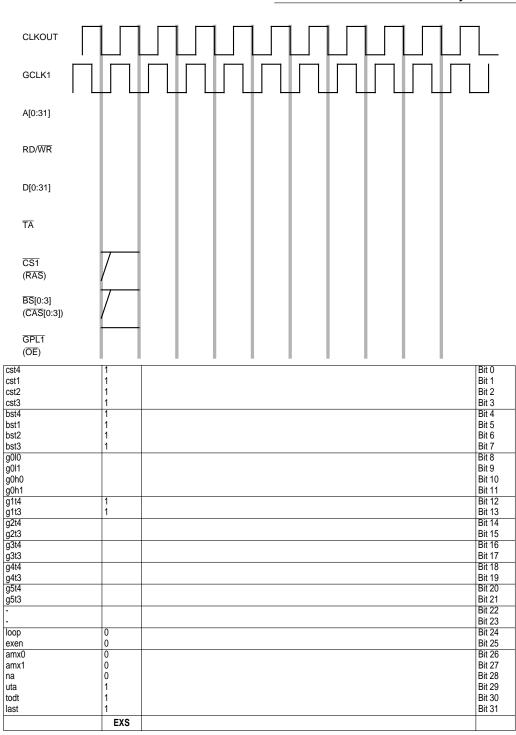

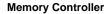

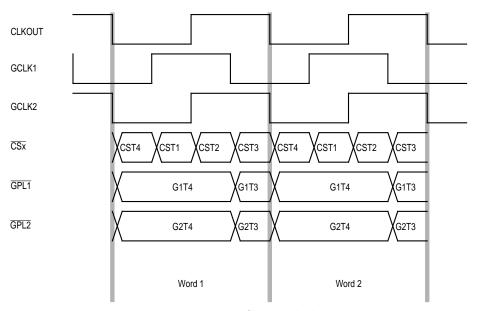

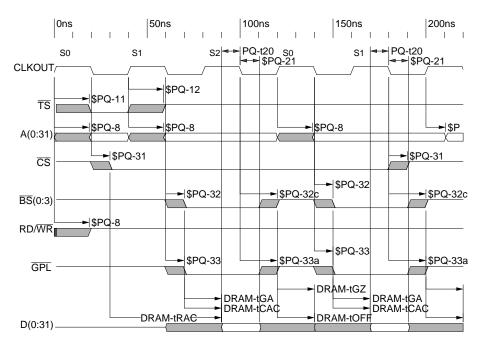

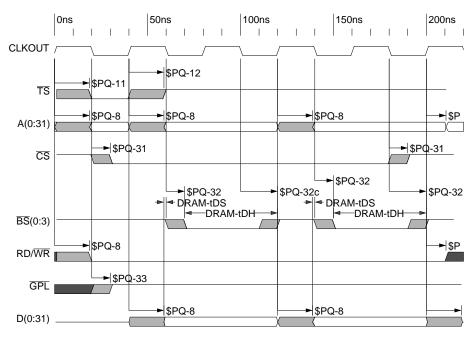

| 15.2.3.1  | RAM Word Structure and Timing Specification 15-25  |

| 15.2.3.2  | CS Signals15-28                                    |

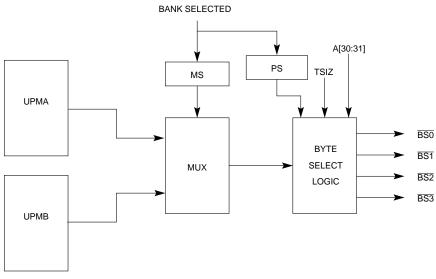

| 15.2.3.3  | Byte Select Signals15-29                           |

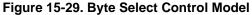

| 15.2.3.4  | General-Purpose Signals15-30                       |

| 15.2.3.5  | Loop Control Signal15-31                           |

| 15.2.3.6  | Exception Handling15-31                            |

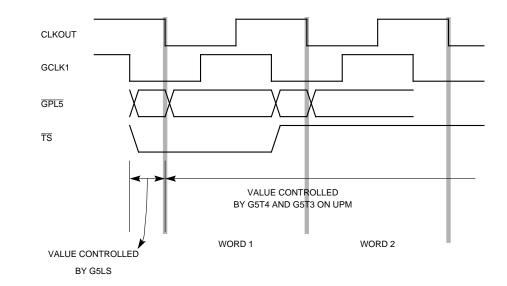

| 15.2.3.7  | Address Control Signals15-32                       |

| 15.2.3.8  | The Disable Timer Mechanism                        |

| 15.2.3.9  | Transfer Acknowledge And Data Sample Control 15-36 |

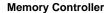

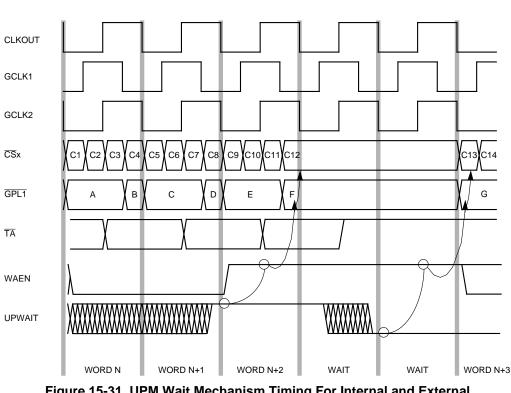

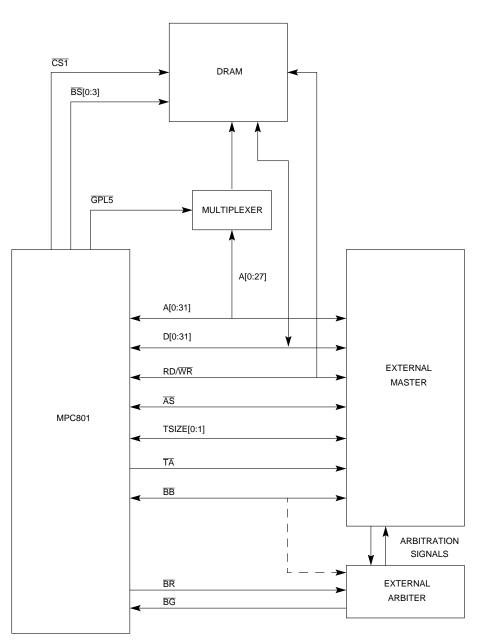

| 15.2.3.10 | The WAIT Mechanism15-36                            |

| 15.2.3.11 | Location of UPM Start Addresses                    |

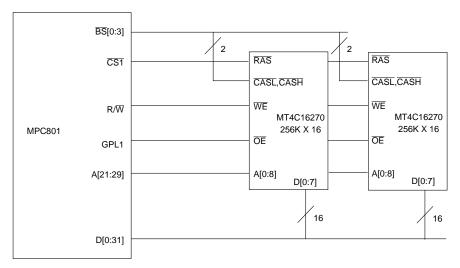

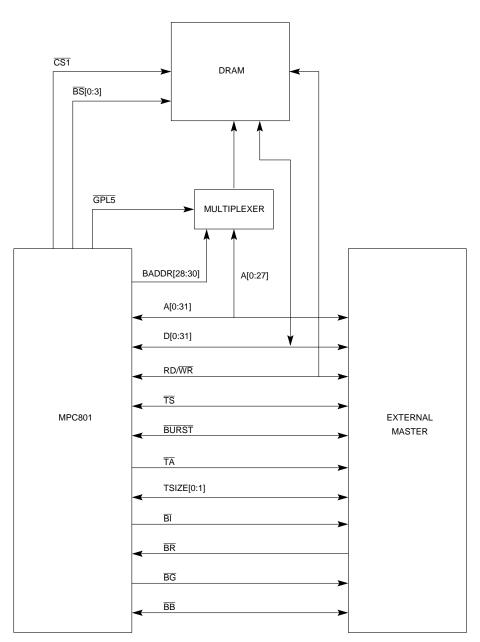

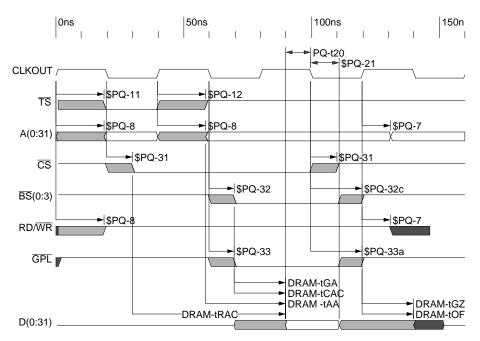

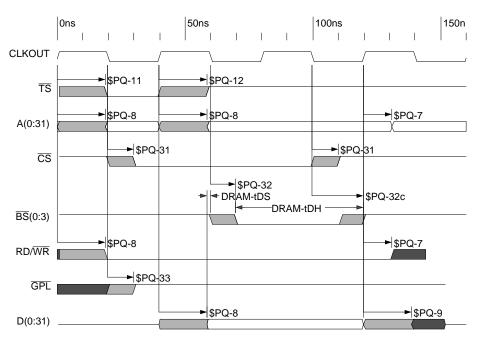

| 15.2.3.12 | Example DRAM Interface15-39                        |

| 15.2.3.13 | Extended Data-Out Interface Example15-52           |

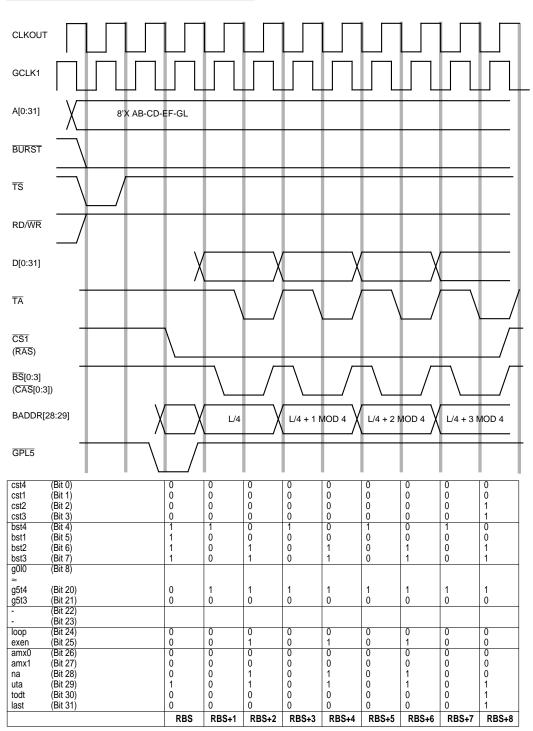

| 15.3      | External Master Support15-59                       |

| 15.4      | Programming the Memory Controller                  |

| 15.4.1    | Memory Status Register15-68                        |

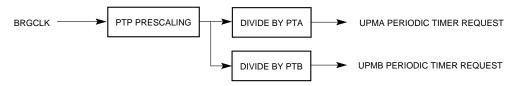

| 15.4.2    | Memory Periodic Timer Prescaler Register           |

15.1

| Paragraph<br>Number | Title                   | Page<br>Number |

|---------------------|-------------------------|----------------|

| 15.4.3              | Base Register           | 15-70          |

| 15.4.4              | Option Register         | 15-72          |

| 15.4.5              | Machine A Mode Register | 15-75          |

| 15.4.6              | Machine B Mode Register | 15-78          |

| 15.4.7              | Memory Command Register | 15-82          |

| 15.4.8              | Memory Data Register    |                |

| 15.4.9              | Memory Address Register | 15-84          |

### Section 16 Serial Communication Modules

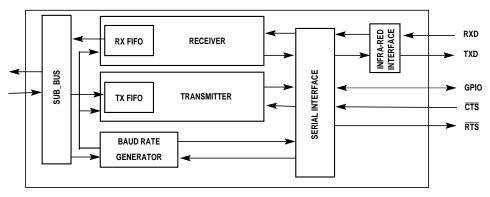

| 16.1     | The UART Controllers                                      |            |

|----------|-----------------------------------------------------------|------------|

| 16.2     | Features                                                  |            |

| 16.3     | Serial Interface Signals                                  |            |

| 16.3.1   | Sub-Block Description                                     |            |

| 16.3.1.1 | The Transmitter                                           |            |

| 16.3.1.2 | The Receiver                                              |            |

| 16.3.1.3 | The Baud Rate Generator                                   |            |

| 16.3.1.4 | The Global Controller Interface                           |            |

| 16.4     | The Serial Controller                                     |            |

| 16.4.1   | Programming the Serial Controller                         |            |

| 16.4.1.1 | Serial Controller Command Register                        |            |

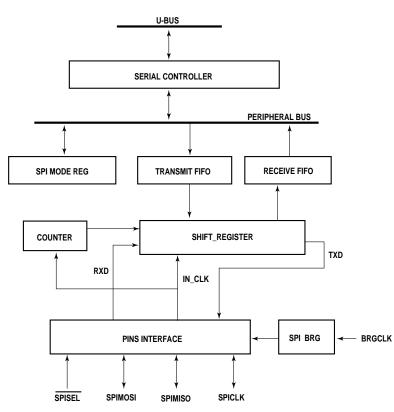

| 16.4.2   | The Serial Peripheral Interface                           |            |

| 16.4.2.1 | Features                                                  | 16-16      |

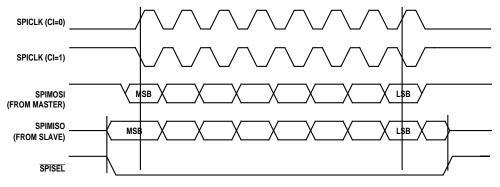

| 16.4.2.2 | Clocking and Pin Functions                                |            |

| 16.4.2.3 | SPI Transmission and Reception Process                    |            |

| 16.4.2.4 | Programming the Serial Peripheral Interface               |            |

| 16.4.3   | The I <sup>2</sup> C Controller                           |            |

| 16.4.3.1 | Features                                                  |            |

| 16.4.3.2 | Clocking and Pin Functions                                |            |

| 16.4.3.3 | I <sup>2</sup> C Controller Transmission and Reception Pr | ocess16-28 |

| 16.4.3.4 | Programming the I <sup>2</sup> C Controller               |            |

| 16.5     | The Parallel I/O Port                                     | 16-35      |

| 16.5.1   | Features                                                  | 16-35      |

| 16.5.2   | Port B Pin Functions                                      | 16-35      |

| 16.5.3   | The Port B Registers                                      | 16-37      |

| 16.5.3.1 | Port B Open-Drain Register                                |            |

| 16.5.3.2 | Port B Data Register                                      |            |

| 16.5.3.3 | Port B Data Direction Register                            |            |

| 16.5.3.4 | Port B Pin Assignment Register                            |            |

#### Paragraph Number

Title

Page Number

### Section 17 Data Alignment

### Section 18 Development Support

| 18.1     | Program Flow Tracking                             | 18-1  |

|----------|---------------------------------------------------|-------|

| 18.1.1   | Basic Operation                                   | 18-2  |

| 18.1.1.1 | The Internal Hardware                             | 18-2  |

| 18.1.1.2 | Special Case of Queue Flush Information           | 18-4  |

| 18.1.1.3 | Program Trace In Debug Mode                       | 18-5  |

| 18.1.1.4 | Sequential Instructions Marked As Indirect Branch | 18-5  |

| 18.1.1.5 | The External Hardware                             | 18-5  |

| 18.1.1.6 | Benefits of Compression                           | 18-7  |

| 18.1.2   | Controlling the Instruction Fetch Show Cycle      | 18-8  |

| 18.2     | Watchpoint And Breakpoint Generation              |       |

| 18.2.1   | Internal Watchpoints and Breakpoints              | 18-9  |

| 18.2.1.1 | Features                                          | 18-11 |

| 18.2.1.2 | Restrictions                                      | 18-12 |

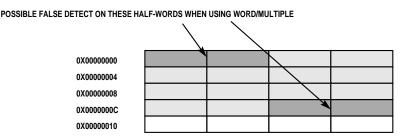

| 18.2.1.3 | Byte And Half-Word Working Modes                  | 18-12 |

| 18.2.1.4 | Context Dependent Filter                          | 18-14 |

| 18.2.1.5 | Ignore First Match Option                         | 18-14 |

| 18.2.1.6 | Generating Compare Types                          | 18-15 |

| 18.2.2   | Basic Watchpoint/Breakpoint Operation             | 18-16 |

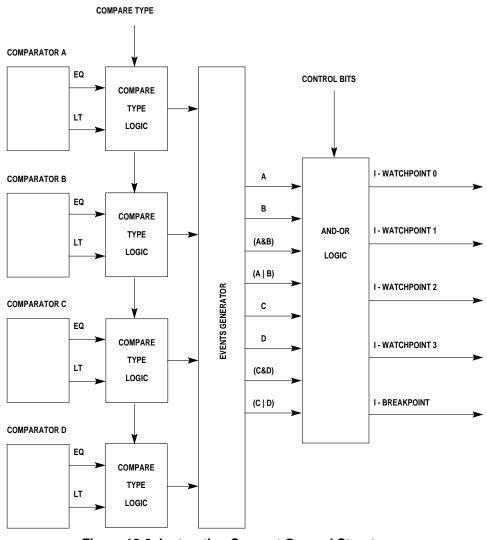

| 18.2.2.1 | Instruction Support                               | 18-16 |

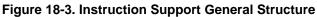

| 18.2.2.2 | Load/Store Support                                | 18-17 |

| 18.2.2.3 | Counter Support                                   | 18-18 |

| 18.2.2.4 | Trap Enable Programming                           | 18-20 |

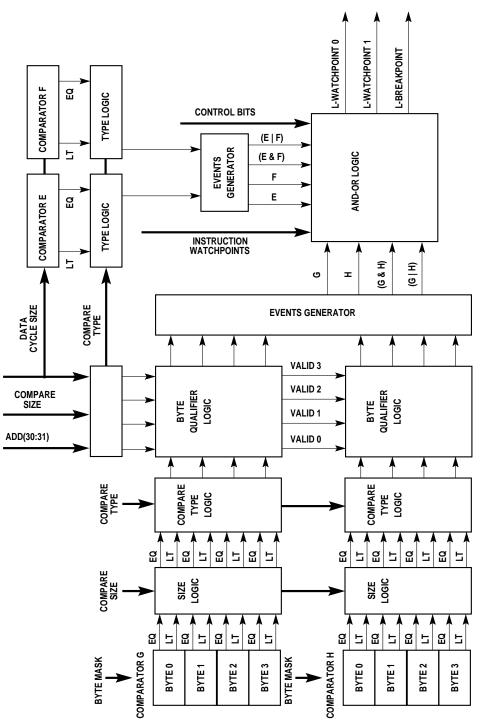

| 18.3     | Development System Interface                      | 18-20 |

| 18.3.1   | Trap Enable Mode                                  | 18-22 |

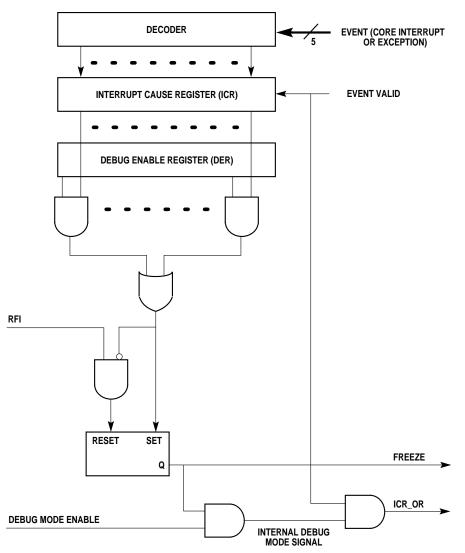

| 18.3.2   | Debug Mode                                        | 18-22 |

| 18.3.2.1 | Debug Mode Enable vs. Debug Mode Disable          | 18-24 |

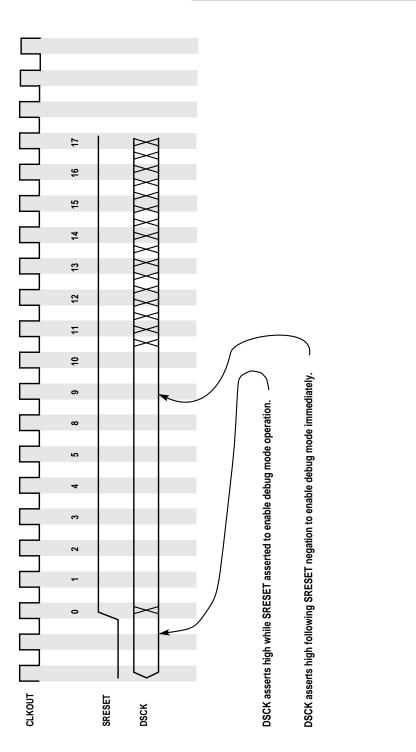

| 18.3.2.2 | Entering Debug Mode                               | 18-24 |

| 18.3.2.3 | CheckStop State And Debug Mode                    | 18-27 |

| 18.3.2.4 | Saving the Machine State in Debug Mode            | 18-27 |

| 18.3.2.5 | Running in Debug Mode                             | 18-28 |

| 18.3.2.6 | Exiting Debug Mode                                | 18-28 |

| 18.3.3   | The Development Port                              | 18-28 |

| 18.3.3.1 | The Development Port Pins                         | 18-29 |

| 18.3.3.2 | Development Port Registers                        | 18-30 |

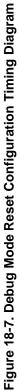

| 18.3.3.3 | Development Port Serial Communications            | 18-31 |

| Paragraph<br>Number | Page<br>Title Number                                  |

|---------------------|-------------------------------------------------------|

| 18.4                | The Software Monitor Debugger18-40                    |

| 18.4.1              | Freeze Indication18-41                                |

| 18.5                | Programming the Development Support Registers         |

| 18.5.1              | Protecting the Development Port Registers             |

| 18.5.2              | Development Port Registers18-42                       |

| 18.5.2.1            | Comparator A–D Value Register                         |

| 18.5.2.2            | Comparator E–F Value Register                         |

| 18.5.2.3            | Comparator G–H Value Register                         |

| 18.5.2.4            | Breakpoint Address Register                           |

| 18.5.2.5            | Instruction Support Control Register                  |

| 18.5.2.6            | Load/Store Support Comparators Control Register 18-46 |

| 18.5.2.7            | Load/Store Support AND–OR Control Register            |

| 18.5.2.8            | Breakpoint Counter A Value and Control Register18-50  |

| 18.5.2.9            | Breakpoint Counter B Value and Control Register18-51  |

| 18.5.3              | Debug Mode Registers18-51                             |

| 18.5.3.1            | Interrupt Cause Register18-51                         |

| 18.5.3.2            | Debug Enable Register18-53                            |

| 18.5.4              | Development Port Data Register                        |

### Section 19 IEEE 1149.1 Test Access Port

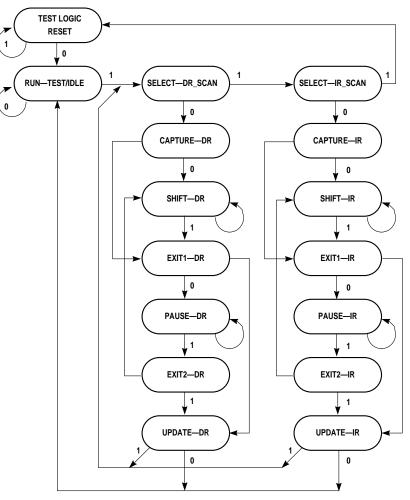

| 19.1   | The TAP Controller               | 19-3  |

|--------|----------------------------------|-------|

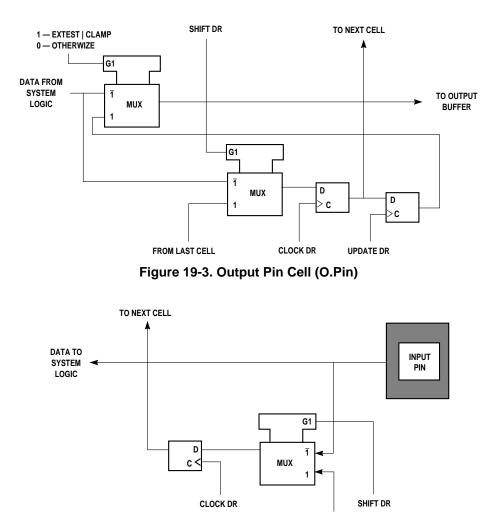

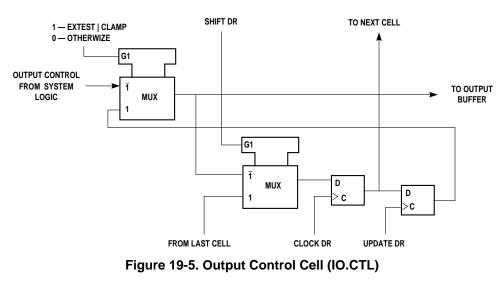

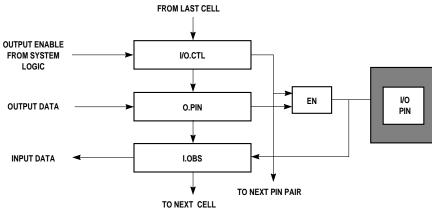

| 19.2   | The Boundary Scan Register       | 19-4  |

| 19.3   | The Instruction Register         | 19-17 |

| 19.3.1 | The External Test Instruction    | 19-18 |

| 19.3.2 | The sample/preload Instruction   | 19-18 |

| 19.3.3 | The bypass Instruction           | 19-18 |

| 19.3.4 | The clamp Instruction            | 19-19 |

| 19.3.5 | The hi-z Instruction             | 19-19 |

| 19.4   | MPC801 Restrictions              | 19-19 |

| 19.5   | Nonscan Chain Operation          | 19-19 |

| 19.6   | Motorola MPC801 BSDL Description | 19-19 |

### Paragraph Number

Title

Page Number

#### Section 20 Electrical Characteristics

| 20.1   | Maximum Ratings (GND = 0V)                             |  |

|--------|--------------------------------------------------------|--|

| 20.2   | Thermal Characteristics                                |  |

| 20.3   | Power Considerations                                   |  |

| 20.3.1 | Layout Practices                                       |  |

| 20.4   | DC Electrical Specifications ( $V_{CC} = 3.0 - 3.6V$ ) |  |

| 20.5   | MPC801 AC Electrical Specifications Control Timing     |  |

| 20.6   | IEEE 1149.1 Electrical Specifications                  |  |

#### Section 21 Communication Electrical Characteristics

| 21.1 | PIO AC Electrical Specifications                           | 21-1 |

|------|------------------------------------------------------------|------|

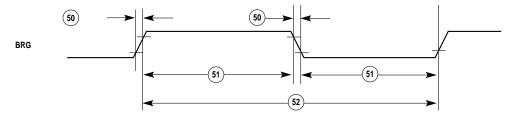

| 21.2 | UART BRG Clock AC Electrical Specifications                |      |

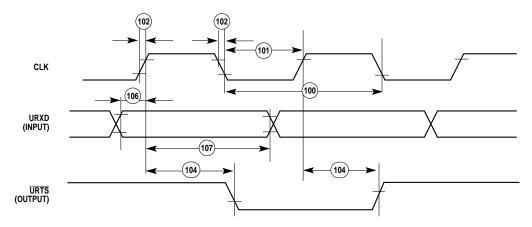

| 21.3 | UART—External Clock AC Electrical Specifications           |      |

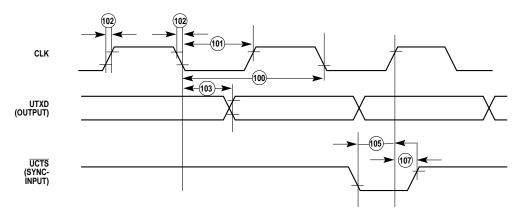

| 21.4 | UART—Internal Clock AC Electrical Specifications           | 21-3 |

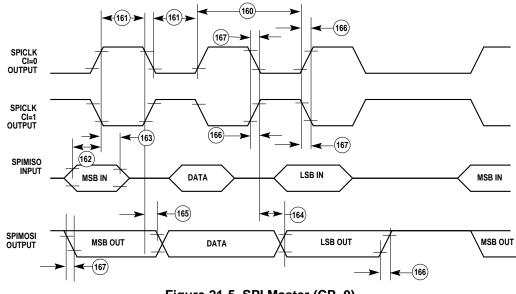

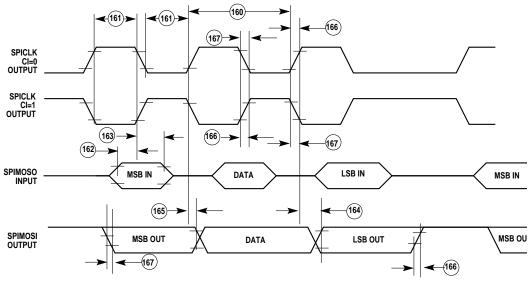

| 21.5 | SPI Master AC Electrical Specifications                    |      |

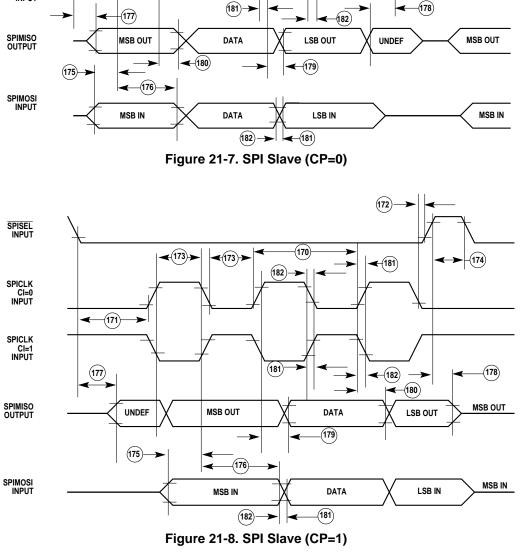

| 21.6 | SPI Slave AC Electrical Specifications                     |      |

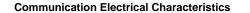

| 21.7 | I <sup>2</sup> C AC Electrical Specifications–SCL < 100kHz | 21-8 |

| 21.8 | I <sup>2</sup> C AC Electrical Specifications–SCL > 100kHz |      |

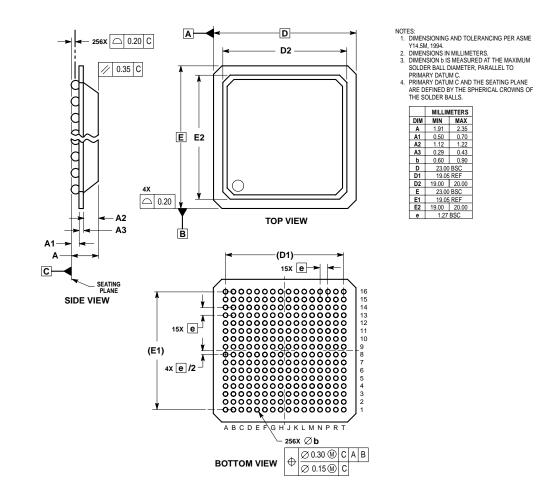

### Section 22 Mechanical Specifications

| 22.1 | Ordering Information                              |  |

|------|---------------------------------------------------|--|

| 22.2 | Pin Assignments – PBGA-Top View                   |  |

| 22.3 | Package Dimensions-Plastic Ball Grid Array (PBGA) |  |

### Section 23

### Terminology

### Appendix A Quick Reference Guide to MPC801 Registers

| A.1 | Core Control Registers      | A-1 |  |

|-----|-----------------------------|-----|--|

| A.2 | Internally Mapped Registers | A-4 |  |

Paragraph Number

Title

### Page Number

## AppendixB Applications

| B.1     | MPC801 Basic Initialization                        | B-1  |

|---------|----------------------------------------------------|------|

| B.1.1   | Programming the UPM                                | B-2  |

| B.1.2   | MPC801 MMU/Cache Example                           |      |

| B.1.2.1 | Basic MMU and Cache Concept                        | B-5  |

| B.1.2.2 | General Concept                                    | B-5  |

| B.1.3   | Memory Management Unit                             | B-6  |

| B.1.3.1 | Memory Protection                                  |      |

| B.1.3.2 | MMU Example                                        | B-10 |

| B.1.4   | M_TWB MMU TABLEWALK BASE REGISTER                  | B-12 |

| B.1.5   | MI_CTR Instruction MMU Control Register            | B-12 |

| B.1.6   | Mx_AP Instruction/Data Access Protection Register  | B-13 |

| B.1.7   | MD_CTR Data MMU Control Register                   | B-14 |

| B.1.8   | Level One Descriptor Format Register               | B-15 |

| B.1.9   | Level Two Descriptor 1K Resolution Format Register | B-18 |

| B.1.10  | Level Two Descriptor 4K Resolution Format Register | B-20 |

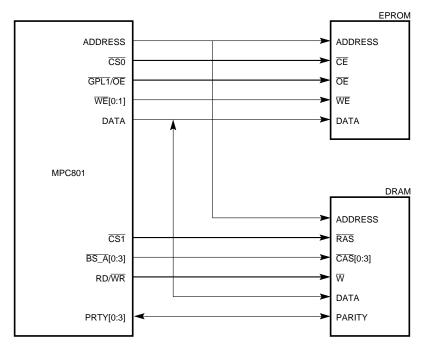

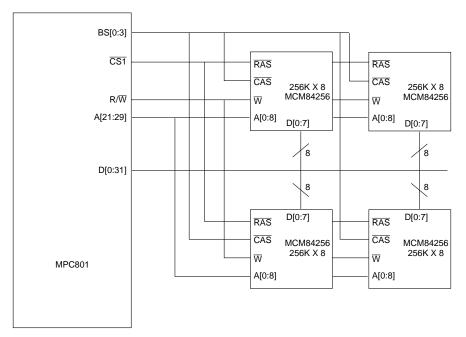

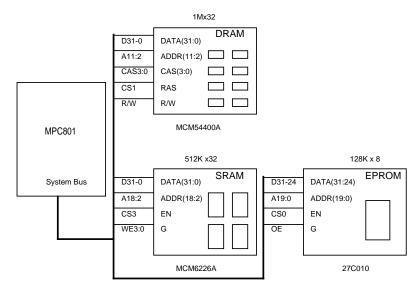

| B.2     | Configuring the MPC801 Memory Controller           | B-26 |

| B.2.1   | General Configuration                              | B-27 |

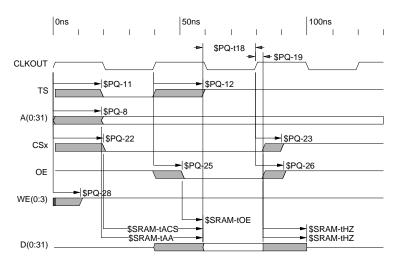

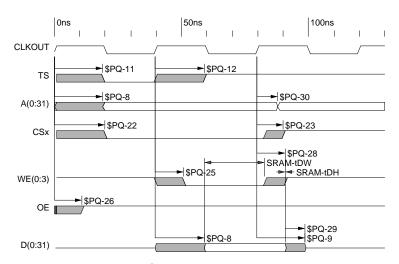

| B.2.2   | SRAM Configuration                                 | B-27 |

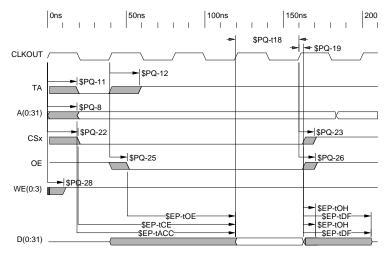

| B.2.3   | EPROM Configuration                                | B-31 |

| B.2.4   | DRAM Configuration                                 |      |

| B.3     | Porting to the PowerQUICC                          | B-43 |

| B.4     | Using the PowerPC Core                             | B-44 |

| B.5     | Bit Labeling                                       |      |

| B.5.1   | Code Portability                                   | B-44 |

| B.6     | Cache                                              | B-44 |

| B.6.1   | Cache Performance Impact                           | B-44 |

| B.6.2   | Data Coherency                                     | B-45 |

| B.6.3   | Debugging                                          | B-45 |

| B.7     | Memory Management Unit                             | B-45 |

| B.8     | Real-Time Operating Systems                        | B-45 |

## LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                                                                                  | Page<br>Number |

|------------------|--------------------------------------------------------------------------------------------------------|----------------|

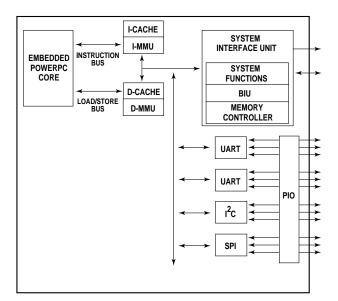

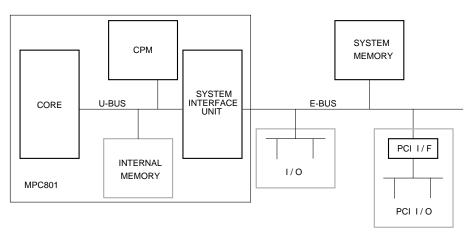

| 1-1.             | MPC801 Block Diagram                                                                                   | 1-4            |

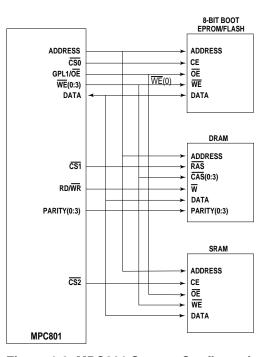

| 1-2.             | MPC801 System Configuration                                                                            |                |

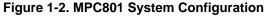

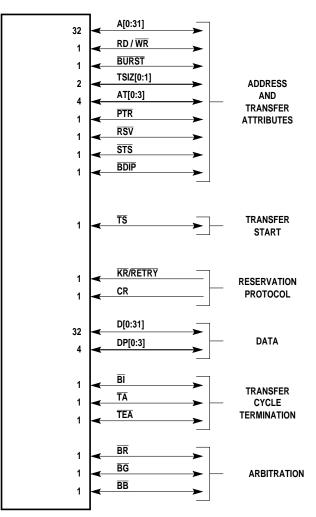

| 2-1.             | MPC801 External Signals                                                                                | 2-1            |

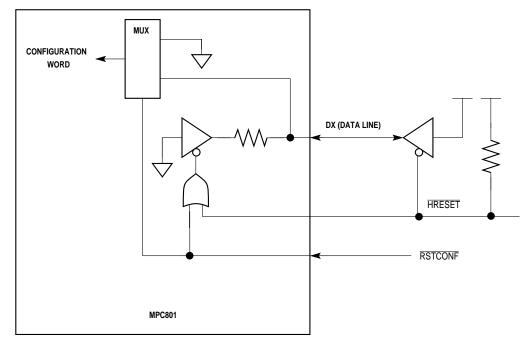

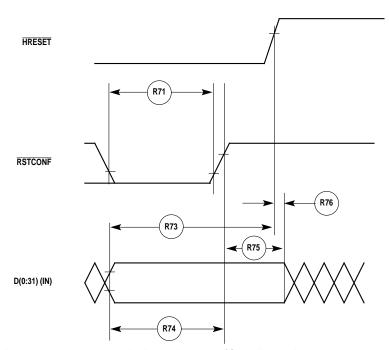

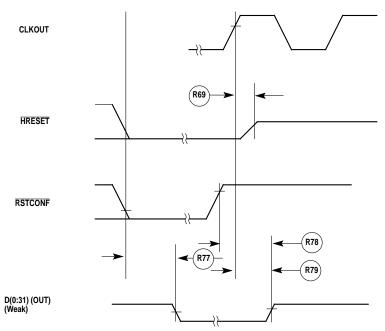

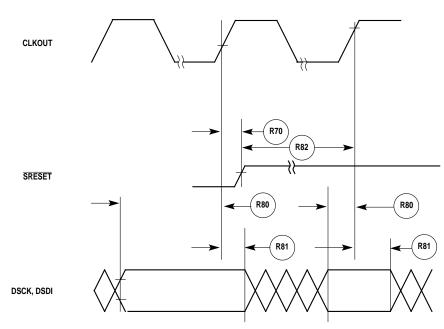

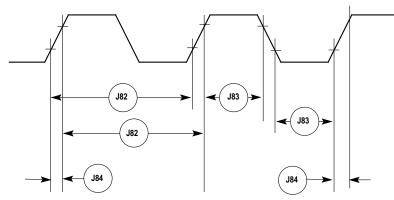

| 4-1.             | Reset Configuration Basic Scheme                                                                       | 4-6            |

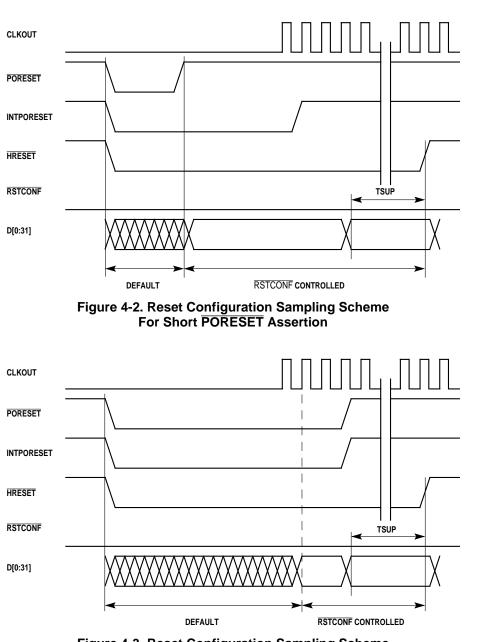

| 4-2.             | Reset Configuration Sampling Scheme For Short PORESET                                                  | 4 -            |

| 4.0              | Assertion                                                                                              | 4-7            |

| 4-3.             | Reset Configuration Sampling Scheme For Long PORESET<br>Assertion                                      | 4-7            |

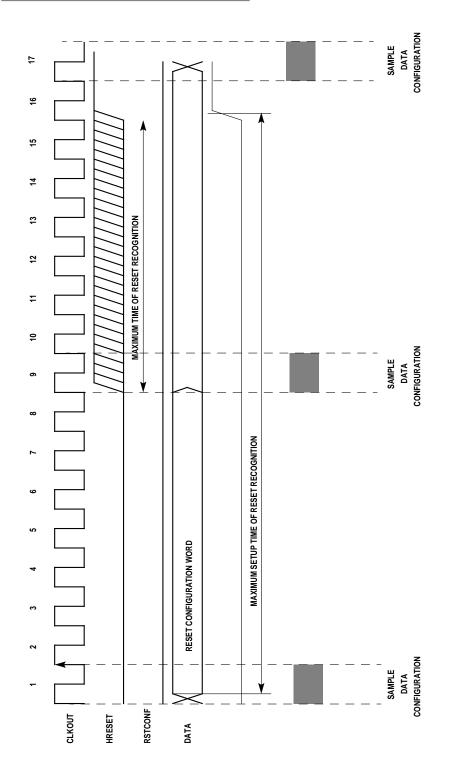

| 4-4.             | Reset Configuration Sampling Timing Requirements                                                       |                |

|                  |                                                                                                        |                |

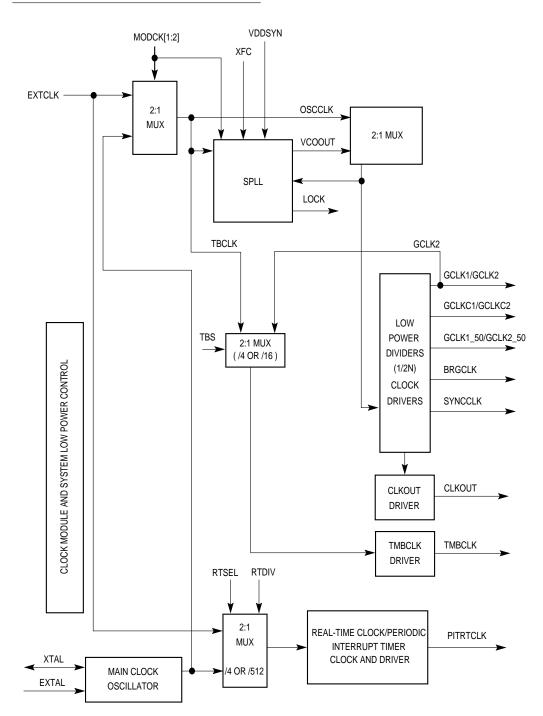

| 5-1.             | Clock Unit Block Diagram                                                                               | 5-2            |

| 5-2.             | MPC801 Power Supply                                                                                    | 5-3            |

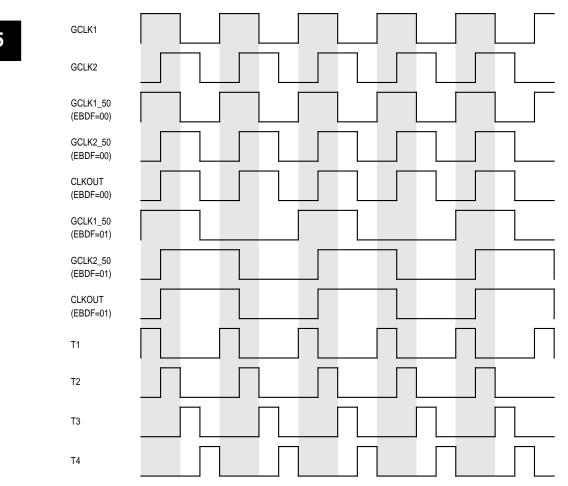

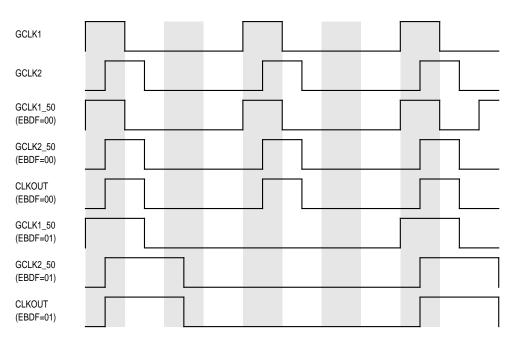

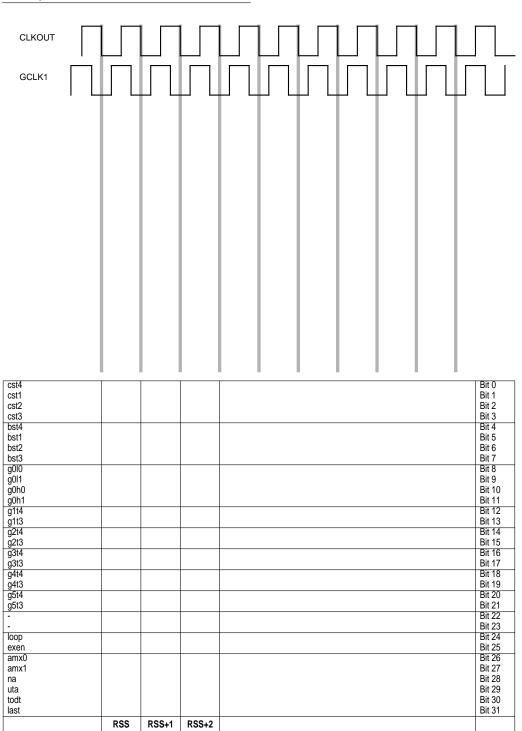

| 5-3.             | MPC801 Clocks Timing Diagram                                                                           | 5-4            |

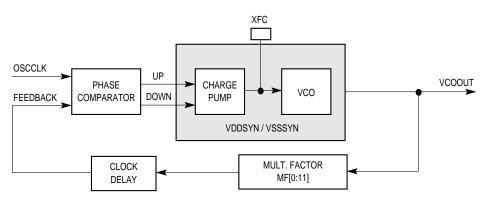

| 5-4.             | System PLL Block Diagram                                                                               |                |

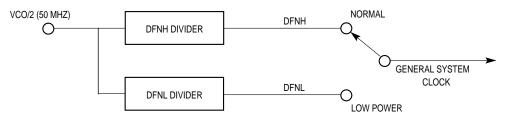

| 5-5.             | General System Clocks Select                                                                           |                |

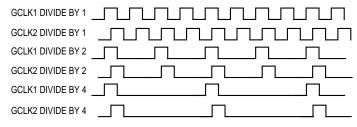

| 5-6.             | Divided System Clocks Timing Diagram                                                                   |                |

| 5-7.             | MPC801 Clocks For DFNH = 1 or DFNL = 0 Timing Diagram                                                  |                |

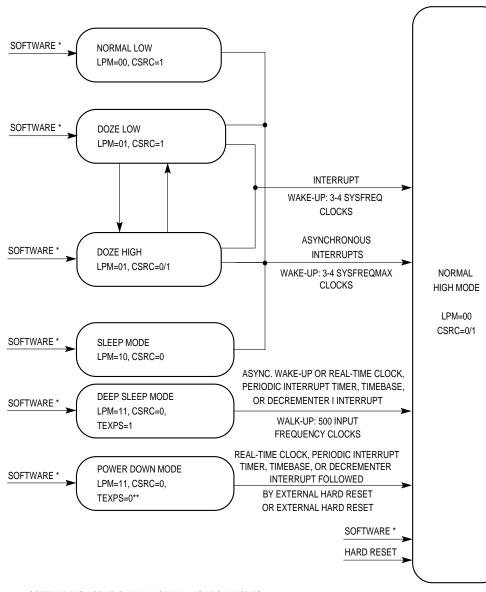

| 5-8.             | MPC801 Low-Power Modes Flowchart                                                                       |                |

| 5-9.             | MPC801 Basic Power Supply Configuration                                                                |                |

| 5-10.            | External Power Supply Scheme (2.0 V Internal Voltage)                                                  |                |

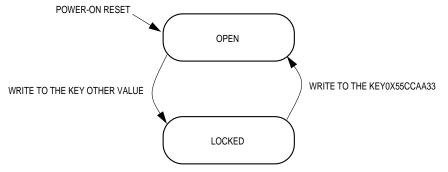

| 5-11.            | Key Mechanism Diagram                                                                                  | 5-24           |

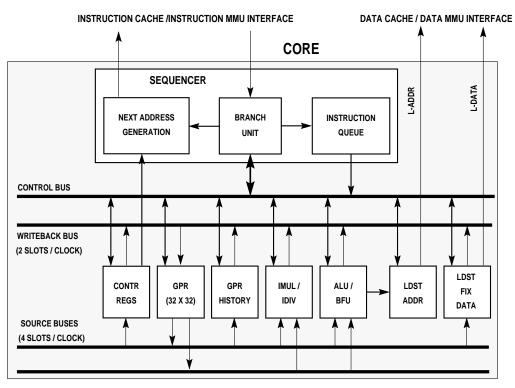

| 6-1.             | Core Block Diagram                                                                                     | 6-3            |

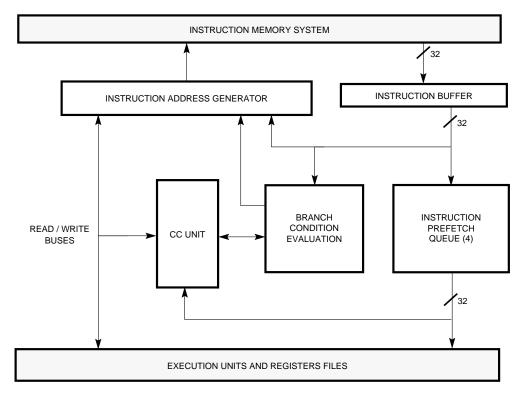

| 6-2.             | Instruction Flow Conceptual Diagram                                                                    |                |

| 6-3.             | Basic Instruction Pipeline Timing Diagram                                                              |                |

| 6-4.             | Sequencer Data Path                                                                                    |                |

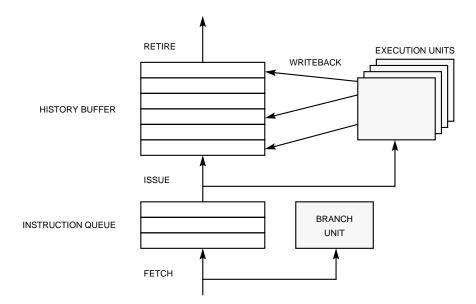

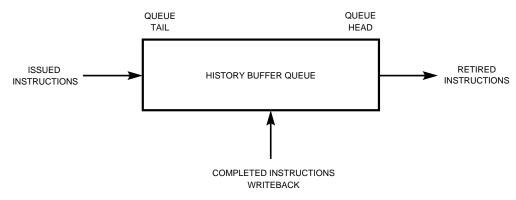

| 6-5.             | History Buffer Queue                                                                                   |                |

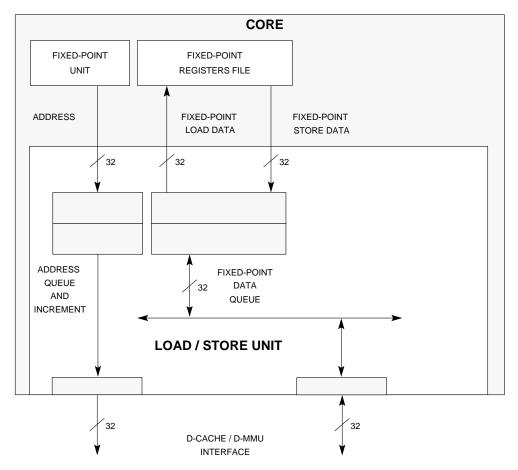

| 6-6.<br>6-7.     | Load/Store Unit Functional Block Diagram<br>Number of Bus Cycles Needed For Unaligned, Single Register | 6-26           |

|                  | Fixed-Point Load/Store Instructions                                                                    | 6-28           |

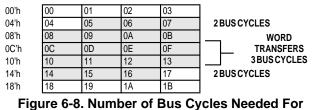

| 6-8.             | Number of Bus Cycles Needed For String Instruction Execution                                           | 6-30           |

| Figure<br>Number             | Title                                                                                                                                                        | Page<br>Number |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 8-1.<br>8-2.<br>8-3.<br>8-4. | Example of a Data Cache Load<br>Example of a Writeback Arbitration<br>Another Example of a Writeback Arbitration                                             | 8-5<br>8-5     |

| 8-4.<br>8-5.<br>8-6.<br>8-7. | Example of a Private Writeback Bus Load<br>Example of an External Load<br>Example of a Full History Buffer<br>Example of Branch Folding                      | 8-7<br>8-8     |

| 8-8.                         | Example of Branch Prediction                                                                                                                                 |                |

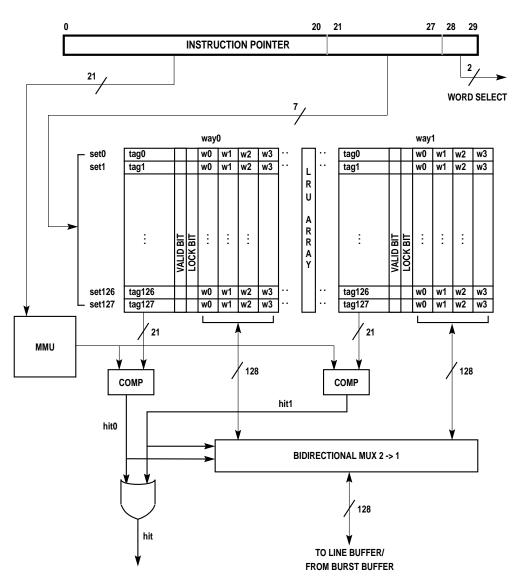

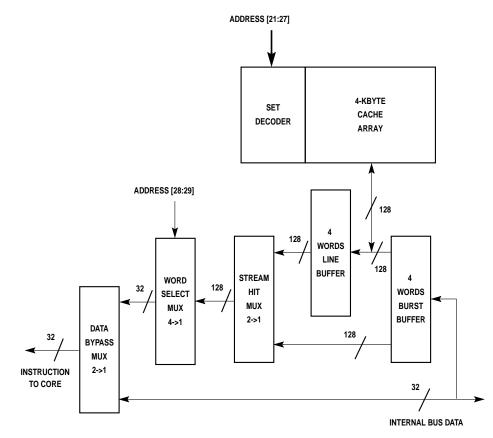

| 9-1.<br>9-2.                 | Instruction Cache Organization<br>Cache Data Path Block Diagram                                                                                              |                |

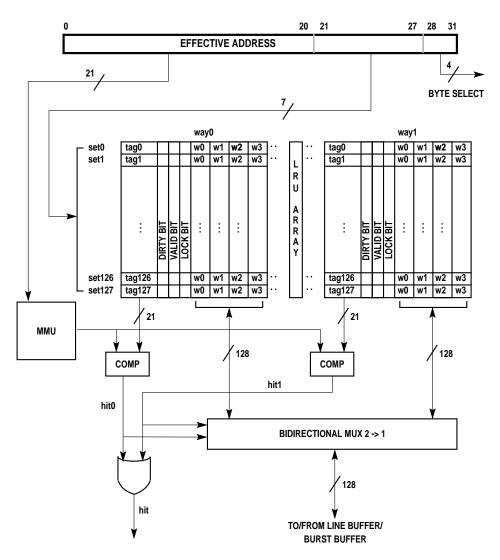

| 10-1.                        | Data Cache Organization                                                                                                                                      |                |

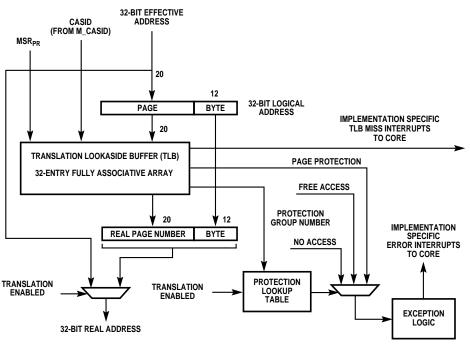

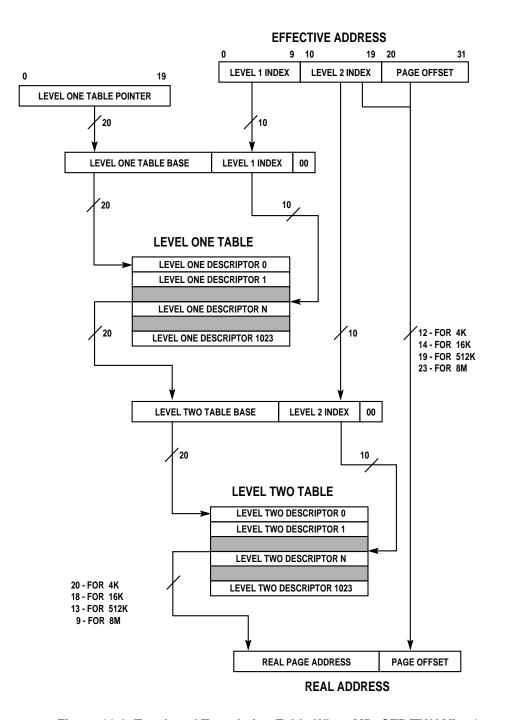

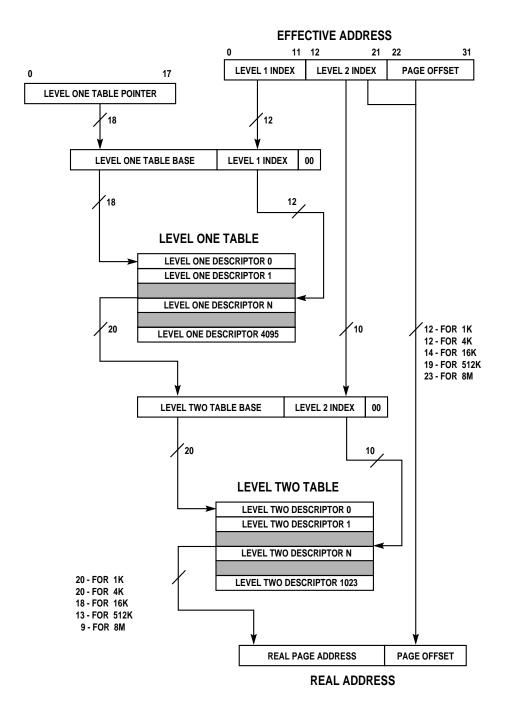

| 11-1.<br>11-2.<br>11-3.      | Effective to Real Address Translation For 4K Pages<br>Two Level Translation Table When MD_CTR(TWAM) = 1<br>Two Level Translation Table When MD_CTR(TWAM) = 0 | 11-5           |

| 12-1.<br>12-2.<br>12-3.      | System Configuration and Protection Logic<br>MPC801 Interrupt Structure<br>Interrupt Table Handling Example                                                  | 12-4           |

| 12-4.                        | RTC Block Diagram                                                                                                                                            | 12-12          |

| 12-5.<br>12-6.               | Periodic Interrupt Timer Block Diagram<br>Software Watchdog Timer Service State Diagram                                                                      |                |

| 12-7.                        | Software Watchdog Timer Block Diagram                                                                                                                        | 12-15          |

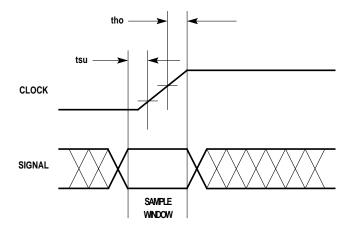

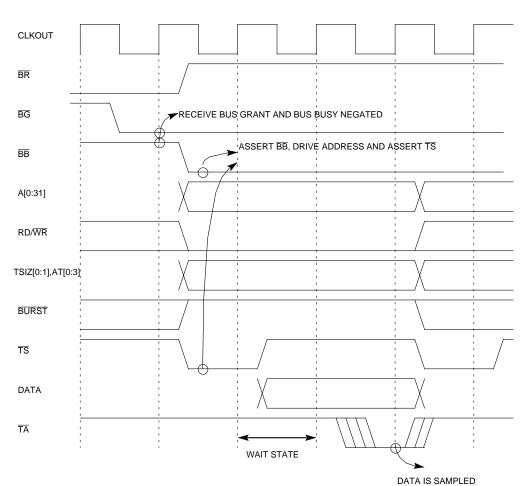

| 13-1.<br>13-2.               | Input Sample Window<br>MPC801 Bus Signals                                                                                                                    |                |

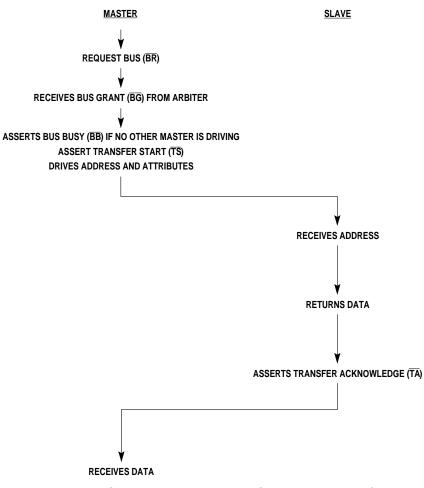

| 13-3.                        | Basic Transfer Protocol                                                                                                                                      | 13-8           |

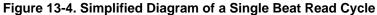

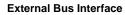

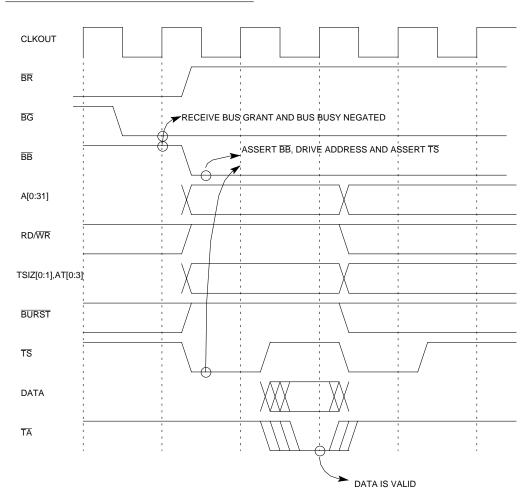

| 13-4.<br>13-5.               | Simplified Diagram of a Single Beat Read Cycle                                                                                                               |                |

| 13-5.                        | Single Beat Read Cycle–Basic Timing–Zero Wait States<br>Single Beat Read Cycle–Basic Timing–One Wait State                                                   |                |

| 13-7.                        | Simplified Flow Diagram of a Single Beat Write Cycle                                                                                                         | 13-12          |

| 13-8.<br>13-9.               | Single Beat Write Cycle Basic Timing One Wait States                                                                                                         |                |

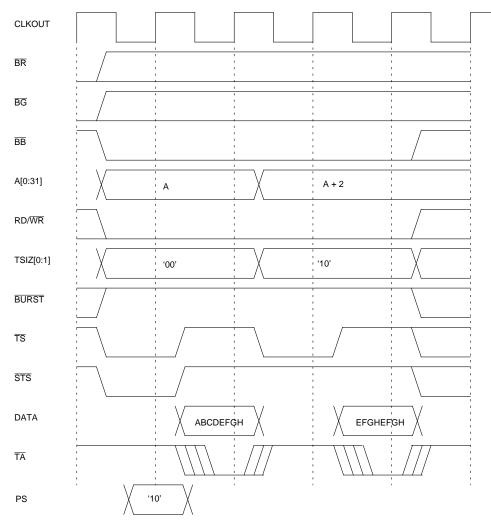

| 13-9.<br>13-10.              | Single Beat Write Cycle–Basic Timing–One Wait State<br>Single Beat–32-Bit Data–Write Cycle–16-Bit Port Size Basic                                            |                |

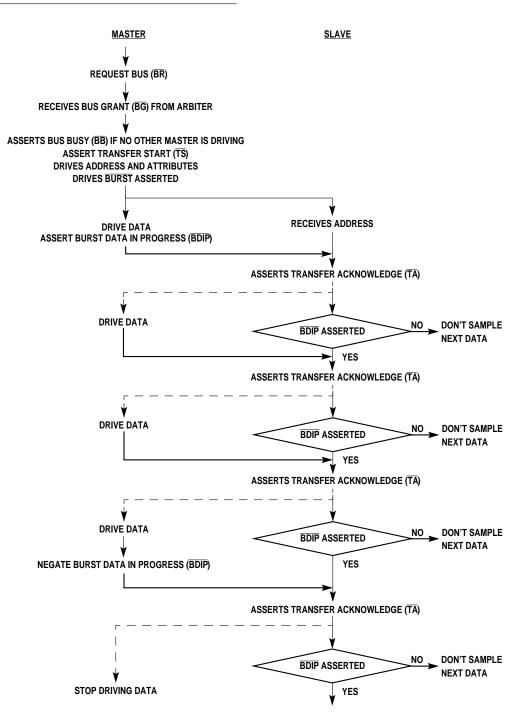

| 13-11.                       | Timing<br>Simplified Flow Diagram Of A Burst Read Cycle                                                                                                      | 13-17          |

| Figure<br>Number | Title                                                                                                                                 | Page<br>Number |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|

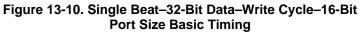

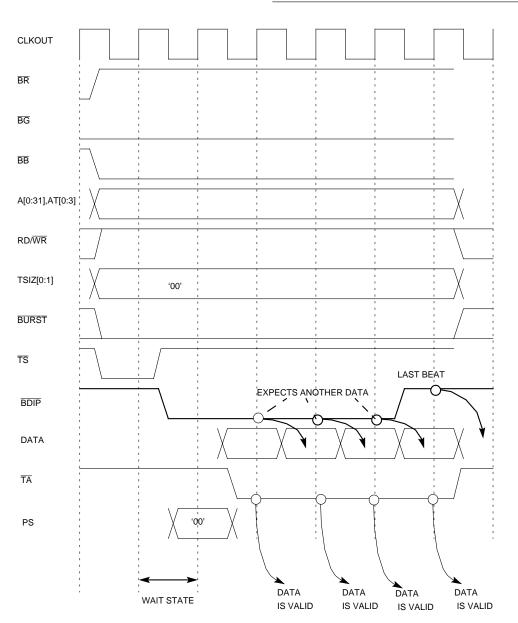

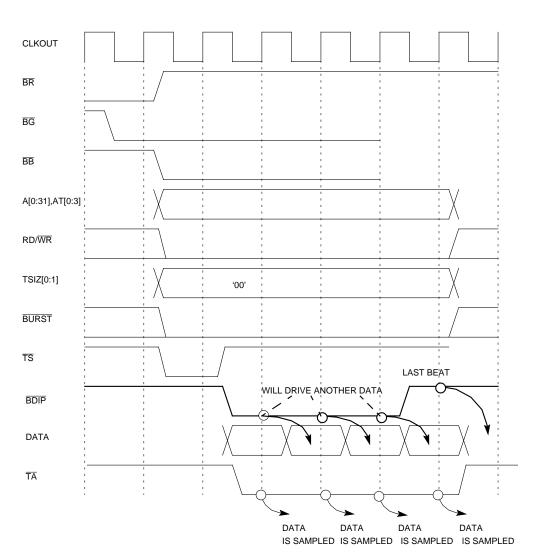

| 13-12.           | Burst-Read Cycle-32-Bit Port Size-Zero Wait State                                                                                     | . 13-18        |

| 13-13.           | Burst-Read Cycle-32-Bit Port Size-One Wait State                                                                                      | 13-19          |

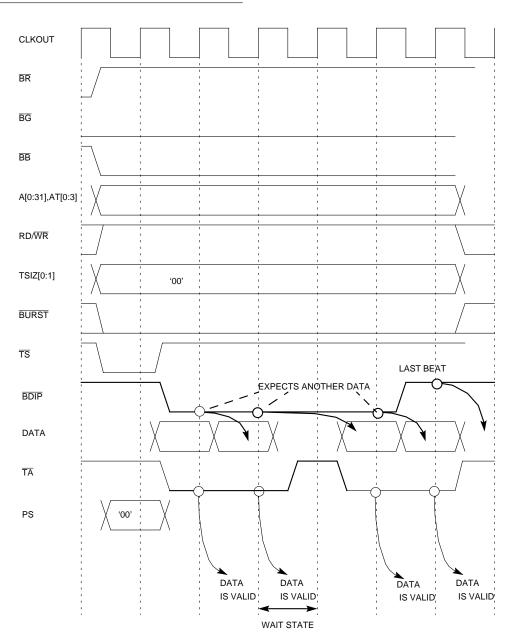

| 13-14.           | Burst-Read Cycle-32-Bit Port Size-Wait States Between Beats                                                                           | . 13-20        |

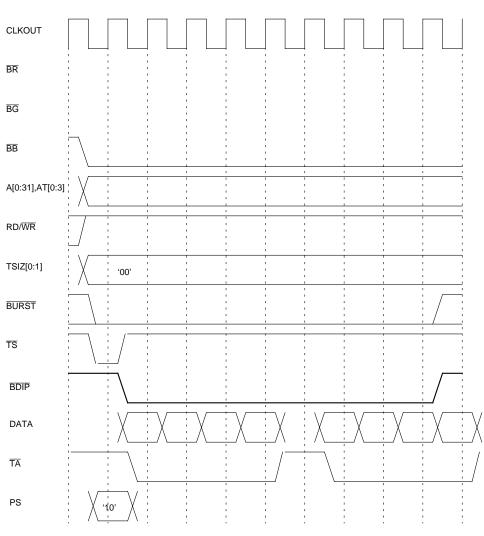

| 13-15.           | Burst-Read Cycle–16-Bit Port Size–One Wait State Between<br>Beats                                                                     | 13-21          |

| 13-16.           | Simplified Flow Diagram of a Burst Write Cycle                                                                                        | . 13-22        |

| 13-17.           | Burst Write Cycle-32-Bit Port Size-Zero Wait States                                                                                   |                |

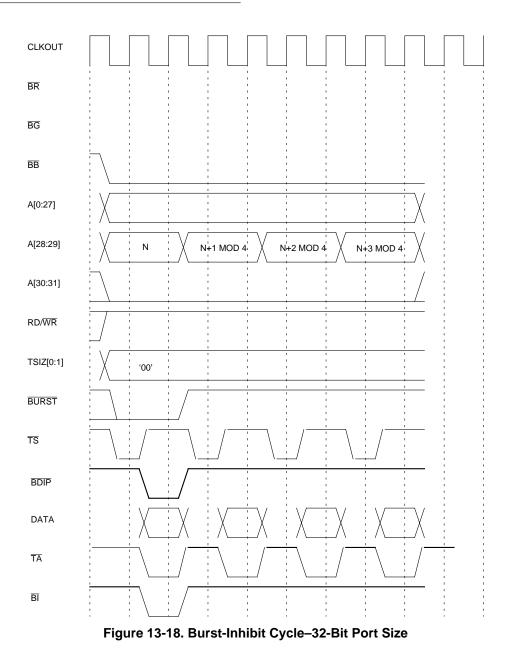

| 13-18.           | Burst-Inhibit Cycle-32-Bit Port Size                                                                                                  |                |

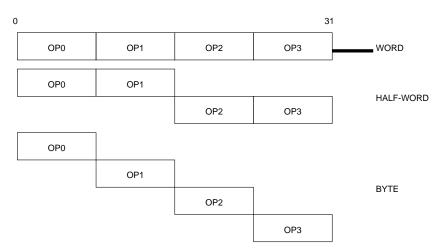

| 13-19.           | Internal Operand Representation                                                                                                       | 13-25          |

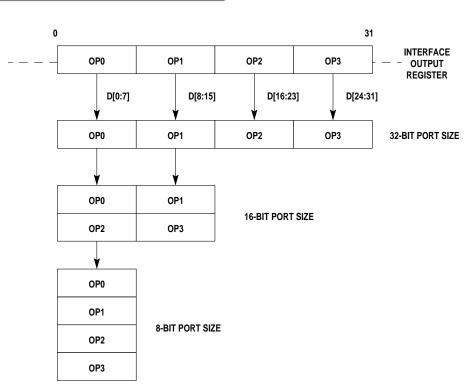

| 13-20.           | Interface To Different Port Size Devices                                                                                              |                |

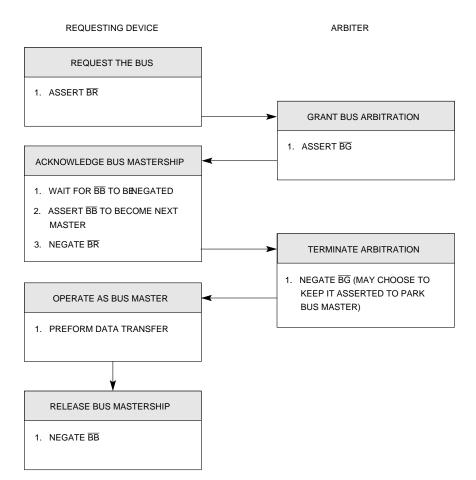

| 13-21.           | Bus Arbitration Flowchart                                                                                                             | 13-28          |

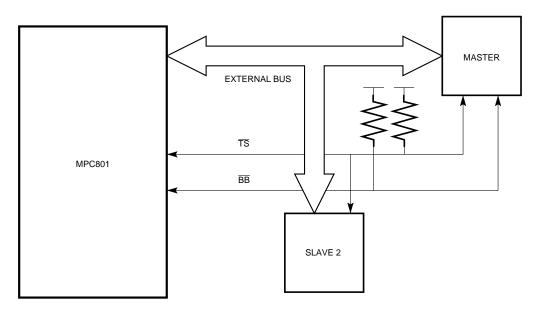

| 13-22.           | Basic Connection of the Master Signal                                                                                                 | . 13-29        |

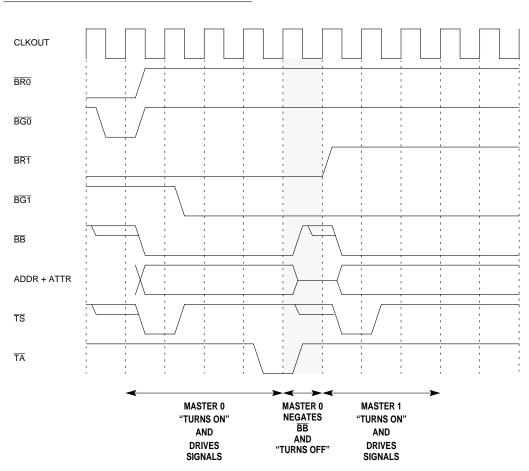

| 13-23.           | Bus Arbitration Timing Diagram                                                                                                        |                |

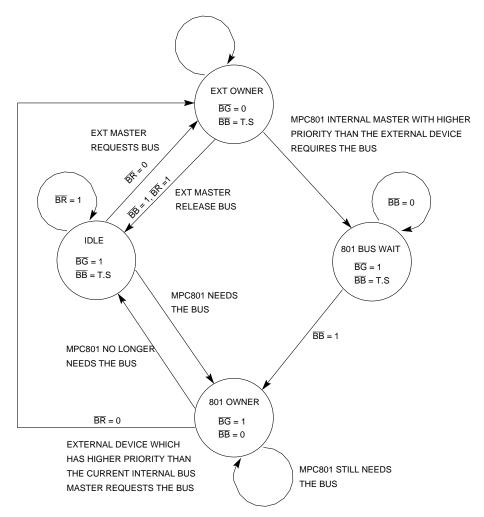

| 13-24.           | Internal Bus Arbitration State Machine                                                                                                | . 13-31        |

| 13-25.           | Termination Signals Protocol Basic Connection                                                                                         | . 13-36        |

| 13-26.           | Termination Signals Protocol Timing Diagram                                                                                           | 13-37          |

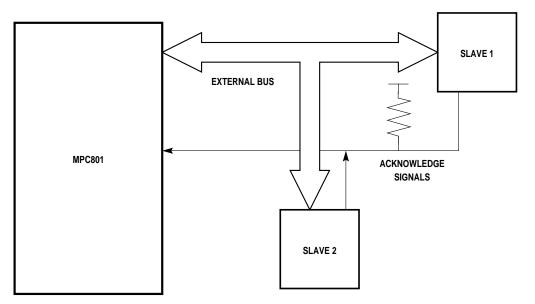

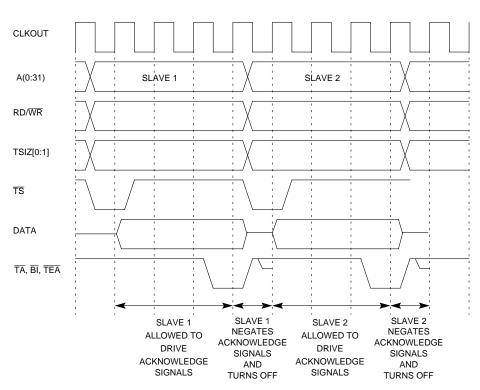

| 13-27.           | Reservation On A Local Bus                                                                                                            |                |

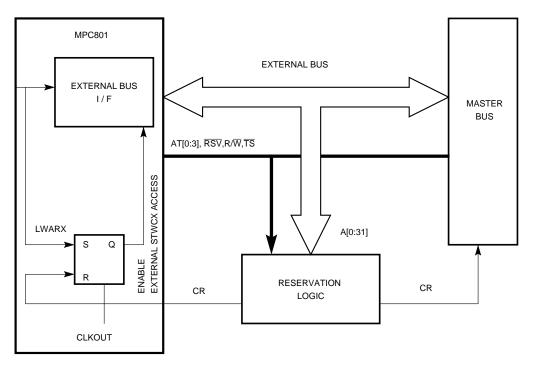

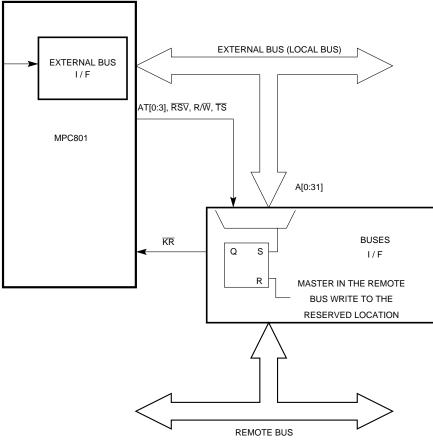

| 13-28.           | Reservation On Multilevel Bus Hierarchy                                                                                               | . 13-39        |

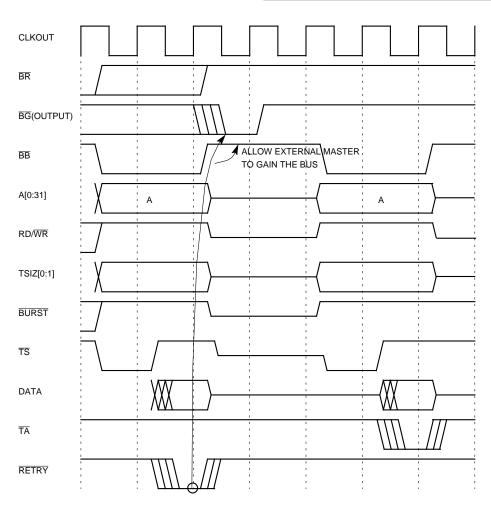

| 13-29.           | Retry Transfer Timing–Internal Arbiter                                                                                                | 13-41          |

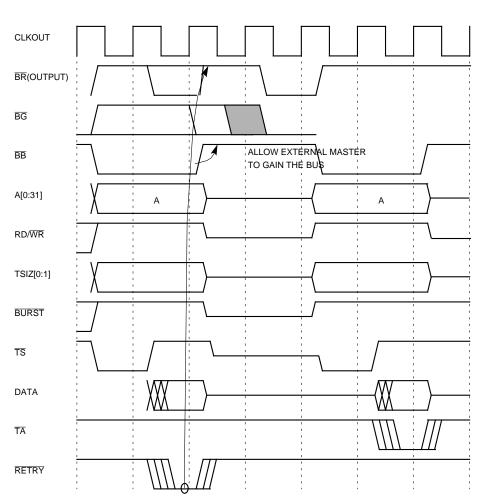

| 13-30.           | Retry Transfer Timing–External Arbiter                                                                                                | . 13-42        |

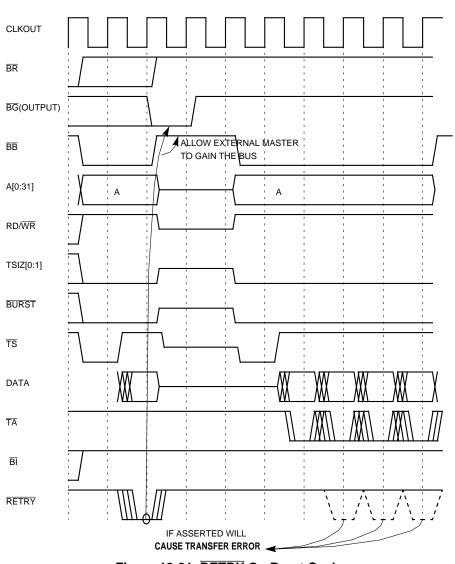

| 13-31.           | Retry On Burst Cycle                                                                                                                  |                |

| 14-1.            | General MPC801 System Diagram                                                                                                         | 14-2           |

| 15-1.            | Memory Controller Block Diagram                                                                                                       |                |

| 15-2.            | MPC801 Simple System Configuration                                                                                                    |                |

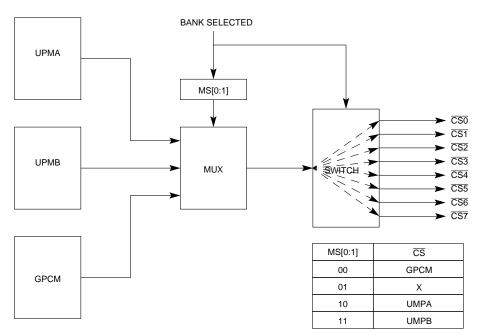

| 15-3.            | Memory Controller Machine Selection                                                                                                   |                |

| 15-4.            | Memory Controller Basic Operation                                                                                                     |                |

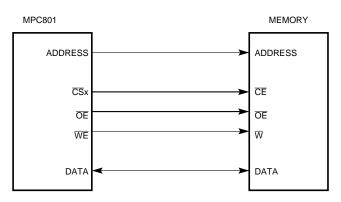

| 15-5.            | MPC801 GPCM–Memory Devices Interface                                                                                                  | 15-8           |

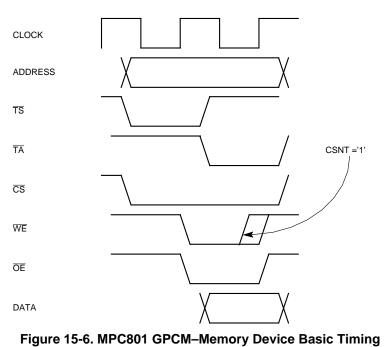

| 15-6.            | MPC801 GPCM–Memory Device Basic Timing                                                                                                | <i>i</i> = .   |

|                  | (ACS = 00, TRLX = 0)                                                                                                                  |                |

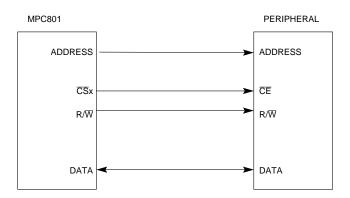

| 15-7.            | MPC801 GPCM–Peripheral Device Interface                                                                                               | 15-9           |

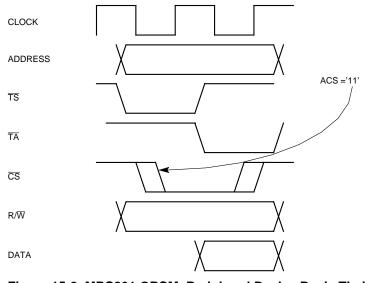

| 15-8.            | MPC801 GPCM–Peripheral Device Basic Timing<br>(ACS = 10, ACS = 11,TRLX = 0)                                                           | 15-10          |

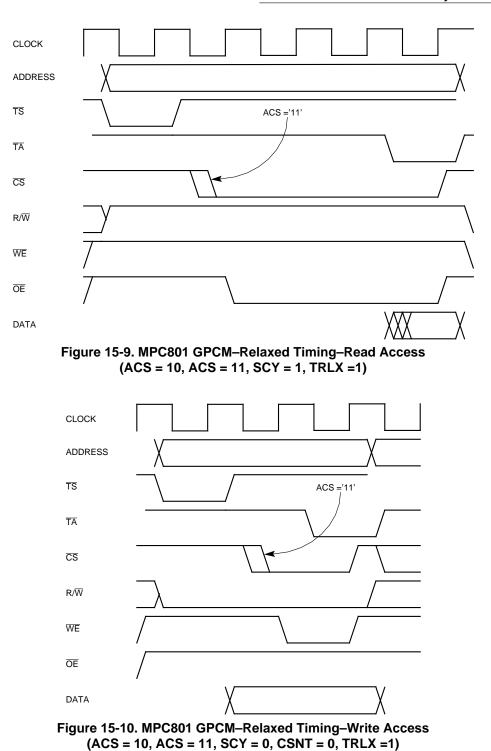

| 15-9.            | MPC801 GPCM–Relaxed Timing–Read Access                                                                                                |                |

| 15-10.           | (ACS = 10, ACS = 11, SCY = 1, TRLX =1)<br>MPC801 GPCM–Relaxed Timing–Write Access<br>(ACS = 10, ACS = 11, SCY = 0, CSNT = 0, TRLX =1) |                |

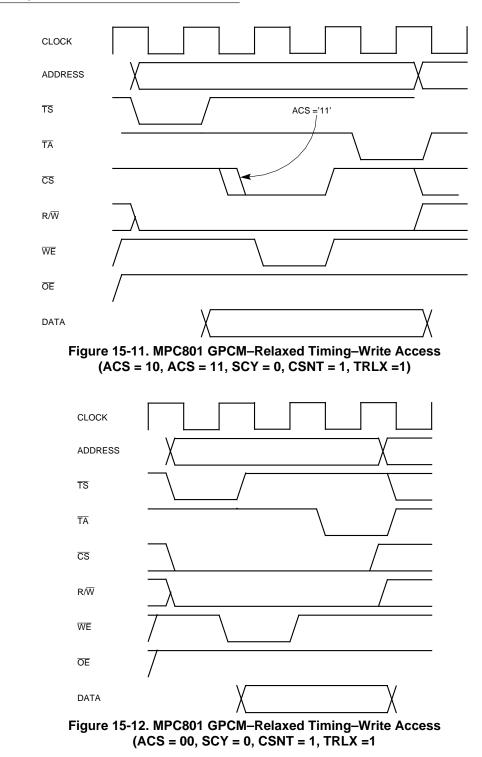

| 15-11.           | MPC801 GPCM–Relaxed Timing–Write Access<br>(ACS = 10, ACS = 11, SCY = 0, CSNT = 1, TRLX =1)                                           |                |

| Figure<br>Number | Title                                                                            | Page<br>Number |

|------------------|----------------------------------------------------------------------------------|----------------|

| 15-12.           | MPC801 GPCM–Relaxed Timing–Write Access                                          |                |

|                  | (ACS = 00, SCY = 0, CSNT = 1, TRLX =1                                            | 15-12          |

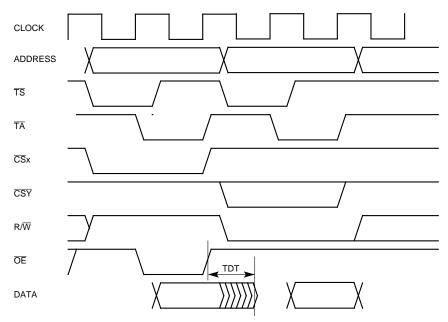

| 15-13.           | MPC801 Consecutive Accesses Write                                                |                |

|                  | After Read–(ORx-EHTR = 0)                                                        | 15-13          |

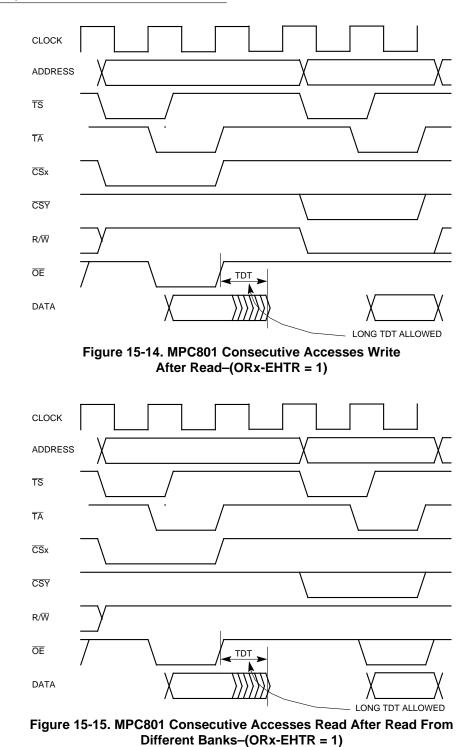

| 15-14.           | MPC801 Consecutive Accesses Write                                                | 45 44          |

| 15-15.           | After Read–(ORx-EHTR = 1)<br>MPC801 Consecutive Accesses Read After Read From    | 15-14          |

| 15-15.           | Different Banks–(ORx-EHTR = 1)                                                   | 15-14          |

| 15-16.           | MPC801 Consecutive Accesses Read After Read From                                 |                |

|                  | Same Bank– (ORx-EHTR = 1)                                                        | 15-15          |

| 15-17.           | MPC801–Simple 128K SRAM Configuration                                            |                |

| 15-18.           | MPC801–Asynchronous External Master Configuration For                            |                |

|                  | GPCM–Handled Memory Devices                                                      | 15-17          |

| 15-19.           | Asynchronous Master GPCM–Memory Devices                                          |                |

|                  | Basic Timing (TRLX = 0)                                                          |                |

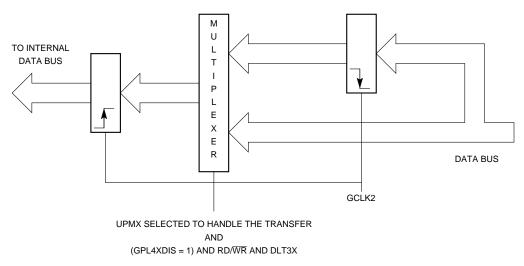

| 15-20.           | General Description of a UPM                                                     |                |

| 15-21.           | Memory Periodic Timer Request Block Diagram                                      | 15-20          |

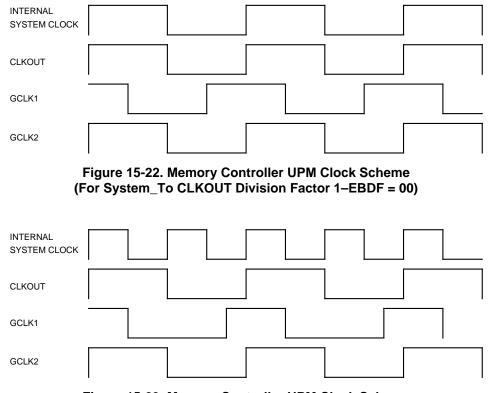

| 15-22.           | Memory Controller UPM Clock Scheme                                               |                |

| 4 = 00           | (For System_To CLKOUT Division Factor 1–EBDF = 00)                               | 15-21          |

| 15-23.           | Memory Controller UPM Clock Scheme                                               | 45.04          |

| 45.04            | (For System_To CLKOUT Division Factor 2–EBDF = 01)                               | 15-21          |

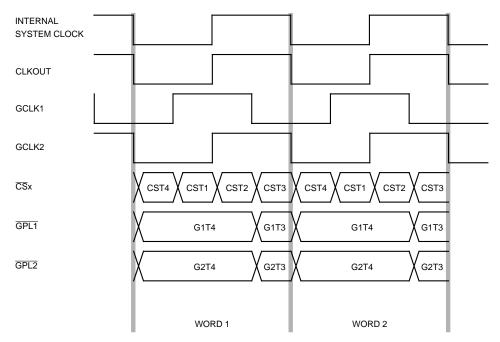

| 15-24.           | UPM Signals Timing Example<br>(For System_To CLKOUT Division Factor 1–EBDF = 00) | 15 00          |

| 15-25.           | UPM Signals Timing Example                                                       | 15-22          |

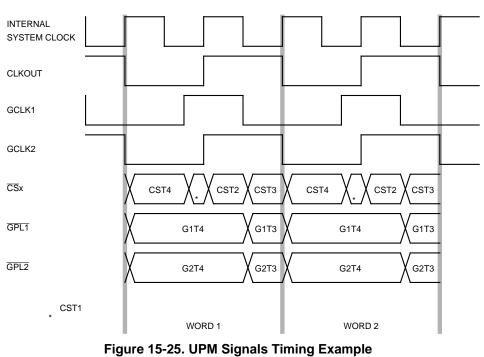

| 15-25.           | (For System_To CLKOUT Division Factor 2–EBDF = 01)                               | 15-23          |

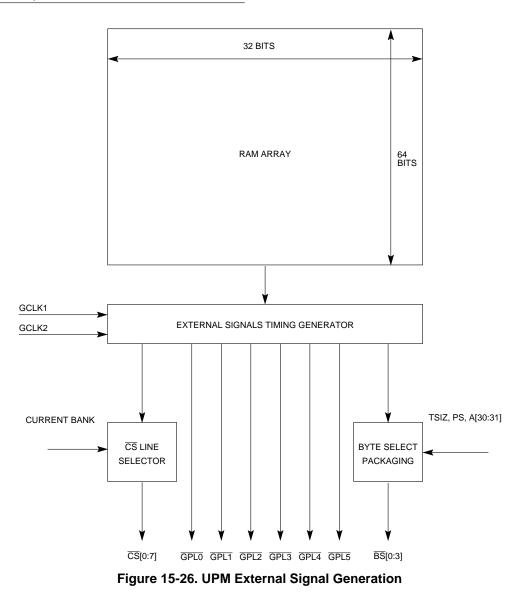

| 15-26.           | UPM External Signal Generation                                                   |                |

| 15-27.           | RAM Word Structure                                                               |                |

| 15-28.           | CS Signal Control Model                                                          |                |

| 15-29.           | Byte Select Control Model                                                        |                |

| 15-30.           | UPM Data Handling In Read Accesses                                               |                |

| 15-31.           | UPM Wait Mechanism Timing For Internal and External                              |                |

|                  | Synchronous Masters 1                                                            | 5-38           |

| 15-32.           | UPM Wait Mechanism Timing For An External Asynchronous                           |                |

|                  | Master                                                                           |                |

| 15-33.           | MPC801–DRAM Interface Connection                                                 |                |

| 15-34.           | Address Start Pointers of the UPM RAM Array                                      |                |

| 15-35.           | Single Beat Read Access To Page Mode DRAM                                        |                |

| 15-36.           | Single Beat Write Access To Page Mode DRAM                                       |                |

| 15-37.           | Burst Read Access To Page Mode DRAM (No LOOP)                                    |                |

| 15-38.           | Burst Read Access To Page Mode DRAM (LOOP)                                       | 15-46          |

| Figure<br>Number | Title                                                                         | Page<br>Number |

|------------------|-------------------------------------------------------------------------------|----------------|

| 15-39.           | Burst Write Access To Page Mode DRAM (No LOOP)                                | 15-47          |

| 15-40.           | Refresh Cycle (CBR) To Page Mode DRAM                                         | 15-48          |

| 15-41.           | Exception Cycle                                                               | 15-49          |

| 15-42.           | Page Mode DRAM Burst Read Access<br>(Data Sampling on Falling Edge of CLKOUT) | 15-51          |

| 15-43.           | EDO Interface Connection                                                      |                |

| 15-44.           | Single Beat Read Access To Page Mode DRAM With Extended<br>Data-Out           |                |

| 15-45.           | Single Beat Write Access To Page Mode DRAM With Extended Data-Out             |                |

| 15-46.           | Burst Read Access To Page Mode DRAM With Extended<br>Data-Out                 |                |

| 15-47.           | Burst Write Access To Page Mode DRAM With Extended                            | 15-55          |

| 13-47.           | Data-Out                                                                      | 15-56          |

| 15-48.           | Refresh Cycle (CBR) To Page Mode DRAM With Extended                           |                |

|                  | Data-Out                                                                      | 15-57          |

| 15-49.           | Exception Cycle For Page Mode DRAM With Extended Data-Out                     | 15-58          |

| 15-50.           | Synchronous External Master Basic Access (GPCM Controlled)                    | 15-62          |

| 15-51.           | Asynchronous External Master Basic Access (GPCM Controlled) .                 | 15-63          |

| 15-52.           | Synchronous External Master–MPC801–DRAM Device                                |                |

| 45.50            | Typical Configuration                                                         | 15-64          |

| 15-53.           | Synchronous External Master–Burst Read Access To Page<br>Mode DRAM            | 15-65          |

| 15-54.           | Asynchronous External Master–MPC801–DRAM Device                               | 10 00          |

|                  | Typical Configuration                                                         | 15-66          |

| 15-55.           | Asynchronous External Master–Read Access To Page Mode                         | 45.07          |

| 15 56            | DRAM<br>Blank Worksheet for a UPM                                             |                |

| 15-56.           |                                                                               | 10-00          |

| 16-1.            | UART Block Diagram                                                            | 16-1           |

| 16-2.            | SPI Block Diagram                                                             |                |

| 16-2. | SPI Block Diagram                         |  |

|-------|-------------------------------------------|--|

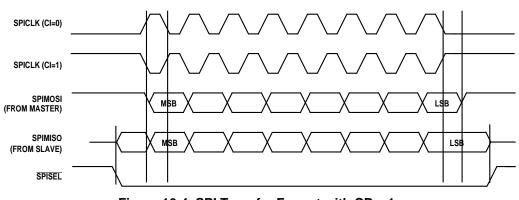

| 16-3. | SPI Transfer Format with CP = 0           |  |

| 16-4. | SPI Transfer Format with CP = 1           |  |

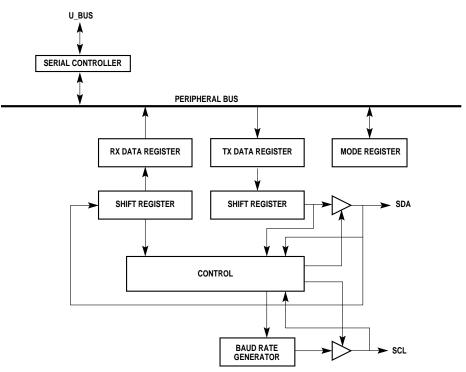

| 16-5. | I <sup>2</sup> C Controller Block Diagram |  |

|       |                                           |  |

| Figure<br>Number                                   | Title                                                                                                                                                                                                        | Page<br>Number               |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

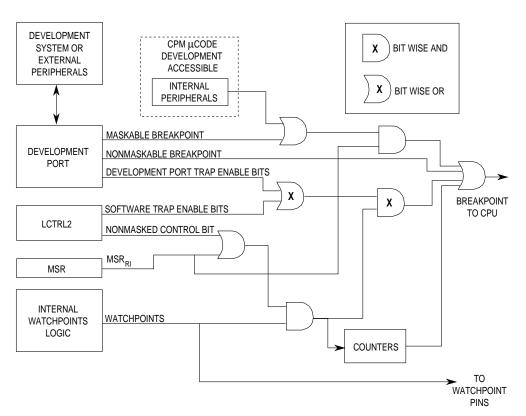

| 18-1.                                              | Watchpoints and Breakpoint Support                                                                                                                                                                           | 18-10                        |

| 18-2.                                              | Partially Supported Watchpoints/Breakpoint Example                                                                                                                                                           |                              |

| 18-3.                                              | Instruction Support General Structure                                                                                                                                                                        |                              |

| 18-4.                                              | Load/Store Support General Structure                                                                                                                                                                         | 18-19                        |

| 18-5.                                              | Relationship Between the Core and Debug Mode                                                                                                                                                                 |                              |

| 18-6.                                              | Debug Mode Logic Implementation                                                                                                                                                                              |                              |

| 18-7.                                              | Debug Mode Reset Configuration Timing Diagram                                                                                                                                                                | 18-25                        |

| 18-8.                                              | Development Port/BDM Connector Pinout Options                                                                                                                                                                |                              |

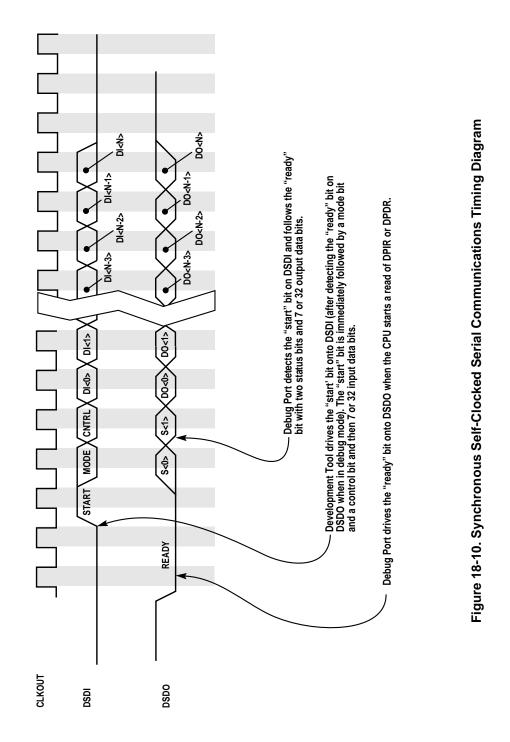

| 18-9.                                              | Asynchronous Clocked Serial Communications Timing Diagram                                                                                                                                                    | . 18-33                      |

| 18-10.                                             | Synchronous Self-Clocked Serial Communications Timing                                                                                                                                                        |                              |

|                                                    | Diagram                                                                                                                                                                                                      |                              |

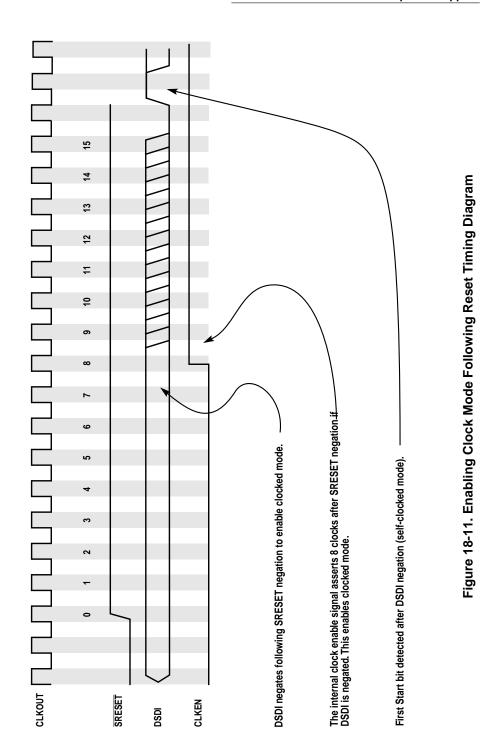

| 18-11.                                             | Enabling Clock Mode Following Reset Timing Diagram                                                                                                                                                           |                              |

| 18-12.                                             | Example of Download Procedure Code                                                                                                                                                                           | 18-39                        |

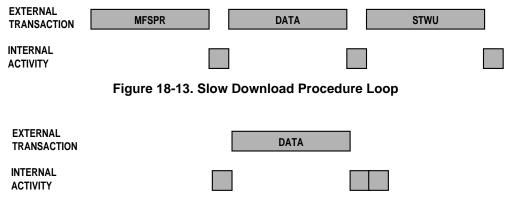

| 18-13.                                             | Slow Download Procedure Loop                                                                                                                                                                                 | 18-40                        |

| 18-14.                                             | Fast Download Procedure Loop                                                                                                                                                                                 | 18-40                        |

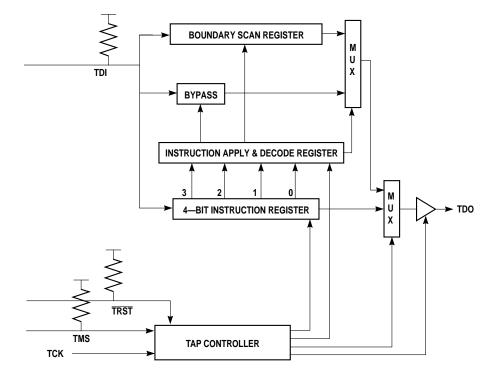

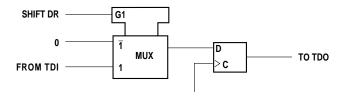

| 19-1.<br>19-2.<br>19-3.<br>19-4.<br>19-5.<br>19-6. | Test Logic Block Diagram<br>TAP Controller State Machine<br>Output Pin Cell (O.Pin)<br>Observe-Only Input Pin Cell (I.Obs)<br>Output Control Cell (IO.CTL)<br>General Arrangement of Bidirectional Pin Cells | 19-3<br>19-4<br>19-4<br>19-5 |

| 19-7.                                              | Bypass Register                                                                                                                                                                                              |                              |

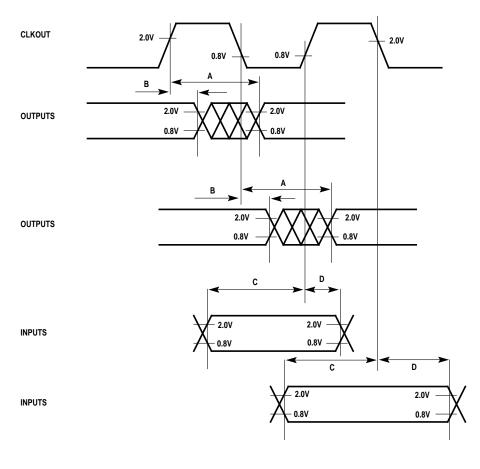

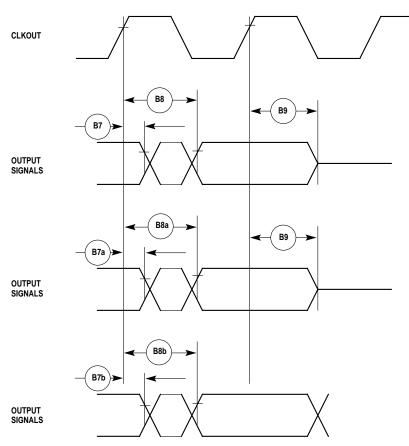

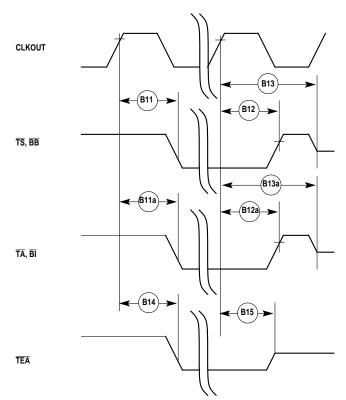

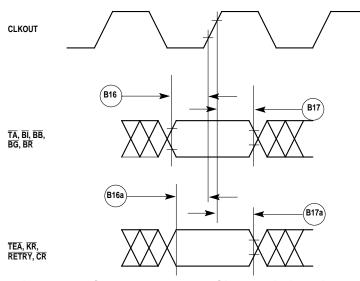

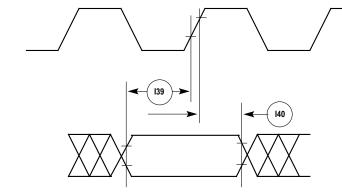

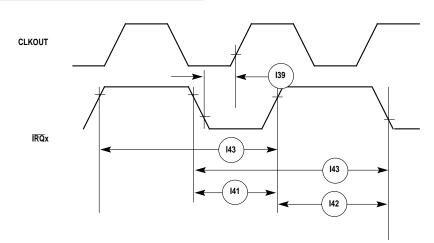

| 20-1.<br>20-2.                                     | External Clock Timing Diagram<br>Synchronous Output Signals Timing Diagram                                                                                                                                   | 20-10                        |

| 20-3.                                              | Synchronous Active Pull-Up And Open-Drain Outputs Signals<br>Timing Diagram                                                                                                                                  | 20-12                        |

| 20-4.                                              | Synchronous Input Signals Timing Diagram                                                                                                                                                                     |                              |

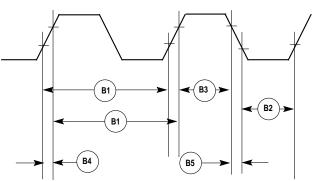

| 20-5.                                              | Input Data In Normal Case Timing Diagram                                                                                                                                                                     |                              |

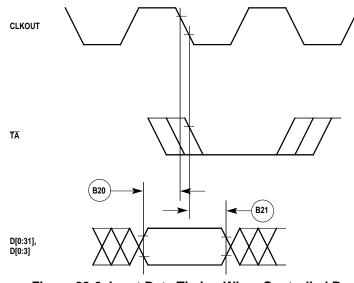

| 20-6.                                              | Input Data Timing When Controlled By The UPM In The                                                                                                                                                          |                              |

|                                                    | Memory Controller                                                                                                                                                                                            | 20-13                        |

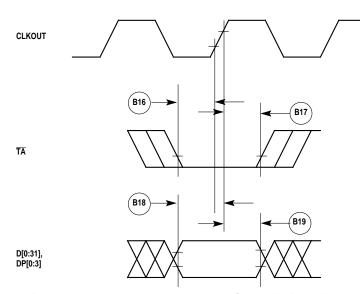

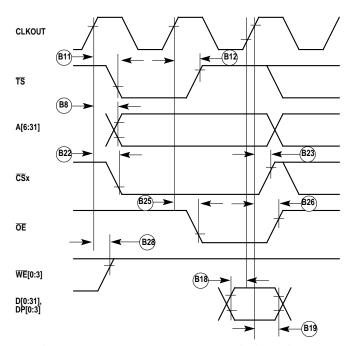

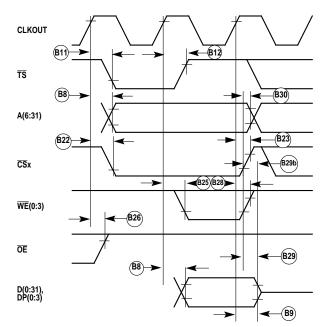

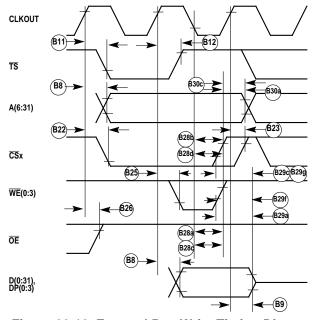

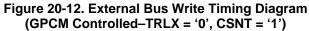

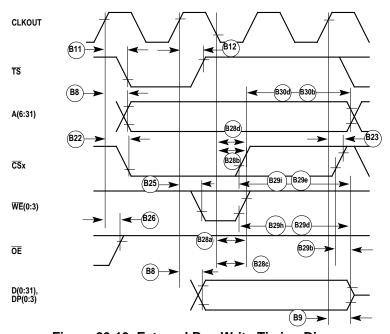

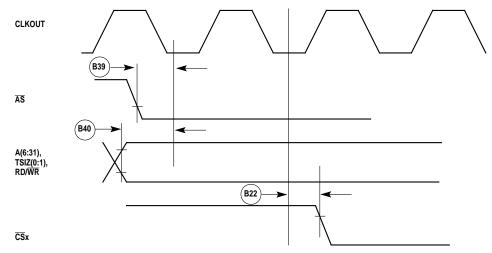

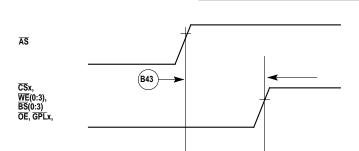

| 20-7.                                              | External Bus Read Timing Diagram<br>(GPCM Controlled–ACS = '00')                                                                                                                                             |                              |

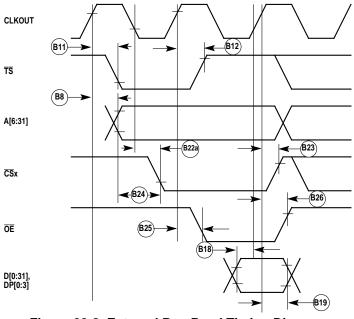

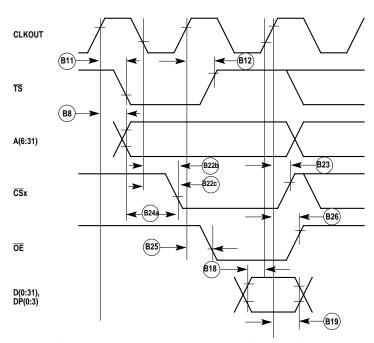

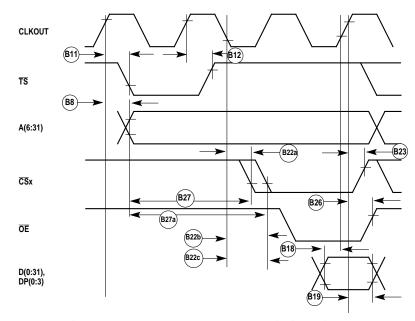

| 20-8.                                              | External Bus Read Timing Diagram                                                                                                                                                                             |                              |

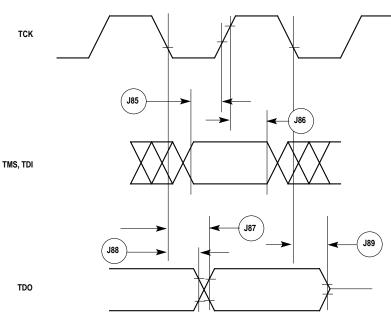

|                                                    | (GPCM Controlled–TRLX = '0' ACS = '10')                                                                                                                                                                      | 20-14                        |