# **Adjustable Dual Output Switching Power Supply**

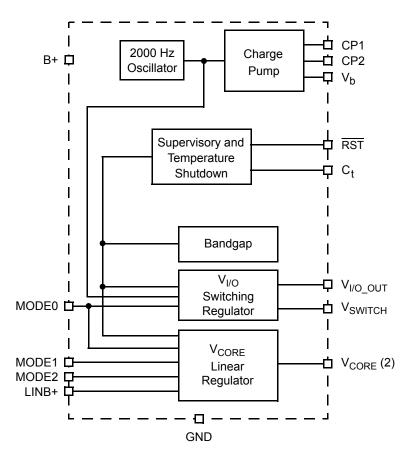

The 34710 is a dual-output power regulator IC that integrates a switching regulator, a linear regulator, supervisor circuitry, and a power supply sequencer. With a wide operating input voltage range of 12 V to 32 V and robust temperature limits, the 34710 is applicable in many commercial and industrial applications that use an MCU.

A user-selectable 5.0 V/3.3 V buck switching regulator is provided for board-level I/Os and user circuitry. The regulator is capable of delivering up to 1.0 A. The MCU core voltage is an adjustable 3.3 V/2.5 V/1.8 V/1.5 V linear voltage regulator that can supply up to 500 mA.

The switching and linear regulator output voltage are determined through three digital input mode terminals that can be controlled by an MCU.

- High-Current Adjustable 5.0 V/3.3 V Switching Regulator

- Low Noise User-Selectable 3.3 V/2.5 V/1.8 V/1.5 V Linear Regulator

- · On-Chip Thermal Shutdown and Error Reset Circuitry

- Supervisory Functions (Power-ON Reset and Error Reset Circuitry)

- Sequenced I/O and Core Voltages

- Pb-Free Packaging Designated by Suffix Code EW

### 34710

### ADJUSTABLE DUAL OUTPUT SWITCHING POWER SUPPLY

### **ORDERING INFORMATION**

| Device       | Temperature<br>Range (T <sub>A</sub> ) | Package     |

|--------------|----------------------------------------|-------------|

| PC34710EW/R2 | 0°C to 85°C                            | 32 SOICW-EP |

## 34710 Simplified Application Diagram 12 V to 32 V 34710 $V_{I/O}$ V<sub>SWITCH</sub> V<sub>I/O\_OUT</sub> MCU Mode0 Mode1 Mode2 LINB+ RST $V_{CORE}$ **V**CORE **GND**

Figure 1. 34710 Simplified Internal Block Diagram

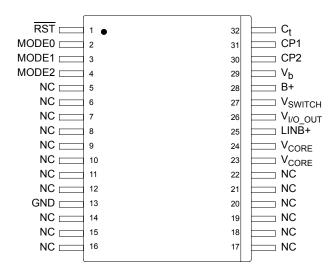

### **TERMINAL FUNCTION DESCRIPTION**

| TERMINAL FUNCTION DESCRIPTION |                         |                                                       |                                                                                            |  |  |  |

|-------------------------------|-------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Terminal                      | Terminal<br>Name        | Formal Name                                           | Definition                                                                                 |  |  |  |

| 1                             | RST                     | Reset                                                 | Reset input and output. This terminal is open drain.                                       |  |  |  |

| 2<br>3<br>4                   | MODE0<br>MODE1<br>MODE2 | Mode Control                                          | These input terminals control $V_{\text{I/O\_OUT}}$ and $V_{\text{CORE}}$ output voltages. |  |  |  |

| 5–12,<br>14–22                | NC                      | No Connects                                           | No internal connection to this terminal.                                                   |  |  |  |

| 13                            | GND                     | Ground                                                | Ground.                                                                                    |  |  |  |

| 23, 24                        | V <sub>CORE</sub>       | Core Voltage Regulator<br>Output                      | Core regulator output voltage.                                                             |  |  |  |

| 25                            | LINB+                   | Core Voltage Regulator<br>Input                       | Core regulator input voltage.                                                              |  |  |  |

| 26                            | V <sub>I/O_OUT</sub>    | V <sub>I/O</sub> Switching Regulator<br>Feedback      | Feedback terminal for $V_{\text{I/O}}$ switching regulator and internal logic supply.      |  |  |  |

| 27                            | V <sub>SWITCH</sub>     | V <sub>I/O</sub> Switching Regulator<br>Switch Output | V <sub>I/O</sub> switching regulator switching output.                                     |  |  |  |

| 28                            | B+                      | Power Supply Input                                    | Regulator input voltage.                                                                   |  |  |  |

| 29                            | V <sub>b</sub>          | Boost Voltage                                         | Boost voltage storage node.                                                                |  |  |  |

| 30                            | CP2                     | Switching Capacitor 2                                 | Charge pump capacitor connection 2.                                                        |  |  |  |

| 31                            | CP1                     | Switching Capacitor 1                                 | Charge pump capacitor connection 1.                                                        |  |  |  |

| 32                            | C <sub>t</sub>          | Reset Delay Capacitor                                 | Reset delay adjustment capacitor.                                                          |  |  |  |

#### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                              | Symbol                     | Max        | Unit |

|---------------------------------------------------------------------|----------------------------|------------|------|

| GLOBAL ABSOLUTE MAXIMUM RATINGS                                     |                            |            |      |

| Input Power Supply Voltage                                          | V <sub>B+</sub>            |            | V    |

| I <sub>B+</sub> = 0 A                                               |                            | -0.3 to 36 |      |

| Terminal Soldering Temperature (Note 1)                             | T <sub>SOLDER</sub>        | 260        | °C   |

| Power Dissipation (Note 2)                                          | P <sub>D</sub>             | 3.0        | W    |

| ESD Standoff Voltage                                                |                            |            | V    |

| Non-Operating, Unbiased, Human Body Model (Note 3)                  | V <sub>ESD1</sub>          | ±2000      |      |

| Thermal Resistance                                                  |                            |            | °C/W |

| Junction-to-Ambient (Note 4)                                        | $R_{	heta JA}$             | 45         |      |

| Junction-to-Ambient (Note 2)                                        | $R_{	hetaJA}$              | 25         |      |

| Junction-to-Case                                                    | $R_{	heta JC}$             | 2.0        |      |

| GLOBAL OPERATING RATINGS                                            |                            |            | •    |

| Operating Ambient Temperature                                       | T <sub>A</sub>             | 0 to 85    | °C   |

| Operating Device Junction Temperature                               | T <sub>J</sub>             | 105        | °C   |

| Input Power Supply Voltage                                          | V <sub>B+</sub>            |            | V    |

| I <sub>B+</sub> = 0 A to 3.0 A                                      |                            | 12 to 32   |      |

| Quiescent Bias Current from B+ (Note 5)                             | I <sub>B+</sub> (q)        |            | mA   |

| V <sub>B+</sub> = 12 V to 32 V                                      |                            | 7.5        |      |

| Operating Junction Temperature                                      | TJ                         | -0 to 105  | °C   |

| V <sub>I/O</sub> SWITCHING REGULATOR (Note 6)                       |                            |            | ·    |

| Maximum Output Voltage Startup Overshoot ( $C_{OUT}$ = 330 $\mu$ F) | V <sub>I/O</sub> (STARTUP) |            | V    |

| MODE0 = 0                                                           |                            | 5.4        |      |

| MODE0 = Open                                                        |                            | 3.6        |      |

| Maximum Output Current                                              | I <sub>VI/O</sub>          |            | А    |

#### Notes

- 1. Soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 2. With 2.0 in<sup>2</sup> of copper headsink.

$T_A = 0$ °C to 105°C

- 3. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

- 4. With no additional heatsinking.

- 5. Maximum quiescent power dissipation is 0.25 W.

- 6.  $12 \text{ V} \leq \text{V}_{B+} \leq 32 \text{ V}$  and  $-20^{\circ}\text{C} \leq \text{T}_{J} \leq 145^{\circ}\text{C}$  unless otherwise noted.

1.2

### **MAXIMUM RATINGS (continued)**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                                                                       | Symbol                      | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|

| V <sub>CORE</sub> LINEAR REGULATOR (Note 7)                                                                                  |                             |      |      |

| Maximum Output Voltage Startup Overshoot (C <sub>OUT</sub> = 10 μF) (Note 8)                                                 | V <sub>CORE</sub> (STARTUP) |      | V    |

| MODE[2:0] = [0,x,0]                                                                                                          |                             | 3.6  |      |

| MODE[2:0] = [0,x,Open]                                                                                                       |                             | 2.7  |      |

| MODE[2:0] = [Open, x, 0]                                                                                                     |                             | 2.0  |      |

| MODE[2:0] = [Open,x,Open]                                                                                                    |                             | 1.65 |      |

| Maximum Output Current                                                                                                       | I <sub>VCORE</sub>          |      | mA   |

| $T_J = 0^{\circ}\text{C to } 105^{\circ}\text{C}, V_{\text{LINB+}} \le V_{\text{CORE}}(\text{NOM}) + 0.8 \text{ V (Note 9)}$ |                             | 500  |      |

#### Notes

- 7. 12 V  $\leq$  V  $_{B+} \leq$  32 V and -20°C  $\leq$  T  $_{J} \leq$  145°C unless otherwise noted.

- 8. Refer to <u>Table 1</u>, page 10.

- 9. Pulse testing with low duty cycle used.

### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 12 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                          | Symbol                       | Min                              | Тур | Max   | Uni |

|-------------------------------------------------------------------------|------------------------------|----------------------------------|-----|-------|-----|

| V <sub>I/O</sub> SWITCHING REGULATOR                                    |                              |                                  |     |       |     |

| Logic Supply Voltage (I <sub>VI/O</sub> = 25 mA to 1.0 A)               | V <sub>I/O</sub>             |                                  |     | _     | V   |

| MODE0 = 0                                                               |                              | 4.8                              | _   | 5.2   |     |

| MODE0 = Open                                                            |                              | 3.15                             | _   | 3.45  |     |

| Logic Supply Current                                                    | I <sub>VI/O</sub>            |                                  |     |       | Α   |

| $V_{I/O}$ = Nominal, Power Dissipation in Switching Regulator = 0.45 W  |                              | 0.025                            | _   | 1.0   |     |

| Output On Resistance                                                    | R <sub>DS(ON)</sub>          |                                  |     |       | Ω   |

| $V_{B+} = 12 \text{ V to } 32 \text{ V}$                                | , ,                          | 0.5                              | TBD | 2.0   |     |

| Soft Start Threshold Voltage                                            | V <sub>I/O</sub> (SOFT)      |                                  |     |       | V   |

| MODE0 = X                                                               |                              | _                                | -   | 2.5   |     |

| Current Limit Threshold (T <sub>J</sub> = 25°C to 100°C)                |                              |                                  |     |       | Α   |

| Normal Operation                                                        | I <sub>LIMIT</sub> (OP)      | 2.1                              | _   | 3.2   |     |

| Soft Start, $V_{I/O} \le 2.5 \text{ V}$                                 | I <sub>LIMIT</sub> (SOFT)    | 1.3                              | -   | 1.8   |     |

| Minimum Voltage Allowable on V <sub>SWITCH</sub> Terminal               | V <sub>VSWITCH</sub> (MIN)   |                                  |     |       | ٧   |

| T <sub>J</sub> = 25°C to 100°C                                          |                              | -0.5                             | -   | -     |     |

| V <sub>CORE</sub> LINEAR REGULATOR                                      |                              |                                  |     |       | ı   |

| Supply Voltage (I <sub>VCORE</sub> = 5.0 mA to 500 mA) (Note 10)        | V <sub>CORE</sub> (NOM)      |                                  |     |       | V   |

| MODE[2:0] = [0, x, 0]                                                   |                              | 3.15                             | _   | 3.45  |     |

| MODE[2:0] = [0,x,Open]                                                  |                              | 2.35                             | _   | 2.65  |     |

| MODE[2:0] = [Open, x, 0]                                                |                              | 1.71                             | _   | 1.89  |     |

| MODE[2:0] = [Open, x, Open]                                             |                              | 1.425                            | _   | 1.575 |     |

| Supply Current                                                          | I <sub>VCORE</sub>           |                                  |     |       | m   |

| $V_{CORE} = V_{CORE}(NOM)$                                              |                              | 1.0                              | -   | 500   |     |

| V <sub>CORE</sub> Dropout Voltage                                       | I <sub>VCORE</sub> (DROPOUT) |                                  |     |       | V   |

| V <sub>CORE</sub> = V <sub>CORE</sub> (NOM), I <sub>VCORE</sub> = 0.5 A |                              | 0.8                              | -   | -     |     |

| Regulator Input Voltage                                                 | V <sub>LINB+</sub>           |                                  |     |       | V   |

| V <sub>CORE</sub> = V <sub>CORE</sub> (NOM), I <sub>VCORE</sub> = 0.5 A |                              | V <sub>CORE</sub> (NOM)<br>+ 1.0 | -   | 10    |     |

| Normal Current Limit Threshold                                          | I <sub>LIMIT</sub>           |                                  |     |       | m   |

| $T_J = 25$ °C to 100°C, $V_{LINB+} = V_{CORE}(NOM) + 1.0 V$             |                              | 800                              | -   | 1000  |     |

#### Notes

10. Refer to Table 1, page 10.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 12 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                                             | Symbol                                   | Min                                      | Тур    | Max                                    | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------|--------|----------------------------------------|------|

| MODE TERMINALS OPERATING VOLTAGES                                                                                                                                                          | •                                        |                                          |        | 1                                      |      |

| MODE Control Terminals Low Voltage  T <sub>J</sub> = 0°C to TBD°C, V <sub>B+</sub> = 12 V to 32 V                                                                                          | V <sub>IL</sub> (MODEn)                  | -                                        | -      | 0.825                                  | V    |

| MODE Control Terminals High Voltage<br>$T_J = 0^{\circ}\text{C to TBD}^{\circ}\text{C}, V_{B+} = 12 \text{ V to } 32 \text{ V}$                                                            | V <sub>IH</sub> (MODEn)                  | 2.6                                      | -      | -                                      | V    |

| MODE Control Terminals Voltage with Input Floating $T_J = 0^{\circ}\text{C}$ to TBD°C, $V_{B+} = 12 \text{ V}$ to 14 V $T_J = 0^{\circ}\text{C}$ to TBD°C, $V_{B+} = 14 \text{ V}$ to 32 V | V <sub>MODE</sub> (FLOAT)                | 7.0<br>8.0                               | -<br>- | 12<br>13.2                             | V    |

| SUPERVISOR CIRCUITRY                                                                                                                                                                       |                                          |                                          |        |                                        |      |

| Minimum Function $V_{B+}$ for Charge Pump and Oscillator Running                                                                                                                           | V <sub>B+</sub> (MIN)                    | 9.0                                      | -      | _                                      | V    |

| Minimum V <sub>B+</sub> for $\overline{\text{RST}}$ Assertion, V <sub>B+</sub> Rising                                                                                                      | V <sub>B+</sub> (ASSERT)                 | 2.0                                      | -      | _                                      | V    |

| $\overline{\text{RST}}$ Low Voltage $V_{\text{B+}}$ = 2.0 V, $I_{\overline{\text{RST}}} \leq 5.0$ mA                                                                                       | V <sub>OL</sub>                          | -                                        | _      | 0.4                                    | V    |

| $\overline{\text{RST}}  V_{I/O}  \text{Threshold}$ $V_{I/O}  \text{Rising}$ $V_{I/O}  \text{Falling}$                                                                                      | V <sub>I/Ot+</sub><br>V <sub>I/Ot-</sub> | –<br>V <sub>I/O</sub> (NOM)<br>- 225 mV  | -      | V <sub>I/O</sub> (NOM)<br>- 80 mV<br>- | ٧    |

| RST Hysteresis for V <sub>I/O</sub>                                                                                                                                                        | V <sub>HYSVI/O</sub>                     | 10                                       | -      | 100                                    | mV   |

| RST V <sub>CORE</sub> Threshold  V <sub>CORE</sub> Rising  V <sub>CORE</sub> Falling                                                                                                       | V <sub>COREt+</sub>                      | -<br>V <sub>CORE</sub> (NOM)<br>- 225 mV | -      | V <sub>CORE</sub> (NOM)<br>- 80 mV     | V    |

| RST Hysteresis for V <sub>CORE</sub> V <sub>B+</sub> = 12 V to 32 V                                                                                                                        | V <sub>HYS</sub> core                    | 10                                       | _      | 100                                    | mV   |

| $V_{CORE}$ - $V_{I/O}$ for $V_{CORE}$ Shutdown<br>$V_{B+}$ = 12 V to 32 V                                                                                                                  | V <sub>CORE</sub> (SHUTDOWN)             | -                                        | -      | TBD                                    | V    |

| Thermal Shutdown Temperature $T_J$ Rising                                                                                                                                                  | T <sub>J</sub> (TSD)                     | 170                                      | _      | -                                      | °C   |

| Overtemperature Hysteresis                                                                                                                                                                 | T <sub>J</sub> (HYSTERESIS)              | 20                                       | -      | TBD                                    | °C   |

| V <sub>b</sub> CHARGE PUMP                                                                                                                                                                 |                                          | <u>'</u>                                 |        | •                                      |      |

| Boost Voltage (Note 11)<br>V <sub>B+</sub> = 12 V to 32 V, I <sub>VD</sub> = 0.5 mA                                                                                                        | V <sub>b</sub>                           | V <sub>B+</sub> +10 V                    | _      | V <sub>B+</sub> +12 V                  | V    |

### Notes

11. Bulk capacitor ESR  $\leq$  10  $\Omega$ .

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions 4.75 V  $\leq$  V $_{IO}$   $\leq$  5.25 V, 12 V  $\leq$  V $_{B+}$   $\leq$  32 V, and 0°C  $\leq$  T $_{J}$   $\leq$  105°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T $_{A}$  = 25°C under nominal conditions unless otherwise noted

| Characteristic                                                                       | Symbol                          | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------|---------------------------------|-----|-----|-----|------|

| V <sub>I/O</sub> SWITCHING REGULATOR                                                 |                                 |     |     |     |      |

| Duty Cycle                                                                           | D                               | 45  | _   | 55  | %    |

| Switching Rise and Fall Time Load Resistance = 100 $\Omega$ , $V_{B+}$ = 30 $V$      | t <sub>r</sub> , t <sub>f</sub> | 25  | _   | _   | ns   |

| Switching Rise and Fall Time Load Resistance = 100 $\Omega$ , V <sub>B+</sub> = 30 V | t <sub>r</sub> + t <sub>f</sub> | _   | _   | 50  | ns   |

### SUPERVISOR CIRCUITRY

| RST Delay C <sub>delay</sub> = 0.1 μF                                                                                         | t <sub>delay</sub>             | 48  | _ | 82  | ms |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----|---|-----|----|

| RST Filter Time $V_{B+} = 9.0 \text{ V}$                                                                                      | t <sub>filter</sub>            | 1.0 | _ | 6.0 | μS |

| $\overline{\text{RST}}$ Fall Time<br>$C_L$ = 100 pF, $R_{PULLUP}$ = 4.7 k $\Omega$ , 90% to 10%                               | t <sub>f</sub>                 | _   | _ | 125 | ns |

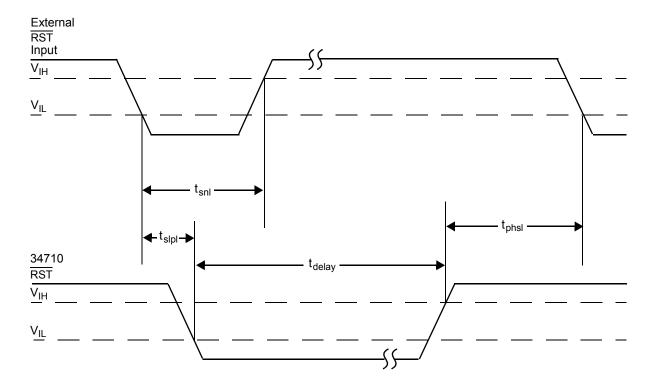

| External Low (Note 12) $V_{I/O} = 5.0 \text{ V}$                                                                              | t <sub>slpl</sub><br>(Note 13) | 30  | - | _   | ns |

| $\overline{\text{RST}}$ Recovery Time Before Next $\overline{\text{RST}}$ Input (Note 12)<br>$V_{\text{I/O}} = 5.0 \text{ V}$ | t <sub>phsl</sub>              | _   | _ | 10  | μS |

### INTERNAL OSCILLATOR

| Charge Pump and V <sub>I/O</sub> Switching Regulator Operating Frequency | f <sub>OP</sub> |     |   |     | kHz |

|--------------------------------------------------------------------------|-----------------|-----|---|-----|-----|

| V <sub>B+</sub> = 9.0 V to 32 V                                          |                 | 140 | - | 260 |     |

#### Notes

- 12. See Figure 2, RST Timing, page 9.

- 13.  $t_{slpl}$  is an input.

### **Timing Diagram**

Figure 2. RST Timing

### SYSTEM/APPLICATION INFORMATION

### INTRODUCTION

### V<sub>I/O</sub> Switching Regulator

The V $_{I/O}$  switching regulator output voltage is determined by the MODE digital input terminals. The 34710's MODE[2:0] select the output voltage (Table 1). For example, if MODE[2:0] = 0, 0, 0, then V $_{I/O}$  = 5.0 V; if MODE[2:0] = Open, Open, Open, then V $_{I/O}$  = 3.3 V. The MODE0 terminal controls the output voltage of both regulators.

The topology of the regulator is a bang-bang buck regulator operating from the internal ~200 kHz oscillator.

### V<sub>CORE</sub> Linear Regulator

The V<sub>CORE</sub> linear regulator can produce a +3.3 V, 2.5 V, 1.8 V, or 1.5 V output voltage at 500 mA. The input to the V<sub>CORE</sub> regulator is a terminal that may be connected to the V<sub>I/O</sub> regulator output. The minimum input voltage must be V<sub>CORE</sub>(NOM) + 0.8 V.

The MODE[2:0] terminals select the output voltage as depicted in Table 1.

Table 1. V<sub>I/O</sub> and V<sub>CORE</sub>(NOM) Regulator Output Voltage Selection

| MODE2 | MODE1 | MODE0 | V <sub>I/O</sub><br>(V) | V <sub>CORE</sub> (NOM)<br>(V) |

|-------|-------|-------|-------------------------|--------------------------------|

| 0     | 0     | 0     | 5.0                     | 3.3                            |

| 0     | 0     | Open  | 3.3                     | 2.5                            |

| 0     | Open  | 0     | 5.0                     | 1.8                            |

| 0     | Open  | Open  | 3.3                     | 1.8                            |

| Open  | 0     | 0     | 5.0                     | 2.5                            |

| Open  | 0     | Open  | 3.3                     | 2.5                            |

| Open  | Open  | 0     | 5.0                     | 1.5                            |

| Open  | Open  | Open  | 3.3                     | 1.5                            |

Open indicates terminal is not connected externally.

#### SUPERVISORY AND MISCELLANEOUS FUNCTIONS

### Introduction

The supervisor circuitry provides control of the  $\overline{RST}$  line, an open drain signal, based on system operating conditions monitored by the 34710.  $V_{I/O}, V_{CORE}, V_{B+},$  and thermal shutdown (TSD) detectors in various parts of the chip are monitored for error conditions. Because other devices in the system may trigger a reset, the  $\overline{RST}$  line itself is also monitored, but the supervisor circuitry controls all reset timing, including externally generated resets. Driving the  $\overline{RST}$  line low causes the system to be held in the reset state.  $V_{I/O}, V_{CORE}, V_{B+},$  and thermal shutdown have both positive- and negative-going thresholds.

The supervisor circuitry also ensures that the power supplies sequence properly. Specifically, that  $V_{I/O}$  is never less than TBD V below  $V_{CORE}.$  This means that  $V_{CORE}$  -  $V_{I/O}$  will be clamped at 0.5 V, and that the  $V_{CORE}$  regulator operation will be suppressed during startup and shutdown to ensure that  $V_{CORE}$  -  $V_{I/O}$  = TBD V.

### **Static Operating Specifications**

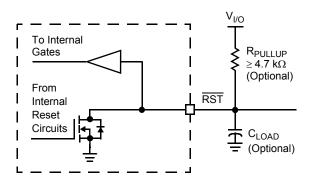

The  $\overline{\text{RST}}$  output is an I/O device with an open drain output driver with a pullup and a CMOS digital input gate (Figure 3). This I/O structure allows wired OR connection to the MCU's  $\overline{\text{RST}}$  I/O terminal, as well as allowing the MCU to initiate a reset cycle by driving its  $\overline{\text{RST}}$  terminal low. When responding to a MCU request for a reset cycle, the 34710 must respond rapidly enough to prevent a glitch. Figure 2, page 9, shows the timing

parameters for responding to an externally applied  $\overline{RST}$  signal. The rise time may be relatively slow, depending on the load capacitance, and the internal  $\overline{RST}$  input gate must operate reliably (no oscillations during the transition) under these conditions, i.e., the  $\overline{RST}$  input can be inhibited for up to  $t_{phsl}(\text{MAX})$ . Error conditions must be present for a minimum time,  $t_{filter}$ , before the 34710 responds to them. Once all error conditions are cleared,  $\overline{RST}$  is held low for an additional time of  $t_{delay}$ . If any monitored item falls below its negative-going threshold for  $t_{filter}$ , 1.0  $\mu s$  to 6.0  $\mu s$ , the  $t_{delay}$  will be restarted when system operating conditions are met. The trigger for the  $t_{delay}$  retriggerable one shot should be ([V\_I/O(LOW) + V\_{CORE}(LOW) + V\_{B+}(LOW) + T\_J(TSD)] &  $t_{filter}$ ), where  $t_{filter}$  is the 1.0  $\mu s$  to 6.0  $\mu s$  delay.

Figure 3. RST Terminal Interface

### V<sub>b</sub> Charge Pump

The high-side MOSFETs in the H-Bridge motor drivers and voltage regulators switch require a gate voltage in excess of  $V_{B+,}$  which is provided by the  $V_b$  supply. The  $V_b$  regulator is a charge pump, switching directly off the  $V_{B+}$  supply, and uses an internal oscillator operating at 200 kHz.

### **Internal Oscillator**

The internal oscillator provides timing for the charge pump and switching regulators.

### **APPLICATIONS**

### **Power Dissipation**

The power budget is described in <u>Table 2</u>. The maximum dissipation for this device is 1.0 W continuous.

Table 2. Power Budget

| Functional Block    | Watt |

|---------------------|------|

| Bias                | 0.00 |

| Charge Pump         | 0.15 |

| Switching Regulator | 0.45 |

| Linear Regulator    | 0.35 |

| Total               | 0.95 |

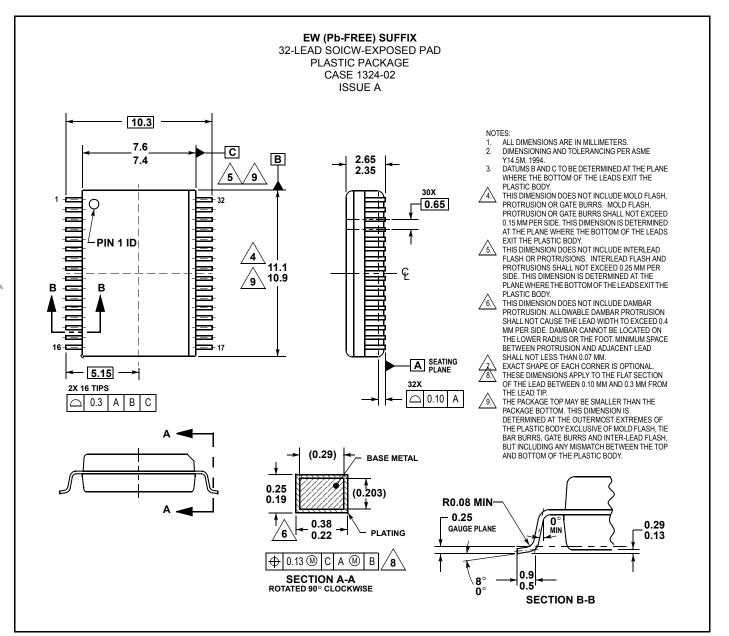

### **PACKAGE DIMENSIONS**

**NOTES**

**NOTES**

**NOTES**

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2004

#### **HOW TO REACH US:**

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

**ASIA/PACIFIC:** Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors