November 1995

## A Fourth Generation of LCD Backlight Technology

Component and Measurement Improvements Refine Performance

Jim Williams

#### **PREFACE**

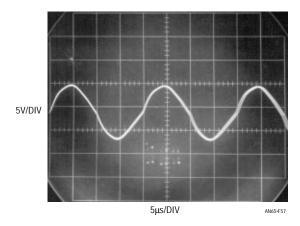

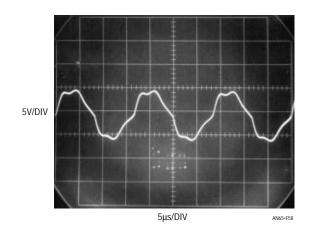

Current generation portable computers and instruments utilize backlit LCDs (Liquid Crystal Displays). These displays have also appeared in applications ranging from medical equipment to automobiles, gas pumps and retail terminals. Cold Cathode Fluorescent Lamps (CCFLs) provide the highest available efficiency for backlighting the display. These lamps require high voltage AC to operate, mandating an efficient high voltage DC/AC converter. In addition to good efficiency, the converter should deliver the lamp drive in sine wave form. This is desirable to minimize RF emissions. Such emissions can cause interference with other devices, as well as degrading overall operating efficiency. The sine wave excitation also provides optimal current-to-light conversion in the lamp. The circuit should permit lamp control from zero to full brightness with no hysteresis or "pop-on," and must also regulate lamp intensity vs power supply variations.

The small size and battery-powered operation associated with LCD equipped apparatus mandate low component count and high efficiency for these circuits. Size constraints place severe limitations on circuit architecture and long battery life is usually a priority. Laptop and handheld portable computers offer an excellent example. The CCFL and its power supply are responsible for almost 50% of the battery drain. Additionally, these components, including

PC board and all hardware, usually must fit within the LCD enclosure with a height restriction of 0.25 inches.

A practical, efficient LCD backlight design is a classic study of compromise in a transduced electronic system. Every aspect of the design is interrelated, and the physical embodiment is an integral part of the electrical circuit. The choice and location of the lamp, wires, display housing and other items have a major effect on electrical characteristics. The greatest care in every detail is required to achieve a practical high efficiency LCD backlight. Getting the lamp to light is just the beginning!

First generation backlights were crude, with poor performance in almost all areas. LTC (Linear Technology Corporation) has introduced feedback stabilization and optimized lamp driving configurations in three successive generations of technology. The effort has culminated in dedicated ICs for backlight driving.

This fourth publication reviews our recent work in components and measurement techniques applicable to LCD backlighting. Theoretical considerations are presented with practical suggestions, remedies and circuits. As always, we welcome reader comments, questions and requests for consultation.

CCFL backlight application circuits contained in this Application Note are covered by U.S. patent number 5408162 and other patents pending.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

### TABLE OF CONTENTS

| INTRODUCTION                                                   |          |

|----------------------------------------------------------------|----------|

| PERSPECTIVES ON DISPLAY EFFICIENCY                             | . AN65-5 |

| Cold Cathode Fluorescent Lamps (CCFLs)                         | . AN65-5 |

| CCFL Load Characteristics                                      | . AN65-7 |

| Display and Layout Losses                                      |          |

| Considerations for Multilamp Designs                           | AN65-31  |

| CCFL Power Supply Circuits                                     | AN65-32  |

| Low Power CCFL Power Supplies                                  | AN65-37  |

| High Power CCFL Power Suppy                                    | AN65-39  |

| "Floating" Lamp Circuits                                       | AN65-40  |

| IC-Based Floating Drive Circuits                               | AN65-43  |

| High Power Floating Lamp Circuit                               | AN65-46  |

| Selection Criteria for CCFL Circuits                           | AN65-46  |

| Summary of Circuits                                            | AN65-49  |

| General Optimization and Measurement Considerations            | AN65-52  |

| Electrical Efficiency Optimization and Measurement             | AN65-53  |

| Electrical Efficiency Measurement                              | AN65-55  |

| Feedback Loop Stability Issues                                 | AN65-55  |

| REFERENCES                                                     | AN65-59  |

| APPENDIX A                                                     | AN65-60  |

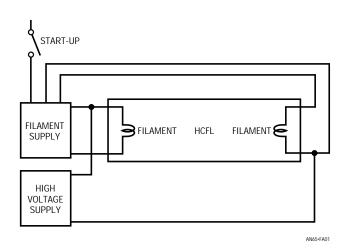

| "HOT" CATHODE FLUORESCENT LAMPS                                | AN65-60  |

| APPENDIX B                                                     |          |

| MECHANICAL DESIGN CONSIDERATIONS FOR LIQUID CRYSTAL DISPLAYS   | AN65-60  |

| Introduction                                                   | AN65-60  |

| Flatness and Rigidity of the Bezel                             | AN65-61  |

| Avoiding Heat Buildup in the Display                           |          |

| Placement of the Display Components                            | AN65-62  |

| Protecting the Face of the Display                             | AN65-62  |

| APPENDIX C                                                     |          |

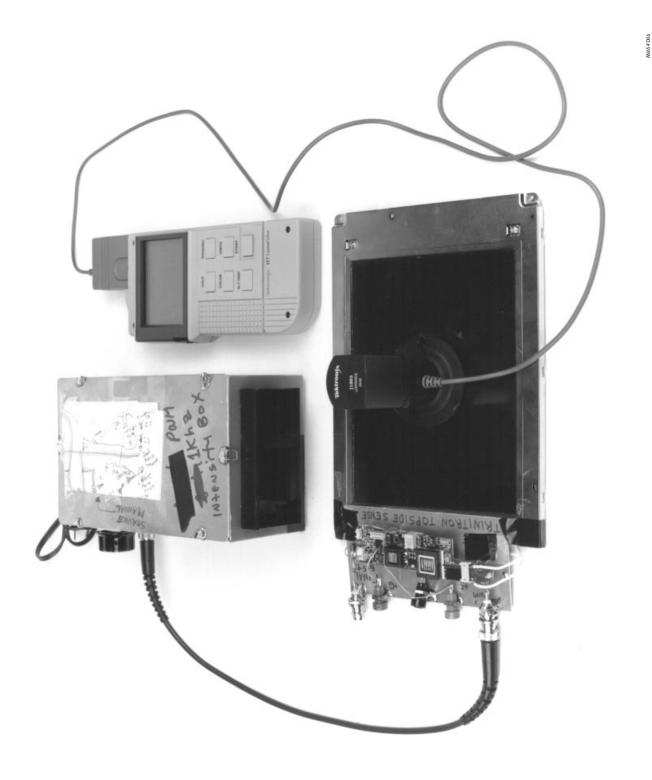

| ACHIEVING MEANINGFUL EFFICIENCY MEASUREMENTS                   | AN65-63  |

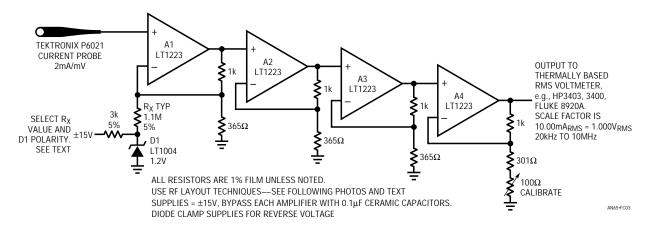

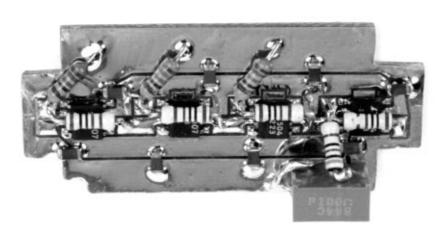

| Current Probe Circuitry                                        | AN65-64  |

| Current Calibrator                                             |          |

| Voltage Probes for Grounded Lamp Circuits                      |          |

| Voltage Probes for Floating Lamp Circuits                      | AN65-72  |

| Differential Probe Calibrator                                  | AN65-76  |

| RMS Voltmeters                                                 |          |

| Calorimetric Correlation of Electrical Efficiency Measurements |          |

| APPENDIX D                                                     | AN65-87  |

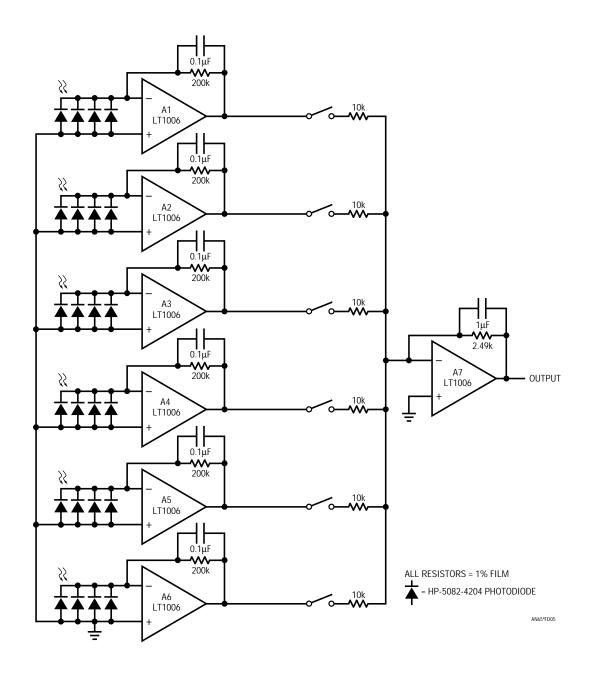

| PHOTOMETRIC MEASUREMENTS                                       | AN65-87  |

| APPENDIX E                                                     | AN65-92   |

|----------------------------------------------------------------|-----------|

| OPEN LAMP/OVERLOAD PROTECTION                                  | AN65-92   |

| Overload Protection                                            | AN65-93   |

| APPENDIX F                                                     |           |

| INTENSITY CONTROL AND SHUTDOWN METHODS                         | AN65-94   |

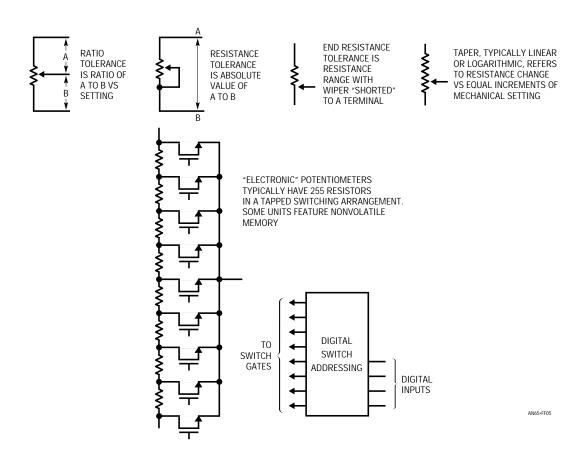

| About Potentiometers                                           | AN65-96   |

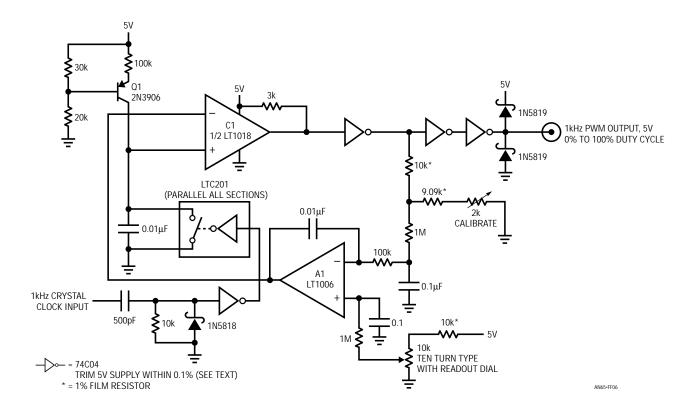

| Precision PWM Generator                                        | . AN65-98 |

| APPENDIX G                                                     | AN65-99   |

| LAYOUT, COMPONENT AND EMISSIONS CONSIDERATIONS                 | AN65-99   |

| Circuit Segmenting                                             | AN65-99   |

| High Voltage Layout                                            | AN65-99   |

| Discrete Component Selection                                   | AN65-106  |

| Basic Operation of Converter                                   |           |

| Requisite Transistor Characteristics                           | AN65-108  |

| Additional Discrete Component Considerations                   | AN65-110  |

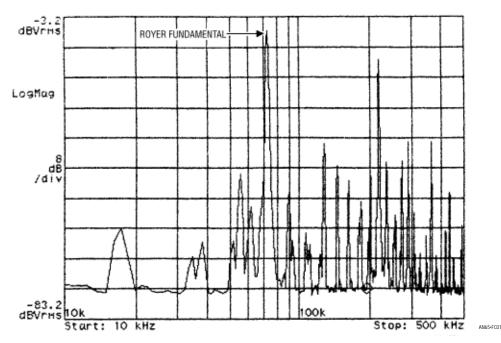

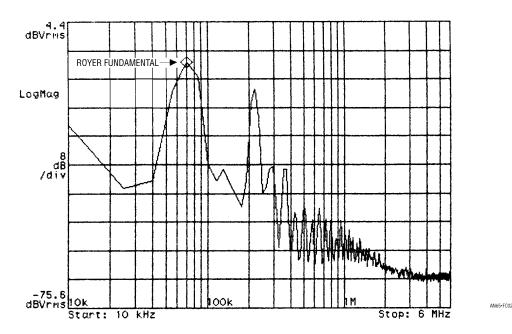

| Emissions                                                      | AN65-110  |

| APPENDIX H                                                     |           |

| LT®1172 OPERATION FROM HIGH VOLTAGE INPUTS                     | AN65-110  |

| APPENDIX I                                                     | AN65-111  |

| ADDITIONAL CIRCUITS                                            | AN65-111  |

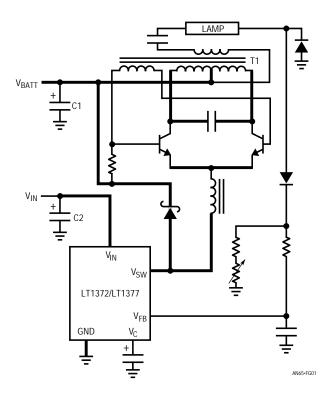

| Desktop Computer CCFL Power Supply                             | AN65-111  |

| Dual Transformer CCFL Power Supply                             |           |

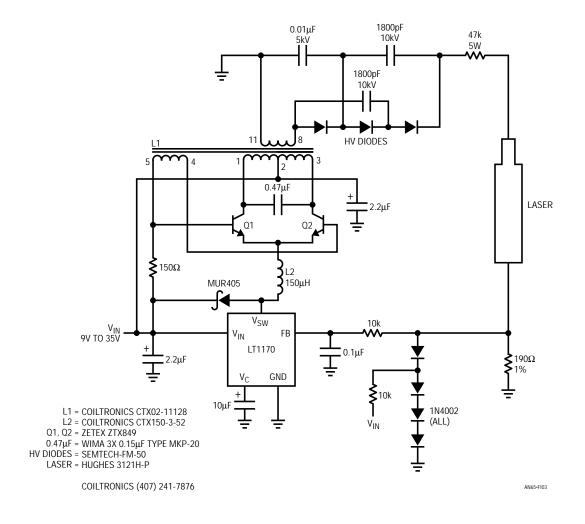

| HeNe Laser Power Supply                                        | AM65-113  |

| APPENDIX J                                                     | AN65-114  |

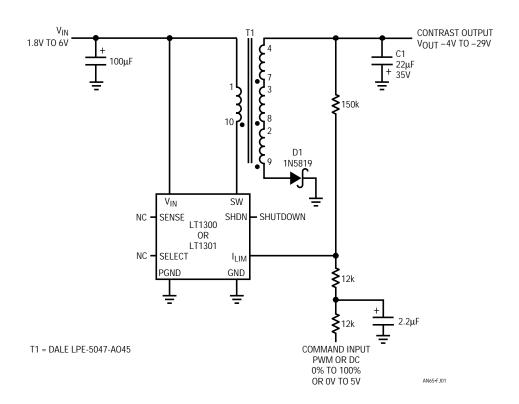

| LCD CONTRAST CIRCUITS                                          | AN65-114  |

| Dual Output LCD Bias Voltage Generator                         | AN65-115  |

| LT118X Series Contrast Supplies                                | AN65-116  |

| APPENDIX K                                                     | AN65-119  |

| WHO WAS ROYER, AND WHAT DID HE DESIGN?                         |           |

| APPENDIX L                                                     |           |

| A LOT OF CUT OFF EARS AND NO VAN GOGHS/Some Not-So-Great Ideas | AN65-120  |

| Not-So-Great Backlight Circuits                                | AN65-120  |

| Not-So-Great Primary Side Sensing Ideas                        | AN65-122  |

#### INTRODUCTION

This scribing marks the fourth LTC publication in as many years concerning LCD illumination. The extraordinary user response to previous efforts has resulted in a continuing LCD backlight development effort by our company. This level of interest, along with significant performance advances since the last publication, justifies further discussion of LCD backlighting.

Development of attractive solutions for LCD illumination has necessitated the longest sustained LTC application engineering effort to date. A single circuit in a 1991 publication (*Measurement and Control Circuit Collection*, LTC Application Note 45, June 1991) has resulted in four years of continuous investigation, summarized in three successive, dedicated publications.

The impetus for all this bustle has been an overwhelming and continuously ascending reader response. Practical, high performance LCD backlighting solutions are needed in a wide range of applications. The optical, transductive and electronic aspects combine (conspire?) to present an extraordinarily challenging problem. The LCD backlight problem's interdisciplinary nature, along with highly interactive effects, provides an exquisitely subtle engineering exercise. Backlights present the most complex set of interdependencies the author has ever encountered. Our academic interest in this challenge is, of course, well

patinaed with capitalistic intent. Substantial comfort arrives with the certainty that the audience is similarly acculturated.

This publication includes pertinent information from previous efforts in addition to updated sections and a large body of new material. The partial repetition is a small penalty compared to the benefits of text flow, completeness and time efficient communication. Older material has been altered, abridged or augmented as appropriate, while simultaneously introducing new findings. Previous work has emphasized obtaining and verifying high efficiency. This characteristic is still quite desirable, but other backlight requirements have become evident. These include low voltage operation, improved system interface, minimization of display-induced losses, circuitry compaction and better measurement/optimization techniques. These advances have been enabled by development of new ICs and instrumentation.

Finally, this preamble must appreciate the text's arrangement and review by various LTC personnel and customers. They transmuted a psychotic uproar of a manuscript into this finessed presentation. Hopefully, readers will join the author in applause.

Note 1. Previous publications are annotated in References 1, 18 and 25.

#### PERSPECTIVES ON DISPLAY EFFICIENCY

The LCD displays currently available require two power sources, a backlight supply and a contrast supply. The display backlight is the single largest power consumer in a typical portable apparatus, accounting for almost 50% of battery drain with the display at maximum intensity. As such, every effort must be expended to maximize backlight efficiency.

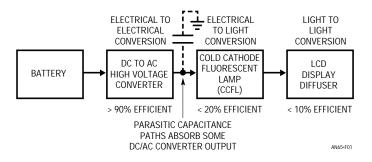

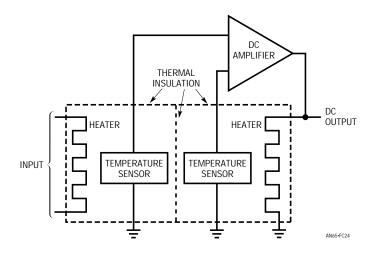

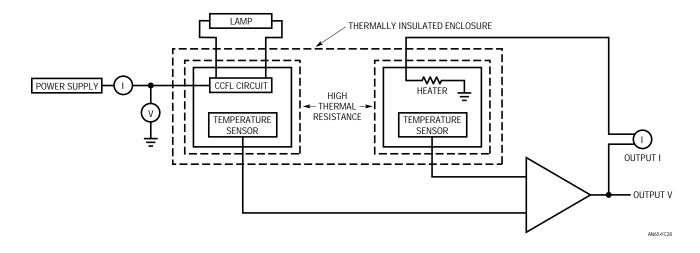

Study of LCD energy management should consider the problem from an interdisciplinary viewpoint. The backlight presents a cascaded energy attenuator to the battery (Figure 1). Battery energy is lost in the electrical-to-electrical conversion to high voltage AC to drive the CCFL. This section of the energy attenuator is the most efficient; conversion efficiencies exceeding 90% are possible. The CCFL, although the most efficient electrical-to-light converter available today, has losses exceeding 80%. Additionally, the optical transmission efficiency of present displays is under 10% for monochrome with color types much lower.

Figure 1. Backlit LCD Display Presents a Cascaded Energy Attenuator to the Battery. DC/AC Conversion is Significantly More Efficient Than Energy Conversions in Lamp and Display

The very high DC/AC conversion efficiency highlights some significant issues. Anything that improves energy transfer in the other "attenuator" areas will have greater impact than further electrical efficiency improvements. Additional improvements in electrical efficiency, while certainly desirable, are reaching the point of diminishing returns. Clearly, overall backlight efficiency gains must come from lamp and display improvements.

There is very little electrical workers can do to improve lamp and display efficiency besides call attention to the problems (see the following sections on lamps and displays).<sup>2</sup> Improvements are, however, possible in related

areas. In particular, the *form* of drive applied to the lamp is quite critical. The waveshape supplied to the lamp influences its current-to-light conversion efficiency. Thus, dissimilar waveforms containing equivalent power can produce different amounts of lamp light output. This implies that a more *electrically* efficient inverter with a nonoptimal output waveshape could produce less light than a "less efficient" inverter with a more appropriate waveform. Experiment reveals this to be true. As such, distinction between electrical and photometric efficiency is necessary and requires attention.

Another practical area where improvement is possible is transmission of inverter drive to the lamp. The high frequency AC waveform is subject to losses due to parasitic capacitances in the wiring and display. Controlling the parasitic capacitances and the manner in which lamp drive is applied can yield significant efficiency improvement.

Practical methods addressing both aforementioned areas are contained in subsequent sections of this publication.

### Cold Cathode Fluorescent Lamps (CCFLs)

Any discussion of CCFL power supplies must consider lamp characteristics. These lamps are complex transducers, with many variables affecting their ability to convert electrical current to light. Factors influencing conversion efficiency include the lamp's current, temperature, drive waveform characteristics, length, width, gas constituents and the proximity to nearby conductors.

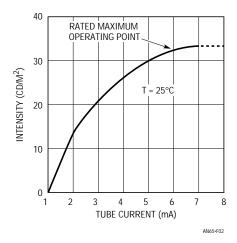

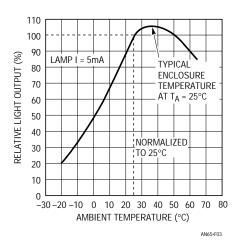

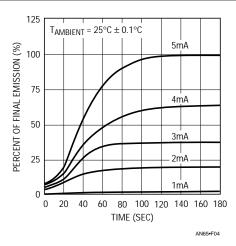

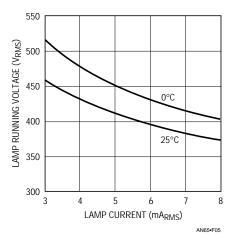

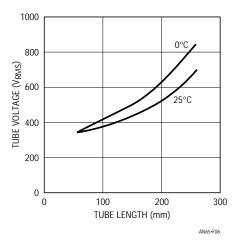

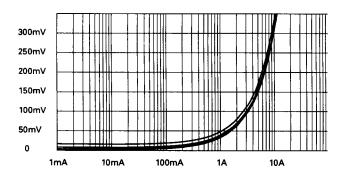

These and other factors are interdependent, resulting in a complex overall response. Figures 2 through 8 show some typical characteristics. A review of these curves hints at the difficulty in predicting lamp behavior as operating conditions vary. The lamp's current, temperature and warm-up time are clearly critical to emission, although electrical efficiency may not necessarily correspond to the best optical efficiency point. Because of this, both electrical and photometric evaluation of a circuit is often required. It is possible, for example, to construct a CCFL circuit with 94% electrical efficiency which produces less

**Note 2.** "Call attention to the problems" constitutes a pleasant euphemism for complaining. This publication's section on displays presents such complaints in visual form along with suggested remedies.

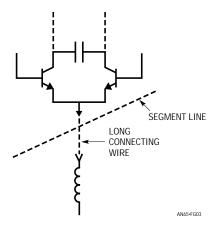

light output than an approach with 80% electrical efficiency. (See Appendix L, "A Lot of Cut Off Ears and No Van Goghs — Some Not-So-Good Ideas.") Similarly, the performance of a very well matched lamp/circuit combination can be severely degraded by a lossy display enclosure or excessive high voltage wire lengths. Display enclosures with too much conducting material near the lamp have huge losses due to capacitive coupling. A poorly designed display enclosure can easily degrade efficiency by 20%. High voltage wire runs typically cause 1% loss per inch of wire.

Figure 2. Emissivity for a Typical 5mA Lamp. Curve Flattens Badly Above 6mA

Figure 3. Ambient Temperature Effects on Emissivity of a Typical 5mA Lamp. Lamp and Enclosure Must Come to Thermal Steady State Before Measurements Are Made

Figure 4. Emissivity vs On-Time for a Typical Lamp in Free Air. Lamp Must Arrive at Temperature Before Emission Stabilizes

Figure 5. Lamp Current vs Voltage in the Operating Region. Note Large Temperature Coefficient

Figure 6. Running Voltage vs Lamp Length at Two Temperatures. Start-Up Voltages Are Usually 50% to 200% Higher Over Temperature

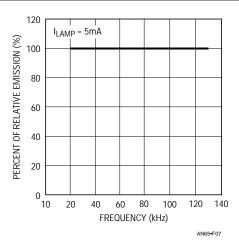

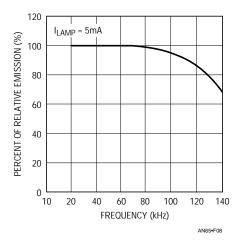

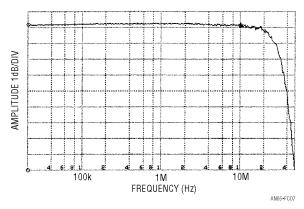

Figure 7. Lamp Emission vs Drive Frequency with Lamp in Free Space. No Change Is Measurable from 20kHz to 130kHz, Indicating Lamp Insensitivity to Frequency

Figure 8. Figure 7's Lamp Shows Significant Emission vs Drive Frequency Degradation When Mounted in a Display. Cause Is Frequency-Dependent Loss Due to Display's Parasitic Capacitance Paths

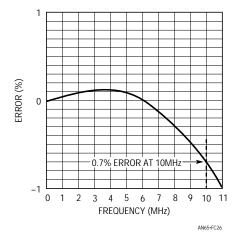

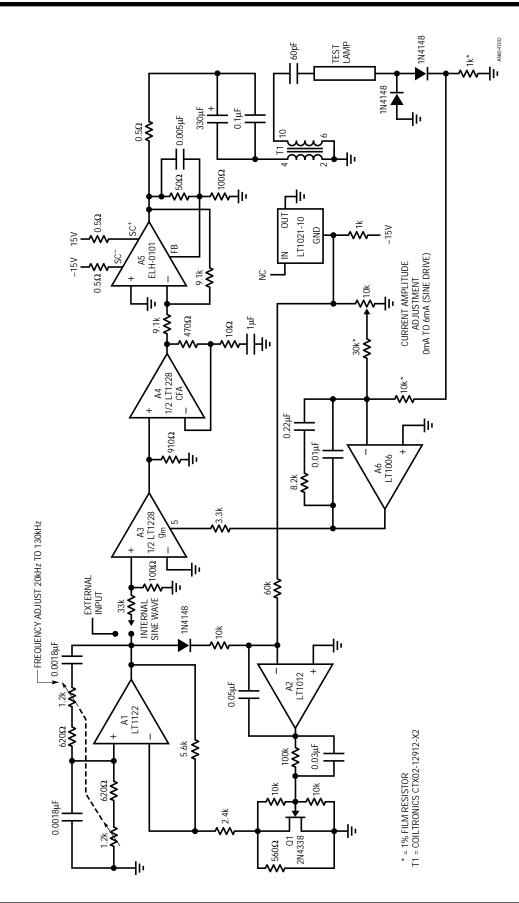

The optimum drive frequency is determined by display and wiring losses, not lamp characteristics. Figure 7 shows lamp emissivity is essentially flat over a wide frequency range. Figure 8 shows results with the same lamp mounted in a typical display.

The apparent emissivity fall-off at high frequencies is caused by reduced lamp current due to parasitic capacitance-induced losses. As frequency increases, the display's parasitic capacitance diverts progressively more energy, lowering lamp current and emission. This effect is sometimes misinterpreted, leading to the mistaken conclusion that lamp emissivity degrades with increasing frequency.

#### **CCFL Load Characteristics**

These lamps are a difficult load to drive, particularly for a switching regulator. They have a "negative resistance" characteristic; the starting voltage is significantly higher than the operating voltage. Typically, the start voltage is about 1000V, although higher and lower voltage lamps are common. Operating voltage is usually 300V to 500V, although other lamps may require different potentials. The lamps will operate from DC, but migration effects within the lamp will quickly damage it. As such, the waveform must be AC. No DC content should be present.

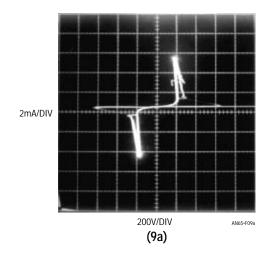

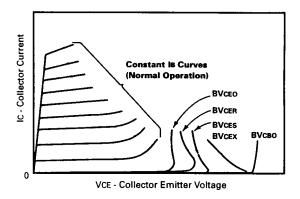

Figure 9a shows an AC driven lamp's characteristics on a curve tracer. The negative resistance-induced "snap-back" is apparent. In Figure 9b another lamp, acting against the curve tracer's drive, produces oscillation. These tenden-

Figure 9. Negative Resistance Characteristic for Two CCFL Lamps. "Snap-Back" Is Readily Apparent, Causing Oscillation in 9b. These Characteristics Complicate Power Supply Design

cies, combined with the frequency compensation problems associated with switching regulators, can cause severe loop instabilities, particularly on start-up. Once the lamp is in its operating region it assumes a linear load characteristic, easing stability criteria. Lamp operating frequencies are typically 20kHz to 100kHz and a sine-like waveform is preferred. The sine drive's low harmonic content minimizes RF emissions, which could cause interference and efficiency degradation. A further benefit to the continuous sine drive is its low crest factor and controlled rise times, which are easily handled by the CCFL. CCFL's RMS current-to-light output efficiency and lifetime degrades with fast rise, high crest factor drive waveforms. 4

#### **Display and Layout Losses**

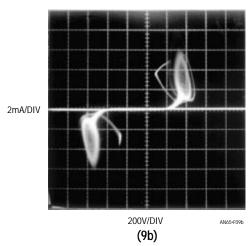

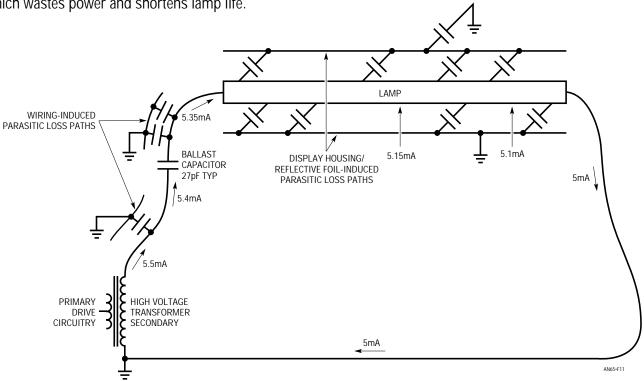

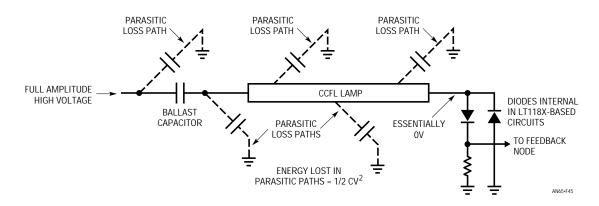

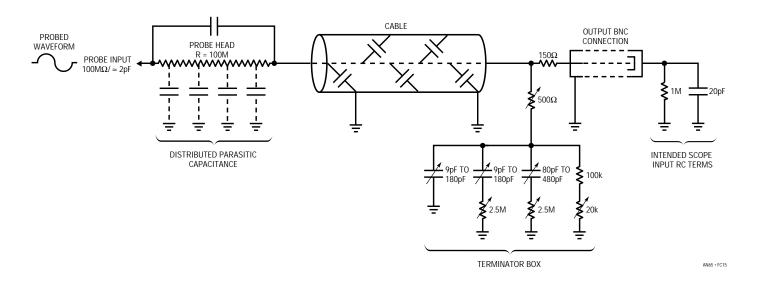

The physical layout of the lamp, its leads, the display housing and other high voltage components are integral parts of the circuit. Placing the lamp into a display introduces pronounced electrical loading effects which must be considered. Poor layout can easily degrade efficiency by 25% and higher layout-induced losses have been observed. Producing an optimal layout requires attention to how losses occur. Figure 10 begins our study by examining potential parasitic paths between the transformer's output and the lamp. Parasitic capacitance to AC ground from any point between the power supply output and the lamp creates a path for undesired current flow. Similarly, stray coupling from any point along the lamp's length to AC ground induces parasitic current flow.

All parasitic current flow is wasted, causing the circuit to produce more energy to maintain desired current flow in the lamp. The high voltage path from the transformer to the display housing should be as short as possible to minimize losses. A good rule of thumb is to assume 1% efficiency loss per inch of high voltage lead. Any PC board traces, ground or power planes should be relieved by at least 1/4" in the high voltage area. This not only prevents losses but eliminates arcing paths.

Parasitic losses associated with lamp placement within the display housing require attention. High voltage wire length within the housing must be minimized, particularly for displays using metal construction. Ensure that the high voltage is applied to the shortest wire(s) in the display. This may require disassembling the display to verify wire length and layout. Another loss source is the reflective foil commonly used around lamps to direct light into the actual LCD. Some foil materials absorb considerably more field energy than others, creating loss. Finally, displays supplied in metal enclosures tend to be lossy. The metal absorbs significant energy and an AC path to ground is unavoidable. Direct grounding of metal enclosed displays further increases losses. Some display manufacturers have addressed this issue by relieving the metal in the lamp area with other materials. Losses introduced by the

**Note 3**. Many of the characteristics of CCFLs are shared by so-called "Hot" cathode fluorescent lamps. See Appendix A, "Hot" Cathode Fluorescent Lamps.

Note 4. See Appendix L, "A Lot of Cut Off Ears and No Van Goghs—Some Not-So-Great Ideas."

Figure 10. Loss Paths Due to Stray Capacitance in a Practical LCD Installation. Minimizing These Paths Is Essential for Good Efficiency

display are substantial and vary widely with different displays. These losses not only degrade overall efficiency, but complicate meaningful determination of the lamp current. Figure 11 shows effects of distributed parasitic capacitance loss paths on lamp current. The display housing and reflective foil-induced loss paths provide a continuous conduit for loss current flow. This results in a continuously varying value of "lamp current" along the lamp's length. In cases where one end of the lamp is at or near ground, the current fall-off is greatest in the lamp's high voltage regions. Although parasitic capacitance is usually uniformly distributed, its effect becomes far greater as voltage scales up.

These effects illustrate why designing around lamp specifications is such a frustrating exercise. Display vendors typically call out lamp operating parameters based on information received from the lamp manufacturer. Lamp vendors often determine operating characteristics in a completely different enclosure, or none at all. This set of uncertainties complicates design effort. The only viable solution is to determine lamp performance with the display of interest. This is the only practical way to maximize performance and ensure against overdriving the lamp, which wastes power and shortens lamp life.

In general, the display introduces parasitics which degrade performance. Latter portions of this text discuss some compensatory techniques, but the deleterious effects of display parasitics dominate practical backlight design.

There are some benefits to lossy displays. One advantage of display parasitics is that they effectively lower lamp breakdown voltage. The parasitic shunt capacitance along the tube's length forms a distributed electrode, effectively shortening the breakdown path, lowering the lamp's turnon voltage. This accounts for the fact that many display mounted lamps start at lower voltages than the "naked" lamp breakdown voltage specification suggests. This effect aids low temperature start-up (see Figures 5 and 6).

A second potential advantage of distributed parasitic lamp capacitance is enhancement of low current operation. In some cases extended dimming range is possible because the parasitics provide a more evenly distributed field along the lamp's length. This tends to maintain illumination along the lamp's entire length at low operating currents, allowing low luminosity operation.

Figure 11. Distributed Parasitic Capacitances in a Practical Situation Cause Continuous Downward Shift in Measured "Lamp Current." In This Case 0.5mA Is Lost to Parasitic Paths. Most Loss Occurs in High Voltage Regions

The lessons here are clear. A thorough characterization of lamp/display losses is crucial to understanding trade-offs and obtaining the best possible performance. The highest efficiency "in system" backlights have been produced by careful attention to these issues. In some cases the entire display enclosure was re-engineered for lower losses.

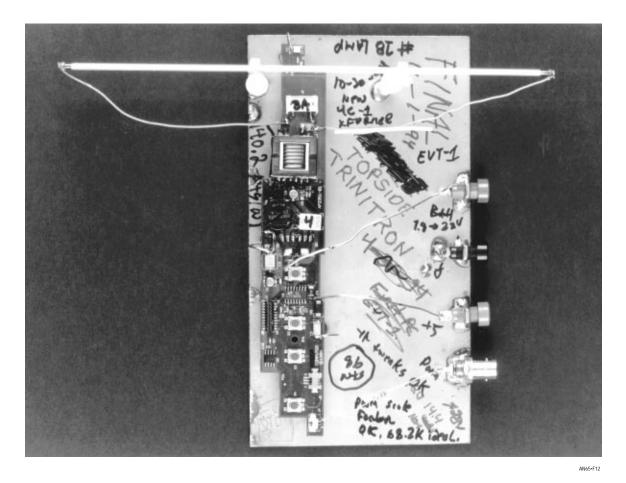

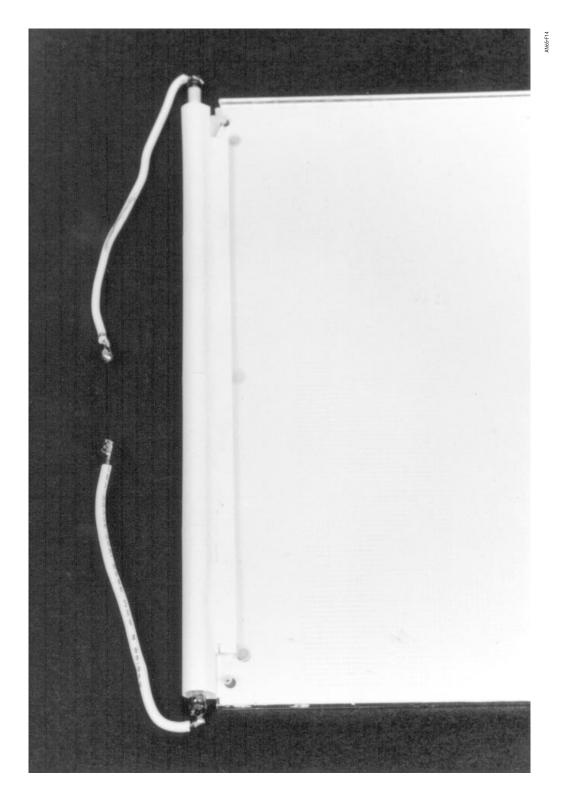

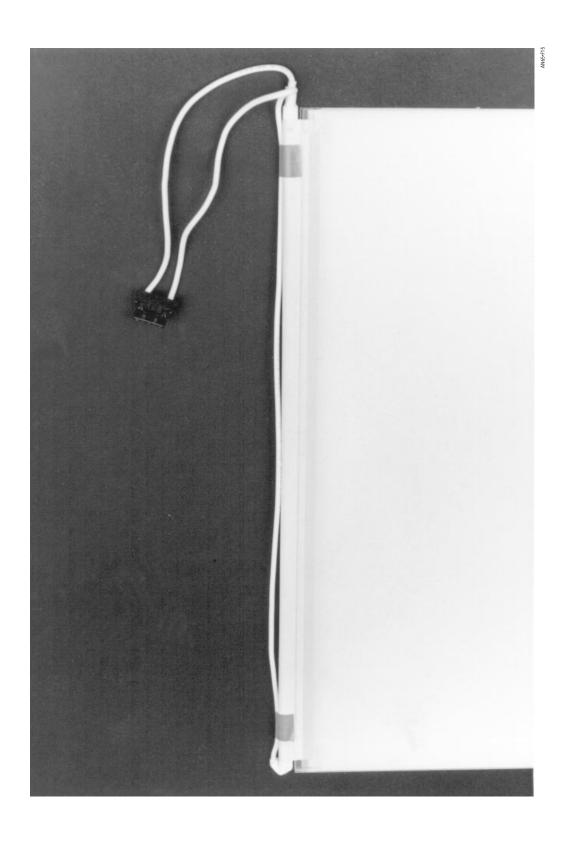

The display loss issue, central to backlight design, merits detailed attention. The following briefly commented photographs (Figures 12 through 32) illustrate a variety of display situations. Hopefully, this visual tour will alert display users and manufacturers to the problems involved, promoting appropriate action by both.

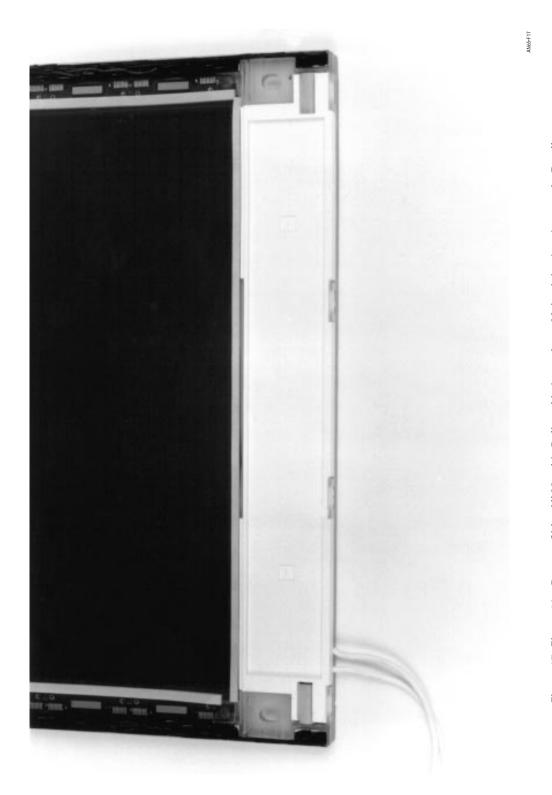

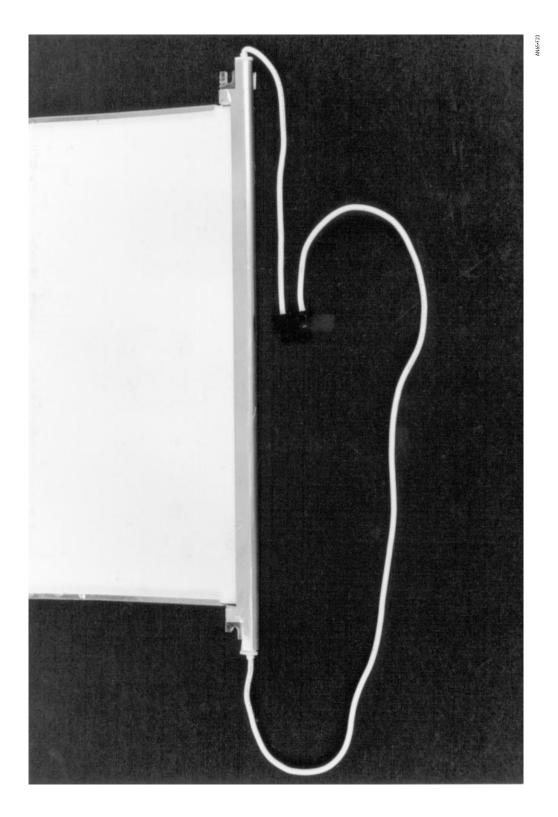

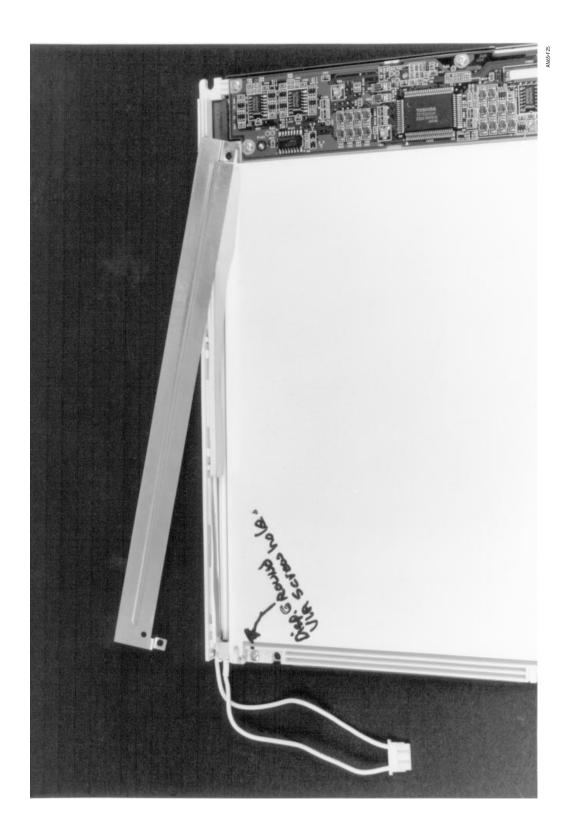

Figure 12. The Ideal Display Is No Display. Drive Electronics Connected to a "Naked" Lamp Simulates a Zero Loss Display. Note Nylon Stand-Offs. Results Obtained Have No Relationship to Practical Display Driving

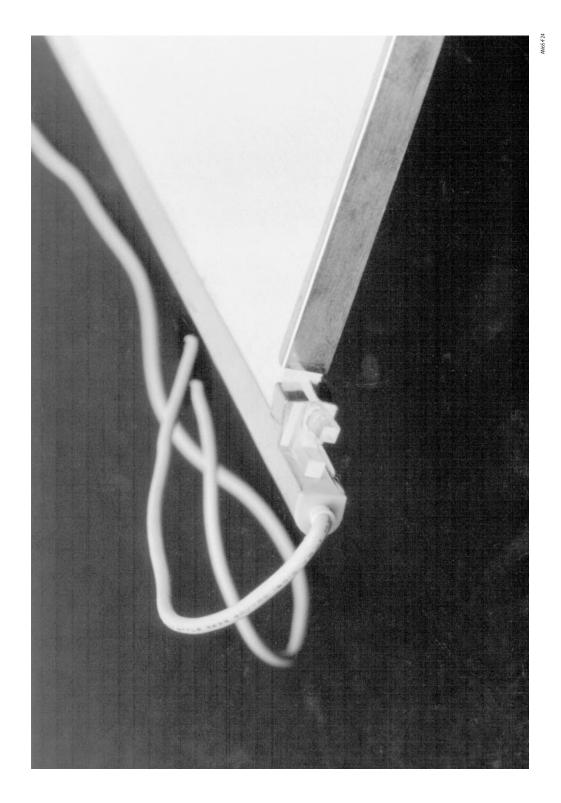

Figure 13. Measuring Lamp Wire to Display Frame Capacitance. Technique Gives Lead Wire-to-Frame Loss Information but Not Lamp-to-Foil-or-Frame Loss Data. Lamp Must Be Energized Before Its Parasitics Are Measurable

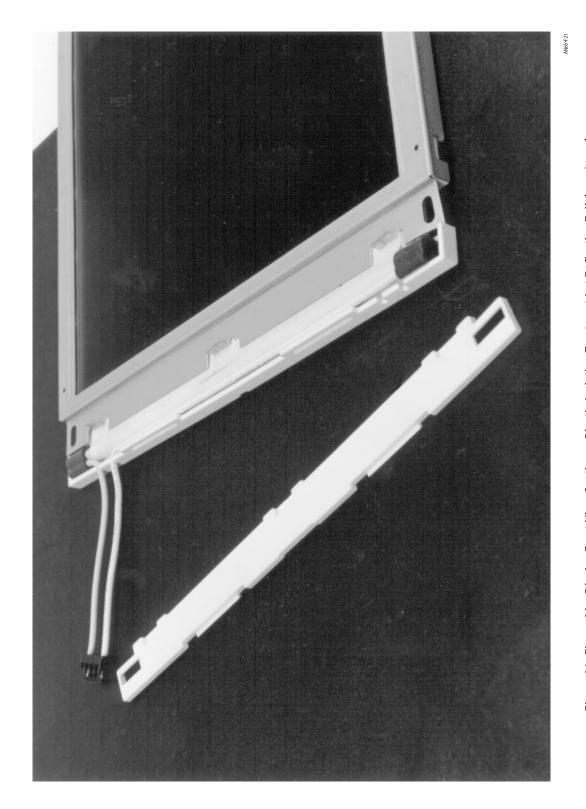

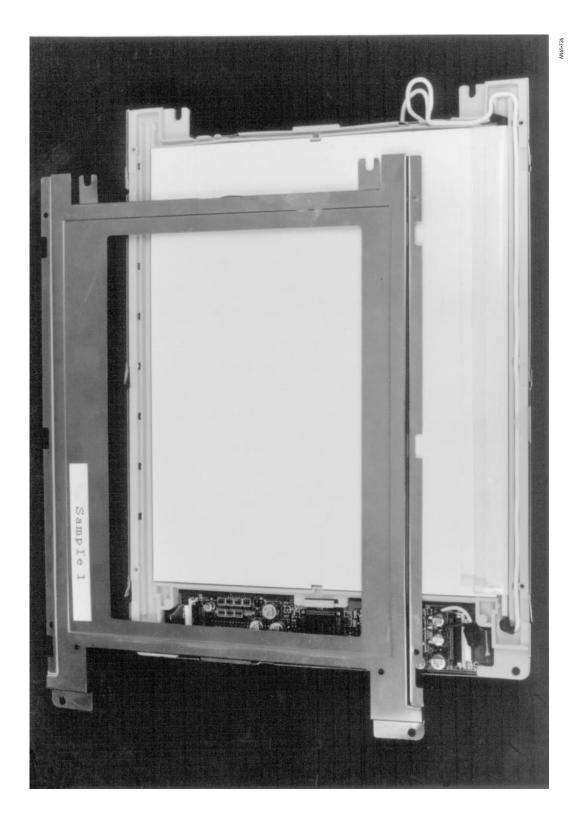

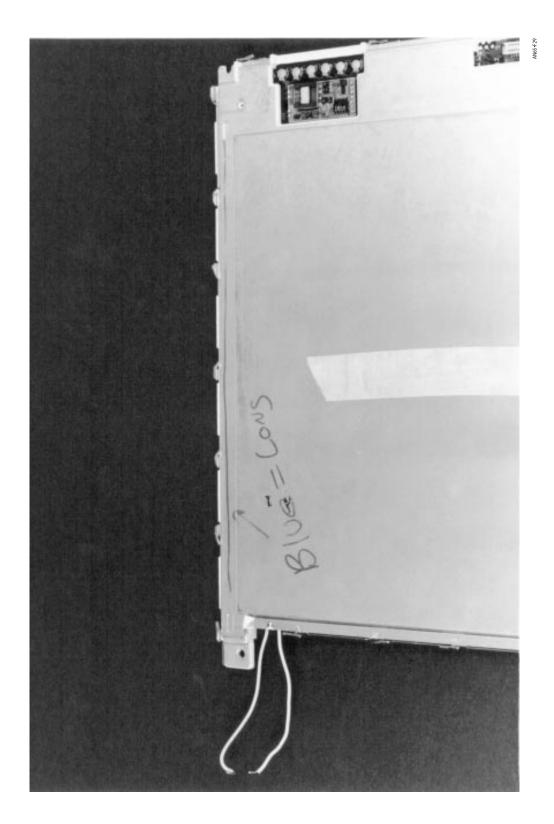

Figure 14. Low Loss Display Has No Metal in Lamp Region. Reflective Foil Floats from Ground and Has Low Absorption. Display Loss About 1.5%

Figure 15. Another Low Loss Display Has Similar Characteristics to Figure 14. Running Long Wire Return Across Lamp Length Increases Loss to about 4%. Spacing Wire Away from Lamp Would Cut Loss by Half

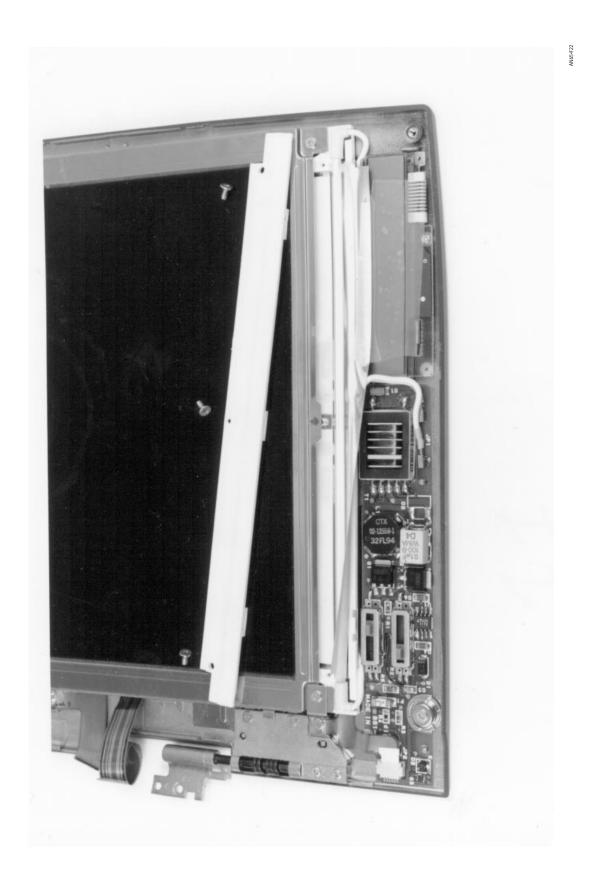

Figure 16. A Custom Designed, Extremely Low Loss Display. All Metal Is Eliminated in Lamp Area (Lower Portion of Photo). A Good Compromise Between Mechanical Strength and Loss Control

Figure 17. Figure 16's Reverse Side. All Metal Is Relieved in Lamp Area, Maintaining Low Losses. An Excellent, Practical Display

TECHNOLOGY TECHNOLOGY

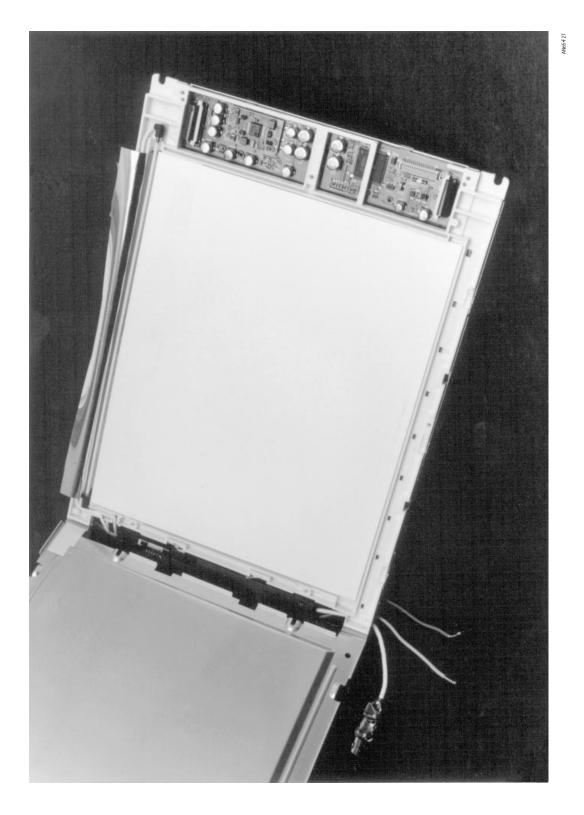

Figure 18. Plastic "Cocoon" Cuts Losses. Metallic Foil Is Absorptive but Floats from Grounded Display Frame. A Good Compromise with about 4% Loss

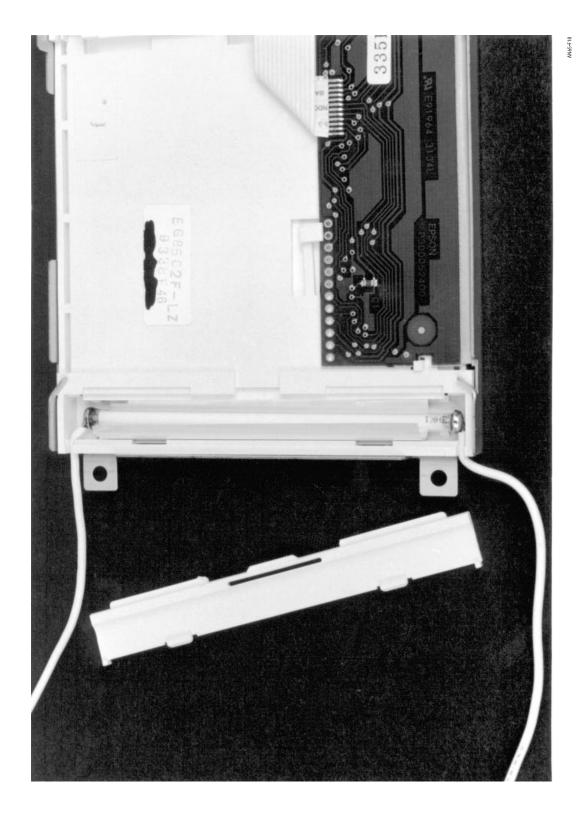

Figure 19. Plastic "Outrigger" Isolates Lamp from Metal Display Frame Loss Path

LINEAR TECHNOLOGY

Figure 20. Plastic Isolates Lamp from Metal Frame in This Display's Rear View

Figure 21. Figure 20's Display Front View Continues Plastic Isolation Treatment but Reflective Foil (over Lamp) Contacts Metal Frame. Massive Losses via This Path Cause Overall 12% Loss. Trimming Foil from Metal Cuts Loss to 4%

LINEAR TECHNOLOGY

Figure 22. Another "Outrigged" Plastic Enclosure Suffers Foil Contacting Display's Frame Metal. Relieving Foil from Metal Cuts Losses from 13% to 6%. Poor Wire Routing (Lower Right) Causes 3% Loss

TECHNOLOGY TECHNOLOGY

Figure 23. Isolation Slits (Center Right and Left) in Metal Reflector Prevent Losses to Grounded Metal Frame (Upper Right and Left). Overall Losses About 6%

TECHNOLOGY TECHNOLOGY

Figure 24. Close-Up of Figure 23's Isolation Slit Construction. Secondary Benefit Is Control of Reflector-to-Lamp Distance, Minimizing Capacitance

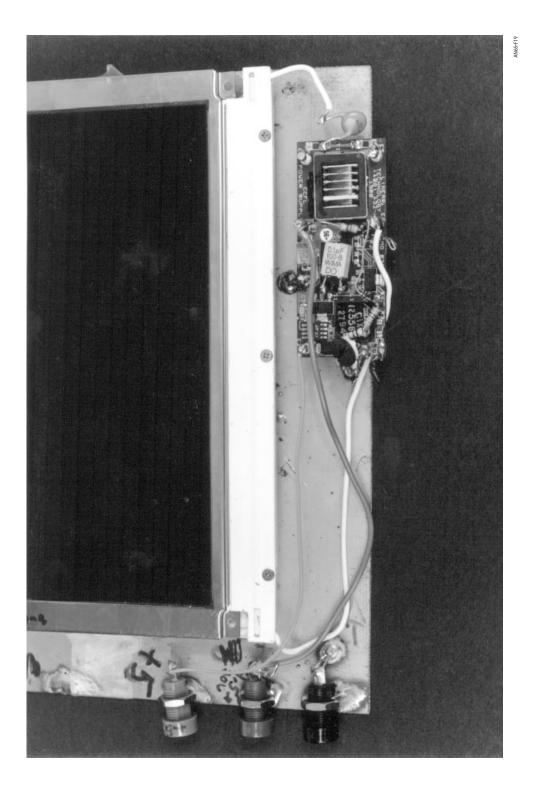

Figure 25. Metal Cover over Lamp Causes 15% Loss. Replacing Cover Securing Screws with Nylon Types Floats Cover from Ground, Dropping Loss to 8%. Replacing Cover with Plastic Improves Loss to Only 3%...a 5X Improvement!

Figure 26. Huge Metal Area over Lamp Causes 14% Loss. Replacing Metal in Lamp Area with Plastic Cuts Loss to 6%

Figure 27. Metallic Foil over Lamp (Upper Center) Dumps Absorbed Energy to Metal Rear Cover. 16% Loss Results

LINEAR TECHNOLOGY

Figure 28. Low Losses of the Display's Nonconductive Frame (Black Plastic) Are Thrown Away by Lossy Reflective Foil Contacting Massive Metal Rear Cover. 15% Loss Results

Figure 29. A Similar Situation to Figure 28. Large Metal Rear Cover Contacts Lossy Foil (Not Visible), Causing Huge Losses

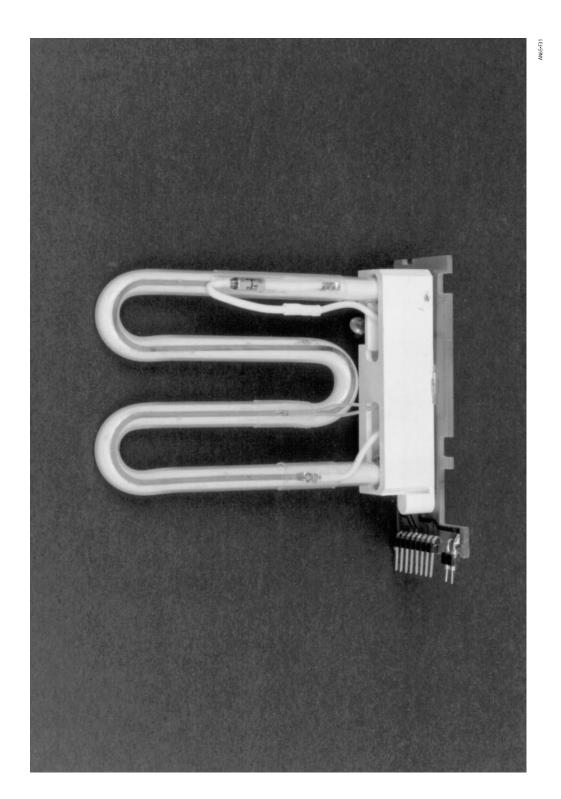

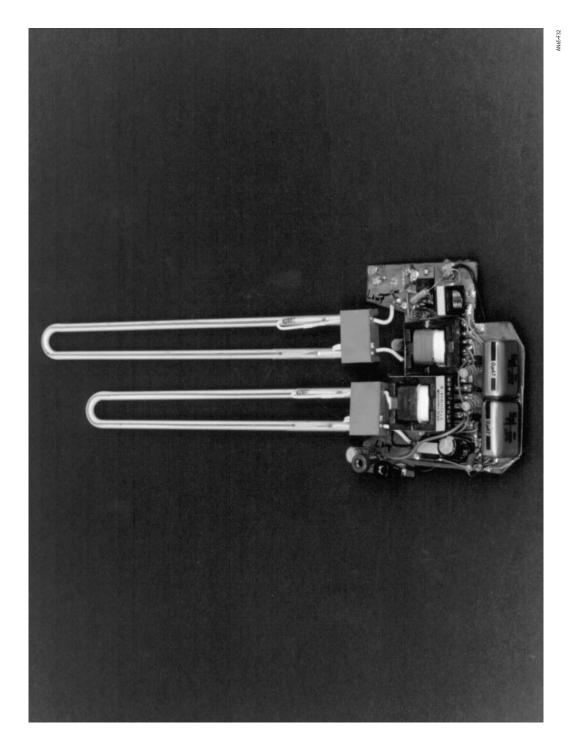

Figure 30. Grounded Metallic Optical Reflector in Automotive Lamp Introduces 18% Loss. Optical Gain over Nonmetallic Reflector May Justify Large Electrical Loss

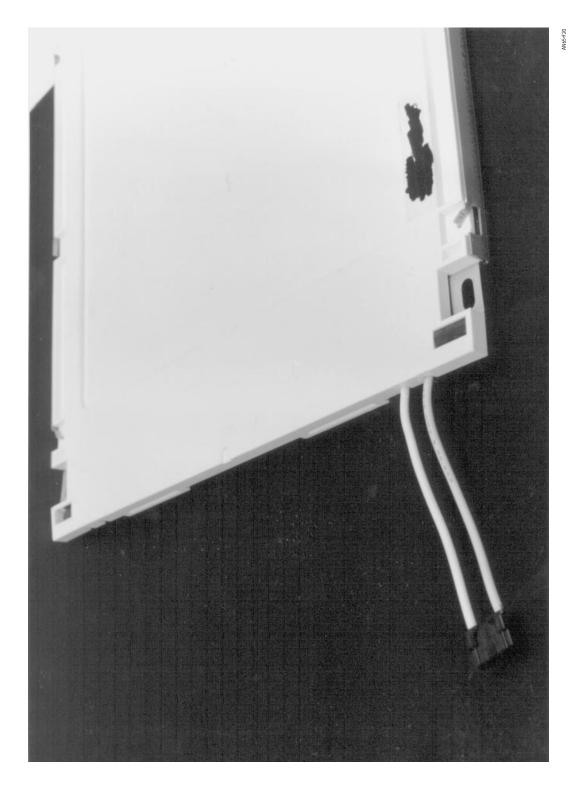

Figure 31. Metallic Heater on Lamp in this Automotive Application Eases Low Temperature Starting but Causes 31% Loss

Figure 32. Similar to Figure 31. Metallic Cold Start Heaters in Automotive Application Induce 23% Loss

#### **Considerations for Multilamp Designs**

Multiple-lamp designs are not recommended if lamp intensity matching is important. Maintaining emission matching over time, temperature and production variations is quite difficult. In some restricted cases multilamp displays may be a viable option, but a single lamp with good diffuser optics is almost always the better approach. Information on dual-lamp displays is presented here for reference purposes only.<sup>5</sup>

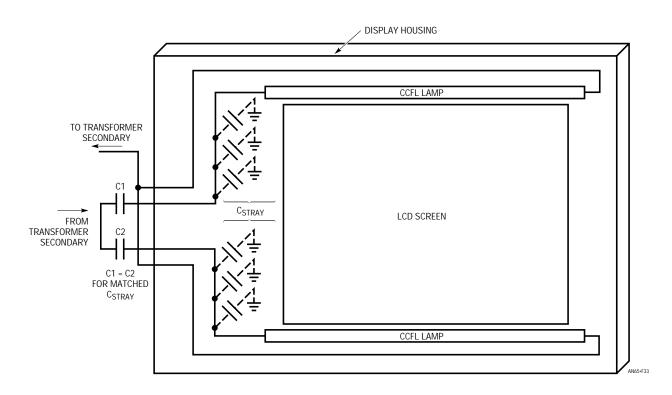

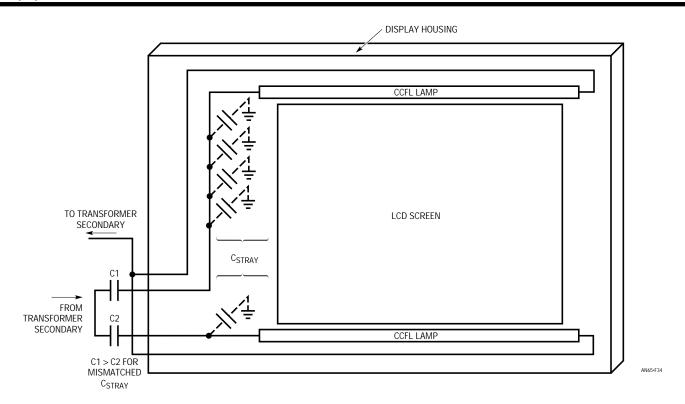

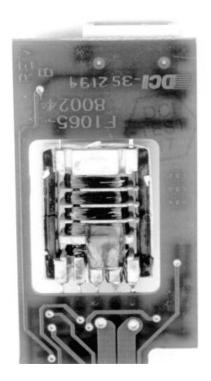

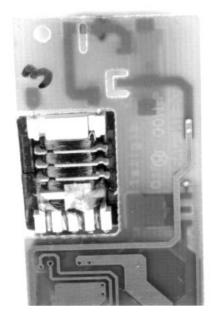

Systems using two lamps have some unique layout problems. Almost all dual-lamp displays are color units. The lower light transmission characteristics of color displays necessitates more light. As such, display manufacturers sometimes use two lamps to produce more light. The wiring layout of these dual-lamp color displays affects efficiency and illumination balance in the lamps. Figure 33 shows an "x-ray" view of a typical display. This symmetrical arrangement presents equal parasitic losses. If C1 and C2 and the lamps are well-matched, the circuit's current output splits evenly and equal illumination occurs.

Figure 34's display arrangement is less friendly. The asymmetrical wiring forces unequal losses and the lamps receive imbalanced current. Even with identical lamps, illumination may not be balanced. This condition is partially correctable by skewing values of C1 and C2. C1, because it drives greater parasitic capacitance, should be larger than C2. This tends to equalize the currents, promoting equal lamp drive. It is important to realize that this compensation does nothing to recapture the lost energy—efficiency is still compromised. There is no substitute for minimizing loss paths. Similarly, any change in lamp characteristics (e.g., aging) can cause imbalanced illumination to recur.

In general, imbalanced illumination causes fewer problems than might be supposed at high intensity levels. Unequal illumination is much more noticeable at lower levels. In the worst case the dimmer lamp may only partially illuminate. This phenomenon, sometimes called "Thermometering," is discussed in detail in the text section, "Floating Drive Circuits."

**Note 5**. The text's tone is intended to convey our distaste for multilamp displays. They are the very soul of heartache.

Figure 33. Loss Paths for "Best Case" Dual-Lamp Display. Symmetry Promotes Balanced Illumination, but Lamp Limitations Dominate Achievable Results

Figure 34. Asymmetric Losses in a Dual-Lamp Display. Skewing C1 and C2 Values Compensates Imbalanced Loss Paths but Not Wasted Energy

### **CCFL Power Supply Circuits**

Choosing an approach for a general purpose CCFL power supply is difficult. A variety of disparate considerations make determining the "best" approach a thoughtful exercise. Above all, the architecture must be extraordinarily flexible. The sheer number and diversity of applications demands this. The considerations take many degrees of freedom. Power supply voltages range from 2V to 30V with output power from minuscule to 50W. The load is highly nonlinear and varies over operating conditions. The backlight is often located some distance from the primary power source, meaning the supply must tolerate substantial supply bus impedances. Similarly, it must not corrupt the supply bus with noise, or introduce appreciable RFI into the system or environment. Component count should be low and the supply must be physically quite small as space is usually extremely limited. Additionally, the circuit must be relatively layout-insensitive because of varying board shape requirements. Interface for shutdown and dimming control should accommodate either digital or

analog inputs, including voltage, current, resistive, PWM or serial bit-stream addressing. Finally, lamp current should be predictable and stable with changes in time, temperature and supply voltage.

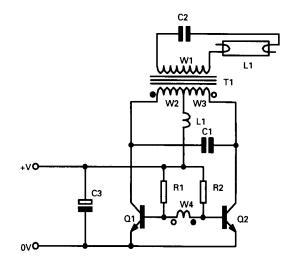

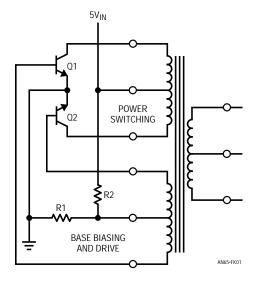

A current-fed, feedback-controlled resonant Royer converter meets these requirements. This approach, because of its extreme flexibility, is a favorable compromise. It operates over wide supply ranges and scales well over a broad output power range. Current is taken from the supply bus almost continuously, making the circuit tolerate supply bus impedance. This characteristic also means that circuit operation does not corrupt power supply lines. There is no RFI problem and component count is low. It is small, relatively insensitive to layout and easy to interface to. Lastly, lamp current is stable and predictable over operating conditions.

**Note 6.** See Appendices K and L for detailed discussion on architecture selection and the Royer configuration.

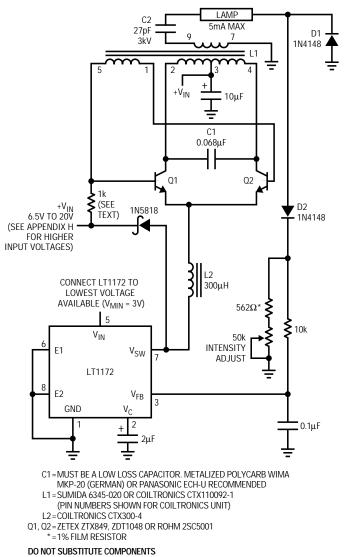

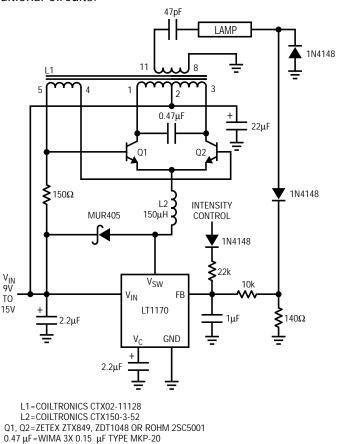

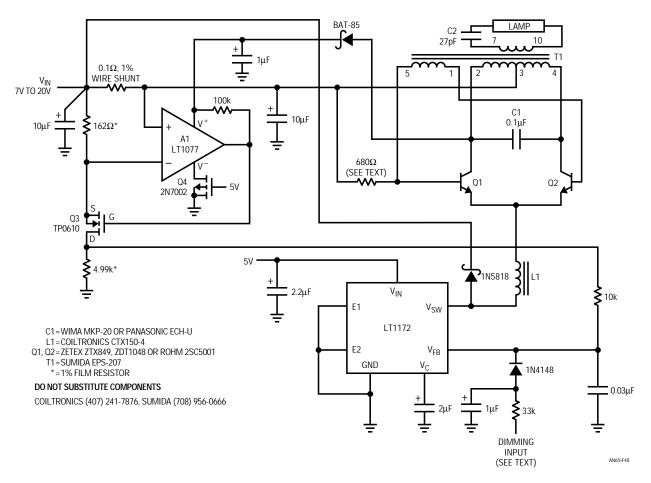

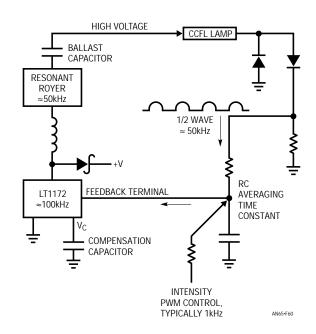

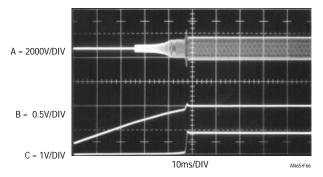

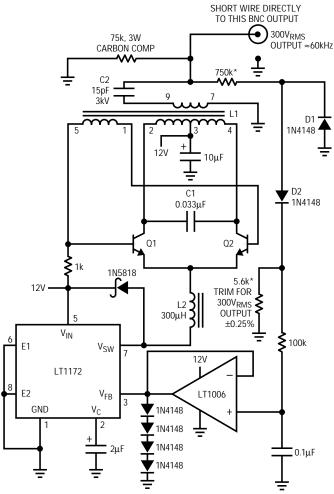

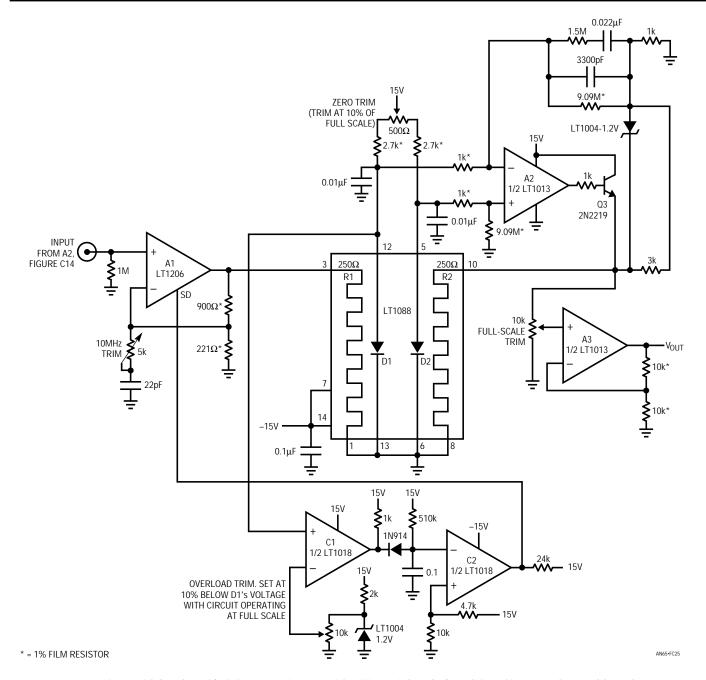

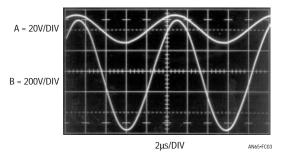

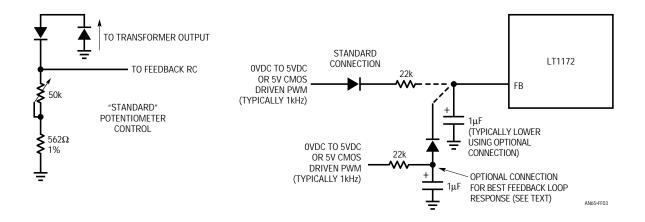

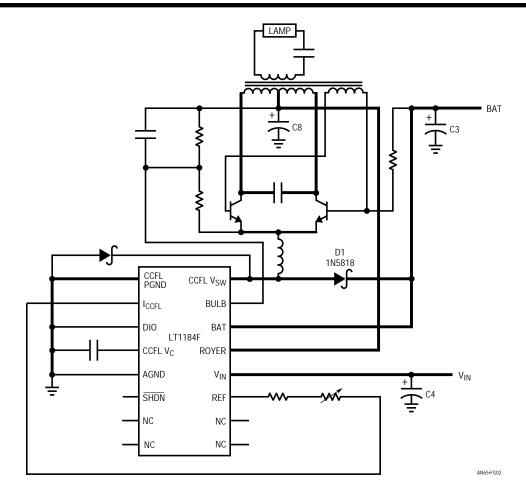

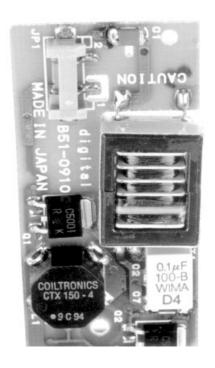

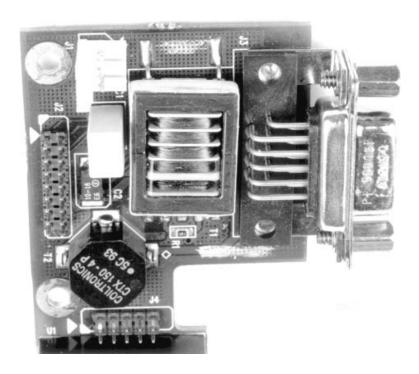

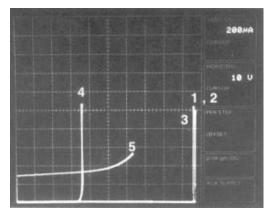

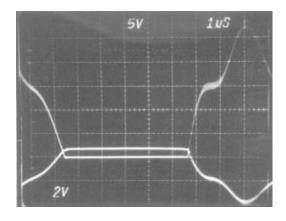

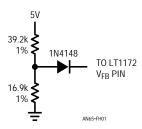

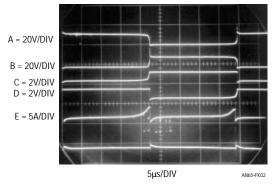

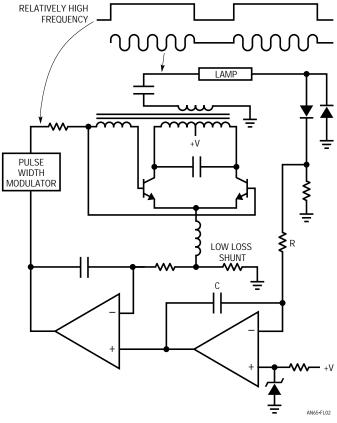

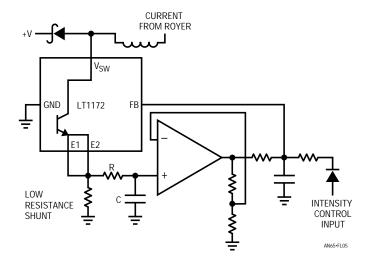

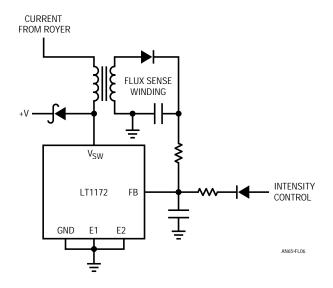

Figure 35 is a practical CCFL power supply circuit based on the above discussion. Efficiency is 88% with an input voltage range of 6.5V to 20V. This efficiency figure can be degraded by about 3% if the LT®1172 V<sub>IN</sub> pin is powered from the same supply as the main circuit  $V_{\text{IN}}$  terminal. Lamp intensity is continuously and smoothly variable from zero to full intensity. When power is applied the LT1172 switching regulator's Feedback pin is below the device's internal 1.2V reference, causing full duty cycle modulation at the V<sub>SW</sub> pin (Trace A, Figure 36). V<sub>SW</sub> conducts current (Trace B) which flows from L1's center tap,

COILTRONICS (407) 241-7876, SUMIDA (708) 956-0666

Figure 35. An 88% Efficiency Cold Cathode Fluorescent **Lamp Power Supply**

AN65+F35

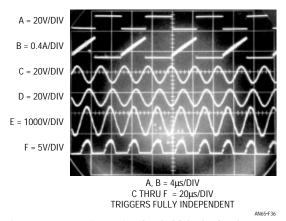

Figure 36. Waveforms for the Cold Cathode Fluorescent Lamp Power Supply. Note Independent Triggering on Traces A and B, and C through F

through the transistors, into L2. L2's current is deposited in switched fashion to ground by the regulator's action.

L1 and the transistors comprise a current driven Royer class converter which oscillates at a frequency primarily set by L1's characteristics (including its load) and the 0.068µF capacitor. LT1172 driven L2 sets the magnitude of the Q1/Q2 tail current, hence L1's drive level. The 1N5818 diode maintains L2's current flow when the LT1172 is off. The LT1172's 100kHz clock rate is asynchronous with respect to the push/pull converter's (60kHz) rate, accounting for Trace B's waveform thickening.

The 0.068µF capacitor combines with L1's characteristics to produce sine wave voltage drive at the Q1 and Q2 collectors (Traces C and D respectively). L1 furnishes voltage step-up and about 1400V<sub>P-P</sub> appears at its secondary (Trace E). Current flows through the 27pF capacitor into the lamp. On negative waveform cycles, the lamp's current is steered to ground via D1. Positive waveform cycles are directed via D2 to the ground referred  $562\Omega/50k$ potentiometer chain. The positive half-sine appearing across the resistors (Trace F) represents 1/2 the lamp current. This signal is filtered by the 10k/0.1µF pair and presented to the LT1172's Feedback pin. This connection closes a control loop which regulates lamp current. The 2μF capacitor at the LT1172's V<sub>C</sub> pin provides stable loop compensation. The loop forces the LT1172 to switch

Note 7. See Appendix K, "Who Was Royer and What Did He Design?" See also Reference 2.

mode modulate L2's average current to whatever value is required to maintain constant current in the lamp. The constant current's value, and hence lamp intensity, may be varied with the potentiometer. The constant current drive allows full 0% to 100% intensity control with no lamp dead zones or "pop-on" at low intensities. Additionally, lamp life is enhanced because current cannot increase as the lamp ages.

The circuit's 0.1% line regulation is notably better than some other approaches. This tight regulation prevents lamp intensity variation when abrupt line changes occur. This typically happens when battery-powered apparatus is connected to an AC-powered charger. The circuit's excellent line regulation derives from the fact that L1's drive waveform never changes shape as input voltage varies. This characteristic permits the simple  $10k\Omega/0.1\mu F$  RC to produce a consistent response. The RC averaging characteristic has serious error compared to a true RMS conversion, but the error is constant and "disappears" in the  $562\Omega$  shunt's value.

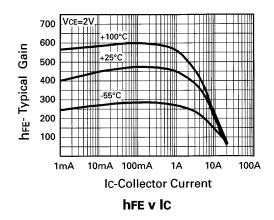

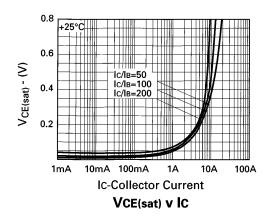

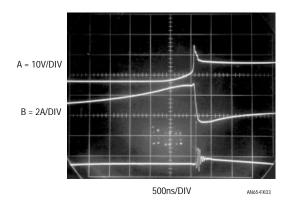

This circuit is similar to one previously described<sup>9</sup> but its 88% efficiency is 6% higher. The efficiency improvement is primarily due to the transistor's higher gain and lower saturation voltage. The base drive resistor's value (nominally 1k) should be selected to provide full V<sub>CE</sub> saturation without inducing base overdrive or beta starvation. A procedure for doing this is described in a following section, "General Optimization and Measurement Considerations."

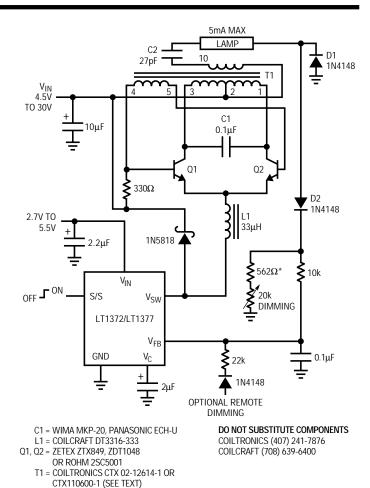

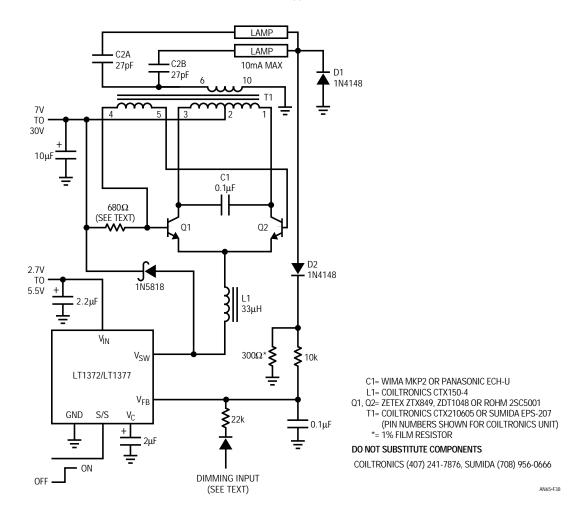

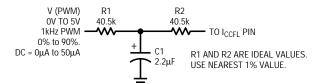

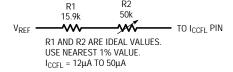

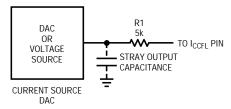

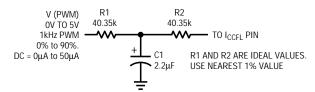

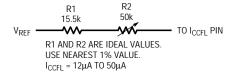

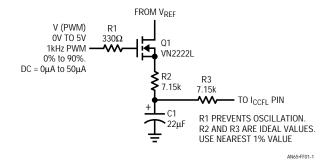

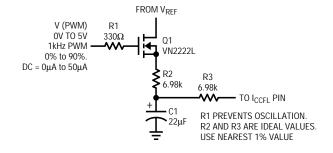

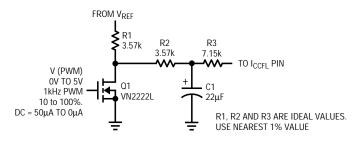

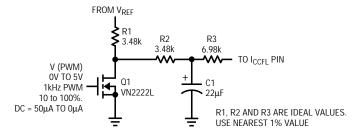

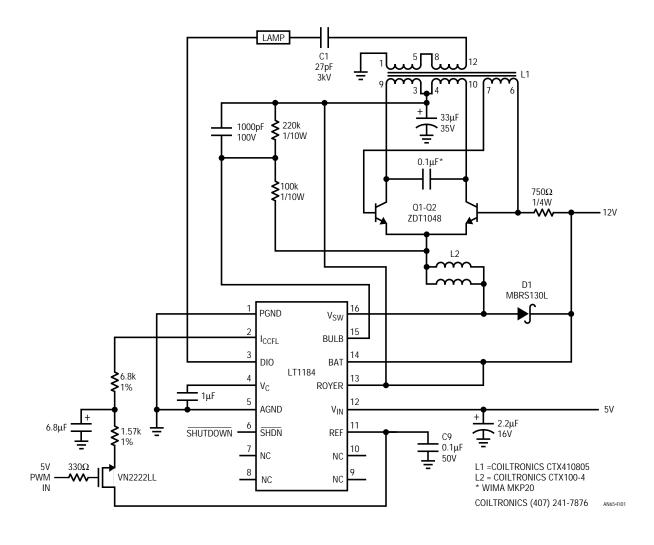

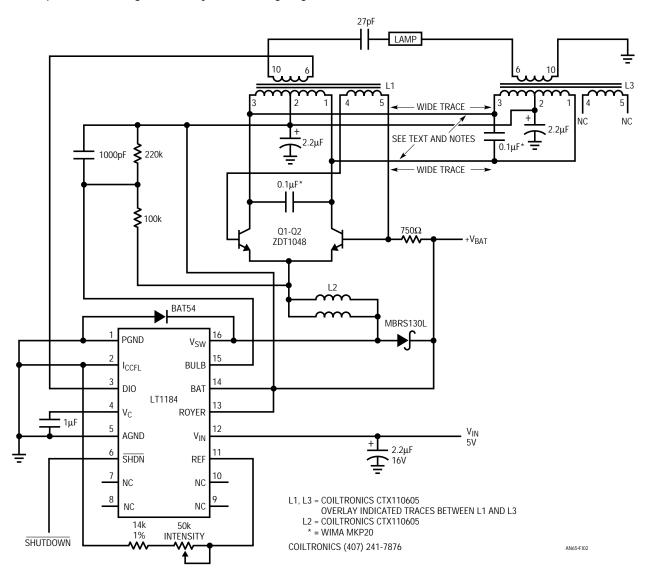

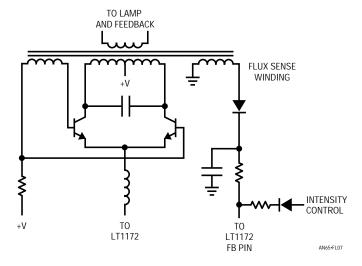

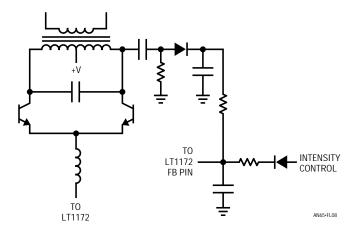

Figure 37's circuit is similar, but uses a transformer with lower copper and core losses to increase efficiency to 91%. The trade-off is slightly larger transformer size. Additionally, a higher frequency switching regulator offers slightly lower V<sub>IN</sub> current, aiding efficiency. L1's smaller value, a result of the higher frequency operation, permits slightly reduced copper loss. The transformer options listed allow efficiency optimization over the supply range of interest. Value shifts in C1, L2 and the base drive resistor reflect different transformer characteristics. This circuit also features shutdown and a DC or pulse width controlled dimming input. Appendix F, "Intensity Control and Shutdown Methods," details operation of these features. Figure 38, directly derived from Figure 37, produces 10mA output to drive color LCDs at 92% efficiency. The

Figure 37. A 91% Efficient CCFL Supply for 5mA Loads Features Shutdown and Dimming Inputs. Higher Frequency Switching Regulator Reduces L1's Size While Requiring Less V<sub>IN</sub> Current

= 1% FILM RESISTOR

slight efficiency improvement comes from a reduction in regulator "housekeeping" current as a percentage of total current drain. Value changes in components are the result of higher power operation. The most significant change involves driving two lamps. Accommodating two lamps involves separate ballast capacitors but circuit operation is similar. Dual-lamp designs reflect slightly different loading back through the transformer's primary. C2 usu-

**Note 8**. Controlling a nonlinear load's current, instead of its voltage, permits applying this circuit technique to a wide variety of nominally evil loads. See Appendix I, "Additional Circuits."

**Note 9.** See "Illumination Circuity for Liquid Crystal Displays," Linear Technology Corporation, Application Note 49, August 1992 and "Techniques for 92% Efficient LCD Illumination," Linear Technology Corporation, Application Note 55, August 1993.

ally ends up in the 10pF to 47pF range. Note that C2A and B appear with their lamp loads in parallel across the transformer's secondary. As such, C2's value is often smaller than in a single-lamp circuit using the same type lamp. Ideally, the transformer's secondary current splits evenly between the C2-lamp branches, with the total load current being regulated. In practice, differences between C2A and B, and differences in lamps and lamp wiring layout preclude a perfect current split. Practically, these differences are small and the lamps appear to emit an equal amount of light at high intensity. Layout and lamp matching can influence C2's value. Some techniques for dealing with these issues appear in the text section, "Considerations for Multilamp Designs." As previously stated, dual-lamp designs are distinctly not recommended, particularly if balanced illumination over wide dimming ranges is required.

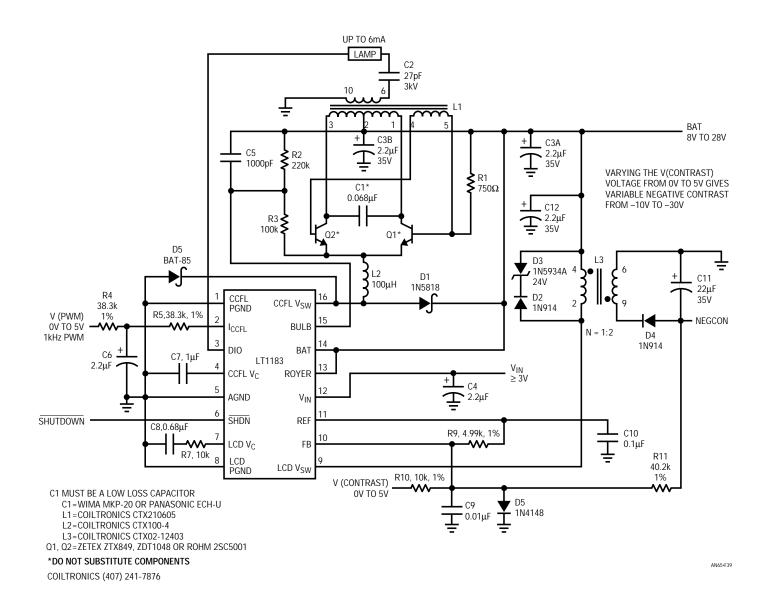

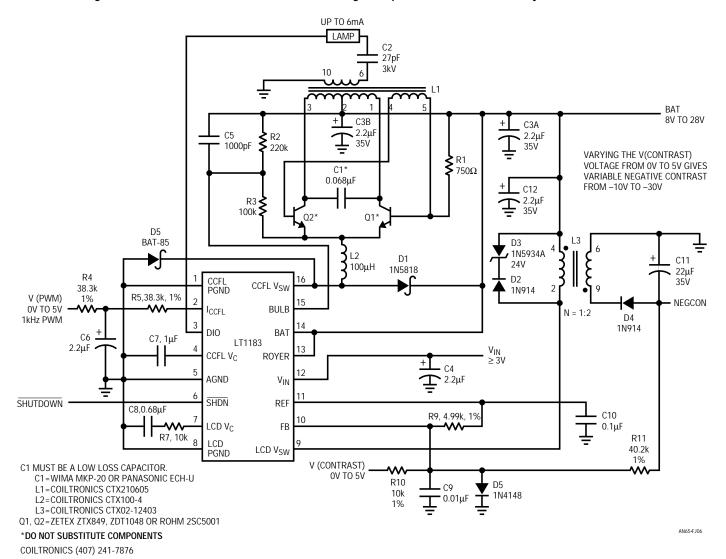

Figure 39 uses a dedicated CCFL IC, the LT1183, to enhance circuit performance. The Royer-based high voltage converter portion is recognizable from previous circuits, with the 200kHz LT1183 performing the switching regulator/feedback function. This IC also features open lamp protection circuitry, simplified frequency compensation, a separate regulator providing LCD contrast and other features. The contrast supply is driven by the LT1183 with L3 and associated discrete components completing the function. The CCFL and contrast outputs may be adjusted with DC, PWM or potentiometers.

**Note 10**. Open lamp protection is often desirable and may be added to the previous circuits at the cost of some discrete components. See Appendix E, "Open Lamp/Overload Protection." Frequency compensation issues are covered in the text section "Feedback Loop Stability Issues." See Appendix J for discussion of LCD contrast supplies.

Figure 38. A 92% Efficient CCFL Supply for 10mA Loads Features Shutdown and Dimming Inputs. Dual-Lamp Designs, Typical of Early Color Displays, Are Not Recommended

Figure 39. Dedicated Backlight IC Includes Switching Regulator, Open Lamp Protection and LCD Contrast Supply. 200kHz Operation Minimizes L2 Size. Shutdown and Control Inputs Are Simplified

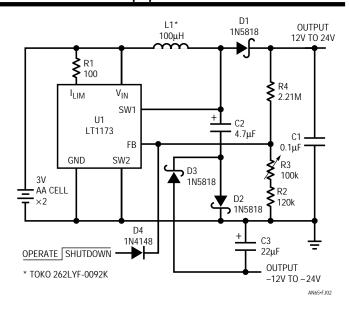

#### Low Power CCFL Power Supplies

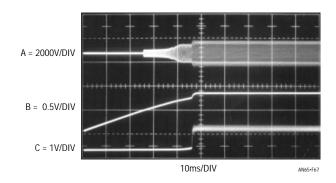

Many applications require relatively low power CCFL back-lighting. Figure 40's variation, optimized for low voltage inputs, produces 4mA output. Circuit operation is similar to the previous examples. The fundamental difference is L1's higher turns ratio, which accommodates the reduced available drive voltage. The circuit values given are typical, although some variation occurs with various lamps and layouts.

Figure 41's design, the so-called "dim backlight," is optimized for very low current lamp operation. The circuit is meant for use at low input voltages, typically 2V to 6V with a 1mA maximum lamp current. This circuit maintains control down to lamp currents of  $1\mu A$ , a very dim light! It is intended for applications where the longest possible

D1 1N4148 10μF C1 0.1uF Q1 Q2 D2 1N4148 **≤**560Ω 1N5818 +V<sub>IN</sub> 3.6V TO 5.5V 700Ω\*≶ 12 50μΗ  $V_{IN}$ 10k 20k F1  $V_{SW}$ INTENSITY ADJUS1 LT1172 E2  $V_{FB}$ GND  $V_C$  $0.1 \mu F$ C1 = MUST BF A LOW LOSS CAPACITOR. MFTALIZED POLYCARB WIMA MKP-20 (GERMAN) OR PANASONIC ECH-U RECOMMENDED L1 = COILTRONICS CTX110654-1 L2 = COILTRONICS CTX50-4 Q1, Q2 = ZETEX ZTX849, ZDT1048 OR ROHM 2SC5001 = 1% FILM RESISTOR DO NOT SUBSTITUTE COMPONENTS

Figure 40. A 4mA Design Intended for Low Voltage Operation. L1's Modified Turns Ratio Allows Operation Down to 3.6V

battery life is desired. Primary supply drain ranges from hundreds of microamperes to 100mA with lamp currents of microamps to 1mA. In shutdown the circuit pulls only 100µA. Maintaining high efficiency at low lamp currents requires modifying the basic design.

Achieving high efficiency at low operating current requires lowering quiescent power drain. To do this the previously employed pulse width modulator-based devices are replaced with an LT1173. The LT1173 is a Burst Mode operation regulator. When this device's Feedback pin is too low it delivers a burst of output current pulses, putting energy into the transformer and restoring the feedback point. The regulator maintains control by appropriately modulating the burst duty cycle. The ground referred diode at the  $V_{SW}$  pin prevents substrate turn-on due to excessive L2 ring-off.

Burst Mode is a trademark of Linear Technology Corporation.

Figure 41. Low Power CCFL Power Supply. Circuit Controls Lamp Current over a  $1\mu A$  to 1mA Range

COILTRONICS (407) 241-7876, SUMIDA (708) 956-0666

During the off periods the regulator is essentially shut down. This type of operation limits available output power, but cuts quiescent current losses. In contrast, the other circuit's pulse width modulator type regulators maintain "housekeeping" current between cycles. This results in more available output power but higher quiescent currents.

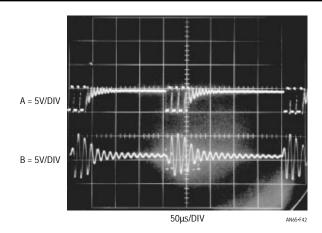

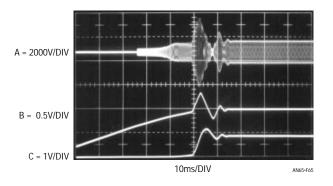

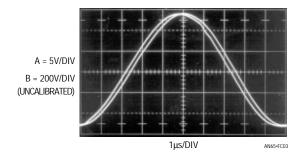

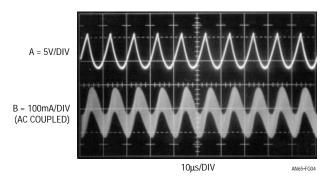

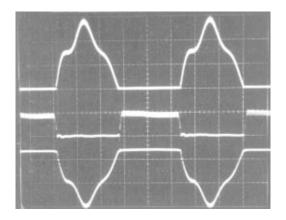

Figure 42 shows operating waveforms. When the regulator comes on (Trace A, Figure 42) it delivers bursts of output current to the L1/Q1/Q2 high voltage converter. The converter responds with bursts of ringing at its resonant frequency. <sup>11</sup> The circuit's loop operation is similar to the previous designs except that T1's drive waveform varies with supply. Because of this, line regulation suffers and the circuit is not recommended for wide ranging inputs.

Some lamps may display nonuniform light emission at very low excitation currents. See the text section, "Floating Lamp Circuits."

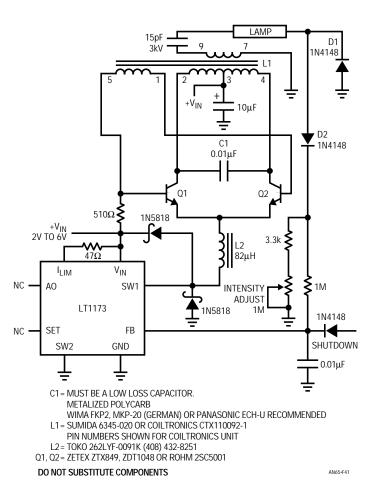

A CCFL power supply that addresses the previous circuit's line regulation problems and operates from 2V to 6V is detailed in Figure 43. This circuit, contributed by Steve Pietkiewicz of LTC, can drive a small CCFL over a 100µA to 2mA range.

Figure 42. Waveforms for the Low Power CCFL Power Supply. LT1173 Burst Type Regulator (Trace A) Periodically Excites the Resonant High Voltage Converter (Q1 Collector Is Trace B)

Note 11. The discontinous energy delivery to the loop causes substantial jitter in the burst repetition rate, although the high voltage section maintains resonance. Unfortunately, circuit operation is in the "chop" mode region of most oscilloscopes, precluding a detailed display. "Alternate" mode operation causes waveform phasing errors, producing an inaccurate display. As such, waveform observation requires special techniques. Figure 42 was taken with a dual-beam instrument (Tektronix 556) with both beams slaved to one time base. Single sweep triggering eliminated jitter artifacts. Most oscilloscopes, whether analog or digital, will have trouble reproducing this display.

Figure 43. Low Power Cold Cathode Fluorescent Lamp Supply Is Optimized for Low Voltage Inputs and Small Lamps

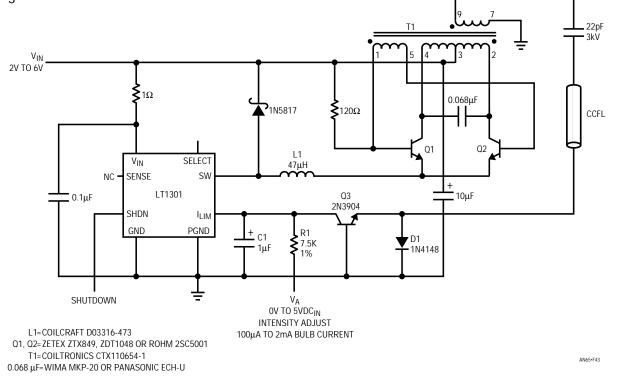

The circuit uses an LT1301 micropower DC/DC converter IC in conjunction with a current driven Royer class converter comprised of T1, Q1 and Q2. When power and intensity adjust voltage are applied, the LT1301's I<sub>LIM</sub> pin is driven slightly positive, causing maximum switching current through the IC's internal Switch pin (SW). Current flows from T1's center tap, through the transistors, into L1.L1's current is deposited in switched fashion to ground by the regulator's action.

Circuit efficiency ranges from 80% to 88% at full load, depending on line voltage. Current mode operation combined with the Royer's consistent waveshape vs input results in excellent line rejection. The circuit has none of the line rejection problems attributable to the hysteretic voltage control loops typically found in low voltage micropower DC/DC converters. This is an especially desirable characteristic for CCFL control, where lamp intensity must remain constant with shifts in line voltage.

The Royer converter oscillates at a frequency primarily set by T1's characteristics (including its load) and the 0.068µF capacitor. LT1301 driven L1 sets the magnitude of the Q1/Q2 tail current, hence T1's drive level. The 1N5817 diode maintains L1's current flow when the LT1301's switch is off. The 0.068µF capacitor combines with T1's characteristics to produce sine wave voltage drive at the Q1 and Q2 collectors. T1 furnishes voltage step-up and about 1400V<sub>P-P</sub> appears at its secondary. Alternating current flows through the 22pF capacitor into the lamp. On positive half-cycles the lamp's current is steered to ground via D1. On negative half-cycles the lamp's current flows through Q3's collector and is filtered by C1. The LT1301's I<sub>LIM</sub> pin acts as a OV summing point with about 25µA bias current flowing out of the pin into C1. The LT1301 regulates L1's current to equalize Q3's average collector current, representing 1/2 the lamp current, and R1's current, represented by V<sub>A</sub>/R1. C1 smooths all current flow to DC. When  $V_A$  is set to zero, the  $I_{LIM}$  pin's bias current forces about 100µA bulb current.

### **High Power CCFL Power Supply**

As mentioned, the CCFL circuit approach presented here scales quite nicely over a wide range of output power. Most circuits are in the 0.5W to 3W region due to the application's small size and battery-driven nature. Automotive, aircraft, desktop computer and other displays often require much higher power.

Figure 44's arrangement is a scaled-up version of the text's CCFL circuits. This design, similar to ones employed for automotive use, drives a 25W CCFL. There are virtually no configuration changes, although most component power ratings have increased. The transistors can handle the higher currents, but all other power components are higher capacity. Efficiency is about 80%.

Additional high power circuits appear in Appendix I, "Additional Circuits."

Figure 44. A 25W CCFL Supply Is a Scaled Version of Lower Power Circuits

COILTRONICS (407) 241-7876

AN65+F44

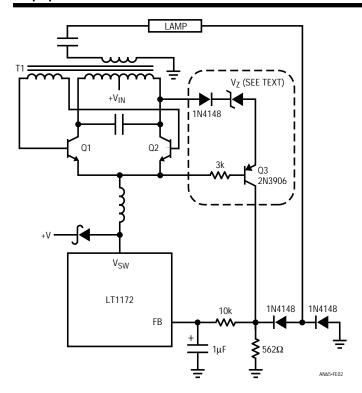

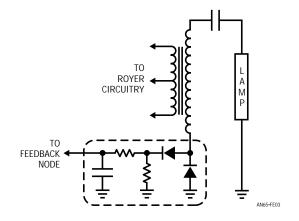

#### "Floating" Lamp Circuits

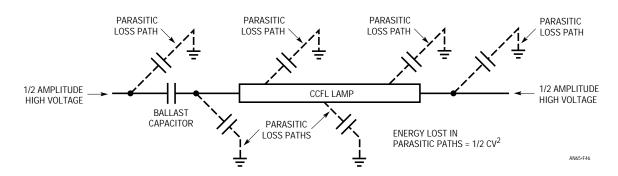

All circuits presented to this point drive the lamp in singleended fashion. Similarly, Figure 45 shows one lamp electrode receiving drive with the other terminal essentially at ground. This causes significant loss via parasitic paths associated with the lamp's driven end. This is so because of the large voltage swing in this region. The parasitic paths near the lamp's grounded end undergo relatively little swing, contributing small energy loss. Unfortunately, the lost energy is heavily voltage-dependent (E =  $1/2 \text{ CV}^2$ ) and net energy loss is excessive if driven end parasitics are large. Figure 46 minimizes the losses by altering the drive scheme. In this case the lamp is driven from both ends instead of grounding one end. This "floating" lamp arrangement requires only half the voltage swing at each lamp end instead of full swing at one end. This introduces more loss in the parasitic paths previously associated with the grounded end. In most cases these increased losses are favorably offset by the reduced swing because of the  $V^2$  loss term associated with voltage amplitude.

The advantage gained varies considerably with display type, although a 10% to 20% reduction in lost energy is common. In some displays loss reduction is not as good, and occasionally improvement is negligible. Heavily asymmetric wiring to or within the display can sometimes make floating drive more lossy than grounded drive. In such cases testing in both modes is necessary to determine which type drive is most efficient.

A second advantage of floating operation is extended illumination range. "Grounded" lamps operating at relatively low currents may display the "thermometer effect," that is, light intensity may be nonuniformly distributed along lamp length.

Figure 45. Ground Referred Lamp Drive Has Large Energy Loss in High Voltage Regions Due to Full Amplitude Swing

Figure 46. "Floating" Lamp Allows Reduced, Bipolar Drive, Cutting Losses Due to Parasitic Capacitance Paths. Formerly Grounded Lamp End's Paths Absorb More Energy Than Before, but Overall Loss Is Lower Due to Equation's V<sup>2</sup> Term

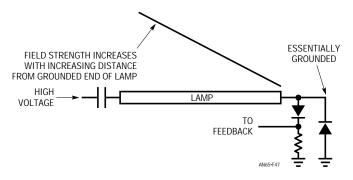

Figure 47 shows that although lamp current density is uniform, the associated field is imbalanced. The field's low intensity, combined with its imbalance, means that there is not enough energy to maintain uniform phosphor glow beyond some point. Lamps displaying the thermometer effect emit most of their light near the driven electrode, with rapid emission fall-off as distance from the electrode

Figure 47. Field Strength vs Distance for a Ground Referred Lamp. Field Imbalance Promotes Uneven Illumination at Low Drive Levels

increases. Placing a conductor along the lamp's length largely alleviates "thermometering." The trade-off is decreased efficiency due to energy leakage. <sup>12</sup> It is worth noting that various lamp types have different degrees of susceptibility to the thermometer effect.

Some displays require extended illumination range. "Thermometering" usually limits the lowest practical illumination level. One acceptable way to minimize "thermometering" is to eliminate the large field imbalance. The floating drive used to reduce energy loss also provides a way to minimize "thermometering." Figure 48 reviews a

Note 12. A very simple experiment quite nicely demonstrates the effects of energy leakage. Grasping the lamp at its low voltage end (low field intensity) with thumb and forefinger produces almost no change in circuit input current. Sliding the thumb/forefinger combination towards the high voltage (higher field intensity) lamp end produces progressively greater input currents. Don't touch the high voltage lead or you may receive an electrical shock. Repeat: Do not touch the high voltage lead or you may receive an electrical shock.

Figure 48. Practical "Floating" Lamp Drive Circuit. A1 Senses Royer Input Current with Q3 Providing Resultant Feedback Information to Switching Regulator. Circuit Reduces Lost Energy Due to Parasitics by 10% to 20%

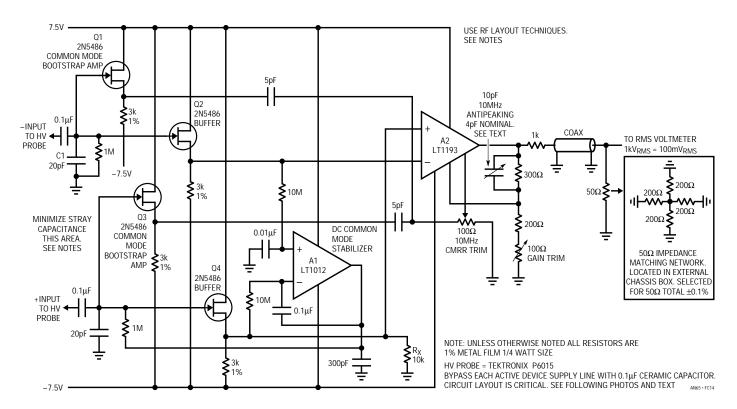

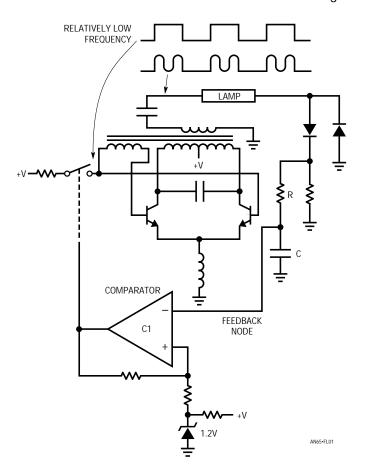

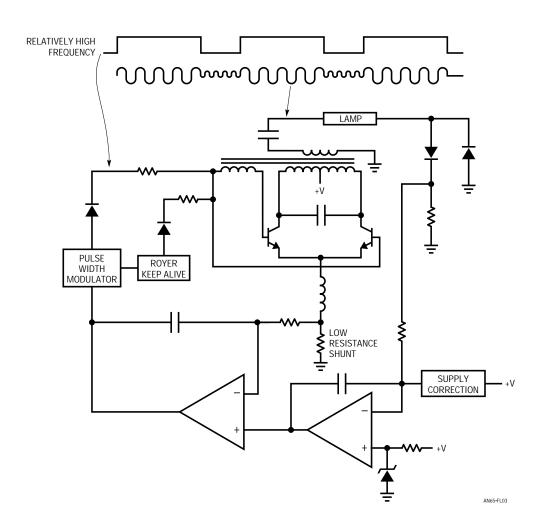

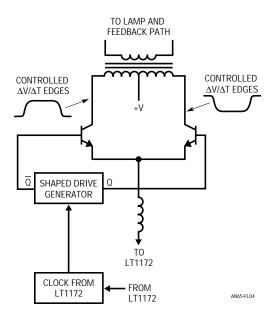

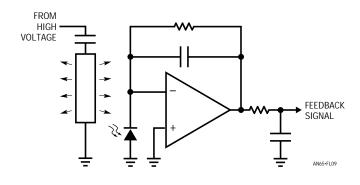

circuit originally introduced in a previous publication. The circuit's most significant aspect is that the lamp is fully floating—there is no galvanic connection to ground as in the previous designs. This allows T1 to deliver symmetric, differential drive to the lamp. Such balanced drive eliminates field imbalance, reducing thermometering at low lamp currents. This approach precludes any feedback connection to the now floating output. Maintaining closed-loop control necessitates deriving a feedback signal from some other point. In theory, lamp current proportions to T1's or L1's drive level and some form of sensing this can be used to provide feedback. In practice, parasitics make a practical implementation difficult. 14

Figure 48 derives the feedback signal by measuring Royer converter current and feeding this information back to the LT1172. The Royer's drive requirement closely proportions to lamp current under all conditions. A1 senses this current across the  $0.1\Omega$  shunt and biases Q3, closing a

local feedback loop. Q3's drain voltage presents an amplified, single-ended version of the shunt voltage to the feedback point, closing the main loop. A1's power supply pin is bootstrapped to T1's boosted swing via the BAT-85 diode, permitting it to sense across the supply-fed shunt resistor. Internal A1 characteristics ensure start-up and substitution of this device is not recommended. 15

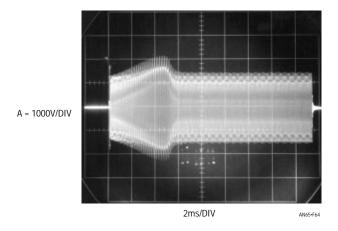

The lamp current is not as tightly controlled as before but 0.5% regulation over wide supply ranges is possible. The dimming in this circuit is controlled by a 1kHz PWM signal. Note the heavy filtering (33k/1 $\mu$ F) *outside* the feedback loop. This allows a fast time constant, minimizing turn-on overshoot. <sup>16</sup>

Note 13. See Reference 1.

**Note 14**. See Appendix L, "A Lot of Cut Off Ears and No Van Goghs—Some Not-So-Great Ideas," for details.

Note 15. See Reference 1, then don't say we didn't warn you.

Note 16. See text section, "Feedback Loop Stability Issues."

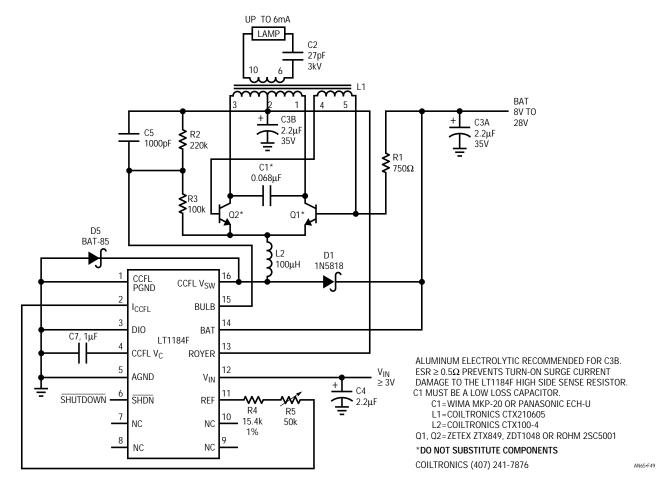

Figure 49. LT1184F IC Version of Figure 48's Floating Lamp Circuit Offers Similar Performance with Fewer Components. Open Bulb Protection and Shutdown Are Included

In all other respects operation is similar to the previous circuits. This circuit typically permits the lamp to operate with less energy loss and over a 40:1 intensity range without "thermometering." The normal feedback connection is usually limited to a 10:1 range.

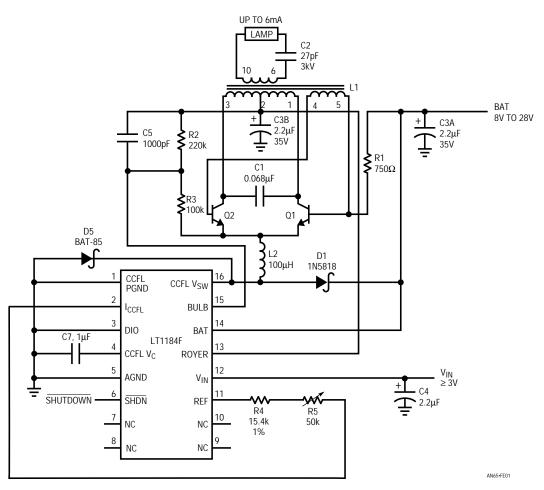

#### **IC-Based Floating Drive Circuits**

Figure 49 compacts Figure 48 into a low component count, floating drive circuit. The LT1184F IC contains all func-

tions except the Royer-based high voltage converter. The circuit also has "open lamp" protection and a 1.23V reference for biasing the dimming potentiometer.

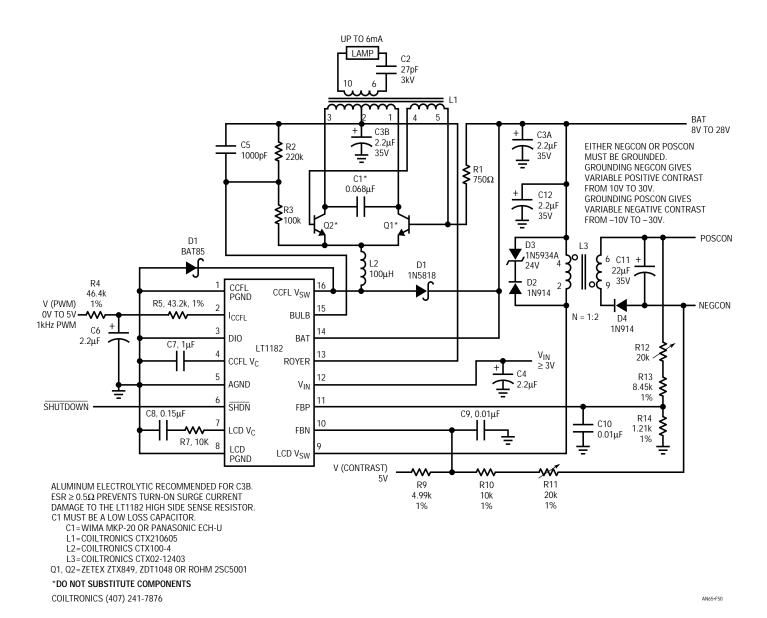

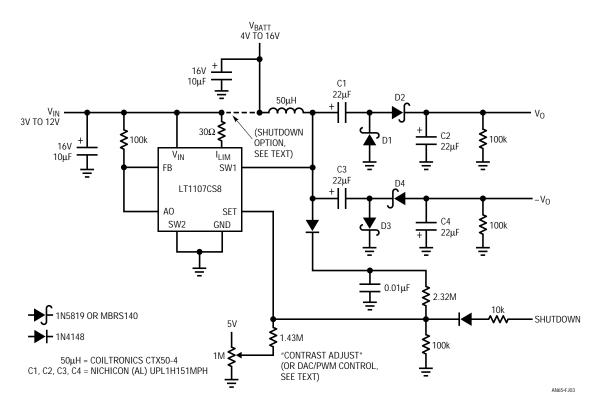

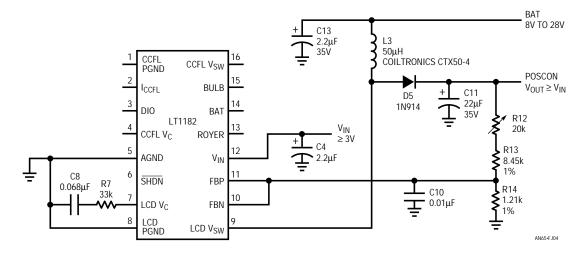

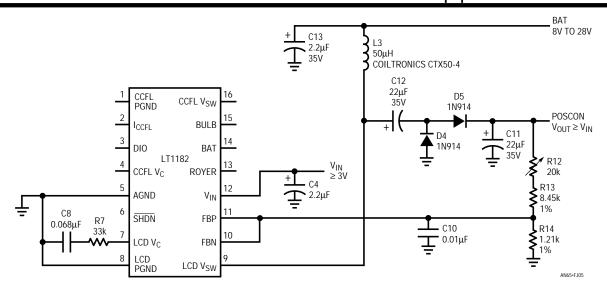

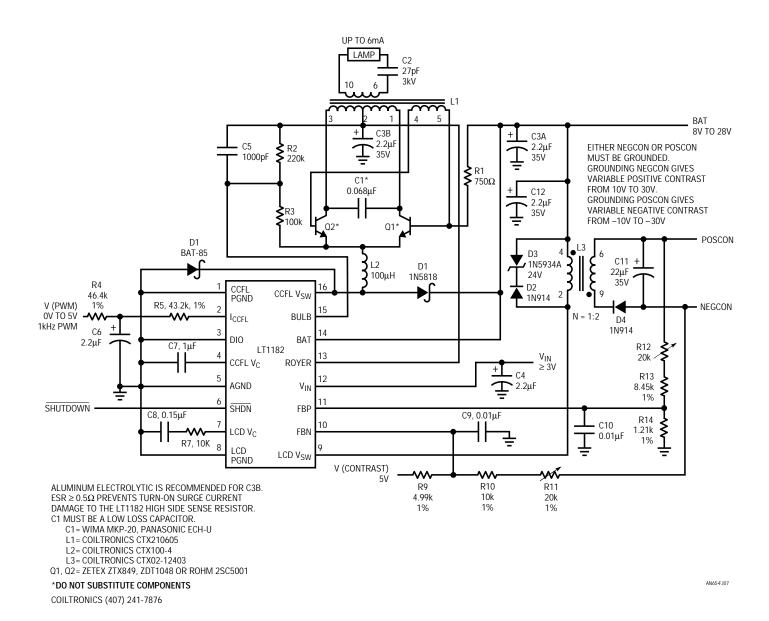

Figure 50 adds a bipolar LCD contrast supply output to Figure 49. The LT1182 allows setting contrast supply polarity by simply grounding the appropriate output terminal. The CCFL portion is similar to the previous circuit, although intensity is controlled with a varying PWM or 0V to 5V input.

Figure 50. LT1182 Has Bipolar Output Contrast Supply in Addition to Floating Lamp Drive

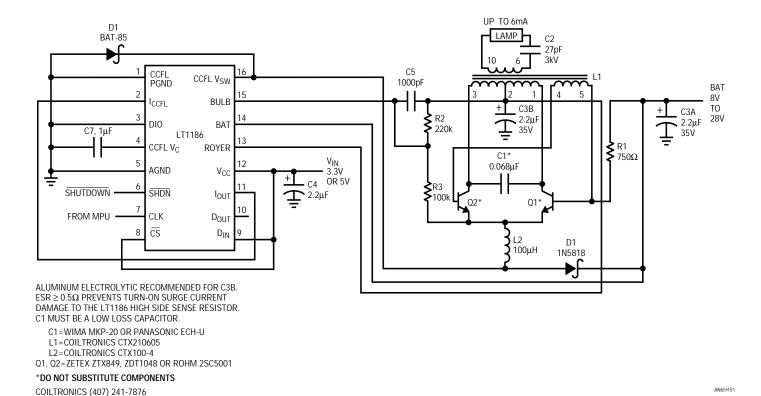

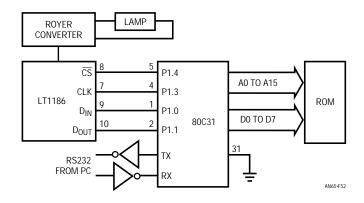

Figure 51's circuit is similar, although no contrast supply is included. The LT1186 implements a floating lamp drive similar to Figure 49. This IC contains an internal D/A converter which may be addressed by accumulating a bit

stream or serial protocol. Figure 52 shows a typical arrangement using an 80C31 type microcontroller. Figure 53 gives the complete software listing which was written by Tommy Wu of LTC.

Figure 51. LT1186 Permits Serial or Bit Stream Data Addressing to Set Floating Lamp Current

Figure 52. Typical Processor Interface for Figure 51

The LT1186 DAC algorithm is written in assembly code in a file named LT1186A.ASM as a function call from the MAIN fuction below.

Note: A user inputs an integer from 0 to 255 on a keyboard and the LT1186 adjusts the IOUT programming current to control the operating lamp current and the brightness of the LCD display.

```

#include <stdio.h>

#include <reg51.h>

#include <absacc.h>

extern char lt1186(char); /* external assembly function in lt1186a.asm*/

sbit Clock = 0x93;

main()

{

int number = 0:

int LstCode;

Clock = 0;

TMOD = 0x20; /* Establish serial communication 1200 baud */

TH1 = 0xE8:

SCON = 0x52;

TCON = 0x69;

while(1) /* Endless loop */

printf("\nEnter any code from 0 - 255:");

scanf("%d",&number);

if((0>number)|(number>255))

number = 0;

printf("The number exceeds its range. Try again!");

else

LstCode = lt1186(number);

printf("Previous # %u".(LstCode&0xFF)); /* AND the previous number with 0xFF to turn off sign

extension */

number = 0;

}

}

; The following assembly program named LT1186A.ASM receives the Din word from the main C program,

; It1186 It1186(). Assembly to C interface headers, declarations and memory allocations are listed before the

; actual assembly code.

; Port p1.4 = CS

Port p1.3 = CLK

Port p1.1 = Dout

; Port p1.0 = Din

```

Figure 53. Complete Software Listing for Figure 52's Processor Interface

```

NAME LT1186 CCFL

PUBLIC It1186, ?lt1186?BYTE

?PR?ADC_INTERFACE?LT1186_CCFL SEGMENT CODE

?DT?ADC_INTERFACE?LT1186_CCFL SEGMENT DATA

RSEG ?DT?ADC_INTERFACE?LT1186_CCFL

?lt1186?BYTE: DS 2

RSEG ?PR?ADC_INTERFACE?LT1186_CCFL

CS

EQU p1.4

CLK

EQU p1.3

DOUT EQU

p1.1

EQU P1.0

DIN

lt1186: setb

CS

;set CS high to initialize the LT1186

r7,?lt1186?BYTE

mov

;move input number(Din) from keyboard to R7

p1, #01h

;setup port p1.0 becomes input

mov

CS

clr

;CS goes low, enable the DAC

mov

a, r7

move the Din to accumulator

;load counter 8 counts

r4, #08h

mov

clr

;clear carry before rotating

С

;rotate left Din bit(MSB) into carry

rlc

а

loop:

mov

DIN, c

;move carry bit to Din port

setb

CLK

;Clk goes high for LT1186 to latch Din bit

c, DOUT

read Dout bit into carry

mov

rotate left Dout bit into accumulator

rlc

clr

CLK

:clear clock to shift the next Dout bit

djnz

r4, loop

;next data bit loop

mov

r7, a

;move previous code to R7 as character return

CS

;bring CS high to disable DAC

setb

ret

END

Note: When CS goes low, the MSB of the previous code appears at Dout.

```

Figure 53 (continued). Complete Software Listing for Figure 52's Processor Interface

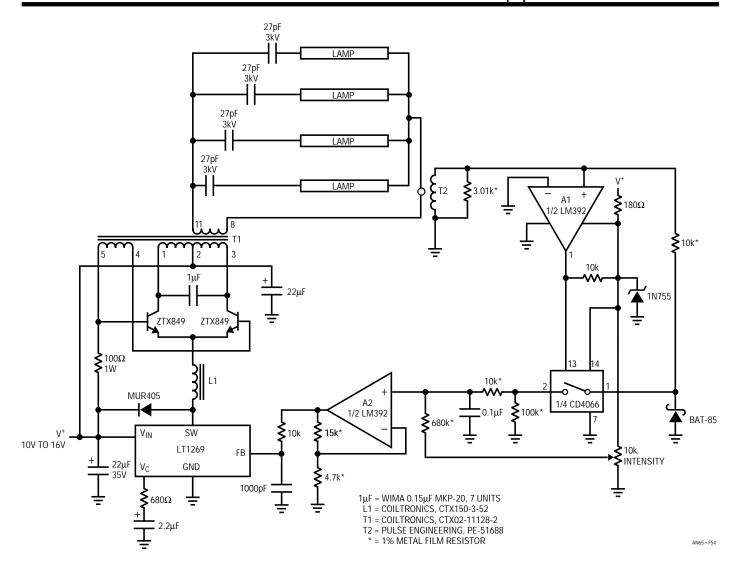

### **High Power Floating Lamp Circuit**

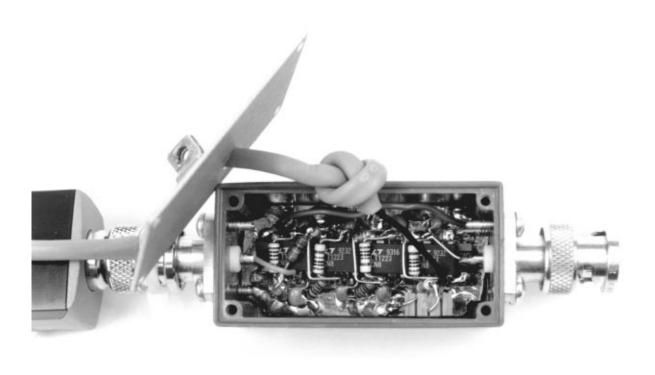

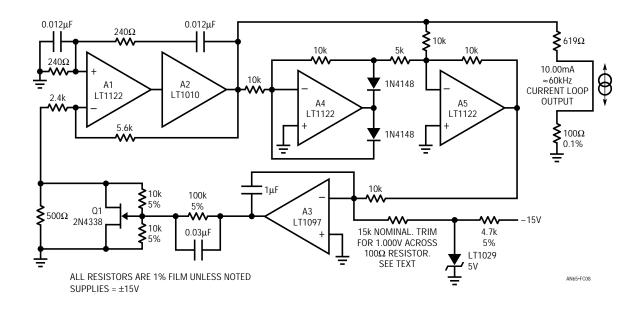

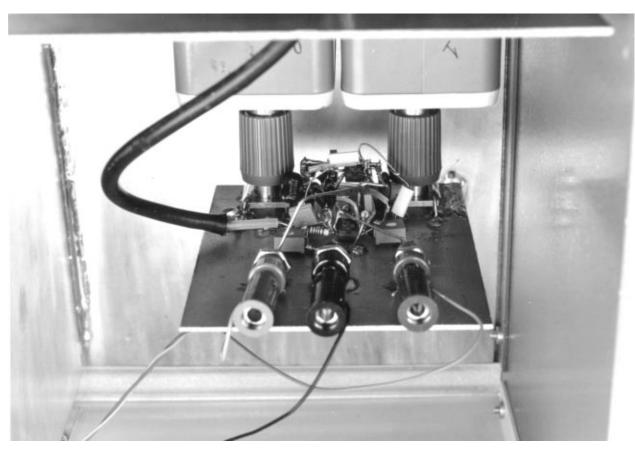

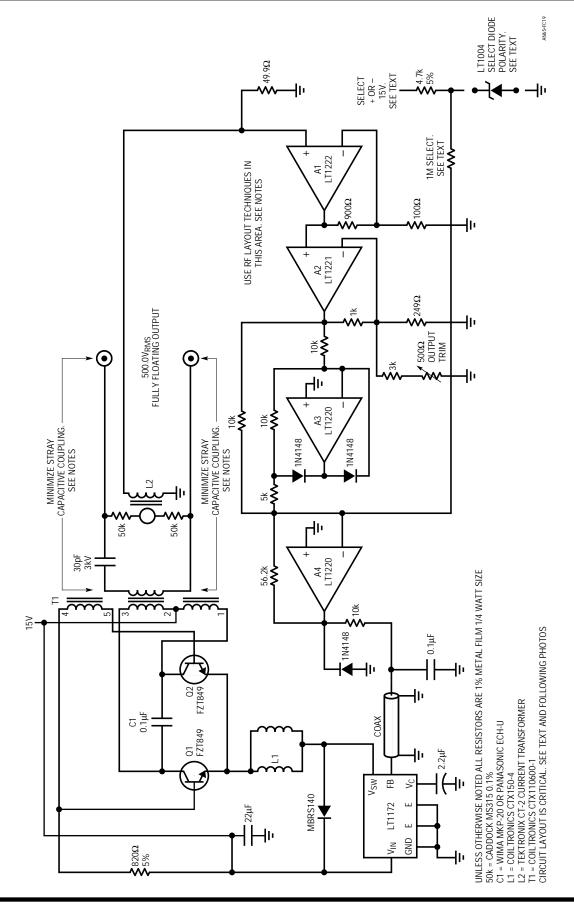

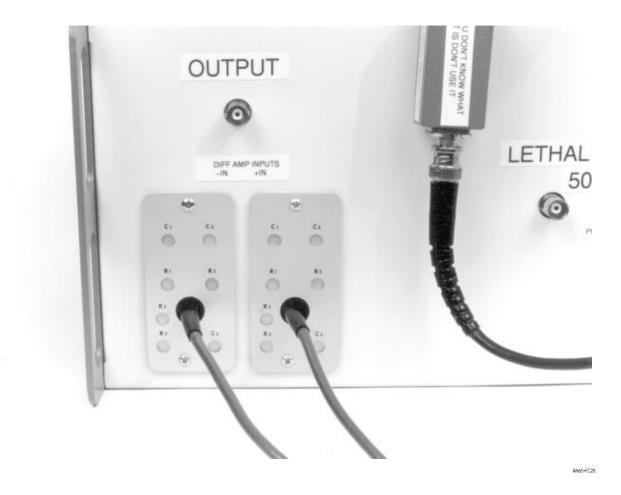

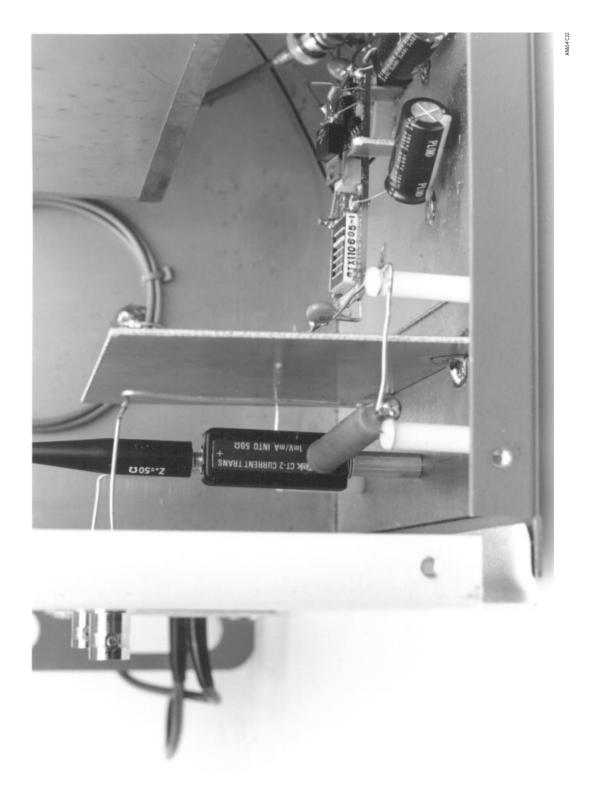

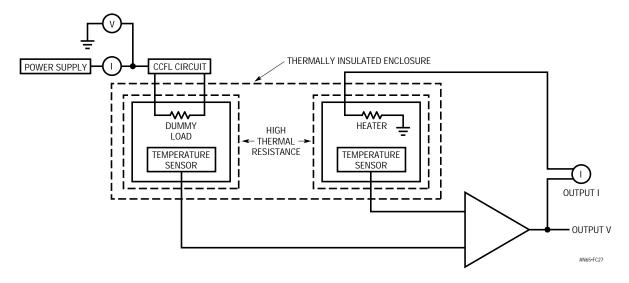

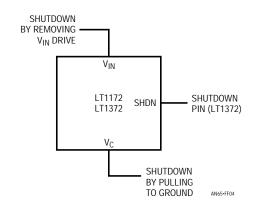

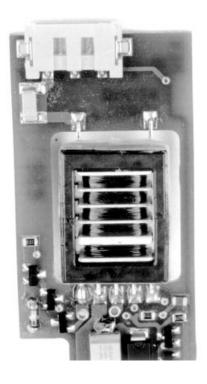

High power floating lamp circuits require more current than the LT118X series can deliver. In such cases the function can be built from discrete components and ICs. Figure 54 shows a 30W CCFL circuit used in an automotive application. This 4-lamp circuit uses an LT1269 current-fed Royer converter to provide high power. Lamp current is sensed in current transformer T2. A1 and associated components form a synchronous rectifier for T2's low level output. A2 provides gain and closes a loop back at the

LT1269's feedback terminal. T2's isolated sensing permits the advantages of floating operation with the LT1269 providing high power capability. This circuit has about 83% efficiency at 30W output, a wide dimming range and 0.1% line regulation.

#### **Selection Criteria for CCFL Circuits**

Selecting which CCFL circuit to use for a specific application involves numerous trade-offs. A variety of issues determine which circuit is the "best" approach. At a

Figure 54. A High Power, Multilamp Display Using the Floating Drive Approach. Power Requirement Necessitates LT1269 Regulator and Discrete Component Approach. Floating Feedback Path Is Via Current Transformer

minimum, the user should consider the following guidelines before committing to any approach. Related discussion to all of the following topics is covered in appropriate text sections.

# Display Characteristics

The display characteristics (including wiring losses) should be well-understood. Typically, display manufacturers list *lamp* requirements. These specifications are often obtained from the lamp vendor, who usually tests in free air, with no significant parasitic loss paths. This means that actual required power, start and running voltages may significantly differ from data sheet specifications. The only

way to be certain of display characteristics is to measure them. The measured display energy loss can determine if a floating or grounded circuit is applicable. Low loss displays (relatively rare) usually provide better overall efficiency with grounded drive. As losses become worse (unfortunately, relatively common) floating drive becomes a better choice. Efficiency measurements may be required in both modes to determine the best choice. (See "General Optimization and Measurement Considerations.")

### Operating Voltage Range

The operating voltage range includes the minimum to maximum voltages the circuit must operate from. In

battery-driven apparatus supply range can easily be 3:1, and sometimes greater. Best backlight performance is usually obtained in the 8V to 28V range. In general, potentials below 7V require some efficiency trade-offs at moderate (1.5W to 3W) power levels. Some systems reduce backlight power when running from the battery, and this can have a pronounced effect on the design. Even seemingly small (e.g., 20%) reductions in power may make painful trade-offs unnecessary. In particular, high turns ratio transformers are required to support low voltage operation at full lamp output. They work well but somewhat less efficiently than lower ratio types due to the higher peak currents characteristic of their operation. Current trends in battery technology encourage system operation at low voltages, necessitating extreme care in transformer selection and Royer circuit design.

### Auxiliary Operating Voltages

Auxiliary, logic supply voltages should be used (if available) to run CCFL "housekeeping" currents, such as IC "V<sub>IN</sub>" pins. This saves power. Always run switching regulators from the lowest potential available, usually 3.3V or 5V. Many systems provide these voltages in switched form, making separate shutdown lines unnecessary. Simply turning off the switching regulator's supply shuts the entire backlight circuit down.

# Line Regulation

Grounded lamp circuits, by virtue of their true global feedback, provide the best line regulation. For abrupt changes, a user may notice anything beyond 1% regulation. A grounded circuit easily meets this requirement; a floating circuit usually will. Slowly changing line inputs causing excursions outside 1% are not normally a problem because they are not detectable. Rapid line changes, such as plugging in a systems AC line adapter, require good regulation to avoid annoying display flicker.

# Power Requirements

The CCFL's power requirement, including display and wiring losses, should be well-defined over all conditions, including temperature and lamp specification variations. Usually, IC versions of floating lamp circuits are restricted to 3W to 4W output power while grounded circuit power is easily scaled.

### Supply Current Profile

The backlight is often physically located far "forward" in the system. Impedances in cables, switches, traces and connectors can build up to significant levels. This means that a CCFL circuit should draw operating power continuously, rather than requiring discrete, high current "chunks" from a lossy supply line. Royer-based architectures are nearly ideal in this regard, pulling current smoothly over time and requiring no special bypassing, supply impedance or layout treatment. Similarly, Royer type circuits do not cause significant disturbances to the supply line, preventing noise injection back into the supply.

#### Lamp Current Certainty

The ability to predict lamp current at full intensity is important to maintain lamp life. Excessive overcurrent greatly shortens lamp life, while yielding little luminosity benefit (see Figure 2). Grounded circuits are excellent in this category with 1% usually achieved. Floating circuits are typically in the 2% to 5% range. Tight current tolerances do not benefit unit/unit display luminosity because lamp emission and display attenuation variations approach  $\pm 20\%$  and vary over life.

### **Efficiency**

CCFL backlight efficiency should be considered from two perspectives. The electrical efficiency is the ability of the circuit to convert DC power to high voltage AC and deliver it to the load (lamp and parasitics) with minimum loss. The optical efficiency is perhaps more meaningful to the user. It is simply the ratio of display luminosity to DC power into the CCFL circuit. The electrical and optical losses are lumped together in this measurement to produce a luminosity vs power specification. It is quite significant that the electrical and optical peak efficiency operating points do not necessarily coincide. This is primarily due to the lamp's emissivity dependence on waveshape. The optimum waveshape for emissivity may or may not coincide with the circuit's electrical operating peak. In fact, it is quite possible for "inefficient" circuits to produce more light than "more efficient" versions. The only way to ensure peak efficiency in a given situation is to optimize the circuit to the display.

#### Shutdown

System shutdown almost always requires turning off the backlight. In many cases the low voltage supply is already available in switched form. If this is so, the CCFL circuits shown go off, absorbing very little power. If switched low voltage power is not available the shutdown inputs may be used, requiring an extra control line.

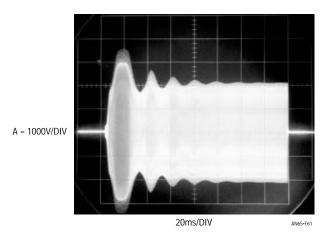

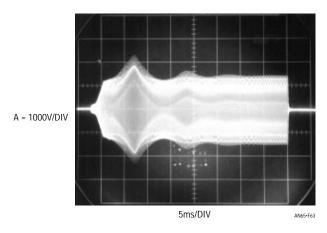

#### Transient Response

The CCFL circuit should turn on the lamp without attendant overshoot or poor control loop settling characteristics. This can cause objectionable display flicker, and in the worst case result in transformer overstress and failure. Properly prepared floating and grounded CCFL circuits have good transient response, with LT118X-based types inherently easier to optimize.

#### Dimming Control

The method of dimming should be considered early in the design. All of the circuits shown can be controlled by potentiometers, DC voltages and currents, pulse width modulation or serial data protocol. A dimming scheme with high accuracy at maximum current prevents excessive lamp drive and should be employed.

#### Open Lamp Protection

The CCFL circuits deliver a current source output. If the lamp is broken or disconnected, compliance voltage is limited by transformer turns ratio and DC input voltage. Excessive voltages can cause arcing and resultant damage. Typically, the transformers withstand this condition but open lamp protection ensures against failures. This feature is built into the LT118X series; it must be added to other circuits.

#### Size

Backlight circuits usually have severe size and component count limitations. The board must fit within tightly defined dimensions. LT118X series-based circuits offer lowest component count, although board space is usually dominated by the Royer transformer. In extremely tight spaces

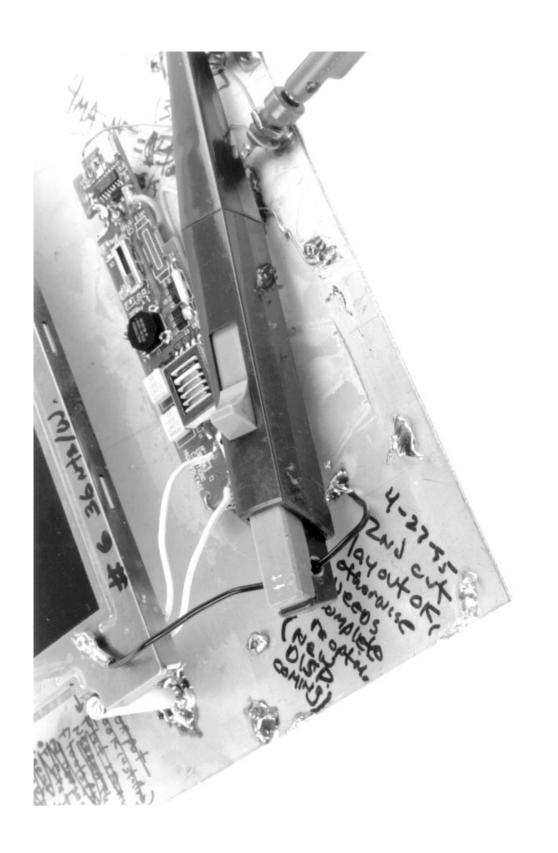

it may be necessary to physically segment the circuit but this should be considered as a last resort.<sup>17</sup>

### Contrast Supply Capability

Some LT118X parts provide contrast supply outputs. The other circuits do not. The LT118X's onboard contrast supply is usually an advantage but space is sometimes so restricted that it cannot be used. In such cases the contrast supply must be remotely located.

#### **Fmissions**

Backlight circuits rarely cause emission problems and shielding is usually not required. Higher power versions (e.g., > 5W) may require attention to meet emission requirements. The fast rise switching regulator output sometimes causes more RFI than the high voltage AC waveform. If shielding is used, its parasitic effects are part of the inverter load and optimization must be carried out with the shield in place.

#### **Summary of Circuits**

The interdependence of backlight parameters makes summarizing or rating various approaches a hazardous exercise. There is simply no intellectually responsible way to streamline the selection and design process if optimum results are desired. A meaningful choice *must* be the outcome of laboratory-based experimentation. There are just too many interdependent variables and surprises for a systematic, theoretically based selection. Pure analytics are pretty; working circuits come from the bench. Some generalizations having limited usefulness are, however, possible. Figures 55 and 56 attempt to summarize salient characteristics vs part type and may (however cautiously) be considered a beginning point. <sup>18</sup>

Figure 55 summarizes characteristics of all the circuits. Figure 56 focuses on the features of the LT118X series parts.

Note 17. See Appendix G, "Layout, Component and Emissions Considerations."

**Note 18.** Readers detecting author ambivalence about inclusion of Figures 55 and 56 are not hallucinating.

| ISSUES                                                                                           | LT118X SERIES                                                                                                           | LT117X SERIES                                                                        | LT137X SERIES                                                                         |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Optical Efficiency                                                                               | Grounded output versions display dependent. Floating versions usually 5% to 20% better.                                 | Display dependent                                                                    | Display dependent                                                                     |  |  |

| Electrical Efficiency                                                                            | Grounded output versions— 75% to 90%, depending on supply voltage and display. Floating output versions slightly lower. | 75% to 90%, depending on supply voltage and display                                  | 75% to 92%, depending on supply voltage and display                                   |  |  |

| Lamp Current Certainty                                                                           | 1% to 2% for grounded versions,<br>1% to 4% for floating output types                                                   | 2% maximum                                                                           | 2% maximum                                                                            |  |  |

| Line Regulation                                                                                  | oulation 0.1% to 0.3% for grounded types, 0.1% to 0.3% 0.5% to 6% for floating versions                                 |                                                                                      | 0.1% to 3%                                                                            |  |  |

| Operating Voltage Range 5.3V to 30V, depending on output power, temperature range, display, etc. |                                                                                                                         | 4.0V to 30V, depending on output power, temperature range, display etc.              | 4.0V to 30V, depending on output power, temperature range, display, etc.              |  |  |

| Power Range                                                                                      | 0.75W to 6W typical                                                                                                     | 0.75W to 20W typical                                                                 | 0.5W to 6W typical                                                                    |  |  |

| Supply Current Profile                                                                           | Continuous—no high current peaks                                                                                        | Continuous—no high current peaks                                                     | Continuous—no high current peaks                                                      |  |  |

| Shutdown Control                                                                                 | Yes—logic compatible                                                                                                    | Requires small FET or bipolar transistor                                             | Yes—logic compatible                                                                  |  |  |

| Transient Response<br>Overshoot                                                                  | Excellent—no optimization required                                                                                      | Excellent—requires optimization in some cases                                        | Excellent—requires optimization in some cases                                         |  |  |

| Dimming Control                                                                                  | ning Control Pot., PWM, variable DC voltage or current. LT1186 has serial or current digital input with data storage.   |                                                                                      | ge Pot., PWM, variable DC voltage<br>or current                                       |  |  |

| Emissions                                                                                        | ons Low Low                                                                                                             |                                                                                      | Low, although high power<br>versions may require attention to<br>layout and shielding |  |  |

| Open Lamp Protection                                                                             | Internal to IC                                                                                                          | Requires external small-signal transistor and some discretes at high supply voltages | Requires external small-signal transistor and some discretes at high supply voltages  |  |  |

| Size                                                                                             | Low component count, small overall board footprint. 200kHz magnetics.                                                   | Small—100kHz magnetics                                                               | Small—1MHz magnetics for fastest versions                                             |  |  |

| Contrast Supply Capability                                                                       | Various contrast supply options available, including bipolar output                                                     | No                                                                                   | No                                                                                    |  |  |

AN65•F55-1

Figure 55. Design Issues vs Typical Part Choice. Chart Makes Simplistic Assumptions and Is Intended As a Guide Only

| LT1269/LT1270                                                                        | LT1301                                                                                                                    | LT1173                                                                               |  |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Display dependent                                                                    | Display dependent                                                                                                         | Display dependent                                                                    |  |  |