Data Sheet June 23, 2006 FN6301.0

### Dual Precision Micropower Single Supply Rail-to-Rail Input and Output Precision Op-Amps

The ISL28276 is a dual channel micropower precision operational amplifier optimized for single supply operation at 5V and can operate down to 2.4V. For equivalent performance in a single channel op-amp reference EL8176.

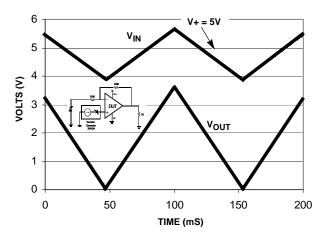

The ISL28276 features an Input Range Enhancement Circuit (IREC) which enables the ISL28276 to maintain CMRR performance for input voltages greater than the positive supply. The input signal is capable of swinging 0.5V above a 5.0V supply (0.25V for a 2.4V supply) and to within 10mV from ground. The output operation is rail to rail.

The ISL28276 draws minimal supply current while meeting excellent DC-accuracy, AC-performance, noise and output drive specifications. Offset current, voltage and current noise, slew rate, and gain-bandwidth product are all two to ten times better than other micropower op-amps with equivalent supply current ratings.

The ISL28276 can be operated from one lithium cell or two Ni-Cd batteries. The input range includes both positive and negative rail.

# **Ordering Information**

| PART NUMBER                  | PART<br>MARKING | TAPE & REEL | PACKAGE                 | PKG.<br>DWG.# |

|------------------------------|-----------------|-------------|-------------------------|---------------|

| ISL28276IAZ<br>(See Note)    | 28276IAZ        | -           | 16 Ld QSOP<br>(Pb-free) | MDP0040       |

| ISL28276IAZ-T7<br>(See Note) | 28276IAZ        | 7"          | 16 Ld QSOP<br>(Pb-free) | MDP0040       |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

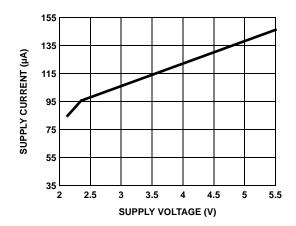

- 120µA supply current for both channels

- 100µV max offset voltage

- 500pA input bias current

- · 400kHz gain-bandwidth product

- 115dB PSRR and CMRR

- Single supply operation down to 2.4V

- Input is capable of swinging above V+ and within 10mV of Ground

- · Rail-to-rail output

- · Output sources 31mA load current

- · Pb-free plus anneal available (RoHS compliant)

#### **Applications**

- · Battery- or solar-powered systems

- · 4mA to 25mA current loops

- · Handheld consumer products

- · Medical devices

- · Thermocouple amplifiers

- Photodiode pre-amps

- · pH probe amplifiers

#### **Pinouts**

(16 LD QSOP)

TOP VIEW

NC 1 16 NC

NC 2 15 V+

OUT\_A 3 14 OUT\_B

IN-\_A 4 13 IN-\_B

IN+\_A 5 12 IN+\_B

EN\_A 6 11 EN\_B

V- 7 10 NC

NC 8 9 NC

ISL28276

#### **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| Supply Voltage                                 | Output Short-Circuit Duration                     |

|------------------------------------------------|---------------------------------------------------|

| Differential Input Current 5mA                 | Ambient Operating Temperature Range40°C to +125°C |

| Differential Input Voltage                     | Storage Temperature Range65°C to +150°C           |

| Input Voltage $V_{-}$ - 0.5V to $V_{+}$ + 0.5V | Operating Junction Temperature+125°C              |

| ESD tolerance, Human Body Model                |                                                   |

| ESD tolerance Machine Model 300V               |                                                   |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# Electrical Specifications $V_+ = 5V$ , 0V, $V_{CM} = 0.1V$ , $V_O = 1.4V$ , $T_A = 25$ °C unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C

| PARAMETER                           | DESCRIPTION                              | CONDITIONS                                        | MIN                   | TYP   | MAX                 | UNIT             |

|-------------------------------------|------------------------------------------|---------------------------------------------------|-----------------------|-------|---------------------|------------------|

| Vos                                 | Input Offset Voltage                     |                                                   | -100<br><b>-150</b>   | 20    | 100<br><b>150</b>   | μV               |

| $\frac{\Delta V_{OS}}{\Delta Time}$ | Long Term Input Offset Voltage Stability |                                                   |                       | 1.2   |                     | μV/Mo            |

| $\frac{\Delta V_{OS}}{\Delta T}$    | Input Offset Drift vs Temperature        |                                                   |                       | 0.3   |                     | μV/°C            |

| I <sub>OS</sub>                     | Input Offset Current                     |                                                   |                       | 0.25  | 1.3<br><b>2.0</b>   | nA               |

| IB                                  | Input Bias Current                       |                                                   | -2<br>- <b>2.5</b>    | 0.5   | 2<br><b>2.5</b>     | nA               |

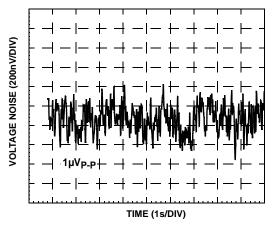

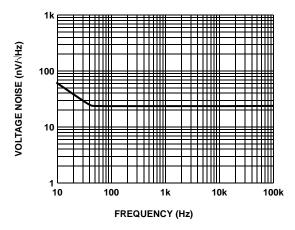

| e <sub>N</sub>                      | Input Noise Voltage Peak-to-Peak         | f = 0.1Hz to 10Hz                                 |                       | 1     |                     | μV <sub>PP</sub> |

|                                     | Input Noise Voltage Density              | f <sub>O</sub> = 1kHz                             |                       | 25    |                     | nV <b>/</b> √Hz  |

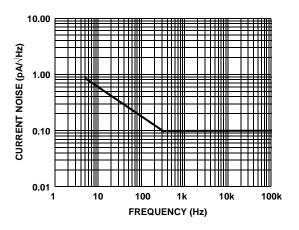

| i <sub>N</sub>                      | Input Noise Current Density              | f <sub>O</sub> = 1kHz                             |                       | 0.1   |                     | pA/√Hz           |

| CMIR                                | Input Voltage Range                      | Guaranteed by CMRR test                           | 0                     |       | 5                   | V                |

| CMRR                                | Common-Mode Rejection Ratio              | V <sub>CM</sub> = 0V to 5V                        | 90<br><b>80</b>       | 115   |                     | dB               |

| PSRR                                | Power Supply Rejection Ratio             | V <sub>+</sub> = 2.4V to 5V                       | 90<br><b>80</b>       | 115   |                     | dB               |

| Avol                                | Large Signal Voltage Gain                | $V_O = 0.5V$ to 4.5V, $R_L = 100k\Omega$          | 350<br><b>350</b>     | 550   |                     | V/mV             |

|                                     |                                          | $V_{O} = 0.5V \text{ to } 4.5V, R_{L} = 1k\Omega$ |                       | 25    |                     | V/mV             |

| Vouт                                | Maximum Output Voltage Swing             | Output low, $R_L = 100k\Omega$                    |                       | 3     | 6<br><b>30</b>      | mV               |

|                                     |                                          | Output low, $R_L = 1k\Omega$                      |                       | 130   | 175<br><b>225</b>   | mV               |

|                                     |                                          | Output high, $R_L = 100k\Omega$                   | 4.990<br><b>4.97</b>  | 4.996 |                     | V                |

|                                     |                                          | Output high, $R_L = 1k\Omega$                     | 4.800<br><b>4.750</b> | 4.880 |                     | V                |

| SR+                                 | Positive Slew Rate                       |                                                   | 0.13<br><b>0.10</b>   | 0.17  | 0.20<br><b>0.25</b> | V/µs             |

| SR-                                 | Negative Slew Rate                       |                                                   | 0.10<br><b>0.09</b>   | 0.13  | 0.17<br><b>0.19</b> | V/µs             |

| GBW                                 | Gain Bandwidth Product                   |                                                   |                       | 400   |                     | kHz              |

| PARAMETER          | DESCRIPTION                       | CONDITIONS             | MIN             | TYP | MAX               | UNIT |

|--------------------|-----------------------------------|------------------------|-----------------|-----|-------------------|------|

| I <sub>S,ON</sub>  | Supply Current, Enabled           | All channels enabled.  |                 | 120 | 156<br><b>175</b> | μA   |

| I <sub>S,OFF</sub> | Supply Current, Disabled          | All channels disabled. |                 | 4   | 7<br><b>9</b>     | μA   |

| I <sub>SC</sub> +  | Short Circuit Sourcing Capability | $R_L = 10\Omega$       | 29<br><b>23</b> | 31  |                   | mA   |

| I <sub>SC</sub> -  | Short Circuit Sinking Capability  | $R_L = 10\Omega$       | 24<br><b>19</b> | 26  |                   | mA   |

| Vs                 | Minimum Supply Voltage            |                        | 2.4             |     |                   | V    |

| V <sub>INH</sub>   | Enable Pin High Level             |                        |                 |     | 2                 | V    |

| V <sub>INL</sub>   | Enable Pin Low Level              |                        | 0.8             |     |                   | V    |

| I <sub>ENH</sub>   | Enable Pin Input Current          | V <sub>EN</sub> = 5V   |                 | 0.7 | 1.3<br><b>1.5</b> | μA   |

| I <sub>ENL</sub>   | Enable Pin Input Current          | V <sub>EN</sub> = 0V   | -0.1            | 0   | +0.1              | μA   |

### **Typical Performance Curves**

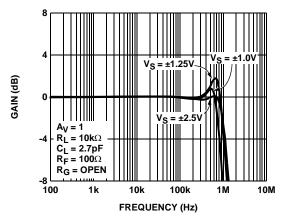

FIGURE 1. FREQUENCY RESPONSE vs SUPPLY VOLTAGE

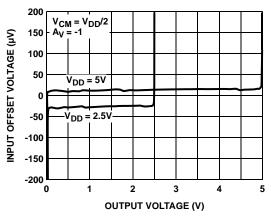

FIGURE 3. INPUT OFFSET VOLTAGE vs OUTPUT VOLTAGE

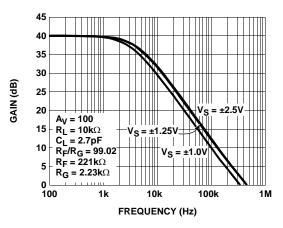

FIGURE 2. FREQUENCY RESPONSE vs SUPPLY VOLTAGE

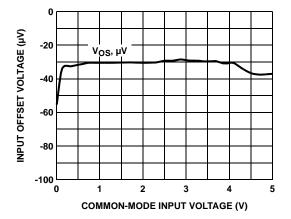

FIGURE 4. INPUT OFFSET VOLTAGE vs COMMON-MODE INPUT VOLTAGE

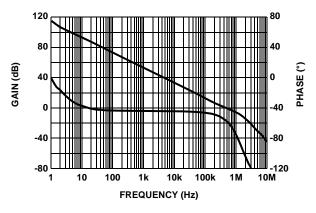

FIGURE 5. A<sub>VOL</sub> vs FREQUENCY @ 100k $\Omega$  LOAD

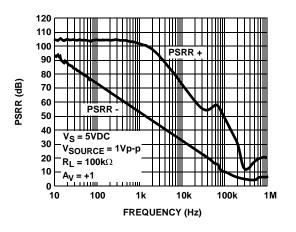

FIGURE 7. PSRR vs FREQUENCY

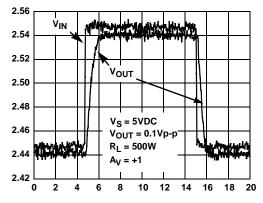

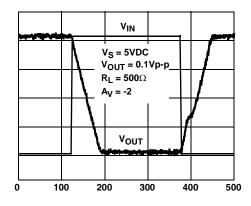

FIGURE 9. SMALL SIGNAL TRANSIENT RESPONSE

FIGURE 6. A<sub>VOL</sub> vs FREQUENCY @  $1k\Omega$  LOAD

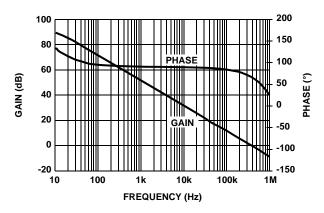

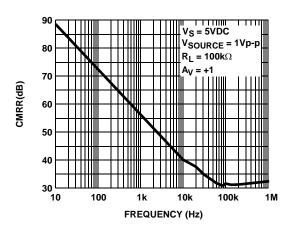

FIGURE 8. CMRR vs FREQUENCY

FIGURE 10. LARGE SIGNAL TRANSIENT RESPONSE

FN6301.0

June 23, 2006

intersil

FIGURE 11. CURRENT NOISE vs FREQUENCY

FIGURE 13. 0.1Hz TO 10Hz INPUT VOLTAGE NOISE

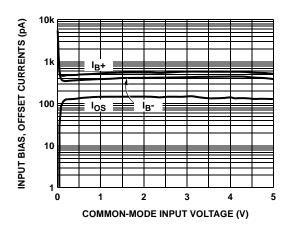

FIGURE 15. INPUT BIAS + OFFSET CURRENTS vs COMMON-MODE INPUT VOLTAGE

FIGURE 12. VOLTAGE NOISE vs FREQUENCY

FIGURE 14. INPUT VOLTAGE SWING ABOVE THE V+ SUPPLY

FIGURE 16. SUPPLY CURRENT vs SUPPLY VOLTAGE

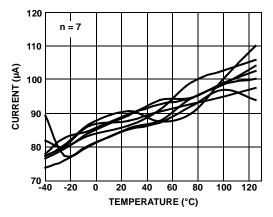

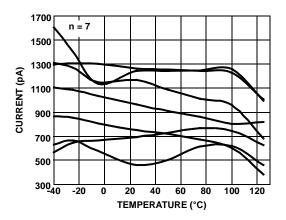

FIGURE 17. SUPPLY CURRENT vs TEMPERATURE  $V_S = \pm 1.2V$  ENABLED.  $R_L = INF$

FIGURE 18. SUPPLY CURRENT vs TEMPERATURE  $V_S = \pm 2.5V$  ENABLED.  $R_L = INF$

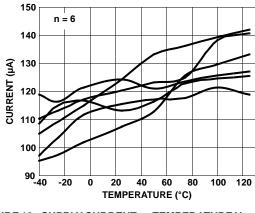

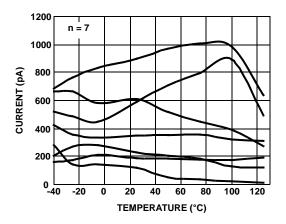

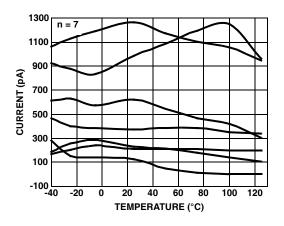

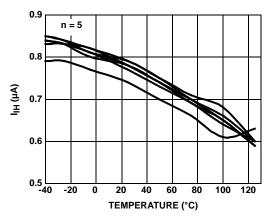

FIGURE 19. I BIAS(+) vs TEMPERATURE  $V_S = \pm 2.5V$

FIGURE 20. I BIAS(+) vs TEMPERATURE  $V_S = \pm 1.2V$

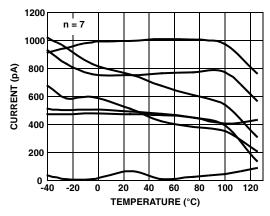

FIGURE 21. I BIAS(-) vs TEMPERATURE  $V_S = \pm 2.5V$

FIGURE 22. I BIAS(-) vs TEMPERATURE  $V_S = \pm 1.2V$

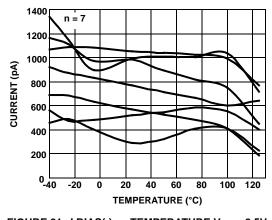

FIGURE 23. INPUT OFFSET CURRENT vs TEMPERATURE  $V_S = \pm 2.5 V$

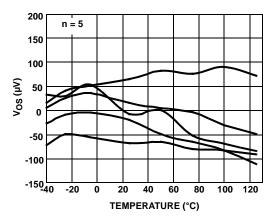

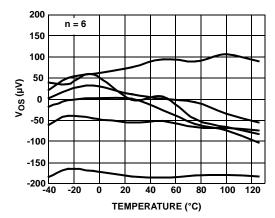

FIGURE 25. INPUT OFFSET VOLTAGE vs TEMPERATURE  $V_S = \pm 2.5 V$

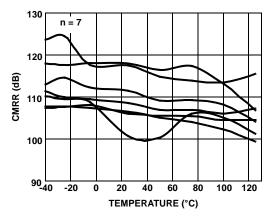

FIGURE 27. CMRR vs TEMPERATURE  $V_{CM} = +2.5V$  TO -2.5V

FIGURE 24. INPUT OFFSET CURRENT vs TEMPERATURE  $V_S = \pm 1.2V$

FIGURE 26. INPUT OFFSET VOLTAGE vs TEMPERATURE  $V_S = \pm 1.2V$

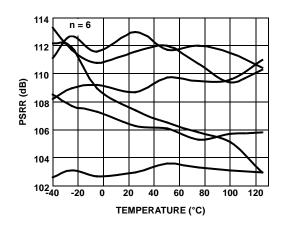

FIGURE 28. PSRR vs TEMPERATURE  $V_S = \pm 1.2V$  TO  $\pm 2.5V$

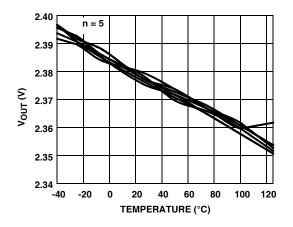

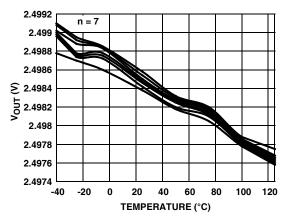

FIGURE 29. POSITIVE  $V_{OUT}$  vs TEMPERATURE  $R_L$  = 1k  $V_S$  = ±2.5V

FIGURE 31. POSITIVE  $V_{OUT}$  vs TEMPERATURE  $R_L$  = 100k  $V_S$  = ±2.5V

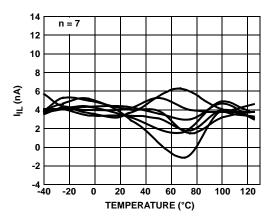

FIGURE 33.  $I_{IL}$  (EN) vs TEMPERATURE  $V_S = \pm 2.5V$

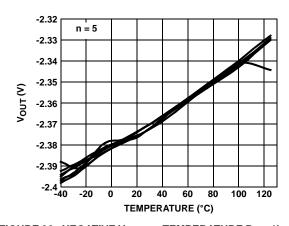

FIGURE 30. NEGATIVE  $V_{OUT}$  vs TEMPERATURE  $R_L$  = 1k  $V_S$  = ±2.5V

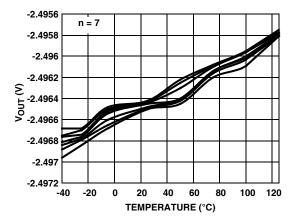

FIGURE 32. NEGATIVE  $V_{OUT}$  vs TEMPERATURE  $R_L = 100k$  $V_S = \pm 2.5V$

FIGURE 34.  $I_{IH}$  (EN) vs TEMPERATURE  $V_S = \pm 2.5V$

inter<sub>sil</sub>

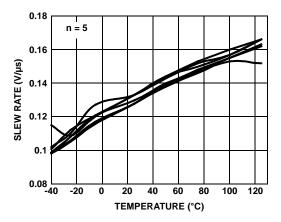

FIGURE 35. + SLEW RATE vs TEMPERATURE  $V_S = \pm 2.5V$ INPUT =  $\pm 0.75V$  A<sub>V</sub> = 2

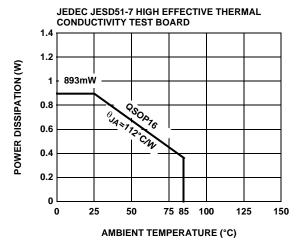

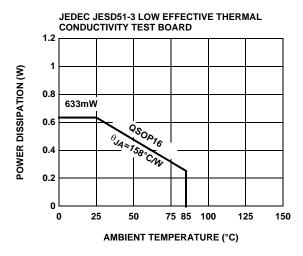

FIGURE 37. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

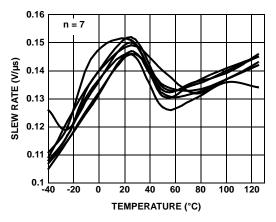

FIGURE 36. - SLEW RATE vs TEMPERATURE  $V_S = \pm 2.5V$ INPUT =  $\pm 0.75V$  A<sub>V</sub> = 2

FIGURE 38. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

FN6301.0 June 23, 2006

### Pin Descriptions

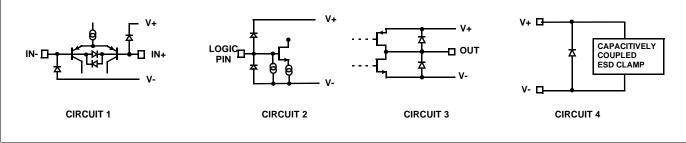

| ISL28276<br>(16 LD QSOP) | PIN NAME | EQUIVALENT<br>CIRCUIT | DESCRIPTION                                                                                                                |

|--------------------------|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1                        | NC       |                       | No internal connection                                                                                                     |

| 2                        | NC       |                       | No internal connection                                                                                                     |

| 3                        | OUT_A    | Circuit 3             | Amplifier A output                                                                                                         |

| 4                        | INA      | Circuit 1             | Amplifier A inverting input                                                                                                |

| 5                        | IN+_A    | Circuit 1             | Amplifier A non-inverting input                                                                                            |

| 6                        | EN_A     | Circuit 2             | Amplifier A enable pin internal pull-down; Logic "1" selects the disabled state; Logic "0" selects the enabled state.      |

| 7                        | V-       | Circuit 4             | Negative power supply                                                                                                      |

| 8                        | NC       |                       | No internal connection                                                                                                     |

| 9                        | NC       |                       | No internal connection                                                                                                     |

| 10                       | NC       |                       | No internal connection                                                                                                     |

| 11                       | EN_B     | Circuit 2             | Amplifier B enable pin with internal pull-down; Logic "1" selects the disabled state; Logic "0" selects the enabled state. |

| 12                       | IN+_B    | Circuit 1             | Amplifier B non-inverting input                                                                                            |

| 13                       | INB      | Circuit 1             | Amplifier B inverting input                                                                                                |

| 14                       | OUT_B    | Circuit 3             | Amplifier B output                                                                                                         |

| 15                       | V+       | Circuit 4             | Positive power supply                                                                                                      |

| 16                       | NC       |                       | No internal connection                                                                                                     |

### **Applications Information**

#### Introduction

The ISL28276 is an enhanced rail-to-rail input micropower precision operational amplifiers with an enable feature. The part is designed to operate from single supply (2.4V to 5.0V) or dual supply ( $\pm 1.2V$  to  $\pm 2.5V$ ). The device is capable of swinging 0.5V above a 5.0V supply (0.25V for a 2.4V supply) and to within 10mV from ground. The ISL28276 maintains CMRR performance for input voltages greater than the positive supply. The output operation can swing within about 3mV of the supply rails with a  $100k\Omega$  load (reference Figures 29 through 32).

#### Rail-to-Rail Input

The input common-mode voltage range of the ISL28276 goes from negative supply to positive supply without introducing additional offset errors or degrading performance associated with a conventional rail-to-rail input operational

amplifier. Many rail-to-rail input stages use two differential input pairs, a long-tail PNP (or PFET) and an NPN (or NFET). Severe penalties have to be paid for this circuit topology. As the input signal moves from one supply rail to another, the operational amplifier switches from one input pair to the other causing drastic changes in input offset voltage and an undesired change in magnitude and polarity of input offset current.

The ISL28276 achieves input rail-to-rail without sacrificing important precision specifications and degrading distortion performance. The devices' input offset voltage exhibits a smooth behavior throughout the entire common-mode input range. The input bias current versus the common-mode voltage range gives us an undistorted behavior from typically 10mV above the negative rail and 10% higher than the V+ rail (0.5V higher than V+ when V+ equals 5v).

#### Input Protection

All input terminals have internal ESD protection diodes to both positive and negative supply rails, limiting the input voltage to within one diode beyond the supply rails. The ISL28276 has additional back-to-back diodes across the input terminals. If overdriving the inputs is necessary, the external input current must never exceed 5mA. External series resistors may be used as an external protection to limit excessive external voltage and current from damaging the inputs.

#### Input Bias Current Compensation

The input bias currents of the ISL28276 are decimated down to a typical of 500pA while maintaining an excellent bandwidth for a micro-power operational amplifier. Inside the ISL28276 is an input bias canceling circuit. The input stage transistors are still biased with an adequate current for speed but the canceling circuit sinks most of the base current, leaving a small fraction as input bias current.

#### Rail-to-Rail Output

A pair of complementary MOSFET devices are used to achieve the rail-to-rail output swing. The NMOS sinks current to swing the output in the negative direction. The PMOS sources current to swing the output in the positive direction. The ISL28276 with a  $100 \mathrm{k}\Omega$  load will swing to within 3mV of the supply rails.

#### Enable/Disable Feature

The ISL28276 offers an  $\overline{\text{EN}}$  pin that disables the device when pulled up to at least 2.2V. In the disabled state (output in a high impedance state), the part consumes typically 4µA. By disabling the part, multiple ISL28276 parts can be connected together as a MUX. The outputs are tied together in parallel and a channel can be selected by the  $\overline{\text{EN}}$  pin. The  $\overline{\text{EN}}$  pin also has an internal pull down. If left open, the  $\overline{\text{EN}}$  pin will pull to the negative rail and the device will be enabled by default.

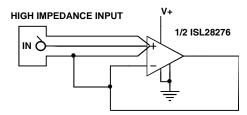

#### **Proper Layout Maximizes Performance**

To achieve the maximum performance of the high input impedance and low offset voltage of the ISL28276, care should be taken in the circuit board layout. The PC board surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board will reduce surface moisture and provide a humidity barrier, reducing parasitic resistance on the board. When input leakage current is a concern, the use of guard rings around the amplifier inputs will further reduce leakage currents. Figure 39 shows a guard ring example for a unity gain amplifier that uses the low impedance amplifier output at the same voltage as the high impedance input to eliminate surface leakage. The guard ring does not need to be a specific width, but it should form a continuous loop around both inputs. For further reduction of leakage

currents, components can be mounted to the PC board using Teflon standoff insulators.

FIGURE 39. GUARD RING EXAMPLE FOR UNITY GAIN AMPLIFIER

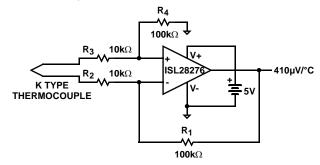

#### **Example Application**

Thermocouples are the most popular temperature-sensing device because of their low cost, interchangeability, and ability to measure a wide range of temperatures. The ISL28276 (Figure 40) is used to convert the differential thermocouple voltage into single-ended signal with 10X gain. The ISL28276's rail-to-rail input characteristic allows the thermocouple to be biased at ground and the converter to run from a single 5V supply.

FIGURE 40. THERMOCOUPLE AMPLIFIER

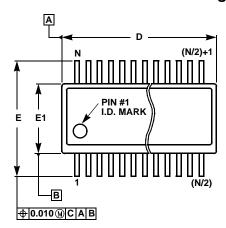

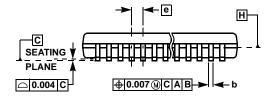

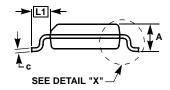

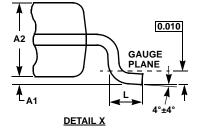

### Quarter Size Outline Plastic Packages Family (QSOP)

### 1DP0040

### QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |

|--------|--------|--------|--------|-----------|-------|

| Α      | 0.068  | 0.068  | 0.068  | Max.      | -     |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -     |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -     |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -     |

| С      | 0.008  | 0.008  | 0.008  | ±0.001    | -     |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -     |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -     |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -     |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -     |

| N      | 16     | 24     | 28     | Reference | -     |

Rev. E 3/01

#### NOTES:

- Plastic or metal protrusions of 0.006" maximum per side are not included.

- Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com