# ISL1540

PRELIMINARY

Data Sheet

#### February 21, 2006

## FN6113.0

## -52V Dual Channel Differential DSL Line Driver

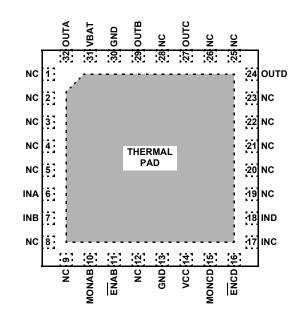

The ISL1540 is a -52V dual channel differential amplifier designed for driving full rate ADSL signals at very low power dissipation. The high supply voltage allows operation from a single standard -52V negative battery supply. It contains two pairs of wideband, high voltage, current mode feedback amplifiers optimized for lower power consumption and highest performance in ADSL and ADSL2+ systems. The line drivers have fixed gain  $A_V$  = 48 with integrated feedback and gain resistors. Its output clamping circuit eliminates the requirement for the Zener protection diodes.

These drivers achieve an MTPR distortion measurement of better than 70dB while consuming typically 3mA per DSL channel of total supply current.

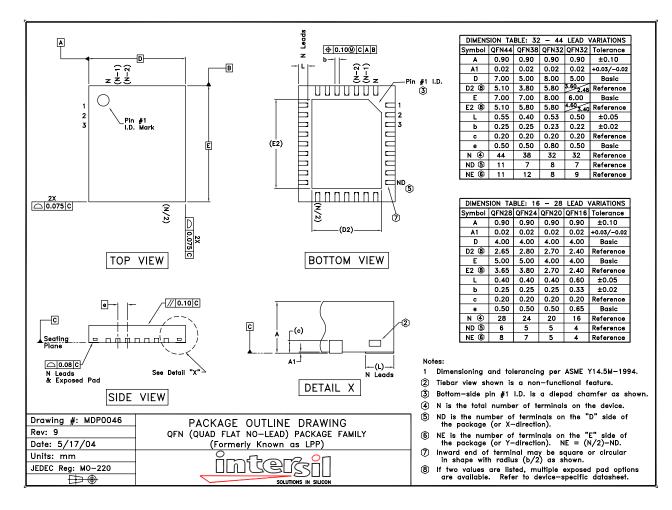

The ISL1540 is supplied in a thermally-enhanced 8mm x 8mm 32-pin QFN package and is specified for operating over the full -40°C to +85°C temperature range.

| PART<br>NUMBER               | PART<br>MARKING | PACKAGE                                | TAPE<br>&<br>REEL | PKG.<br>DWG. # |

|------------------------------|-----------------|----------------------------------------|-------------------|----------------|

| ISL1540IR                    | 1540IR          | 32-Pin QFN<br>(8mm x 8mm)              | -                 | MDP0046        |

| ISL1540IR-T7                 | 1540IR          | 32-Pin QFN<br>(8mm x 8mm)              | 7"                | MDP0046        |

| ISL1540IR-T13                | 1540IR          | 32-Pin QFN<br>(8mm x 8mm)              | 13"               | MDP0046        |

| ISL1540IRZ<br>(See Note)     | 1540IRZ         | 32-Pin QFN<br>(8mm x 8mm)<br>(Pb-Free) | -                 | MDP0046        |

| ISL1540IRZ-T7<br>(See Note)  | 1540IRZ         | 32-Pin QFN<br>(8mm x 8mm)<br>(Pb-Free) | 7"                | MDP0046        |

| ISL1540IRZ-T13<br>(See Note) | 1540IRZ         | 32-Pin QFN<br>(8mm x 8mm)<br>(Pb-Free) | 13"               | MDP0046        |

## Ordering Information

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- 200mA output current driving capability

- · Operates from a single -40V to -60V power supply

- 800mW per channel total power dissipation

- MTPR of -70dB

- 96V<sub>P-P</sub> differential output swing

- · Fixed gain, integrated gain resistors

- Current control pins

- · Output clamp for lightning and surge protection

- · Channel separation

- 75dB @ 1MHz

- Pb-free plus anneal available (RoHS compliant)

## Applications

- · Dual port ADSL and ADSL2+ line drivers

- HDSL, HDSL2, HDSL 4 and SHDSL line drivers

- DSLAM, DLC, MDU/MTU line drivers

- Performance upgrade to Le87213 and Le87213A

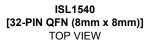

### Pinout

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| V <sub>CC</sub> Voltage to GND0.3V to 6.0V | Current into any Input8mA                    |

|--------------------------------------------|----------------------------------------------|

| V <sub>BAT</sub> Voltage to GND65V to 0.3V | Output Current from Driver (Static)          |

| Driver V <sub>IN</sub> + Voltage           | Power Dissipation See Curves                 |

| ENA Voltage to GND                         | Storage Temperature Range                    |

| I <sub>ADJ</sub> Voltage to GND            | Operating Temperature Range40°C to +85°C     |

|                                            | Operating Junction Temperature40°C to +150°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

#### **Electrical Specifications** $V_{BAT} = -52V$ , $R_F = 10k\Omega$ , $R_L = 300\Omega$ , $V_{CC} = 3.3V$ , $I_{ADJ} = \overline{EN} = 0V$ , $T_A = 25^{\circ}C$ . Amplifiers tested separately.

| PARAMETER                               | DESCRIPTION                                                                                           | CONDITIONS                                                                                | MIN  | ТҮР  | MAX  | UNIT   |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|--------|

| SUPPLY CHARACT                          | ERISTICS                                                                                              |                                                                                           |      | 1    |      |        |

| I <sub>BAT</sub> (Full I <sub>S</sub> ) | Negative Supply Current per Amplifier                                                                 | All outputs at 0V, EN = 0V                                                                |      | -3   |      | mA     |

| I <sub>BAT</sub> (Power-down)           | Negative Supply Current per Amplifier                                                                 | All outputs at 0V, EN = 3.3V                                                              |      | 50   |      | μA     |

| INPUT CHARACTE                          | RISTICS                                                                                               |                                                                                           |      |      | 4    | ļ      |

| V <sub>OS</sub>                         | Input Offset Voltage                                                                                  |                                                                                           | -50  | +10  | +50  | mV     |

| $\Delta V_{OS}$                         | V <sub>OS</sub> Mismatch                                                                              |                                                                                           | -5   | 1    | +5   | mV     |

| I <sub>B</sub> +                        | Non-Inverting Input Bias Current                                                                      |                                                                                           | -15  |      | +14  | μA     |

| I <sub>B</sub> -                        | Inverting Input Bias Current                                                                          |                                                                                           | -30  |      | +30  | μA     |

| Δl <sub>B</sub> -                       | I <sub>B</sub> - Mismatch                                                                             |                                                                                           | -25  | 0    | +25  | μA     |

| R <sub>OL</sub>                         | Transimpedance                                                                                        |                                                                                           | TBD  | TBD  | TBD  | MΩ     |

| e <sub>N</sub>                          | Input Noise Voltage                                                                                   |                                                                                           |      | TBD  |      | nV∕√Hz |

| i <sub>N</sub>                          | -Input Noise Current                                                                                  |                                                                                           |      | TBD  |      | pA∕√Hz |

| V <sub>IH</sub>                         | Input High Voltage                                                                                    | EN & MON inputs, with signal                                                              | 2    |      |      | V      |

| V <sub>IL</sub>                         | Input Low Voltage                                                                                     | EN & MON inputs                                                                           |      |      | 0.8  | V      |

| I <sub>IH1</sub>                        | Input High Current for MON                                                                            | MON = 3.3V                                                                                | 0.05 | 0.25 | 5    | μA     |

| I <sub>IH0</sub>                        | Input High Current for EN                                                                             | <u>EN</u> = 3.3V                                                                          | 0.05 | 0.5  | 5    | μA     |

| IIL                                     | Input Low Current for C <sub>0</sub> or MON                                                           | <del>EN</del> = 0V, MON = 0V                                                              | -0.3 | 0    | +0.3 | μA     |

| OUTPUT CHARACT                          | TERISTICS                                                                                             |                                                                                           |      |      |      | 1      |

| V <sub>OUT-Headroom</sub>               | Loaded Output Headroom<br>(R <sub>L</sub> Single-ended to GND)<br>V <sub>BAT</sub> - V <sub>OUT</sub> | R <sub>L</sub> = 300Ω                                                                     |      | 1.5  |      | V      |

|                                         |                                                                                                       | R <sub>L</sub> = 100Ω (+)                                                                 |      | 2.3  |      | V      |

|                                         |                                                                                                       | R <sub>L</sub> = 100Ω (-)                                                                 |      | 3.4  |      | V      |

| I <sub>OL</sub>                         | Linear Output Current                                                                                 | $A_V = 5$ , $R_L = 100\Omega$ , $f = 100$ kHz,<br>THD = -60dBc (10 $\Omega$ single-ended) |      | 200  |      | mA     |

| IOUT                                    | Output Current                                                                                        | $V_{OUT}$ = 1V, $R_L$ = 1 $\Omega$                                                        |      | 1    |      | Α      |

| DYNAMIC PERFOR                          | MANCE                                                                                                 |                                                                                           |      |      |      | 1      |

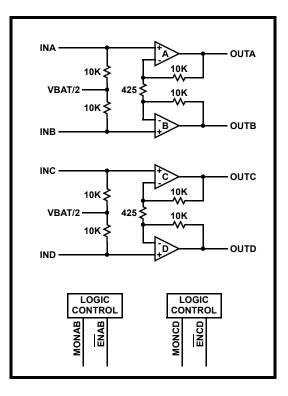

| A <sub>V</sub>                          | Gain 25kHz to 4MHz                                                                                    |                                                                                           |      | 48   |      | V/V    |

| BW                                      | -3dB Bandwidth                                                                                        | A <sub>V</sub> = +48                                                                      |      | 14   |      | MHz    |

| HD2                                     | 2nd Harmonic Distortion                                                                               | f <sub>C</sub> = 1MHz, R <sub>L</sub> = 300Ω, V <sub>OUT</sub> = 2V <sub>P-P</sub>        |      | TBD  |      | dBc    |

|                                         |                                                                                                       | f <sub>C</sub> = 1MHz, R <sub>L</sub> = 100Ω, V <sub>OUT</sub> = 2V <sub>P-P</sub>        |      | TBD  |      | dBc    |

| HD3                                     | 3rd Harmonic Distortion                                                                               | f <sub>C</sub> = 1MHz, R <sub>L</sub> = 300Ω, V <sub>OUT</sub> = 2V <sub>P-P</sub>        |      | TBD  |      | dBc    |

|                                         |                                                                                                       | f <sub>C</sub> = 1MHz, R <sub>L</sub> = 100Ω, V <sub>OUT</sub> = 2V <sub>P-P</sub>        |      | TBD  |      | dBc    |

**Electrical Specifications**  $V_{BAT} = -52V$ ,  $R_F = 10k\Omega$ ,  $R_L = 300\Omega$ ,  $V_{CC} = 3.3V$ ,  $I_{ADJ} = \overline{EN} = 0V$ ,  $T_A = 25^{\circ}C$ . Amplifiers tested separately.

| PARAMETER | DESCRIPTION             | CONDITIONS                                                         | MIN | TYP | MAX | UNIT |

|-----------|-------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| MTPR      |                         | 26kHz to 1.1MHz, $R_{LINE} = 600\Omega$ ,<br>$P_{LINE} = 20.4$ dBM |     | -70 |     | dBc  |

| SR        | Slewrate (single-ended) | $V_{OUT}$ from -24V to +24V measured at $\pm 12V$                  |     | 750 |     | V/µs |

## **Pin Descriptions**

| PIN NUMBER                                                 | PIN NAME | PIN DESCRIPTION                                 |  |

|------------------------------------------------------------|----------|-------------------------------------------------|--|

| 1, 2, 3, 4, 5, 8, 9, 12, 19, 20,<br>21, 22, 23, 25, 26, 28 | NC       | Not connected                                   |  |

| 6                                                          | INA      | Input A                                         |  |

| 7                                                          | INB      | Input B                                         |  |

| 10                                                         | MONAB    | Full bias/half bias current control for AB amps |  |

| 11                                                         | ENAB     | Enable/disable for AB amps                      |  |

| 13, 30                                                     | GND      | Ground                                          |  |

| 14                                                         | VCC      | 3.3V supply for bias and logic                  |  |

| 15                                                         | MONCD    | Full bias/half bias current control for CD amps |  |

| 16                                                         | ENCD     | Enable/disable for CD amps                      |  |

| 17                                                         | INC      | Input C                                         |  |

| 18                                                         | IND      | Input D                                         |  |

| 24                                                         | OUTD     | Output D                                        |  |

| 27                                                         | OUTC     | Output C                                        |  |

| 29                                                         | OUTB     | Output B                                        |  |

| 31                                                         | VBAT     | -52 battery voltage                             |  |

| 32                                                         | OUTA     | Output A                                        |  |

## Block Diagram

4

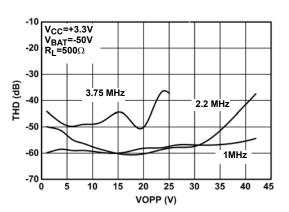

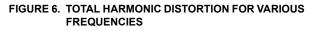

## **Typical Performance Curves**

FIGURE 1. FREQUENCY RESPONSE FOR VARIOUS RL

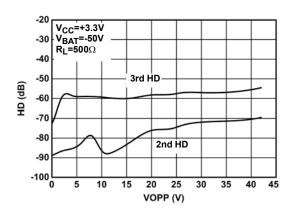

FIGURE 3. 1MHz 2nd & 3rd HARMONIC DISTORTION vs OUTPUT VOLTAGE

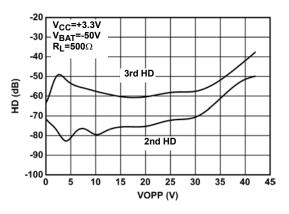

FIGURE 5. 3.75MHz 2nd & 3rd HARMONIC DISTORTION vs OUTPUT VOLTAGE

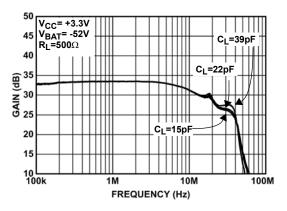

FIGURE 2. FREQUENCY RESPONSE FOR VARIOUS CL (EACH OUTPUTS TO GROUND)

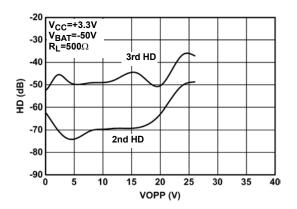

FIGURE 4. 2.2MHz 2nd & 3rd HARMONIC DISTORTION vs OUPUT VOLTAGE

FIGURE 7. CROSSTALK vs FREQUENCY

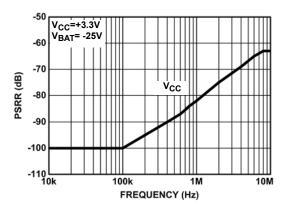

FIGURE 8. PSRR vs FREQUENCY

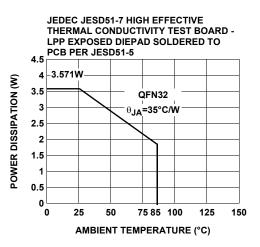

FIGURE 9. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 10. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

## **Application Information**

## PCB Layout Considerations for QFN Package

The ISL1540 die is packaged in a thermally efficient 32-pins QFN leadless plastic package (8mm x 8mm). A thermal pad is underneath the package and can use PCB surface metal vias areas and internal ground planes to spread heat away from the package. The larger the PCB area, the lower the junction temperature of the device will be. In ADSL applications, multiple layer circuit boards with internal ground plane are generally used. 13 mil vias are recommended to connect the metal area under the device with internal ground plane.

### **Power Control Function**

The ISL1540 contains four forms of power control operation. The two inputs, MON1 and MON2, can be used to control the supply current of the ISL1540 drive amplifiers. ENAB and ENCD can be used to enable and disable the device. Below is the table showing the power modes.

| MON1 | MON2 | ENAB | ENCD | OPERATION                     |

|------|------|------|------|-------------------------------|

| 0    | 0    | 0    | 0    | IS Full Power Mode            |

| 1    | 1    | 0    | 0    | 1/2-I <sub>S</sub> Power Mode |

| Х    | Х    | 1    | 1    | Power Down                    |

TABLE 1. POWER MODES FOR ISL1541

## Package Outline Drawing

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com