#### Data Sheet

#### January 1999 File Number 2786.4

# Programmable Data Buffer

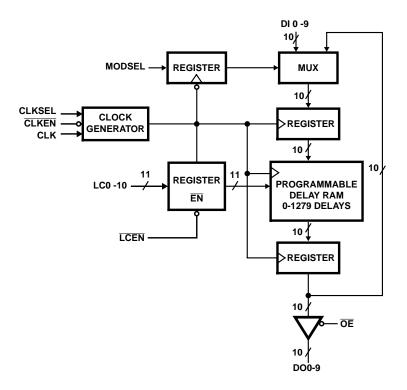

The HSP9501 is a 10-Bit wide programmable data buffer designed for use in high speed digital systems. Two different modes of operation can be selected through the use of the MODSEL input. In the delay mode, a programmable data pipeline is created which can provide 2 to 1281 clock cycles of delay between the input and output data. In the data recirculate mode, the output data path is internally routed back to the input to provide a programmable circular buffer.

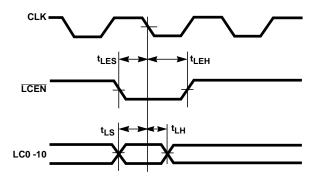

The length of the buffer or amount of delay is programmed through the use of the 11-bit Length Control Input Port (LC0-10) and the Length Control Enable ( $\overline{\text{LCEN}}$ ). An 11-bit value is applied to the LC0-10 inputs,  $\overline{\text{LCEN}}$  is asserted, and the next selected clock edge loads the new count value into the Length Control Register. The delay path of the HSP9501 consists of two registers with a programmable delay RAM between them, therefore, the value programmed into the Length Control Register is the desired length - 2. The range of values which can be programmed into the Length Control Register are from 0 to 1279, which in turn results in an overall range of programmable delays from 2 to 1281.

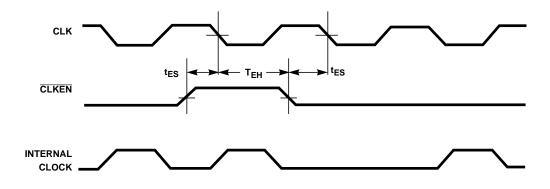

Clock select logic is provided to allow the use of a positive or negative edge system clock as the CLK input to the HSP9501. The active edge of the CLK input is controlled through the use of the CLKSEL input. All synchronous timing (i.e., data setup, hold, and output delays) are relative to the clock edge selected by CLKSEL. An additional clock enable input (CLKEN) provides a means of disabling the internal clock and holding the existing contents temporarily. All outputs of the HSP9501 are three-state outputs to allow direct interfacing to system or multi-use busses.

The HSP9501 is recommended for digital video processing or any applications which require a programmable delay or circular data buffer.

## Features

- DC to 32MHz Operating Frequency

- Programmable Buffer Length from 2 to 1281 Words

- · Supports Data Words to 10-Bits

- Clock Select Logic for Positive or Negative Edge System Clocks

- Data Recirculate or Delay Modes of Operation

- Expandable Data Word Width or Buffer Length

- Three-State Outputs

- TTL Compatible Inputs/Outputs

- Low Power CMOS

## Applications

- Sample Rate Conversion

- Data Time Compression/Expansion

- Software Controlled Data Alignment

- · Programmable Serial Data Shifting

- Audio/Speech Data Processing Video/Image Processing

# Video/Image Processing

- 1-H Delay Line of 910 NTSC, 1135 PAL or 1280 Samples:

- High Resolution Monitor Delay Line

- Comb Filter Designs

- Progressive Scanning Display

- TV Standards Conversion

- Image Processing

# **Ordering Information**

| PART NUMBER    | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE                     | PKG.<br>NO. |

|----------------|----------------------------------|-----------------------------|-------------|

| HSP9501JC-25   | 0 to 70                          | 44 Ld PLCC                  | N44.65      |

| HSP9501JC-32   | 0 to 70                          | 44 Ld PLCC                  | N44.65      |

| HSP9501JC-2596 | 0 to 70                          | 44 Ld PLCC<br>Tape and Reel | N44.65      |

Block Diagram

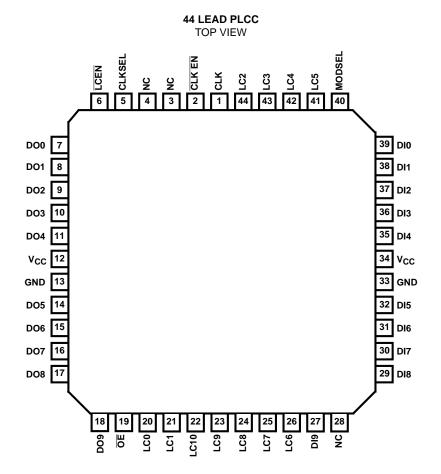

# **Pin Descriptions**

| NAME            | PIN NUMBER       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | 12, 34           |      | The +5V power supply pin. A $0.1\mu\text{F}$ capacitor between the $V_{CC}$ and GND pin is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND             | 13, 33           |      | The device ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLK             | 1                | I    | Input Clock. This clock signal is used to control the data movement through the programmable buff-<br>er. It is also the signal which latches the input data, length control word and mode select. Input<br>setup and hold times with respect to the clock must be met for proper operation.                                                                                                                                                                                                                                                 |

| DIO-9           | 27, 29-32, 35-39 | I    | Data Inputs. This 10-bit input port is used to provide the input data. When MODSEL is low, data on the DI0-9 inputs is latched on the clock edge selected by CLKSEL.                                                                                                                                                                                                                                                                                                                                                                         |

| DO0-9           | 7-11, 14-18      | 0    | Data Outputs. This 10-bit port provides the output data from the Internal Delay Registers. Data latched into the DI0-9 inputs will appear at the DO0 9 outputs on the Nth clock cycle, where N is the total delay programmed.                                                                                                                                                                                                                                                                                                                |

| LC0-10          | 20-26, 41-44     | I    | Length Control Inputs. These inputs are used to specify the number of clock cycles of delay be-<br>tween the DI0-9 inputs and the DO0-9 outputs. An integer value between 0 and 1279 is placed on<br>the LC0-10 inputs, and the total delay length (N) programmed is the LC0-10 value plus 2. In order<br>to properly load an active length control word, the value must be presented to the LC0-10 inputs<br>and LCEN must be asserted during an active clock edge selected by CLKSEL.                                                      |

| LCEN            | 6                | I    | Length Control Enable. LCEN is used in conjunction with LC0-10 and CLK to load a new length control word. An 11-bit value is loaded on the LC0-10 inputs, LCEN is asserted, and the next selected clock edge will load the new count value. Since this operation is synchronous, LCEN must meet the specified setup/hold times with respect to CLK for proper operation.                                                                                                                                                                     |

| ŌĒ              | 19               | I    | Output Enable. This input controls the state of the DO0-9 output port. A low on this control line enables the port for output. When $\overline{OE}$ is high, the output drivers are in the high impedance state. Internal latching or transfer of data is not affected by this input.                                                                                                                                                                                                                                                        |

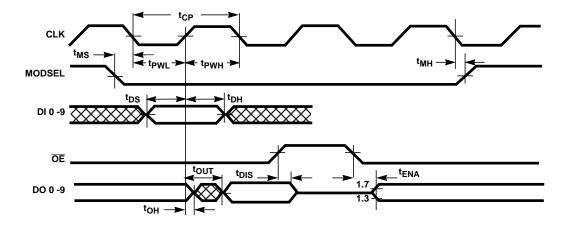

| MODSEL          | 40               | I    | Mode Select. This input is used to control the mode of operation of the HSP9501. A low on MOD-SEL causes the device to latch new data at the DI0-9 inputs on every clock cycle, and operate as a programmable pipeline register. When MODSEL is high, the HSP9501 is in the recirculate mode, and will operate as a programmable length circular buffer. This control signal may be used in a synchronous fashion during device operation, however, care must be taken to ensure the required set-up/hold times with respect to CLK are met. |

| CLKSEL          | 5                | I    | Clock Select Control. This input is used to determine which edge of the CLK signal is used for con-<br>trolling all internal events. A low on CLKSEL selects the negative going edge, therefore, all setup,<br>hold, and output delay times are with respect to the negative edge of CLK. When CLKSEL is high,<br>the positive going edge is selected and all synchronous timing is with respect to the positive edge<br>of the CLK signal.                                                                                                  |

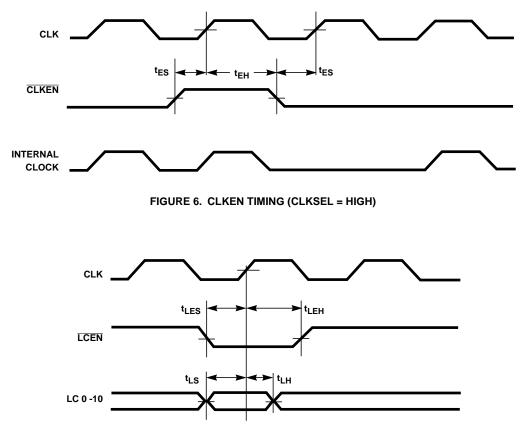

| CLKEN           | 2                | I    | Clock Enable. This control signal can be used to enable or disable the CLK input. When low, the CLK input is enabled and will operate in a normal fashion. A high on CLKEN will disable the CLK input and will "hold" all internal operations and data. This control signal may also be used in a synchronous fashion, however, setup and hold requirements with respect to CLK must be met for proper device operation. This signal takes effect on the clock following the one that latches it in.                                         |

# Functional Description

The HSP9501 is a 10-bit wide programmable length data buffer. The length of delay is programmable from 2 to 1281 delays in single delay increments.

Data into the delay line may be selected from the data input bus (DI0-9) or as recirculated output, depending on the state of the mode select (MODSEL) control input.

# Mode Select

The MODSEL control pin selects the source of the data moving into the delay line. When MODSEL is low, the data input bus (DI0-9) is the source of the data. When MODSEL is high, the output of the HSP9501 is routed back to the input to form a circular buffer.

The MODSEL control line is latched at the input by the CLK signal. The edge which latches this control signal is determined by the CLKSEL control line. In either case, the MODSEL line is latched on one edge of the CLK signal with the following edge moving data into and through the HSP9501. Refer to the functional timing waveforms for specific timing references.

# Clock Select Logic

The clock select logic is provided to allow the use of positive or negative edge system clocks. The active edge of the CLK input to the HSP9501 is controlled through the use of the CLKSEL input.

When CLKSEL is low, the negative going edge of CLK is used to control all internal operations. A high on CLKSEL selects the positive going edge of CLK.

All synchronous timing (i.e., setup, hold and output propagation delay times are relative to the CLK edge

selected by CLKSEL. Functional timing waveforms for each state of CLKSEL are provided (refer to Timing Waveforms for details).

# Delay Path Control

The HSP9501 buffer length is programmable from 2 to 1281 data words in one word increments. The minimum number of delays which can be programmed is two, consisting of the input and Output Buffer Registers only.

The length control inputs (LC0-10) are used to set the length of the programmable delay ram which can vary in length from 0 to 1279. The total length of the HSP9501 data buffer will then be equal to the programmed value on LC0-10 plus 2. The programmed delay is established by the 11-bit integer value of the LC0-10 inputs with LC-10 as the MSB and LC0 as the LSB.

For example,

| LC10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | LC0 |

|------|---|---|---|---|---|---|---|---|---|-----|

| 0    | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1   |

programs a length value of  $2^6 + 2^0 = 65$ . The total length of the delay will be 65 + 2 or 67 delays.

Table 1 indicates several programming values. The decimal value placed on LC0-10 must not exceed 1279. Controlled operation with larger values is not guaranteed.

Values on LC0-10 are latched on the CLK edge selected by the CLKSEL control line, when  $\overline{\text{LCEN}}$  is active. LC0-10 and  $\overline{\text{LCEN}}$  must meet the specified setup and hold times relative to the selected CLK edge for proper device operation.

| LC10 2 <sup>10</sup> | LC9<br>2 <sup>9</sup> | LS8<br>2 <sup>8</sup> | LC7<br>2 <sup>7</sup> | LC6<br>2 <sup>6</sup> | LC5<br>2 <sup>5</sup> | LC4<br>2 <sup>4</sup> | LC3<br>2 <sup>3</sup> | LC2<br>2 <sup>2</sup> | LC1<br>2 <sup>1</sup> | LC0<br>2 <sup>0</sup> | PROGRAMMED<br>LENGTH | TOTAL<br>LENGTH<br>N |

|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|

| 0                    | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                    | 2                    |

| 0                    | 0                     | 0                     | 0                     | 1                     | 1                     | 1                     | 0                     | 1                     | 1                     | 0                     | 118                  | 120                  |

| 0                    | 1                     | 1                     | 0                     | 0                     | 1                     | 0                     | 1                     | 0                     | 0                     | 0                     | 808                  | 810                  |

| 1                    | 0                     | 0                     | 0                     | 0                     | 0                     | 1                     | 1                     | 0                     | 0                     | 1                     | 1049                 | 1051                 |

| 1                    | 0                     | 0                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1279                 | 1281                 |

#### TABLE 1. LENGTH CONTROL PROGRAMMING EXAMPLES

#### **Absolute Maximum Ratings**

# **Operating Conditions**

| Temperature Range         | 70 <sup>0</sup> C |

|---------------------------|-------------------|

| Voltage Range +4.75V to 5 |                   |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------|--------------------------------------|

| PLCC Package                             | 45.2                                 |

| Maximum Junction Temperature             | 150 <sup>0</sup> C                   |

| Maximum Storage Temperature Range        | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s) | 300 <sup>0</sup> C                   |

| (PLCC - Lead Tips Only)                  |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

| DC Electrical Specifications   | V <sub>CC</sub> = 5.0V +5%, 1 | $T_A = 0^{\circ}C$ to 70°C, Commercial                                                        |     |     |       |

|--------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------|-----|-----|-------|

| PARAMETER                      | SYMBOL                        | SYMBOL TEST CONDITIONS                                                                        |     |     | UNITS |

| Logical One Input Voltage      | V <sub>IH</sub>               | V <sub>CC</sub> = 5.25V                                                                       | 2.0 | -   | V     |

| Logical Zero Input Voltage     | V <sub>IL</sub>               | V <sub>CC</sub> = 4.75V                                                                       | -   | 0.8 | V     |

| Output HIGH Voltage            | V <sub>OH</sub>               | $I_{OH} = -4mA V_{CC} = 4.75V$                                                                | 2.4 | -   | V     |

| Output LOW Voltage             | V <sub>OL</sub>               | I <sub>OL</sub> = +4.0mA V <sub>CC</sub> = 4.75V                                              | -   | 0.4 | V     |

| Input Leakage Current          | Ц                             | $V_{IN} = GND \text{ or } V_{CC} V_{CC} = 5.25V$                                              | -10 | 10  | μA    |

| Output Leakage Current         | Ι <sub>Ο</sub>                | $V_{OUT} = GND \text{ or } V_{CC} = 5.25V$                                                    | -10 | 10  | μΑ    |

| Standby Current                | I <sub>CCSB</sub>             | $V_{IN} = V_{CC}$ or GND, $V_{CC} = 5.25V$ , Note 3                                           | -   | 500 | μA    |

| Operating Power Supply Current | ICCOP                         | $    f = 25 MHz, V_{IN} = V_{CC} \text{ or GND} $ $    V_{CC} = 5.25 V, \text{ Notes } 2, 3 $ | -   | 125 | mA    |

| Input Capacitance              | C <sub>IN</sub>               | FREQ = 1MHz, V <sub>CC</sub> = Open, All                                                      | -   | 10  | pF    |

| Output Capacitance             | CO                            | measurements are referenced to device                                                         | -   | 10  | pF    |

#### AC Electrical Specifications $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}C$ to +70°C, Commercial, (Note 5)

|                        |                  | ÷   | 32  | -2  | 25  |       |        |

|------------------------|------------------|-----|-----|-----|-----|-------|--------|

| PARAMETER              | SYMBOL           | MIN | MAX | MIN | MAX | UNITS | NOTES  |

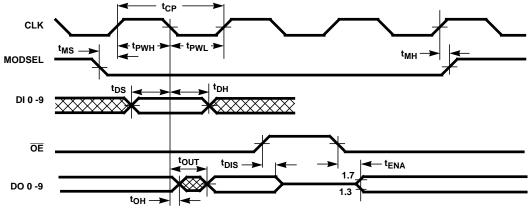

| Clock Period           | t <sub>CP</sub>  | 31  | -   | 40  | -   | ns    | -      |

| Clock Pulse Width High | t <sub>PWH</sub> | 12  | -   | 15  | -   | ns    | -      |

| Clock Pulse Width Low  | t <sub>PWL</sub> | 12  | -   | -   | 15  | ns    | -      |

| Data Input Setup Time  | t <sub>DS</sub>  | 10  | -   | 12  | -   | ns    | -      |

| Data Input Hold Time   | t <sub>DH</sub>  | 2   | -   | 2   | -   | ns    | -      |

| Output Enable Time     | t <sub>ENA</sub> | -   | 20  | -   | 25  | ns    | -      |

| Output Disable Time    | t <sub>DIS</sub> | -   | 24  | -   | 25  | ns    | Note 4 |

| CLKEN to Clock Setup   | t <sub>ES</sub>  | 10  | -   | 12  | -   | ns    | -      |

| CLKEN to Clock Hold    | t <sub>EH</sub>  | 2   | -   | 2   | -   | ns    | -      |

| LC0-10 Setup Time      | t <sub>LS</sub>  | 10  | -   | 13  | -   | ns    | -      |

| LC0-10 Hold Time       | t <sub>LH</sub>  | 2   | -   | 2   | -   | ns    | -      |

| ICEN to Clock Setup    | t <sub>LES</sub> | 10  | -   | 13  | -   | ns    | -      |

| LCEN to Clock Hold     | tLEH             | 2   | -   | 2   | -   | ns    | -      |

|                        |                  | -32 |     | -2  | 25  |       |        |

|------------------------|------------------|-----|-----|-----|-----|-------|--------|

| PARAMETER              | SYMBOL           | MIN | MAX | MIN | МАХ | UNITS | NOTES  |

| MODSEL Setup Time      | t <sub>MS</sub>  | 10  | -   | 13  | -   | ns    | -      |

| MODSEL Hold Time       | t <sub>MH</sub>  | 2   | -   | 2   | -   | ns    | -      |

| Clock to Data Out      | T <sub>OUT</sub> | -   | 16  | -   | 22  | ns    | -      |

| Output Hold from Clock | т <sub>он</sub>  | 4   | -   | 4   | -   | ns    | -      |

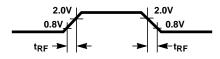

| Rise, Fall Time        | T <sub>RF</sub>  | -   | 6   | -   | 6   | ns    | Note 4 |

## AC Electrical Specifications $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0^{\circ}C$ to +70°C, Commercial, (Note 5) (Continued)

NOTES:

2. Power supply current is proportional to operating frequency. Typical rating for  $I_{CCOP}$  is 5mA/MHz.

4. Controlled by design or process parameters and not directly tested. Characterized upon initial design and after major process and/or design changes.

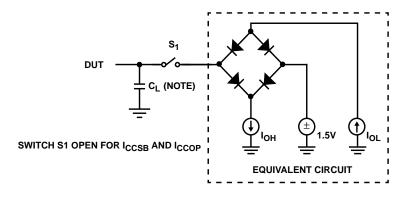

5. AC Testing is performed as follows: Input levels: 0V and 3.0V, timing reference levels = 1.5V, input rise and fall times driven at 1ns/V, output load C<sub>L</sub> = 40pF.

# Test Load Circuit

NOTE: Includes stray and jig capacitance.

<sup>3.</sup> Output load per test load circuit with switch open and  $C_L = 40 pF$ .

# **Timing Waveforms**

FIGURE 1. FUNCTIONAL TIMING (CLKSEL = LOW)

FIGURE 3. OUTPUT RISE AND FALL TIMES

FIGURE 4. LENGTH CONTROL TIMING (CLKSEL = LOW)

# Timing Waveforms (Continued)

FIGURE 5. FUNCTIONAL TIMING (CLKSEL = HIGH)

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com