# HM-65262/883

### 16K x 1 Asynchronous CMOS Static RAM

March 1997

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Fast Access Time ...... 70/85ns Max

- Low Standby Current......50μA Max

- Low Operating Current ...... 50mA Max

- TTL Compatible Inputs and Outputs

- JEDEC Approved Pinout

- No Clocks or Strobes Required

- Temperature Range ...... +55°C to +125°C

- Gated Inputs-No Pull-Up or Pull-Down Resistors Required

- Equal Cycle and Access Time

- Single 5V Supply

#### **Ordering Information**

#### Description

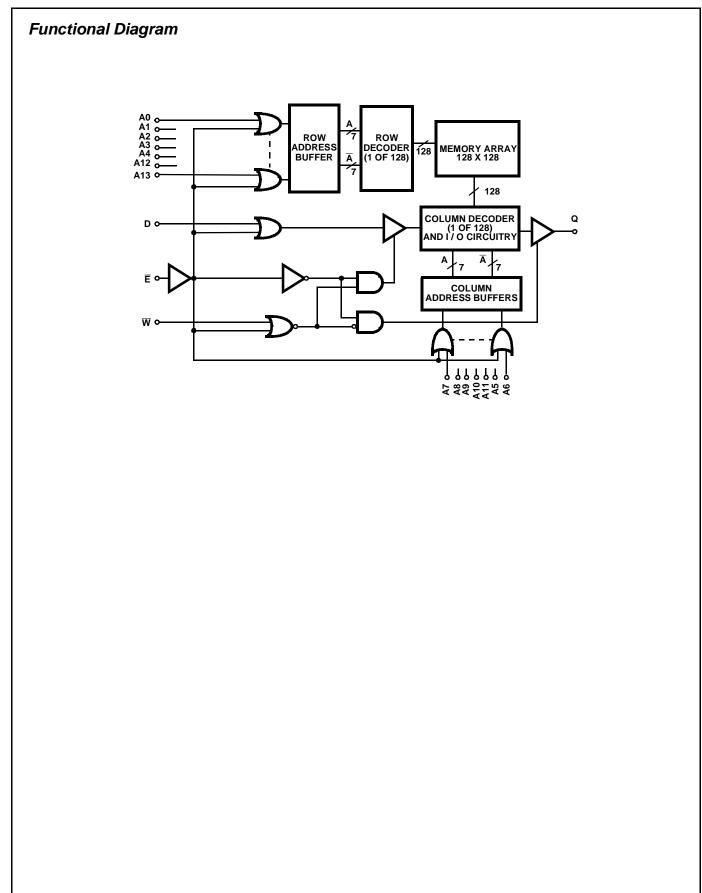

The HM-65262/883 is a CMOS 16384 x 1-bit Static Random Access Memory manufactured using the Intersil Advanced SAJI V process. The device utilizes asynchronous circuit design for fast cycle times and ease of use. The HM-65262/883 is available in both JEDEC Standard 20 pin, 0.300 inch wide CERDIP and 20 pad CLCC packages, providing high board-level packing density. Gated inputs lower standby current, and also eliminate the need for pull-up or pull-down resistors.

The HM-65262/883, a full CMOS RAM, utilizes an array of six transistor (6T) memory cells for the most stable and lowest possible standby supply current over the full military temperature range. In addition to this, the high stability of the 6T RAM cell provides excellent protection against soft errors due to noise and alpha particles. This stability also improves the radiation tolerance of the RAM over that of four transistor (4T) devices.

| <b>70ns/20</b> μA | <b>85ns/20</b> μ <b>A</b> | 85ns/400μA | TEMP. RANGE     | PACKAGE | PKG. NO. |

|-------------------|---------------------------|------------|-----------------|---------|----------|

| -                 | HM1-65262/883             | -          | -55°C to +125°C | CERDIP  | F20.3    |

| HM4-65262B/883    | HM4-65262/883             | -          | -55°C to +125°C | CLCC    | J20.C    |

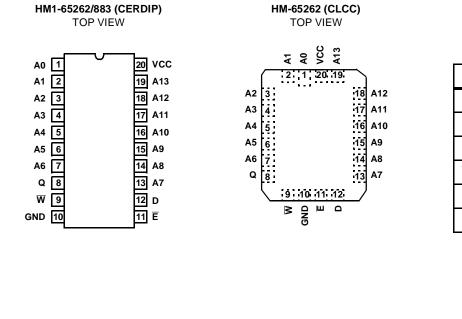

#### **Pinouts**

| A0 - A13 | Address Input          |

|----------|------------------------|

| Ē        | Chip Enable/Power Down |

| Q        | Data Out               |

| D        | Data In                |

| VSS/GND  | Ground                 |

| VCC      | Power (+5)             |

| W        | Write Enable           |

| Absolute Maximum Ratings                                                                                                                                                 | Thermal Information |                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------|--|--|--|

| Supply Voltage  +7.0V    Input or Output Voltage Applied for all Grades  -0.3V to VCC +0.3V    Typical Derating Factor  .5mA/MHz Increase in ICCOP    ESD Classification | CERDIP Package      |                                |  |  |  |

|                                                                                                                                                                          | Die Characteristics |                                |  |  |  |

|                                                                                                                                                                          | Gate Count          | 26256 Gates                    |  |  |  |

| CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may ca<br>of the device at these or any other conditions above those indicated in the open            | 5                   | ress only rating and operation |  |  |  |

#### **Operating Conditions**

| Operating Voltage Range                   | Input High Voltage (VIH)±2.2V to VCC       |

|-------------------------------------------|--------------------------------------------|

| Operating Temperature Range55°C to +125°C | Data Retention Supply Voltage 2.0V to 4.5V |

| Input Low Voltage0V to +0.8V              | Input Rise and Fall Time                   |

#### TABLE 1. HM-65262/883 DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

| DC PARAMETER                             | SYMBOL | (NOTE 1)<br>CONDITIONS                                 | GROUP A<br>SUB-GROUPS | TEMPERATURE                                                             | MIN  | МАХ | UNITS |

|------------------------------------------|--------|--------------------------------------------------------|-----------------------|-------------------------------------------------------------------------|------|-----|-------|

| High Level Output Voltage                | VOH1   | VCC = 4.5V, IO = -4.0mA                                | 1, 2, 3               | $-55^{0}C \le T_{A} \le +125^{0}C$                                      | 2.4  | -   | V     |

| Low Level Output Voltage                 | VOL    | VCC = 4.5V, IO = 8.0mA                                 | 1, 2, 3               | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -    | 0.4 | V     |

| High Impedance Output<br>Leakage Current | IOZ    | VCC = 5.5V, $\overline{E}$ = 5.5V, VO = GND<br>or VCC  | 1, 2, 3               | $\text{-55}^{o}\text{C} \leq \text{T}_{A} \leq \text{+125}^{o}\text{C}$ | -1.0 | 1.0 | μΑ    |

| Input Leakage Current                    | II     | VCC = 5.5V, VI = GND or VCC                            | 1, 2, 3               | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -1.0 | 1.0 | μΑ    |

| Standby Supply Current                   | ICCSB1 | VCC = 5.5V, IO = 0mA, $\overline{E}$ = VCC<br>-0.3V    | 1, 2, 3               | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -    | 50  | μΑ    |

| Standby Supply Current                   | ICCSB  | VCC = 5.5V, IO = 0mA, $\overline{E}$ = 2.2V            | 1, 2, 3               | $-55^{0}C \leq T_{A} \leq +125^{0}C$                                    | -    | 5   | mA    |

| Operating Supply<br>Current              | ICCOP  | VCC = 5.5V, (Note 2), f = 1MHz, <del>E</del><br>= 0.8V | 1, 2, 3               | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -    | 50  | mA    |

| Data Retention Supply<br>Current         | ICCDR  | VCC = 2.0V, IO = 0mA, $\overline{E}$ = VCC<br>-0.3V    | 1, 2, 3               | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -    | 20  | μΑ    |

| Enable Supply Current                    | ICCEN  | VCC = 5.5V, IO = 0mA, $\overline{E}$ = 0.8V            | 1, 2, 3               | $-55^{0}C \leq T_{A} \leq +125^{0}C$                                    | -    | 50  | mA    |

| Functional Test                          | FT     | VCC = 4.5V (Note 3)                                    | 7, 8A, 8B             | $-55^{o}C \le T_{A} \le +125^{o}C$                                      | -    | -   | -     |

#### NOTES:

1. All voltages referenced to device GND.

2. Typical derating 1.5mA/MHz increase in ICCOP.

3. Tested as follows: f = 2MHz, VIH = 2.4V, VIL = 0.4V, IOH = -4.0mA, IOL = 4.0mA, VOH  $\ge$  1.5V, and VOL  $\le$  1.5V.

#### TABLE 2. HM-65262/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

|                          |           | (NOTES 1, 2)        | GROUP A<br>2) SUB- |                                      | 65262 | M-<br>:B/883<br>IITS |     | 262/883<br>IITS |       |

|--------------------------|-----------|---------------------|--------------------|--------------------------------------|-------|----------------------|-----|-----------------|-------|

| AC PARAMETER             | SYMBOL    | CONDITIONS          | GROUPS             | TEMPERATURE                          | MIN   | MAX                  | MIN | MAX             | UNITS |

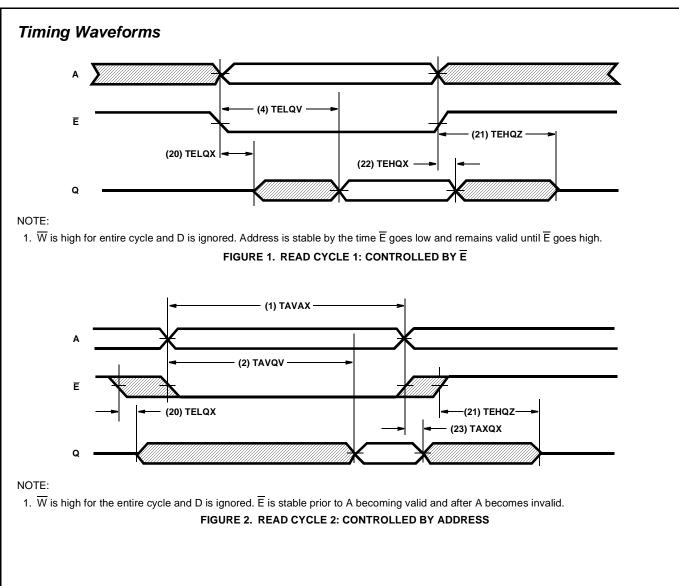

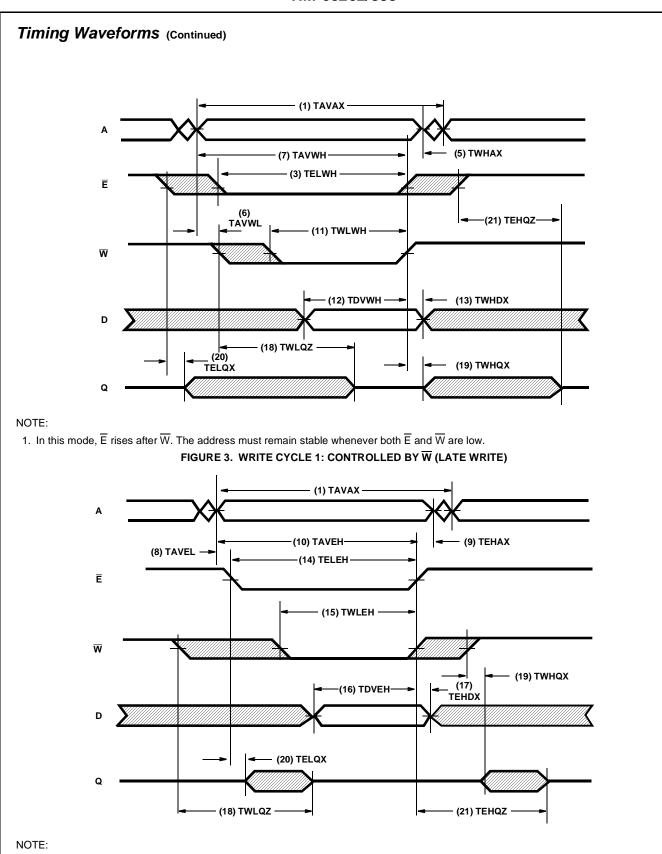

| Read/Write/Cycle<br>Time | (1) TAVAX | VCC = 4.5V and 5.5V | 9, 10, 11          | $-55^{o}C \leq T_{A} \leq +125^{o}C$ | 70    | -                    | 85  | -               | ns    |

| Address Access<br>Time   | (2) TAVQV | VCC = 4.5V and 5.5V | 9, 10, 11          | $-55^{0}C \leq T_{A} \leq +125^{0}C$ | -     | 70                   | -   | 85              | ns    |

#### TABLE 2. HM-65262/883 AC ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued) Device Guaranteed and 100% Tested

|                                   |            |                            | GROUP A<br>SUB- |                                                  | 65262 | M-<br>2B/883<br>IITS |     | 262/883<br>NTS |       |

|-----------------------------------|------------|----------------------------|-----------------|--------------------------------------------------|-------|----------------------|-----|----------------|-------|

| AC PARAMETER                      | SYMBOL     | (NOTES 1, 2)<br>CONDITIONS | GROUPS          | TEMPERATURE                                      | MIN   | MAX                  | MIN | MAX            | UNITS |

| Chip Enable to End<br>of Write    | (3) TELWH  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 55    | -                    | 65  | -              | ns    |

| Chip Enable Access<br>Time        | (4) TELQV  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \leq T_{A} \leq +125^{o}C$             | -     | 70                   | -   | 85             | ns    |

| Address Hold Time                 | (5) TWHAX  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 0     | -                    | 0   | -              | ns    |

| Address Setup Time                | (6) TAVWL  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 0     | -                    | 0   | -              | ns    |

| Address Valid to<br>End of Write  | (7) TAVWH  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 55    | -                    | 65  | -              | ns    |

| Address Setup Time                | (8) TAVEL  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 0     | -                    | 0   | -              | ns    |

| Address Hold Time                 | (9) TEHAX  | VCC = 4.5V and 5.5V        | 9, 10, 11       | $\text{-55}^{o}C \leq T_A \leq \text{+125}^{o}C$ | 0     | -                    | 0   | -              | ns    |

| Address Valid to<br>End of Writes | (10) TAVEH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \leq T_{A} \leq +125^{o}C$             | 55    | -                    | 65  | -              | ns    |

| Write Enable Pulse<br>Write       | (11) TWLWH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 40    | -                    | 45  | -              | ns    |

| Data Setup Time                   | (12) TDVWH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 30    | -                    | 35  | -              | ns    |

| Data Hold Time                    | (13) TWHDX | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 0     | -                    | 0   | -              | ns    |

| Enable Pulse Width                | (14) TELEH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 55    | -                    | 65  | -              | ns    |

| Write to End of<br>Write          | (15) TWLEH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 40    | -                    | 45  | -              | ns    |

| Data Setup Time                   | (16) TDVEH | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{o}C \le T_{A} \le +125^{o}C$               | 30    | -                    | 35  | -              | ns    |

| Data Hold Time                    | (17) TEHDX | VCC = 4.5V and 5.5V        | 9, 10, 11       | $-55^{0}C \le T_{A} \le +125^{0}C$               | 0     | -                    | 0   | -              | ns    |

NOTES:

1. All voltages referenced to device GND.

Input pulse levels: 0.8V to VCC -2.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate equivalent, CL = 50pF (min) - for CL greater than 50pF, access time is derated by 0.15ns per pF.

3. TAVQV = TELQV + TAVEL.

|                    |        | (NOTE 1)                                                                    |       |                                     | LIMIT | rs  |       |

|--------------------|--------|-----------------------------------------------------------------------------|-------|-------------------------------------|-------|-----|-------|

| PARAMETER          | SYMBOL | CONDITIONS                                                                  | NOTES | TEMPERATURE                         | MIN   | MAX | UNITS |

| Input Capacitance  | CIN    | VCC = Open, f = 1MHz, All<br>Measurements Refer-<br>enced To Device Grounds | 1, 2  | T <sub>A</sub> = +25 <sup>o</sup> C | -     | 10  | pF    |

|                    |        | VCC = Open, f = 1MHz, All<br>Measurements Refer-<br>enced To Device Grounds | 1, 3  | T <sub>A</sub> = +25 <sup>o</sup> C | -     | 6   | pF    |

| Output Capacitance | со     | VCC = Open, f = 1MHz, All<br>Measurements Refer-<br>enced To Device Grounds | 1, 2  | T <sub>A</sub> = +25 <sup>o</sup> C | -     | 12  | pF    |

|                    |        | VCC = Open, f = 1MHz, All<br>Measurements Refer-<br>enced To Device Grounds | 1, 3  | T <sub>A</sub> = +25 <sup>o</sup> C | -     | 8   | pF    |

|                                        |                 | (NOTE 1)                |       |                                      | LIMITS    |     |       |

|----------------------------------------|-----------------|-------------------------|-------|--------------------------------------|-----------|-----|-------|

| PARAMETER                              | SYMBOL          | CONDITIONS              | NOTES | TEMPERATURE                          | MIN       | MAX | UNITS |

| Write Enable to Output in High Z       | (18)<br>TWLQZ   | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \le T_{A} \le +125^{o}C$   | -         | 40  | ns    |

| Write Enable High to Output ON         | (19)<br>TWHQX   | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \le T_{A} \le +125^{o}C$   | 0         | -   | ns    |

| Chip Enable to Output ON               | (20)<br>TELQX   | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \le T_{A} \le +125^{o}C$   | 5         | -   | ns    |

| Output Enable High to Output in High Z | (21) TEHQZ      | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \le T_{A} \le +125^{o}C$   | -         | 40  | ns    |

| Chip Disable to Output Hold Time       | (22) TE-<br>HQX | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \leq T_{A} \leq +125^{o}C$ | 5         | -   | ns    |

| Address Invalid Output Hold Time       | (23) TAXQX      | VCC = 4.5V and 5.5V     | 1     | $-55^{o}C \le T_{A} \le +125^{o}C$   | 5         | -   | ns    |

| High Level Output Voltage              | (24) VOH2       | VCC = 4.5V, IO = -100mA | 1     | -55°C ≤ T <sub>A</sub> ≤<br>+125°C-  | VCC -0.4V | -   | V     |

NOTES:

1. The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design release and upon design changes which would affect these characteristics.

2. Applies to DIP device types only.

3. Applies to LCC device types only.

#### **TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | 1, 7, 9                       |

| PDA                | 100%/5004    | 1                             |

| Final Test         | 100%/5004    | 2, 3, 8A, 8B, 10, 11          |

| Group A            | Samples/5005 | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C & D       | Samples/5005 | 1, 7, 9                       |

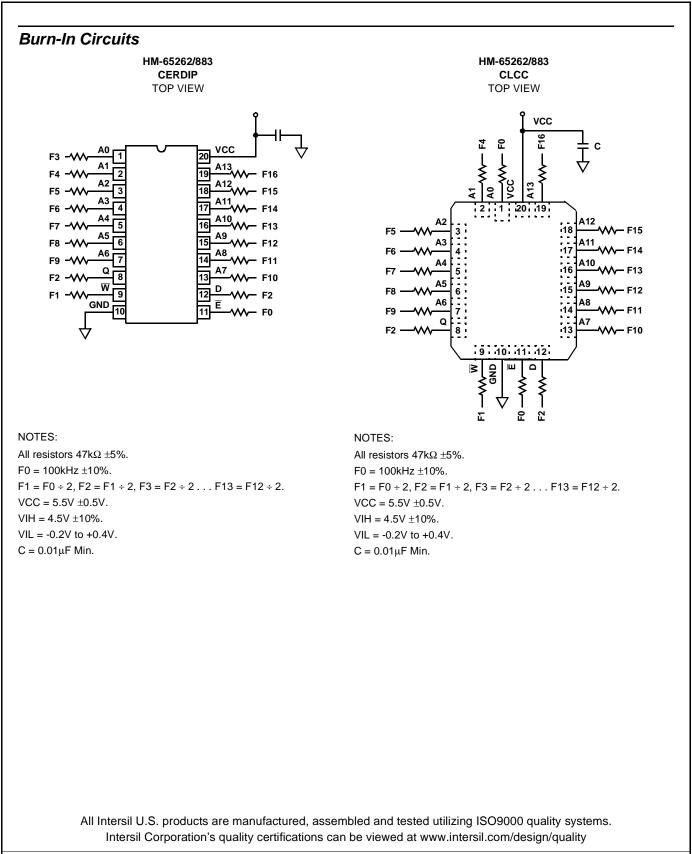

#### HM-65262/883

1. In this mode,  $\overline{W}$  rises after  $\overline{E}$ . If W falls before  $\overline{E}$  by a time exceeding TWLQZ (Max) TELQX (Min), and rises after  $\overline{E}$  by a time exceeding TEHQZ (Max) TWHQZ (Min), then Q will remain in the high impedance state throughout the cycle.

#### FIGURE 4. WRITE CYCLE 2: CONTROLLED BY E (EARLY WRITE)

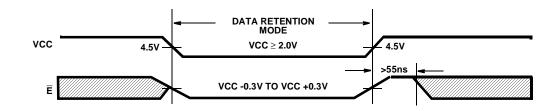

Intersil CMOS RAMs are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:

- 1. Chip Enable  $(\overline{E})$  must be held high during data retention; within VCC to VCC +0.3V.

- 2. On RAMs which have selects or output enables (e.g., S,  $\overline{G}$ ), one of the selects or output enables should be held in the deselected state to keep the RAM outputs high impedance, minimizing power dissipation.

- 3. Inputs which are to be held high (e.g.,  $\overline{E}$ ) must be kept between VCC +0.3V and 70% of VCC during the power up and down transitions.

- 4. The RAM can begin operation >55ns after VCC reaches the minimum operating voltage (4.5V).

FIGURE 5. DATA RETENTION TIMING

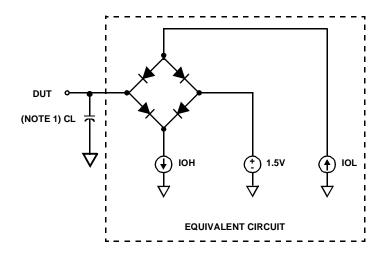

#### **Test Circuit**

#### NOTE:

1. Test head capacitance includes stray and jig capacitance.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time withou notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may resul from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

#### **Die Characteristics**

#### **DIE DIMENSIONS:**

148 x 187 x 19 mils

#### **METALLIZATION:**

Type: Si - Al Thickness: 11kÅ ±2kÅ

#### Metallization Mask Layout

**GLASSIVATION:** Type: SiO<sub>2</sub> Thickness: 8kÅ ±1kÅ

## WORST CASE CURRENT DENSITY: $1.2 \times 10^5 \text{ A/cm}^2$

HM-65262/883 vcc A2 A1 A0 A13 A12 19 A11 A3 202 ĵ BA J 16 A10 A4 Α5 A9 9 12 10 14 A6 A8  $\overline{\mathbf{W}}$ GND Ē D A7 Q