# Intel<sup>®</sup> PXA27x Processor Reference Platform

**User's Guide**

September 2004

Version 1.4

Order Number: 278961-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® PXA27x Processor Reference Platform or Intel® PXA27x Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel, Intel logo, Intel XScale, Intel Wireless MMX, Intel Mobile Scaleable Link, Intel StrataFlash, and Intel SpeedStep are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2004. All Rights Reserved.

| 1 | Introduction and Startup7 |        |                                        |    |  |  |  |  |  |  |  |

|---|---------------------------|--------|----------------------------------------|----|--|--|--|--|--|--|--|

|   | 1.1                       | System | n Overview                             | 7  |  |  |  |  |  |  |  |

|   |                           | 1.1.1  | User Interface                         |    |  |  |  |  |  |  |  |

|   |                           | 1.1.2  | Intel® PXA27x Processor                |    |  |  |  |  |  |  |  |

|   |                           | 1.1.3  | Communications Processor               | 9  |  |  |  |  |  |  |  |

|   |                           | 1.1.4  | Mobile Scalable Link (MSL)             |    |  |  |  |  |  |  |  |

|   |                           | 1.1.5  | Dialog Semiconductor DA9030*           |    |  |  |  |  |  |  |  |

|   |                           | 1.1.6  | Wireless Subsystems                    |    |  |  |  |  |  |  |  |

|   | 1.2                       |        | ent Organization                       |    |  |  |  |  |  |  |  |

|   | 1.3                       |        | Started                                |    |  |  |  |  |  |  |  |

|   | 1.4                       |        | d Documents                            |    |  |  |  |  |  |  |  |

| 2 | llear                     |        | e                                      |    |  |  |  |  |  |  |  |

| _ | 2.1                       |        | nterface                               |    |  |  |  |  |  |  |  |

|   | ۷.۱                       | 2.1.1  | Liquid Crystal Displays (LCD)          |    |  |  |  |  |  |  |  |

|   |                           | 2.1.1  | User Notifications                     |    |  |  |  |  |  |  |  |

|   |                           | 2.1.2  | Touchscreen                            |    |  |  |  |  |  |  |  |

|   |                           | 2.1.3  | Keypad                                 |    |  |  |  |  |  |  |  |

|   |                           | 2.1.4  | Camera                                 |    |  |  |  |  |  |  |  |

|   |                           | 2.1.5  | USB                                    |    |  |  |  |  |  |  |  |

|   |                           | 2.1.0  | Infrared                               |    |  |  |  |  |  |  |  |

|   |                           | 2.1.7  | Secure Digital                         |    |  |  |  |  |  |  |  |

|   |                           | 2.1.0  | Radio/Wireless                         |    |  |  |  |  |  |  |  |

|   |                           | 2.1.9  |                                        |    |  |  |  |  |  |  |  |

|   |                           |        | Wireless LAN (802.11b)                 |    |  |  |  |  |  |  |  |

|   | 2.2                       |        | Input and Voltage Regulation           |    |  |  |  |  |  |  |  |

| • |                           |        |                                        |    |  |  |  |  |  |  |  |

| 3 |                           |        | 'x Processor                           |    |  |  |  |  |  |  |  |

|   | 3.1                       |        | are Description                        |    |  |  |  |  |  |  |  |

|   |                           | 3.1.1  | Flash Memory and Boot ROM              |    |  |  |  |  |  |  |  |

|   |                           | 3.1.2  | Universal Serial Bus On-The-Go         |    |  |  |  |  |  |  |  |

|   |                           | 3.1.3  | IrDA Infrared Transceiver              |    |  |  |  |  |  |  |  |

|   |                           | 3.1.4  | Audio Codecs                           |    |  |  |  |  |  |  |  |

|   |                           | 3.1.5  | Touch-Screen Controllers               |    |  |  |  |  |  |  |  |

|   |                           | 3.1.6  | MultiMediaCard* / Secure Digital* Card |    |  |  |  |  |  |  |  |

|   |                           | 3.1.7  | SIM Connector                          |    |  |  |  |  |  |  |  |

|   |                           | 3.1.8  | Camera                                 | 18 |  |  |  |  |  |  |  |

|   |                           | 3.1.9  | Bluetooth* UART / Radio                |    |  |  |  |  |  |  |  |

|   |                           | 3.1.10 | Baseband                               |    |  |  |  |  |  |  |  |

|   | 3.2                       | _      | mming Guide                            |    |  |  |  |  |  |  |  |

|   |                           | 3.2.1  | Memory Map and Chip Selects            |    |  |  |  |  |  |  |  |

|   |                           | 3.2.2  | Memory-Control Registers               |    |  |  |  |  |  |  |  |

|   |                           | 3.2.3  | LCD-Control Registers                  |    |  |  |  |  |  |  |  |

|   |                           | 3.2.4  | Intel® PXA27x Processor Pin Usage      |    |  |  |  |  |  |  |  |

|   |                           | 3.2.5  | Programming Application Flash Memory   |    |  |  |  |  |  |  |  |

|   |                           | 3.2.6  | Flash Memory                           | 33 |  |  |  |  |  |  |  |

#### **Contents**

| 4 | Com   | munication           | ons Processor and Audio Concept                                        | 35 |

|---|-------|----------------------|------------------------------------------------------------------------|----|

|   | 4.1   | Commu                | nications Processor                                                    | 35 |

|   |       |                      | Communications Processor Frequency Settings                            |    |

|   |       | 4.1.2                | Communications Processor Pin Usage                                     | 35 |

|   | 4.2   | Intel <sup>®</sup> P | XA27x Processor Reference Platform GSM Radio                           | 40 |

|   |       |                      | Radio Description                                                      |    |

|   |       |                      | Antenna                                                                |    |

|   |       |                      | Radio Interface Requirements                                           |    |

|   | 4.3   | Commu                | nications Processor Boot Loader Application                            | 43 |

|   |       | 4.3.1                | Activating the Boot Loader                                             | 43 |

|   |       | 4.3.2                | Connecting the Boot Loader                                             | 44 |

|   |       | 4.3.3                | Transfer Files into the Communications Processor                       |    |

|   |       |                      | Load\Save File List                                                    |    |

|   | 4.4   |                      | Concept                                                                |    |

|   | 4.5   |                      | cenarios                                                               |    |

|   |       |                      | Basic Voice Call                                                       |    |

|   |       |                      | Voice Call with Bluetooth* Earphone                                    |    |

|   |       |                      | Endless Recording                                                      |    |

|   |       |                      | Voice Call with MP3 Play to Near End                                   |    |

|   |       |                      | Voice Call with MP3 Play to Near and Far End                           |    |

|   |       | 4.5.6                | Recording Near End Notes During Voice Call                             | 59 |

| 5 | Intel | ® PXA27x             | Processor Reference Platform System Power Management                   | 61 |

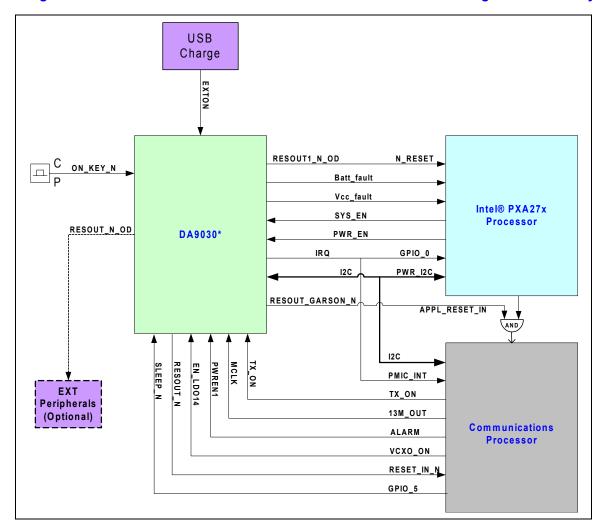

|   | 5.1   | DA9030               | )* Definition                                                          | 61 |

|   |       |                      | DA9030* Connectivity to the Intel® PXA27x Processor Reference Platform |    |

|   | 5.2   |                      | ree                                                                    |    |

|   |       | 5.2.1                | Clock Tree Functional Description                                      | 69 |

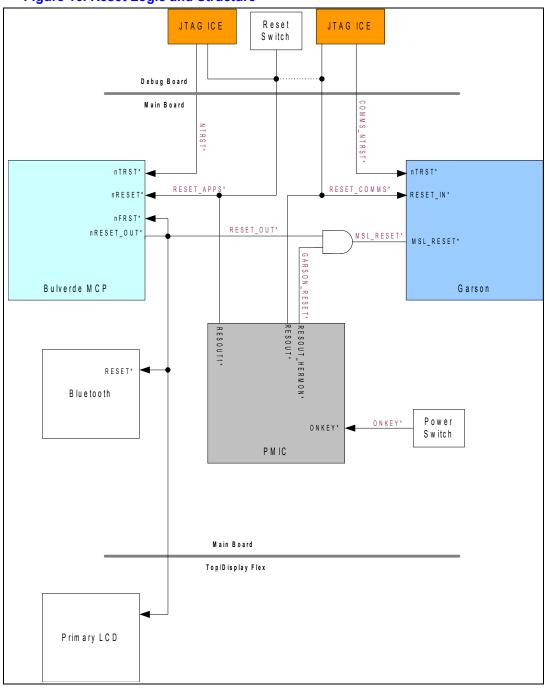

|   | 5.3   | System               | Reset                                                                  | 71 |

|   |       | 5.3.1                | System Power Up and Reset Sequence                                     | 72 |

|   |       |                      | Initiating Reset                                                       |    |

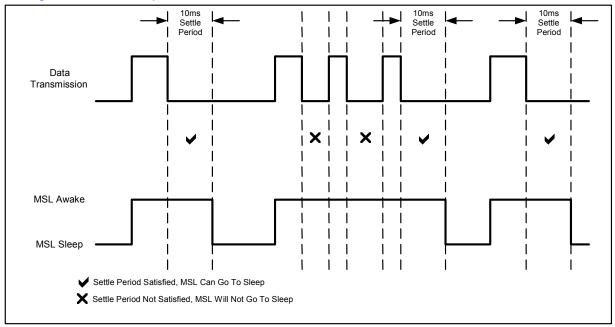

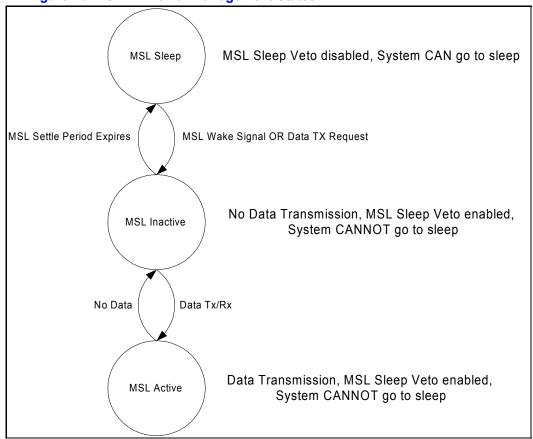

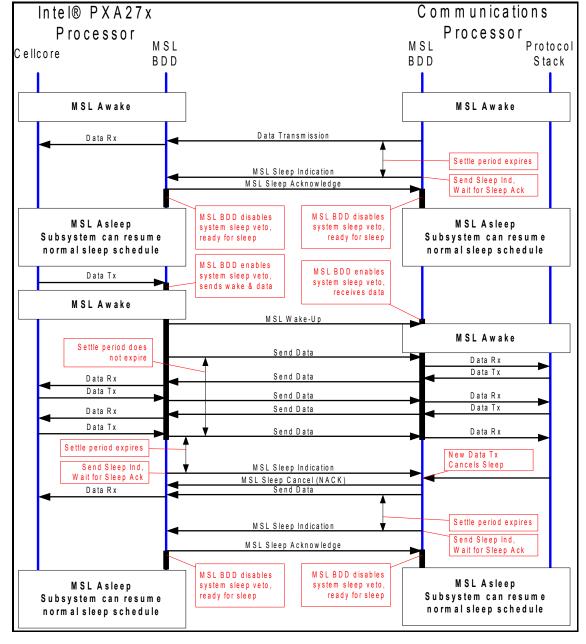

|   | 5.4   | Two-Ch               | ip System Power Management using MSL                                   | 74 |

|   |       |                      | General                                                                |    |

|   |       |                      | MSL Power Management                                                   |    |

|   |       |                      | MSL Wake                                                               |    |

|   |       |                      | Power Management During a Call (Voice and Data)                        |    |

|   | 5.5   |                      | Consumption Approximations                                             |    |

|   |       | 5.5.1                | Assumptions and Modes Definitions                                      | 79 |

| 6 | Intel | ® PXA27x             | Processor Reference Platform Wireless Subsystems                       | 89 |

|   | 6.1   | Bluetoo              | th*                                                                    | 89 |

|   |       | 6.1.1                | Supported Profiles and Applications                                    |    |

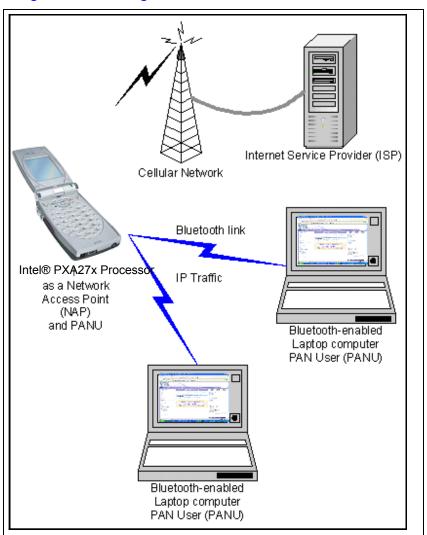

|   |       | 6.1.2                | Personal Area Networking (PAN)                                         |    |

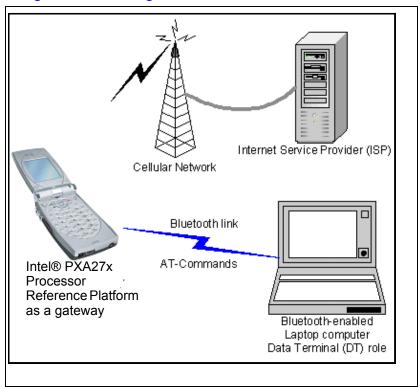

|   |       | 6.1.3                | Dial-Up Network (DUN)                                                  |    |

|   |       | 6.1.4                | Intel® PXA27x Processor Reference Platform Bluetooth* Concept          |    |

|   |       | 6.1.5                | Philips TrueBlue* (BGB201)                                             | 92 |

|   |       | 6.1.6                | BGB201 Hardware Interfaces with Intel® PXA27x Processor Reference Plat |    |

|   |       | 6.1.7                | BGB20 Power Consumption                                                | 94 |

|   |       | 6.1.8                | Antenna Filter Definition                                              | 94 |

|   |       | 6.1.9                | Bluetooth* Antenna Design                                              |    |

|   |       | 6.1.10               | BGB201 Power Modes                                                     | 95 |

|   |          | 6.2   | 802.11    | b WLAN                                                                                              | 95       |

|---|----------|-------|-----------|-----------------------------------------------------------------------------------------------------|----------|

|   |          |       | 6.2.1     | Intel® PXA27x Processor Reference Platform WLAN Concept                                             |          |

|   |          |       | 6.2.2     | Philips SA2443 and BGW100SA2443 Hardware Interfaces with Intel® PXA27x Processor Reference Platform | 95       |

|   |          |       | 6.2.3     |                                                                                                     |          |

|   |          |       | 6.2.4     | 802.11b Power Consumption                                                                           | 96       |

| 7 |          | Gloss | sarv      |                                                                                                     | 99       |

|   |          | Olos. | sar y     |                                                                                                     | 55       |

|   |          |       |           |                                                                                                     |          |

|   |          |       |           |                                                                                                     |          |

|   | _        | ures  |           |                                                                                                     |          |

|   | 1        |       |           | 7x Processor Reference Platform Block Diagram                                                       |          |

|   | 2        |       |           | 7x Processor Reference Platform Form Factor Overview                                                |          |

|   | 3        |       |           | 7x Processor Reference Platform Design Keypad Logic                                                 |          |

|   | 4        |       |           | iagram                                                                                              |          |

|   | 5        |       |           | r System Overview                                                                                   |          |

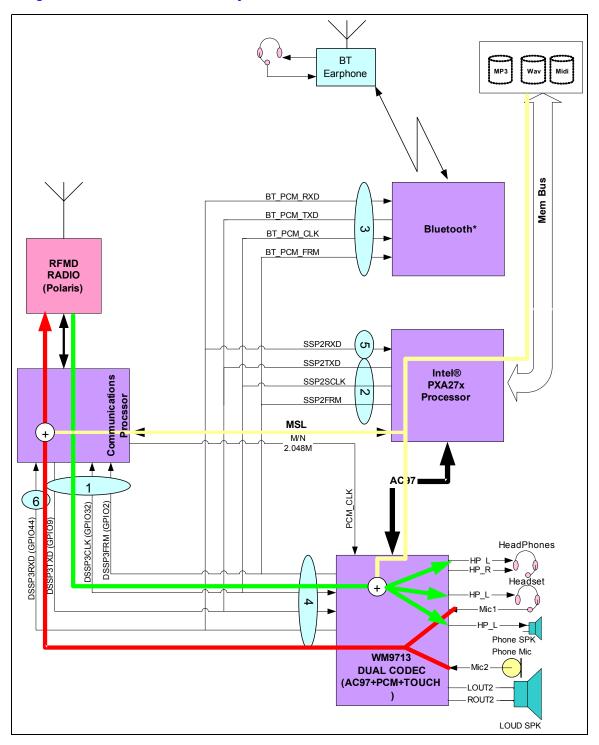

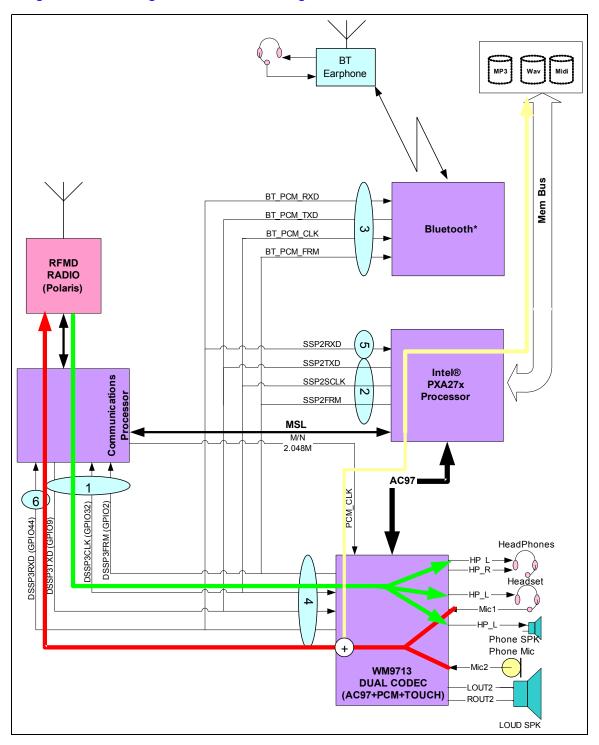

|   | 6        |       |           | Audio Concept and Hardware Connectivity                                                             |          |

|   | 7        |       |           | : Call                                                                                              |          |

|   | 8        |       |           | vith Bluetooth*                                                                                     |          |

|   | 9        |       |           | cording                                                                                             |          |

|   | 10       |       |           | ack to Near End During a Call                                                                       |          |

|   | 11       |       |           | vith MP3 Play to Near and Far Ends                                                                  |          |

|   | 12<br>13 | Rec   | oraing r  | Near End Notes During Voice Call<br>=> Intel <sup>®</sup> PXA27x Processor USB OTG Configuration    | 59<br>65 |

|   | 14       | DAS   | )U3U <-   | => Intel® PXA27x Processor Reference Platform Logical Connectivity                                  | 00<br>67 |

|   | 15       | Into  | 1® DY A 2 | 27x Processor Reference Platform Clock Flow                                                         | 07<br>60 |

|   | 16       |       |           | and Structure                                                                                       |          |

|   | 17       |       | _         | Settle Period                                                                                       |          |

|   | 18       |       |           | wer Management States                                                                               |          |

|   | 19       |       |           | ver Management Sequence                                                                             |          |

|   | 20       |       |           | Models                                                                                              |          |

|   | 21       |       |           | Model                                                                                               |          |

|   | 22       |       |           | GB201                                                                                               |          |

|   | 23       |       |           | CM Short Frame Sync Format                                                                          |          |

|   | 24       |       |           | wer Consumption                                                                                     |          |

|   |          |       |           | ·                                                                                                   |          |

| _ | ah       | les   |           |                                                                                                     |          |

|   |          |       |           |                                                                                                     | 40       |

|   | 1        |       |           | cuments                                                                                             |          |

|   | 2        |       |           | 7x Processor Reference Platform Keypad Logic                                                        |          |

|   | 3<br>4   | Pny   | SICAI AO  | dresses and Chip Selects                                                                            | 19       |

|   | 4<br>5   | Con   | 1° PXA2   | ations Processor Pin Usage for the Intel® PXA27x Processor Reference Platform                       | 29<br>25 |

|   | 6        |       |           | ain Components                                                                                      |          |

|   | 7        |       |           | 27x Processor Reference Platform <=> DA9030* Domains Allocation                                     |          |

|   | 8        |       |           | 17x Processor Reference Platform Clock Allocation                                                   |          |

|   | 9        |       |           | 27x Processor Reference Platform Reset Allocation                                                   |          |

|   | 10       |       |           | iled Results                                                                                        |          |

|   | 11       |       |           | s Summary                                                                                           |          |

|   | 12       |       |           | ed Results                                                                                          |          |

|   |          |       |           |                                                                                                     |          |

#### Contents

| 13 | Voice Mode Results Summary          | 83 |

|----|-------------------------------------|----|

| 14 | Voice Mode Detailed Results         | 83 |

|    | Voice Mode Results Using Bluetooth* |    |

|    | GPRS Data Mode Results Summary      |    |

|    | GPRS Data Mode Detailed Results     |    |

| 18 | 802.11 Data Mode Results Summary    | 86 |

|    | 802.11 Data Mode Detailed Results   |    |

|    | UART Signal Description             |    |

|    | Bluetooth* PCM Signal Description   |    |

|    | BGB201 Power Consumption            |    |

|    | WLAN Signals                        |    |

# **Revision History**

| Date           | Revision | Description             |

|----------------|----------|-------------------------|

| April 2004     | 001      | Initial Version         |

| May 2004       | 002      | Updates for version 1.2 |

| September 2004 | 003      | Updates for version 1.4 |

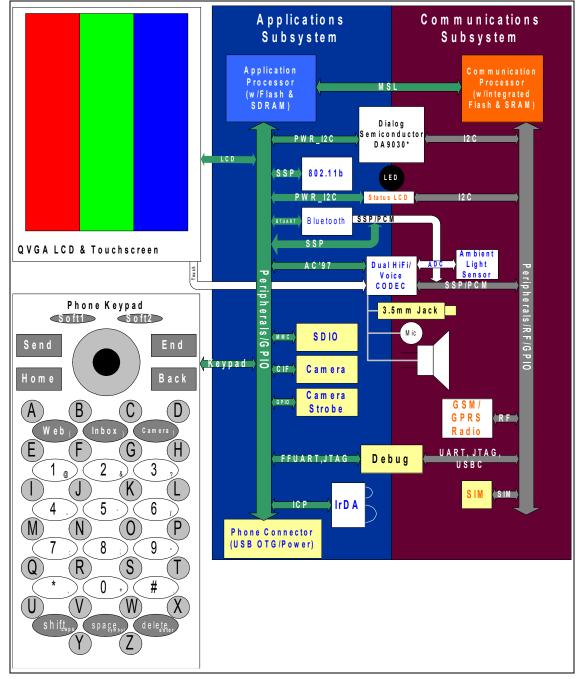

## 1.1 System Overview

The Intel<sup>®</sup> PXA27x Processor Reference Platform includes numerous peripherals that are available to the end user. The feature set consists of:

- High-performance processor, Intel<sup>®</sup> PXA27x Processor (PXA27x processor), which handles

the running of a full-featured operating system (FFOS) and the man-machine interface

peripherals (keyboards, LCD, etc.)

- High Performance communications processor, which handles the GSM/GPRS cellular protocol stack, the control for the GSM/GPRS radio, and the SIM interface

- Quad-band GSM cellular radio, supporting GPRS

- Bluetooth\* radio, Bluetooth 1.1 compliant

- Wireless LAN 802.11b baseband and radio

- 240x320 pixel QVGA, 16 bit-per-pixel main LCD

- Five-line sub-LCD character display

- Alphanumeric keypad with dedicated alphabet keys, soft keys, and five-way directional pad

- High-fidelity stereo audio

- Notification LED

- Integrated 1.3 Megapixel CMOS camera and flash

- MMC/SDIO port

- USB client connector with On-The-Go (OTG) support

- IrDA infrared transceiver with CIR capability

- Housing which supports "Flip-n-Twist" operation for PDA-style or phone-style usage

**Note:** Changing firmware or software, adding or removing hardware may cause damage to the Intel<sup>®</sup> PXA27x Processor Reference Platform.

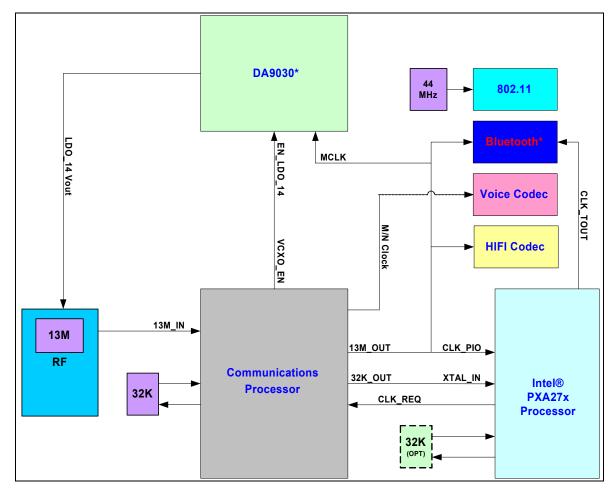

Figure 1. Intel® PXA27x Processor Reference Platform Block Diagram

## 1.1.1 User Interface

The user interface is comprised of a touch screen, keypad, and two LCDs that support data applications and cell-phone communications.

## 1.1.2 Intel® PXA27x Processor

Intel® PXA27x Processor (PXA27x processor) adds several new features that help enable wireless devices to capture high quality images, extend battery life, and deliver fast multimedia performance. It is the third implementation of the Intel XScale® microarchitecture family, featuring an improved LCD controller, expanded card interface, and more conservative power management features. It is also the first processor in the family to include a baseband interface, integrated SRAM, a camera capture interface, scalable core frequencies and voltages, USB On-The-Go (OTG), full SDIO support, and an Intel coprocessor. The coprocessor extends the Intel XScale® microarchitecture capabilities by adding Intel® Wireless MMX<sup>TM</sup> functionality and additional audio and video processing operations.

#### 1.1.3 Communications Processor

The communications processor is the first Intel<sup>®</sup> Personal Internet Client Architecture (Intel<sup>®</sup> PCA) cellular processor to be fully integrated in a high-performance, power efficient Intel XScale<sup>®</sup> core for implementing wireless protocols with an Intel<sup>®</sup> Micro Signal Architecture (Intel<sup>®</sup> MSA) GSM/GPRS baseband processor. This provides wireless modem functionality along with on-die 0.13mm Flash memory and SRAM. The MSA core is a dual multiply and accumulate (MAC) digital signal processor running at 104 MHz. This design enables the development of powerful, cost-effective, advanced third-generation wireless devices capable of running rich data applications.

The PXA27x processor and the communications processor communicate with each other through the Intel<sup>®</sup> Mobile Scalable Link (Intel<sup>®</sup> MSL), a high performance baseband interface providing throughput up to 192 Mbps.

## 1.1.4 Mobile Scalable Link (MSL)

The communications processor has an RF connection to the cellular system and is connected to the PXA27x processor using a standard link called the MSL. The MSL hardware is capable of running up to 52 MHz or has a data throughput of 192 Mbps, and it is used mainly for exchanging data packets between subsystems.

## 1.1.5 Dialog Semiconductor DA9030\*

The Intel® PXA27x Processor Reference Platform receives its power primarily from the Dialog Semiconductor DA9030\*. The DA9030\* controls battery charging and manages power supplies.

## 1.1.6 Wireless Subsystems

The wireless subsystem supports headset, hands-free, personal area network, dial-up network, and object push profiles using Bluetooth\* technology.

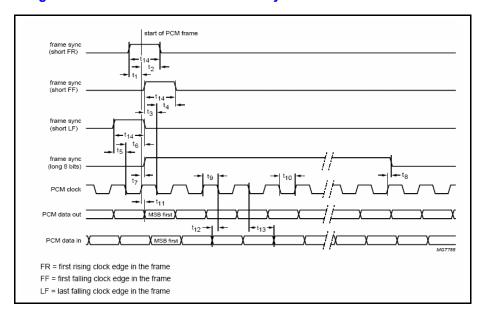

The Bluetooth\* baseband+radio chip is connected using a Universal Asynchronous Receiver Transmitter (UART) connection; it also has serial Pulse Coded Modulation (PCM) interfaces to both the PXA27x processor and the communications processor. The PCM connection to the PXA27x processor is used during audio scenarios handled by the PXA27x processor, such as voice memo pad (VMP), voice recognition (VR), calendar/incoming e-mail alerts, and so on. The direct connection to the communications processor is used during cellular voice calls.

The wireless LAN (WLAN) allows mobile users to connect to a LAN through a wireless radio connection. WLAN enables higher productivity, functionality, and convenience by untethering the user from any single wired port and allowing the user to access his databases and services remotely.

## 1.2 Document Organization

This user's guide contains the following chapters:

Chapter 1, "Introduction and Startup" provides an introduction of the Intel® PXA27x Processor Reference Platform.

Chapter 2, "User Interface" describes the system overview and user interfaces.

Chapter 3, "Intel® PXA27x Processor" describes the PXA27x processor and provides instructions for its use.

Chapter 4, "Communications Processor and Audio Concept" describes the communications processor and provides instructions for its use.

Chapter 5, "Intel® PXA27x Processor Reference Platform System Power Management" describes the Intel® PXA27x Processor Reference Platform power management design and Intel® Mobile Scalable Link (MSL).

Chapter 6, "Intel® PXA27x Processor Reference Platform Wireless Subsystems" describes the wireless subsystem components.

## 1.3 Getting Started

The Intel® PXA27x Processor Reference Platform *Quick Start Guide*, packed with the Intel® PXA27x Processor Reference Platform, contains a current packing list and instructions for setting up and starting the system. The Quick Start Guide also contains updates that became available after the publication of this document.

## 1.4 Related Documents

Table 1. Related Documents

| Item                                                                        | Number |

|-----------------------------------------------------------------------------|--------|

| Intel® PXA27x Processor Reference Platform Schematics                       | 278877 |

| Intel® PXA27x Processor Reference Platform Parts List                       | 278879 |

| Intel® PXA27x Processor Reference Platform Quick Start Guide                | 278982 |

| Diagnostics for the Intel® PXA27x Processor Reference Platform User's Guide | 278983 |

| Intel® PXA27x Processor Family Developer's Manual                           | 280000 |

# **User Interface**

This chapter describes the Intel® PXA27x Processor Reference Platform hardware.

- Section 2.1 User Interface

- Section 2.2 Power Input and Voltage Regulation

## 2.1 User Interface

Figure 2. Intel® PXA27x Processor Reference Platform Form Factor Overview

## 2.1.1 Liquid Crystal Displays (LCD)

The Intel® PXA27x Processor Reference Platform includes a primary and secondary (status) LCD.

## 2.1.1.1 Primary LCD

The primary LCD is capable of 16-bit color depth, 240x320 pixel resolution, and a native portrait orientation. Since the Intel<sup>®</sup> PXA27x Processor Reference Platform is 'flip' style, the primary LCD is not required to be 'always-on'.

## 2.1.1.2 Secondary (Status) LCD

The secondary (status) LCD displays the phone and call status information. It is operational when the phone is 'closed-flip' and powered down when the phone is 'open-flip'.

#### 2.1.2 User Notifications

## 2.1.2.1 Light Emitting Diode (LED)

The design includes an LED for visual user notifications. The control of the blink rate and duty cycles of this LED is handled autonomously by the LED modulator controller within the Dialog Semiconductor DA9030\*.

#### 2.1.2.2 Silent/Audible Notifications

For silent and audible user notifications, the design utilizes a multi-function speaker.

#### 2.1.2.2.1 Silent Alert\* Motor Control

A test point provides for controlling an external Silent Alert\* vibrator motor.

#### 2.1.3 Touchscreen

The touchscreen is mounted on the primary LCD. For operating systems that do not support a touch screen, the touch screen digitizer can be disabled or ignored.

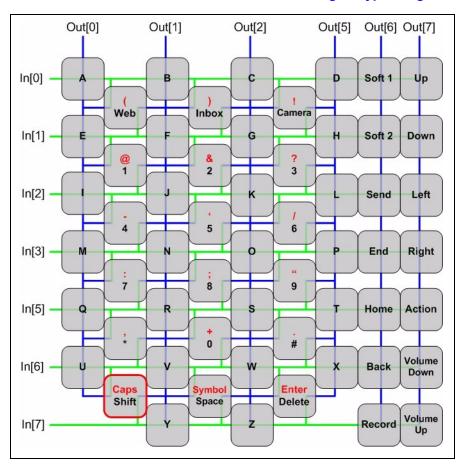

## 2.1.4 Keypad

The keypad supports numeric entry capabilities, dedicated alphabet text entry capabilities, and navigation features.

Figure 3 shows the keypad logic.

Figure 3. Intel<sup>®</sup> PXA27x Processor Reference Platform Design Keypad Logic

*Note:* The keys in [] relate to the PXA27x processor GPIO keypad matrix.

Table 2. Intel® PXA27x Processor Reference Platform Keypad Logic

|     | Out0 | Out1 | Out2 | Out5 | Out6   | Out7     |

|-----|------|------|------|------|--------|----------|

| In0 | Α    | В    | С    | D    | soft1  | up       |

| In1 | E    | F    | G    | Н    | soft2  | down     |

| In2 | I    | J    | К    | L    | send   | left     |

| In3 | М    | N    | 0    | Р    | end    | right    |

| In5 | Q    | R    | S    | Т    | home   | action   |

| In6 | U    | V    | W    | х    | back   | vol down |

| In7 |      | Υ    | Z    |      | record | vol up   |

|         | Out0&Out1 | Out1&Out2 | Out2&Out5 |

|---------|-----------|-----------|-----------|

| In0&In1 | Web       | Inbox     | Camera    |

| In1&In2 | 1         | 2         | 3         |

| In2&In3 | 4         | 5         | 6         |

| ln3&ln5 | 7         | 8         | 9         |

| In5&In6 | *         | 0         | #         |

| In6&In7 | shift     | space     | delete    |

| Shifted | Out0&Out1 | Out1&Out2 | Out2&Out5 |

|---------|-----------|-----------|-----------|

| In0&In1 | (         | )         | !         |

| In1&In2 | @         | &         | ?         |

| In2&In3 | -         | 1         | 1         |

| ln3&ln5 | :         | ;         | "         |

| In5&In6 | ,         | +         |           |

| In6&In7 | caps      | symbol    | enter     |

#### 2.1.5 **Camera**

The camera utilizes a 1.3 megapixel resolution CMOS imager that connects to the PXA27x processor's camera interface (for pixel data transfer) and I<sup>2</sup>C interface (for command and control). It includes an integrated dual-mode, camera strobe/flash which contains a dimmer always-on mode for video capture and a flashlight capability and a brighter strobe mode for still picture capture capability. The camera can be used for both video conferencing and 'point-n-shoot' operation.

#### 2.1.6 USB

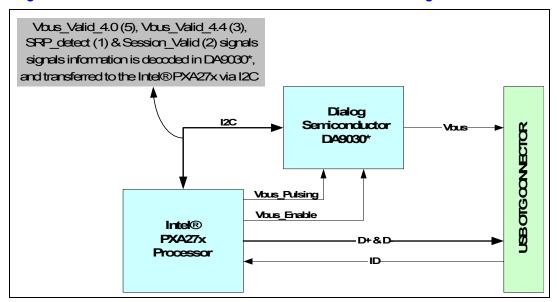

The applications subsystem supports the USB OTG controller and the onboard transceivers in the PXA27x processor. It connects to other devices via an on-board mini type AB USB connector. A supply on the DA9030\* generates the USB\_VBUS supply.

#### 2.1.7 Infrared

An IrDA transceiver is capable of supporting both serial infrared (SIR) and consumer infrared (CIR) operations.

## 2.1.8 Secure Digital

One on-board, full size secure digital socket supports a four-bit data bus width and SDIO operation.

#### 2.1.9 Radio/Wireless

A quad band GSM/GPRS radio is supported for wireless communication.

#### 2.1.10 Bluetooth\*

The applications subsystem supports an onboard Bluetooth\* baseband and RF module that comply with the Bluetooth 1.1 standard. The physical interfacing includes a PXA27x processor UART for control/data and a PCM link for Voice.

## 2.1.11 Wireless LAN (802.11b)

The applications subsystem supports an onboard 802.11b baseband and RF module. The physical interfacing utilizes a PXA27x processor SPI port for control and data.

## 2.2 Power Input and Voltage Regulation

The system derives its power from a single-cell lithium ion battery pack which mates with connector J5. The battery voltage is regulated down into the various power domains for the board by the DA9030\*. Switch SW4 asserts the DA9030\* ONKEY\* signal, powering up the board and generating an interrupt from the DA9030\* to the PXA27x processor. A DA9030\* watchdog timer

## User Interface

is also started at this point. Software running on the PXA27x processor must disable this watchdog within eight seconds through a register write to the DA9030\*. If eight seconds pass before this is done, the DA9030\* will shut down.

# Intel<sup>®</sup> PXA27x Processor

This chapter includes the following sections:

- Section 3.1 Hardware Description

- Section 3.2 Programming Guide

## 3.1 Hardware Description

Intel® PXA27x Processor (PXA27x processor) includes the following features.

- Section 3.1.1 Flash Memory and Boot ROM

- Section 3.1.2 Universal Serial Bus On-The-Go

- Section 3.1.3 IrDA Infrared Transceiver

- Section 3.1.4 Audio Codecs

- Section 3.1.5 Touch-Screen Controllers

- Section Keypad

- Section 3.1.6 MultiMediaCard\* / Secure Digital\* Card

- Section 3.1.7 SIM Connector

- Section 3.1.8 Camera

- Section 3.1.9 Bluetooth\* UART / Radio

- Section 3.1.10 Baseband

## 3.1.1 Flash Memory and Boot ROM

The Intel<sup>®</sup> PXA271 Processor (PXA271 processor) contains 32 MBytes of Intel StrataFlash<sup>®</sup> memory and 32 MBytes of Low Power SDRAM.

The Intel® PXA27x Processor Reference Platform platform utilizes the PXA271 processor which uses chip select nCS[0], and boots from internal flash memory.

For more information on programming flash memory, see the JFlash release notes or the Intel<sup>®</sup> XDB JTAG Debugger release notes.

Additionally, the PXA271 processor has internal SDRAM, typically internally connected to chip select nSDCS[0].

#### 3.1.2 Universal Serial Bus On-The-Go

The PXA27x processor contains a USB device controller that complies with the USBC 1.1 specification. It can also be used to produce A- and B-device, On-The-Go operations as specified in the On-The-Go supplement to the USB specification.

#### 3.1.3 IrDA Infrared Transceiver

The main board contains a dual-mode Agilent IrDA transceiver capable of slow infrared (SIR) and consumer infrared (CIR) protocols. For more information about the transceiver's operation, refer to the Agilent HSDL-3002 data sheet.

The IrDA transceiver uses the PXA27x processor Infrared Communication Port.

#### 3.1.4 Audio Codecs

A dual codec Wolfson WM9713 is included on the Intel<sup>®</sup> PXA27x Processor Reference Platform to produces HiFi audio over the AC'97 interface and a voice band codec over PCM.

#### 3.1.5 Touch-Screen Controllers

The touchscreen controller is built into the Wolfson WM9713. This is a four wire touch panel controller supporting position measurements.

## Keypad

The panel-mounted Fastap\* keypad uses the PXA27x processor Keypad Interface, mapped as follows:

The 55-button, 6x7 matrix keypad maps to the PXA27x processor matrix keypad signals MKIN<7:0> and MKOUT<7:0>.

## 3.1.6 MultiMediaCard\* / Secure Digital\* Card

The PXA27x processor contains a MultiMediaCard\* (MMC), Secure Digital\* (SD) card, and Secure Digital I/O controller. The main board socket supports both types of cards.

#### 3.1.7 SIM Connector

The Subscriber Identity Module interface is a primary device and communications interface for a GSM mobile handset. The SIM interface also supports communication with SmartCards\*, which are used in many applications including e-commerce. For the SIM Connector module, both 3.0 V and 1.8 V SIM cards are compatible.

#### 3.1.8 **Camera**

The camera capture interface acquires data and control signals from the CMOS sensor. An Omnivision OV9640\*, revision 3, 1.3 Mpixel camera module is standard.

#### 3.1.9 Bluetooth\* UART / Radio

A Philips BGB201 is connected to the PXA27x processor Bluetooth\* UART.

#### **3.1.10** Baseband

The baseband runs at 1.2 volts nominally and interfaces with the Intel<sup>®</sup> MSL module in the PXA27x processor.

## 3.2 Programming Guide

- Section 3.2.1 Memory Map and Chip Selects

- Section 3.2.2 Memory-Control Registers

- Section 3.2.3 LCD-Control Registers

- Section 3.2.5 Programming Application Flash Memory

- Section 3.2.6 Flash Memory

## 3.2.1 Memory Map and Chip Selects

Table 3 describes the physical addresses and active-low chip selects for the PXA27x processor. For a complete listing of the PXA27x processor memory map, refer to the Memory Controller chapter in the *Intel*<sup>®</sup> *PXA27x Processor Family Developer's Manual*.

#### Table 3. Physical Addresses and Chip Selects (Sheet 1 of 2)

| Function                                                                              | Chip<br>Select | Size       | Base Address | Ending<br>Address |

|---------------------------------------------------------------------------------------|----------------|------------|--------------|-------------------|

| Boot ROM flash memory                                                                 | nCS0           | 32 Mbytes  | 0x0000_0000  | 0x03FF_FFFF       |

| reserved                                                                              | nCS1           | 64 Mbytes  | 0x0400_0000  | 0x07FF_FFFF       |

| reserved                                                                              | nCS2           | 6 Mbytes   | 0x0800_0000  | 0x0BFF_FFFF       |

| reserved                                                                              | nCS3           | 64 Mbytes  | 0x0C00_0000  | 0x0FFF_FFFF       |

| Ethernet controller (Non-form factor Intel® PXA27x Processor Reference Platform only) | nCS4           | 64 Mbytes  | 0x1000_0000  | 0x13FF_FFFF       |

| reserved                                                                              | nCS5           | 64 Mbytes  | 0x1400_0000  | 0x17FF_FFFF       |

| reserved                                                                              | _              | 64 Mbytes  | 0x1800_0000  | 0x1BFF_FFFF       |

| reserved                                                                              | _              | 64 Mbytes  | 0x1C00_0000  | 0x1FFF_FFFF       |

| reserved                                                                              | _              | 256 Mbytes | 0x2000_0000  | 0x2FFF_FFFF       |

| reserved                                                                              | _              | 256 Mbytes | 0x3000_0000  | 0x3FFF_FFFF       |

| Peripherals memory-mapped registers                                                   | _              | 64 Mbytes  | 0x4000_0000  | 0x43FF_FFFF       |

| LCD memory-mapped registers                                                           | _              | 64 Mbytes  | 0x4400_0000  | 0x47FF_FFFF       |

| Memory Control memory-mapped registers                                                | _              | 64 Mbytes  | 0x4800_0000  | 0x4BFF_FFFF       |

| USB host                                                                              | _              | 64 Mbytes  | 0x4C00_0000  | 0x4FFF_FFFF       |

| reserved                                                                              | _              | 64 Mbytes  | 0x5000_0000  | 0x53FF_FFFF       |

| reserved                                                                              | _              | 64 Mbytes  | 0x5400_0000  | 0x57FF_FFFF       |

| Internal memory control                                                               | _              | 64 Mbytes  | 0x5800_0000  | 0x5BFF_FFFF       |

Table 3. Physical Addresses and Chip Selects (Sheet 2 of 2)

| Function                | Chip<br>Select | Size       | Base Address | Ending<br>Address |

|-------------------------|----------------|------------|--------------|-------------------|

| Internal memory storage | _              | 256 K      | 0x5C00_0000  | 0x5FFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0x6000_0000  | 0x6FFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0x7000_0000  | 0x7FFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0x8000_0000  | 0x8FFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0x9000_0000  | 0x9FFF_FFFF       |

| SDRAM                   | nSDCS0         | 32 Mbytes  | 0xA000_0000  | 0xA3FF_FFFF       |

| reserved                | nSDCS1         | 64 Mbytes  | 0xA400_0000  | 0xA7FF_FFFF       |

| reserved                | nSDCS2         | 64 Mbytes  | 0xA800_0000  | 0xABFF_FFFF       |

| reserved                | nSDCS3         | 64 Mbytes  | 0xAC00_0000  | 0xAFFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0xB000_0000  | 0xBFFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0xC000_0000  | 0xCFFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0xD000_0000  | 0xDFFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0xE000_0000  | 0xEFFF_FFFF       |

| reserved                | _              | 256 Mbytes | 0xF000_0000  | 0xFFFF_FFFF       |

## 3.2.2 Memory-Control Registers

The following subsections provide the recommended settings for the memory-control registers. These settings are required for proper operation of the PXA27x processor in a stand-alone application *or* in combination with the main board. The following registers must be configured:

- Section 3.2.2.1 SDRAM Configuration Register (MDCNFG)

- Section 3.2.2.2 SDRAM Mode Register Set Configuration Register (MDMRS)

- Section 3.2.2.3 SLP SDRAM Mode Register Set Configuration Register (MDMRSLP)

- Section 3.2.2.4 SDRAM Memory Device Refresh Register (MDREFR)

- Section 3.2.2.5 Static Memory Control Register 0 (MSC0)

- Section 3.2.2.6 Static Memory Control Register 1 (MSC1)

- Section 3.2.2.7 Static Memory Control Register 2 (MSC2)

- Section 3.2.2.8 Expansion Memory Configuration Register (MECR)

- Section 3.2.2.9 Synchronous Static Memory Configuration Register (SXCNFG)

- Section 3.2.2.10 Expansion Memory Timing Configuration Registers: MCMEM0, MCMEM1, MCATT0, MCATT1, MCIO0, MCIO1

The recommended settings for the memory-control registers presume the following:

• Memory-controller clock frequency (CLK\_MEM) = 91 MHz, based upon the value of L in the PXA27x processor Core Clock Configuration Register. See the Clocks and Power Manager chapter in the *Intel*® *PXA27x Processor Family Developer's Manual*.

- 32 MB of SDRAM installed, mapped as 1 device, 13 row-address bits, 9 column-address bits, and 16 data bits. Extended Mode Register in the SDRAMs set as follows:

- All SDRAM banks are maintained in self-refresh (all PASR bits clear).

- Temperature-compensated refresh (TCR) is set for 45° C.

To set these SDRAM characteristics for each device, refer to the following information sources:

- **SDRAM device registers:** PXA271 processor with 32 MBytes of SDRAM.

- Accessing the SDRAM registers: PXA27x processor Special Low-Power SDRAM Mode Register Set Configuration register (see the Memory Controller chapter in the Intel® PXA27x Processor Family Developer's Manual)

It may be necessary to adjust the recommended settings, depending on the following:

- Desired clock sources for example, core PLL instead of internal or external processor oscillator. See the Clocks and Power Manager chapter in the *Intel*® *PXA27x Processor Family Developer's Manual*.

- Run- and turbo-mode frequencies (MEM\_CLK depends on the core run-mode frequency in the PXA27x processor Core Clock Configuration Register. See the Clocks and Power Manager chapter in the *Intel*® PXA27x Processor Family Developer's Manual.)

- Use of fast-bus mode (see the Clocks and Power Manager chapter in the *Intel*® *PXA27x Processor Family Developer's Manual*)

- Expansion-card presence and memory-bus configuration (PXA27x processor Static Memory Control Register 2 see the Memory Controller chapter in the *Intel® PXA27x Processor Family Developer's Manual.*)

- Use of SDRAM extended low-power modes refer to the following information sources:

- **SDRAM device registers:** Refer to the *Intel*® *PXA27x Processor Family Developer's Manual*.

- Accessing the SDRAM registers: PXA27x processor Special Low-Power SDRAM Mode Register Set Configuration register (see the Memory Controller chapter in the Intel® PXA27x Processor Family Developer's Manual).

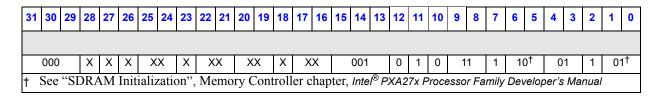

## 3.2.2.1 SDRAM Configuration Register (MDCNFG)

#### **MDCNFG Recommended Settings:**

## 3.2.2.2 SDRAM Mode Register Set Configuration Register (MDMRS)

#### **MDMRS Recommended Settings:**

| 31 | 30                                                                                                                         | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| S  | Stand-alone Intel® PXA27x Processor and Intel® PXA27x Processor with Intel® PXA27x Processor Reference Platform main board |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 0  | 0 XXXX XXXX 011 0 010 0 0000 0000 <sup>†</sup> 011 0 010                                                                   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| †  | † Burst reads, burst writes                                                                                                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

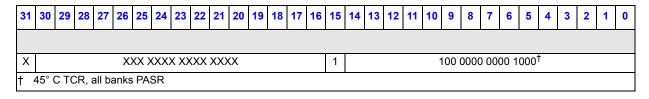

## 3.2.2.3 SLP SDRAM Mode Register Set Configuration Register (MDMRSLP)

#### **MDMRSLP Recommended Settings:**

## 3.2.2.4 SDRAM Memory Device Refresh Register (MDREFR)

When configuring this register, follow the procedure recommended in the *Intel*<sup>®</sup> *PXA27x Processor Family Developer's Manual* for initializing SDRAM.

#### **MDREFR Recommended Settings:**

#### NOTES:

- 1. SDCLK[0] = MEMCLK / 4

- 2. Auto Power-Down (APD) enabled for all except synchronous flash-memory devices.

For more information on the APD function, see the MDREFR register description in the Memory Controller chapter of the Intel® PXA27x Processor Family Developer's Manual.

- 3. SDCLK[1] = 45.5 MHz

- 4. Overridden by MDREFR[29]

- One refresh every 7.62 μs. This value may change, depending on the presence of an expansion board with SDRAM mapped to any of nSDCS<3:1>.

#### 3.2.2.5 Static Memory Control Register 0 (MSC0)

Note:

The flash-memory bank might not operate reliably at MEM\_CLK = 130 MHz if all timing parameters are near worst-case conditions (long propagation delays). The first-access delay (t<sub>ELQV</sub> in the 3-volt *Intel StrataFlash® Memory Data Sheet* for J3-family devices) is 150 ns. However, the maximum first-access delay allowed by the processor (MSC0[RDF0/1]) with MEM\_CLK = 130 MHz (period = 7.69ns) is 192.3 ns. Thus, it might be necessary to select a run-mode frequency that produces a MEM\_CLK frequency of 91 MHz or lower under normal operating conditions.

The table below shows how to program both nCS0 (synchronous flash memory on the PXA27x processor) and nCS1 (asynchronous flash memory on the main board) for asynchronous read accesses. The setting for nCS0 is optimized for CLK MEM = 91 MHz.

Upon reset or power-up, the MEM CLK frequency defaults to 91 MHz.

#### **MSC0 Recommended Settings:**

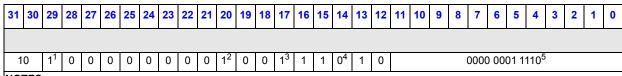

| 31 | 30 | 29  | <b>28</b> | <b>27</b> | 26 | 25 | 24 | 23 | 22 | <b>21</b> | 20 | 19 | 18 | 17  | 16 | 15 | 14 | 13  | 12 | 11 | 10 | 9  | 8 | 7 | 6  | 5  | 4 | 3 | 2 | 1   | 0 |

|----|----|-----|-----------|-----------|----|----|----|----|----|-----------|----|----|----|-----|----|----|----|-----|----|----|----|----|---|---|----|----|---|---|---|-----|---|

|    |    |     |           |           |    |    |    |    |    |           |    |    |    |     |    |    |    |     |    |    |    |    |   |   |    |    |   |   |   |     |   |

| Х  |    | XXX |           |           | XX | XX |    |    | XX | XX        |    | Χ  |    | XXX |    | 0  |    | 111 |    |    | 11 | 11 |   |   | 11 | 11 |   | 1 | ( | 010 |   |

## 3.2.2.6 Static Memory Control Register 1 (MSC1)

The timing values shown in the following table are for the SRAM.

#### **MSC1** Recommended Settings:

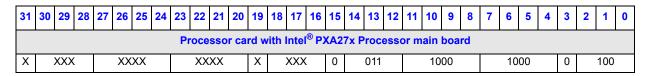

| 31 | 30    | 29 2   | 8 27   | 26 2               | 25 24  | 23    | 22 21  | 20    | 19                | 18              | 17  | 16   | 15 | 14 | 13    | 12   | 11                | 10 9 | 8     | 7    | 6    | 5   | 4   | 3   | 2    | 1    | 0 |

|----|-------|--------|--------|--------------------|--------|-------|--------|-------|-------------------|-----------------|-----|------|----|----|-------|------|-------------------|------|-------|------|------|-----|-----|-----|------|------|---|

|    | Stand | l-alon | e Inte | el <sup>®</sup> PX | A27x F | Proce | ssor a | nd lı | ntel <sup>©</sup> | <sup>®</sup> PX |     | c Pr |    |    | r wit | h In | itel <sup>®</sup> | PXA2 | 27x P | roce | ssor | Ref | ere | nce | Plat | form | 1 |

| 0  |       | 000    |        | 0000               | 0      |       | 0000   |       | 0                 | (               | 000 |      | 1  |    | 010   |      |                   | 0110 | )     |      | 100  | 01  |     | 0   |      | 001  |   |

## 3.2.2.7 Static Memory Control Register 2 (MSC2)

#### **MSC2** Recommended Settings:

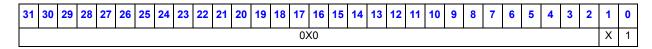

## 3.2.2.8 Expansion Memory Configuration Register (MECR)

#### **MECR Recommended Settings:**

## 3.2.2.9 Synchronous Static Memory Configuration Register (SXCNFG)

Before setting up SXCNFG, configure the PXA27x processor flash-memory devices for synchronous operation. To do this, refer to the *Intel*<sup>®</sup> *Synchronous StrataFlash*<sup>®</sup> *Memory Data Sheet* for the L18-family devices. In the Flash Configuration register for each device, set the first-access latency count (CR[13:11]) to 0b011.

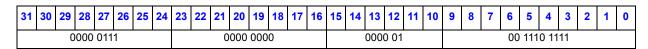

#### **SXCNFG Recommended Settings:**

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23 | 22 | 21 | 20 | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|------|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|------|----|---|---|---|---|---|---|---|

| 0  | 1  | 0  | 0  |    |    | 00 | 0 00 | 00 |    |    |    | 001 |    | 0  | 0  | 0  | 1  | 0  | 0  |    |    | 00 | 0 00 | 00 |   |   |   |   |   | 0 | 0 |

#### 3.2.2.10 Expansion Memory Timing Configuration Registers

The following table shows the settings for all six of these configuration registers.

*Note:* The values in the following table presumes a 250-ns card cycle time.

# MCMEM0, MCMEM1, MCATT0, MCATT1, MCIO0, and MCIO1 Recommended Settings:

| 3 | 1 | 30 | 29 | 28 | 27  | 26   | 25    | 24   | 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16   | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4  | 3    | 2  | 1 | 0 |

|---|---|----|----|----|-----|------|-------|------|----|----|----|----|----|----|------|------|----|----|----|----|----|----|-----|---|---|---|---|----|------|----|---|---|

|   |   |    |    |    | 000 | 0 00 | 000 ( | 0000 |    |    |    |    |    |    | 00 0 | )111 |    |    | 0  | 0  |    | 0  | 011 | 1 |   |   |   | 00 | 1 00 | 01 |   |   |

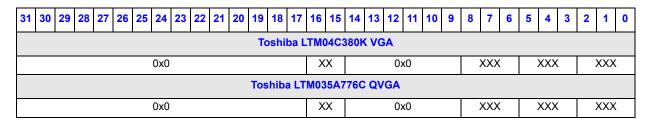

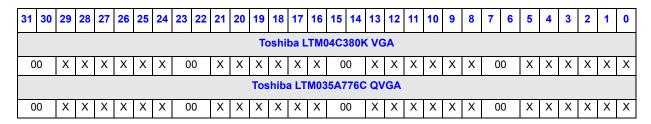

## 3.2.3 LCD-Control Registers

The following subsections provide the recommended settings for the PXA27x processor LCD-control registers. These settings are required for proper operation with the Sharp LS022Q8DD06, CG Silicon LCD Module (320x240).

The following registers must be configured:

- Section 3.2.3.1 LCD Controller Control Register 0 (LCCR0)

- Section 3.2.3.2 LCD Controller Control Register 1 (LCCR1)

- Section 3.2.3.3 LCD Controller Control Register 2 (LCCR2)

- Section 3.2.3.4 LCD Controller Control Register 3 (LCCR3)

- Section 3.2.3.5 LCD Controller Control Register 4 (LCCR4)

- Section 3.2.3.6 LCD Controller Control Register 5 (LCCR5)

The recommended settings for the LCD-control registers presume the following:

- Core is clocked off of the core PLL, with a core run-mode frequency of 130 MHz (L=10 in the Core Clock Configuration Register)

- The LCD-controller frequency is 65 MHz (see the Clocks and Power Manager chapter in the *Intel® PXA27x Processor Family Developer's Manual*)

It may be necessary to adjust the recommended settings, depending on the following:

- Custom clock configurations:

- Clock sources

- Run- and turbo-mode frequencies

- Use of fast-bus mode

For clock-configuration information, see the Clocks and Power Manager chapter in the *Intel*® *PXA27x Processor Family Developer's Manual*.

• Presence of an alternate LCD

## 3.2.3.1 LCD Controller Control Register 0 (LCCR0)

#### LCCR0 Recommended Settings:

| 31 | 30 | 29 | 28   | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15  | 14 | 13 | 12 | 11 | 10 | 6 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|------|----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    | 00 | 00 0 | 00 |    |    | 1  | 1  | 0  | 1  | 1  |    |    | 0  | 000 | 000 | 0  |    |    | 1  | 0  | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

## 3.2.3.2 LCD Controller Control Register 1 (LCCR1)

#### **LCCR1 Recommended Settings:**

## 3.2.3.3 LCD Controller Control Register 2 (LCCR2)

#### **LCCR2 Recommended Settings:**

| 31 | 30 | 29 | 28  | 27  | 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19  | 18 | 17 | 16 | 15 | 14 | 13  | 12   | 11 | 10 | 9 | 8 | 7 | 6  | 5   | 4    | 3   | 2 | 1 | 0 |

|----|----|----|-----|-----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|-----|------|----|----|---|---|---|----|-----|------|-----|---|---|---|

|    |    | 0  | 000 | 000 | 0  |    |    |    |    | 0  | 000 | 001 | 0  |    |    |    |    | 000 | 0 10 |    |    |   |   |   | 01 | 001 | 1 11 | 111 |   |   |   |

#### 3.2.3.4 LCD Controller Control Register 3 (LCCR3)

#### **LCCR3 Recommended Settings:**

| 31 | 30 | 29 | 28 | 27 | 26 | 25  | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12  | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|---|---|---|---|---|-----|-----|---|---|---|

| C  | 0  | 0  | 0  | 0  |    | 100 |    | 0  | 1  | 1  | 1  |    | XX | XX |    |    |    | 0  | 000 | 000 | 0  |   |   |   |   | 0 | 000 | 100 | 0 |   |   |

## 3.2.3.5 LCD Controller Control Register 4 (LCCR4)

#### **LCCR4 Recommended Settings:**

## 3.2.3.6 LCD Controller Control Register 5 (LCCR5)

#### **LCCR5** Recommended Settings:

## 3.2.4 Intel<sup>®</sup> PXA27x Processor Pin Usage

Table 4. Intel® PXA27x Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| GPIO_Pin | Pin_Name    | Direction | Description                                      |

|----------|-------------|-----------|--------------------------------------------------|

| 0        | GPIO[0]     | ı         | nPMIC_INT; DA9030* interrupt                     |

| 1        | GPIO[1]     | I         | AC'97 Interrupt                                  |

| 2        | SYS_EN      | 0         | SYS_EN; System enable                            |

| 3        | PWR_SCL     | 0         | PWR_SCL; Power I <sup>2</sup> C clock            |

| 4        | PWR_SDA     | I/O       | PWR_SDA; Power I <sup>2</sup> C data             |

| 5        | PWR_CAP[0]  | -         | PWR_CAP[0]; Sleep/deep-sleep regulator capacitor |

| 6        | PWR_CAP[1]  | -         | PWR_CAP[1]; Sleep/deep-sleep regulator capacitor |

| 7        | PWR_CAP[2]  | -         | PWR_CAP[2]; Sleep/deep-sleep regulator capacitor |

| 8        | PWR_CAP[3]  | -         | PWR_CAP[3]; Sleep/deep-sleep regulator capacitor |

| 9        | CLK_POUT    | I         | CLK_PIO; Processor clock                         |

| 10       | CLK_TOUT    | 0         | CLK_TOUT; 32 kHz clock                           |

| 11       | EXT_SYNC[0] | 1         | 802.11b interrupt                                |

| 12       | EXT_SYNC[1] | I         | CIF_DD[7]; Camera data                           |

| 13       | CLK_EXT     | I         | KP_MKIN[7]; Keypad matrix in 7                   |

| 14       | L_VSYNC     | I         | SDIO Card Detect                                 |

| 15       | nCS[1]      | I         | Hall Flip Sensor Closed                          |

| 16       | PWM_OUT[0]  | 0         | LED Camera Strobe                                |

| 17       | PWM_OUT[1]  | I         | CIF_DD[6]; camera interface                      |

| 18       | RDY         | I         | RDY; Ready                                       |

| 19       | L_CS        | I/O       | SSPSCLK2; Audio PCM Clock                        |

| 20       | nSDCS[2]    | I         | Hall Flip Sensor Flipped                         |

| 21       | nSDCS[3]    | I         | Ethernet Interrupt                               |

| 22       | SSPEXTCLK2  | 0         | KP_MKOUT[7]; keypad output                       |

| 23       | SSPSCLK     | 0         | CIF_MCLK; Camera master clock                    |

| 24       | SSPSFRM     | 1         | CIF_FV; Camera frame sync                        |

| 25       | SSPTXD      | 1         | CIF_LV; Camera line sync                         |

| 26       | SSPRXD      | I         | CIF_PCLK; Camera pixel clock                     |

| 27       | SSPEXTCLK   | I         | CIF_DD[0]; Camera data                           |

| 28       | BITCLK      | 1         | AC97_BITCLK; AC97 bit clock                      |

| 29       | SDATA_IN    | I         | AC97_SDATA_IN_0; AC97 data in                    |

| 30       | SDATA_OUT   | 0         | AC97_SDATA_OUT; AC97 data out                    |

Table 4. Intel® PXA27x Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| GPIO_Pin | Pin_Name     | Direction | Description                                       |

|----------|--------------|-----------|---------------------------------------------------|

| 31       | SYNC         | 0         | AC97_SYNC; AC97 synch                             |

| 32       | MMCLK        | 0         | MMCLK; MMC clock                                  |

| 33       | nCS[5]       | I/O       | General Purpose Switch or LED                     |

| 34       | FFRXD        | 1         | FFRXD; FFUART receive                             |

| 35       | FFCTS        | I/O       | SSPSFRM3; WLAN slave select                       |

| 36       | SSPSCLK2     | 0         | USB_P2_4; USB OTG                                 |

| 37       | SSPSFRM2     | 0         | USB_P2_8; USB OTG                                 |

| 38       | SSPTXD2      | 0         | SSPTXD3; WLAN transmit                            |

| 39       | FFTXD        | 0         | FFTXD; FFUART transmit                            |

| 40       | SSPRXD2      | 0         | SSPSCLK3; WLAN clock                              |

| 41       | FFRTS        | 1         | USB_P2_7; USB OTG                                 |

| 42       | BTRXD        | 1         | BTRXD; Bluetooth* receive                         |

| 43       | BTTXD        | 0         | BTTXD; Bluetooth* transmit                        |

| 44       | BTCTS        | I         | BTCTS; Bluetooth* clear to send                   |

| 45       | BTRTS        | 0         | BTRTS; Bluetooth* request to send                 |

| 46       | ICP_RXD      | 1         | ICP_RXD; Infrared receive                         |

| 47       | ICP_TXD      | 0         | ICP_TXD; Infrared transmit                        |

| 48       | BB_OB_DAT[1] | 0         | BB_OB_DAT[1]; MSL outbound data 1                 |

| 49       | nPWE         | 0         | nPWE [Ethernet]; Ethernet/<br>PCMCIA work enabled |

| 50       | BB_OB_DAT[2] | 0         | BB_OB_DAT[2]; MSL outbound                        |

| 51       | BB_OB_DAT[3] | 0         | BB_OB_DAT[3]; MSL outbound                        |

| 52       | BB_OB_CLK    | 0         | BB_OB_CLK; MSL clock                              |

| 53       | BB_OB_STB    | 0         | BB_OB_STB; MSL strobe                             |

| 54       | BB_OB_WAIT   | 1         | BB_OB_WAIT; MSL wait                              |

| 55       | BB_IB_DAT[1] | I         | BB_IB_DAT[1]; MSL inbound data                    |

| 56       | BB_IB_DAT[2] | I         | BB_IB_DAT[2]; MSL inbound data                    |

| 57       | BB_IB_DAT[3] | I         | BB_IB_DAT[3]; MSL inbound data                    |

| 58       | L_DD[0]      | 0         | L_DD[0]; LCD data                                 |

| 59       | L_DD[1]      | 0         | L_DD[1]; LCD data                                 |

| 60       | L_DD[2]      | 0         | L_DD[2]; LCD data                                 |

| 61       | L_DD[3]      | 0         | L_DD[3]; LCD data                                 |

| 62       | L_DD[4]      | 0         | L_DD[4]; LCD data                                 |

| 63       | L_DD[5]      | 0         | L_DD[5]; LCD data                                 |

Table 4. Intel® PXA27x Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| GPIO_Pin | Pin_Name     | Direction | Description                           |

|----------|--------------|-----------|---------------------------------------|

| 64       | L_DD[6]      | 0         | L_DD[6]; LCD data                     |

| 65       | L_DD[7]      | 0         | L_DD[7]; LCD data                     |

| 66       | L_DD[8]      | 0         | L_DD[8]; LCD data                     |

| 67       | L_DD[9]      | 0         | L_DD[9]; LCD data                     |

| 68       | L_DD[10]     | 0         | L_DD[10]; LCD data                    |

| 69       | L_DD[11]     | 0         | L_DD[11]; LCD data                    |

| 70       | L_DD[12]     | 0         | L_DD[12]; LCD data                    |

| 71       | L_DD[13]     | 0         | L_DD[13]; LCD data                    |

| 72       | L_DD[14]     | 0         | L_DD[14]; LCD data                    |

| 73       | L_DD[15]     | 0         | L_DD[15]; LCD data                    |

| 74       | L_FCLK       | 0         | L_FCLK: LCD frame clock               |

| 75       | L_LCLK       | 0         | L_LCLK; LCD clock                     |

| 76       | L_PCLK       | 0         | L_PCLK; LCD pixel clock               |

| 77       | L_BIAS       | 0         | LCDCS / L_BIAS; LCD chip select       |

| 78       | nCS[2]       | 0         | Strobe Intensity                      |

| 79       | nCS[3]       | 0         | CIR On                                |

| 80       | nCS[4]       | 0         | nCS[4] Ethernet; Ethernet chip select |

| 81       | BB_OB_DAT[0] | 0         | BB_OB_DAT[0]; MSL outbound data       |

| 82       | BB_IB_DAT[0] | I         | BB_IB_DAT[0]; MSL outbound data       |

| 83       | BB_IB_CLK    | I         | BB_IB_CLK: MSL clock                  |

| 84       | BB_IB_STB    | 1         | BB_IB_STB; MSL strobe                 |

| 85       | BB_IB_WAIT   | 0         | BB_IB_WAIT; MSL wait                  |

| 86       | L_DD[16]     | I/O       | SSPRXD2; Audio PCM receive            |

| 87       | L_DD[17]     | I/O       | SSPTXD2; Audio PCM transmit           |

| 88       | USBHPWR[0]   | I/O       | SSPSFRM2; Audio PCM frame             |

| 89       | USBHPEN[0]   | 1         | SSPRXD3; WLAN receive                 |

| 90       | nURST        | 1         | CIF_DD[4]; Camera data                |

| 91       | UCLK         | 1         | CIF_DD[5]; Camera data                |

| 92       | MMDAT[0]     | I/O       | MMDAT[0]; MMC data                    |

| 93       | KP_DKIN[0]   | 1         | KP_DKIN[0]; Keypad direct IN          |

| 94       | KP_DKIN[1]   | 1         | KP_DKIN[1]; Keypad direct IN          |

| 95       | KP_DKIN[2]   | 1         | KP_MKIN[6]; Keypad direct IN          |

| 96       | KP_DKIN[3]   | 0         | KP_MKOUT[6]; Keypad direct<br>OUT     |

| 97       | KP_DKIN[4]   | I         | KP_MKIN[3]; Keypad direct IN          |

Table 4. Intel® PXA27x Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| GPIO_Pin | Pin_Name     | Direction | Description                    |

|----------|--------------|-----------|--------------------------------|

| 98       | KP_DKIN[5]   | 0         | AC97_SYSCLK; AC97 system clock |

| 99       | KP_DKIN[6]   | I         | KP_MKIN[5]; Keypad matrix IN   |

| 100      | KP_MKIN[0]   | 1         | KP_MKIN[0]; Keypad matrix IN   |

| 101      | KP_MKIN[1]   | I         | KP_MKIN[1]; Keypad matrix IN   |

| 102      | KP_MKIN[2]   | 1         | KP_MKIN[2]; Keypad matrix IN   |

| 103      | KP_MKOUT[0]  | 0         | KP_MKOUT[0]; Keypad matrix OUT |

| 104      | KP_MKOUT[1]  | 0         | KP_MKOUT[1]; Keypad matrix OUT |

| 105      | KP_MKOUT[2]  | 0         | KP_MKOUT[2]; Keypad matrix OUT |

| 106      | KP_MKOUT[3]  | 1         | CIF_DD[9]; Camera data         |

| 107      | KP_MKOUT[4]  | 1         | CIF_DD[8]; Camera data         |

| 108      | KP_MKOUT[5]  | 0         | KP_MKOUT[5]; Keypad matrix OUT |

| 109      | MMDAT[1]     | I/O       | MMDAT[1]; MMC data             |

| 110      | MMDAT[2]     | I/O       | MMDAT[2]; MMC data             |

| 111      | MMDAT[3]     | I/O       | MMDAT[3]; MMC data             |

| 112      | MMCMD        | 0         | MMCMD; MMC command             |

| 113      | AC97_RESET_n | 0         | AC97_RESET_n; AC97 reset       |

| 114      | UVS0         | 1         | CIF_DD[1]; Camera data         |

| 115      | nUVS1        | Ţ         | CIF_DD[3]; Camera data         |

| 116      | nUVS2        | I         | CIF_DD[2]; Camera data         |

| 117      | SCL          | I         | SDIO WP; SDIO write packet     |

| 118      | SDA          | 0         | Keypad EL Driver               |

| 119      | USBHPWR[1]   | 0         | IRDA Shutdown                  |

| 120      | USBHPEN[1]   | 0         | Camera Shutdown                |

## 3.2.5 Programming Application Flash Memory

This section provides instructions for programming the flash memory in the PXA27x processor.

Programming these devices takes place via the PXA27x processor JTAG interface, using the Intel<sup>®</sup> JTAG Cable programming kit and a host computer with Windows\* 98, Windows\* NT, Windows\* 2000, or Windows\* XP installed as the operating system.

## 3.2.5.1 Preparing the Hardware

The Intel<sup>®</sup> JTAG Cable programming kit hardware consists of two cables and an interface module. To install the Intel<sup>®</sup> JTAG Cable programmer and prepare the Intel<sup>®</sup> PXA27x Processor Reference Platform for programming, follow these steps:

- 1. Turn off the Intel® PXA27x Processor Reference Platform power.

- 2. Plug in the Intel® PXA27x Processor Reference Platform Debug Board.

- 3. Attach the 25-pin parallel-port cable between the host computer's parallel port and the matching connector on the Intel<sup>®</sup> JTAG Cable interface device.

- 4. Attach the 20-pin ribbon cable between the matching connector on the interface card and the JTAG connector (J2) on the Intel<sup>®</sup> PXA27x Processor Reference Platform Debug Board.

**Note:** The Intel<sup>®</sup> JTAG Cable interface device draws a few milliamps of 3.3-volt power from the Intel<sup>®</sup> PXA27x Processor Reference Platform on pin 1 of the Intel<sup>®</sup> JTAG Cable connector.

#### 3.2.5.2 Preparing the Host Computer

The flash-memory programming software, JFlashMM, requires that a parallel port device driver be installed on the host computer when using Windows\* 98, Windows\* NT, Windows\* 2000, or Windows\* XP. To configure the host with this device driver, follow these steps:

- 1. Configure the parallel port for ECP mode.

- 2. Install the JFlashMM software by following the instructions in the JFlashMM release notes.

## 3.2.6 Flash Memory

To start the flash-memory programmer, follow these steps:

- 1. Remove power from the platform.

- 2. Connect a Intel<sup>®</sup> PXA27x Processor Reference Platform Debug Board to the system by inserting it fully into the SD socket.

- 3. Apply power to the system and turn on the system.

- 4. Follow the instruction in JFlash release notes to install JFlashMM.

- 5. Apply power to the PXA27x processor.

- 6. On the host computer, execute the file jflashmm.exe.

After programming is complete, return the PXA27x processor to normal operation by turning off PXA27x processor power.

# Communications Processor and Audio Concept

This chapter includes the following sections:

- Section 4.1 Communications Processor

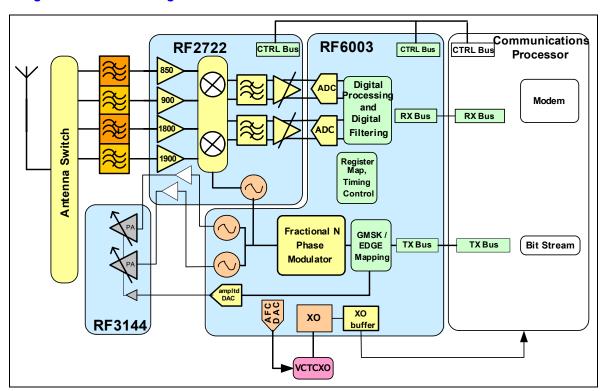

- Section 4.2 Intel® PXA27x Processor Reference Platform GSM Radio

- Section 4.3 Communications Processor Boot Loader Application

- Section 4.4 Audio Concept

- Section 4.5 Audio Scenarios

## 4.1 Communications Processor

## 4.1.1 Communications Processor Frequency Settings

#### 4.1.1.1 Communications Processor PMU Clock Settings

- Main PLL 104 MHz

- USB PLL not used

- Intel Xscale® 104 MHz

- MSA 104 MHz

- PX bus 104 MHz

- APB clock 26 MHz

- MEMC not used (no external memory)

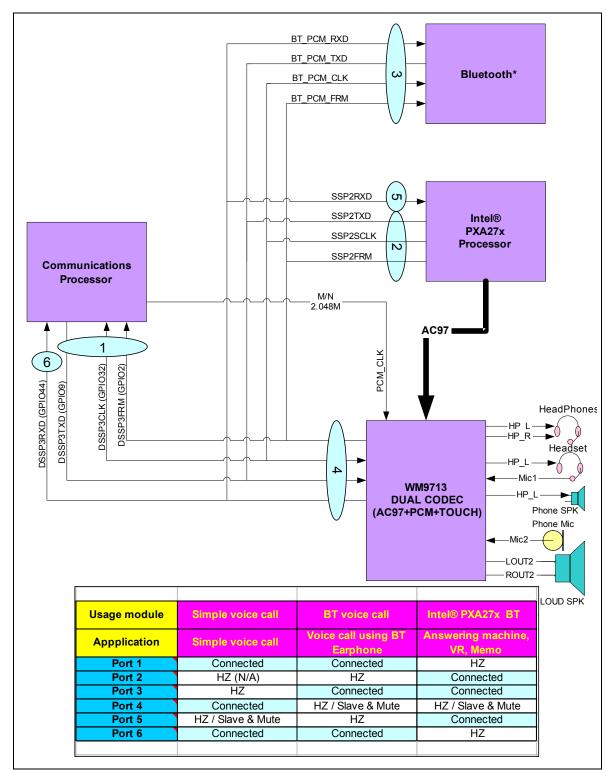

## 4.1.2 Communications Processor Pin Usage

The following table describes the communications processor pin usage for the Intel® PXA27x Processor Reference Platform.

# Table 5. Communications Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| Pin Name | Intel <sup>®</sup> PXA27x Processor<br>Reference Platform Usage | Description                                  |

|----------|-----------------------------------------------------------------|----------------------------------------------|

| GPIO2    | DSSP3_FRM                                                       | PCM Frame Sync                               |

| GPIO32   | DSSP3_CLK                                                       | PCM CLK                                      |

| GPIO5    | SLEEP                                                           | Communications Processor<br>Sleep Indication |

Table 5. Communications Processor Pin Usage for the Intel® PXA27x Processor Reference Platform

| Pin Name    | Intel <sup>®</sup> PXA27x Processor<br>Reference Platform Usage | Description                            |

|-------------|-----------------------------------------------------------------|----------------------------------------|

| GPIO6       | N/A                                                             | N/A                                    |

| GPIO7       | N/A                                                             | N/A                                    |

| GPIO4       | N/A                                                             | N/A                                    |

| GPIO43      | N/A                                                             | N/A                                    |

| GPIO44      | DSSP3_RX                                                        | RCM RXD                                |

| GPIO8       | N/A                                                             | N/A                                    |

| GPIO9       | DSSP3_TX                                                        | PCM TXD                                |

| USB_P       | USB_P                                                           | Communications Processor<br>USB Client |

| USB_N       | USB_N                                                           | Communications Processor USB Client    |

| GPIO45      | N/A                                                             | N/A                                    |

| GPIO46      | N/A                                                             | N/A                                    |

| GPIO47      | N/A                                                             | N/A                                    |

| TCO14       | TCO14                                                           | RF Control Signal                      |

| TCO13       | TCO13                                                           | RF Control Signal                      |

| TCO12       | TCO12                                                           | RF Control Signal                      |

| TCO11       | TCO11                                                           | RF Control Signal                      |

| ABBCLK      | ABBCLK                                                          | Common DSSP Clock                      |

| ABBCLK_EN   | ABBCLK_EN                                                       | Common DSSP Clock enable               |

| DSSP3_FRM   | N/A                                                             | N/A                                    |

| DSSP3_RX    | N/A                                                             | N/A                                    |

| DSSP3_TX    | N/A                                                             | N/A                                    |

| DSSP4_RX    | DSSP4_RX                                                        | RF synthesizers control SSP            |

| DSSP4_FRM   | DSSP4_FRM                                                       | RF synthesizers control SSP            |

| DSSP4_TX    | DSSP4_TX                                                        | RF synthesizers control SSP            |

| ABB_RESET_N | N/A                                                             | N/A                                    |

| DSSP2_FRM   | DSSP2_FRM                                                       | RF Data In SSP                         |

| DSSP2_RX    | DSSP2_RX                                                        | RF Data In SSP                         |

| DSSP1_FRM   | DSSP1_FRM                                                       | RF Data Out SSP                        |

| DSSP1_TX    | DSSP1_TX                                                        | RF Data Out SSP                        |

| DSSP5_CLK   | DSSP5_CLK                                                       | N/A                                    |

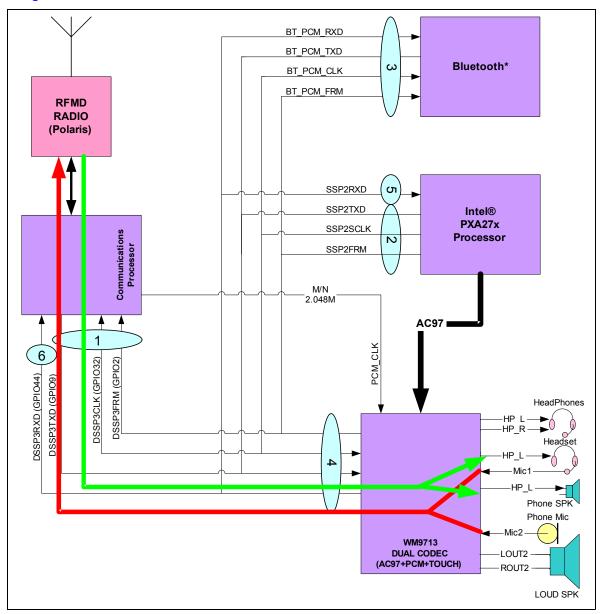

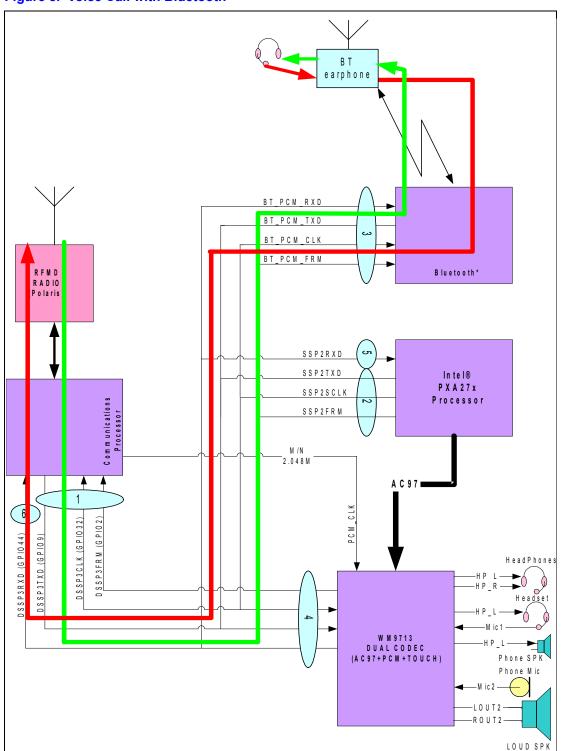

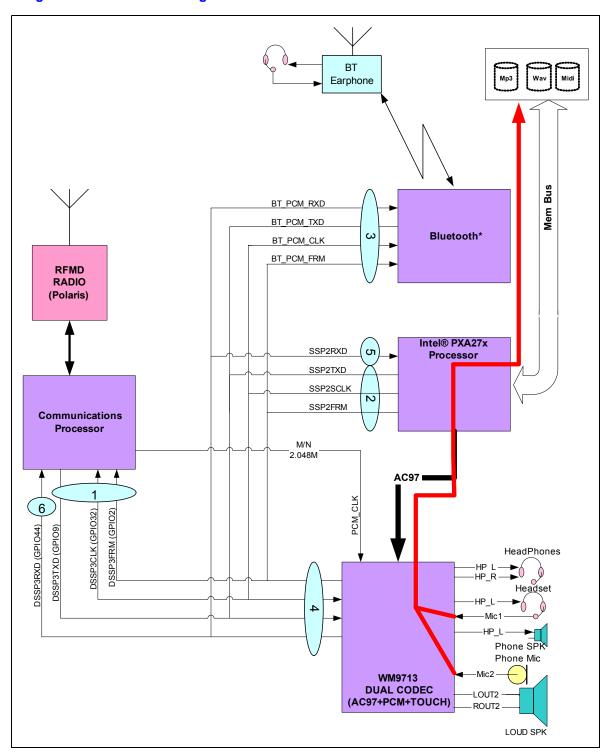

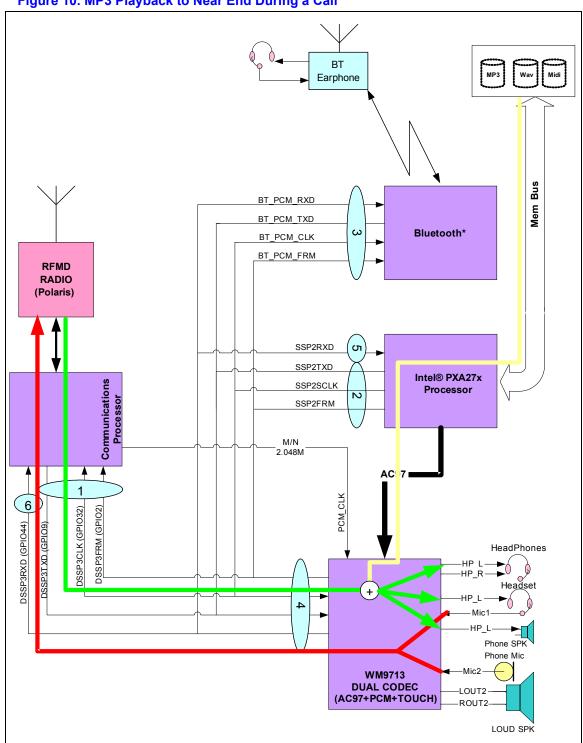

| DSSP5_FRM   | DSSP5_FRM                                                       | N/A                                    |