Maintenance only

#### 4096-word $\times$ 4-bit High-Speed CMOS Static RAM

### Features

- Single 5 V supply and high density 20-pin package

- High speed: fast access time 25/35/45 ns (max)

- Low power

- Active: 250 mW (typ)

- Standby: 100 μW (typ), 5 μW (typ) (L-version)

- Completely static memory: no clock or timing strobe required

- Equal access and cycle times

- Directly TTL compatible—all inputs and outputs

- Battery back-up operation capability (L-version)

### **Pin Arrangement**

| A4              |          | 20 🗌 V <sub>CC</sub> |  |  |  |  |  |  |  |

|-----------------|----------|----------------------|--|--|--|--|--|--|--|

| A5              | 2        | 19 🗌 A3              |  |  |  |  |  |  |  |

| A6              | □ 3      | 18 🗌 A2              |  |  |  |  |  |  |  |

| A7              | 4        | 17 🗋 A1              |  |  |  |  |  |  |  |

| A8              | 5        | 16 🗌 A0              |  |  |  |  |  |  |  |

| A9              | 6        | 15 🗍 I/O1            |  |  |  |  |  |  |  |

| A10             | 7        | 14 🗍 1/02            |  |  |  |  |  |  |  |

| A11             | 8        | 13 🗍 I/O3            |  |  |  |  |  |  |  |

| CS              | <u> </u> | 12 🗍 I/O4            |  |  |  |  |  |  |  |

| V <sub>SS</sub> | <u> </u> | 11 🗌 WE              |  |  |  |  |  |  |  |

|                 |          |                      |  |  |  |  |  |  |  |

| (Top view)      |          |                      |  |  |  |  |  |  |  |

|                 |          |                      |  |  |  |  |  |  |  |

### **Ordering Information**

| Type No.    | Access time | Package                     |  |

|-------------|-------------|-----------------------------|--|

| HM6268P-25  | 25 ns       | 300-mil 20-pin, plastic DIP |  |

| HM6268P-35  | 35 ns       | (DP-20N)                    |  |

| HM6268P-45  | 45 ns       |                             |  |

| HM6268LP-25 | 25 ns       |                             |  |

| HM6268LP-35 | 35 ns       |                             |  |

| HM6268LP-45 | 45 ns       |                             |  |

Note: This device is not available for new application.

HM6268 Series

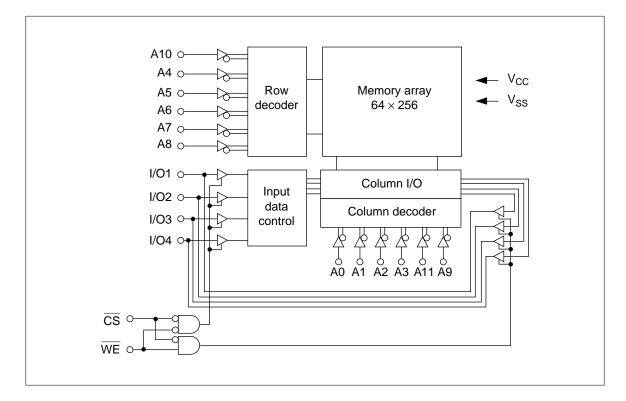

### **Block Diagram**

# **Truth Table**

| CS | WE | Mode         | V <sub>CC</sub> current            | I/O pin | Cycle       |

|----|----|--------------|------------------------------------|---------|-------------|

| Н  | x  | Not Selected | I <sub>SB</sub> , I <sub>SB1</sub> | High-Z  | _           |

| L  | Н  | Read         | I <sub>CC</sub>                    | Dout    | Read cycle  |

| L  | L  | Write        | I <sub>CC</sub>                    | Din     | Write cycle |

### **Absolute Maximum Ratings**

| Parameter                               | Symbol         | Rating                     | Unit |

|-----------------------------------------|----------------|----------------------------|------|

| Voltage on any pin relative to $V_{SS}$ | V <sub>T</sub> | -0.5 <sup>*1</sup> to +7.0 | V    |

| Power dissipation                       | P <sub>T</sub> | 1.0                        | W    |

| Operating temperature                   | Topr           | 0 to + 70                  | °C   |

| Storage temperature                     | Tstg           | –55 to +125                | ٥°C  |

| Temperature under bias                  | Tbias          | -10 to + 85                | °C   |

Note: 1. -3.5 V for pulse width  $\leq 10$  ns.

### **Recommended DC Operating Conditions** (Ta = 0 to $+ 70^{\circ}$ C)

| Parameter                    | Symbol          | Min                | Тур | Max | Unit |

|------------------------------|-----------------|--------------------|-----|-----|------|

| Supply voltage               | V <sub>CC</sub> | 4.5                | 5.0 | 5.5 | V    |

|                              | V <sub>SS</sub> | 0                  | 0   | 0   | V    |

| Input high (logic 1) voltage | V <sub>IH</sub> | 2.2                |     | 6.0 | V    |

| Input low (logic 0) voltage  | V <sub>IL</sub> | -0.5 <sup>*1</sup> | _   | 0.8 | V    |

Note: 1. -3.0 V for pulse width  $\leq 10$  ns.

### **DC Characteristics** ( $V_{CC} = 5 V \pm 10\%$ , $V_{SS} = 0 V$ , Ta = 0 to $+70^{\circ}C$ )

| Parameter                        | Symbol           | Min | Typ *1           | Max   | Unit | Test condition                                                                                                                    |

|----------------------------------|------------------|-----|------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| Input leakage current            | I <sub>LI</sub>  | _   | _                | 2.0   | μA   | $V_{CC} = 5.5 \text{ V},$<br>Vin = V <sub>SS</sub> to V <sub>CC</sub>                                                             |

| Output leakage current           | I <sub>LO</sub>  | _   | _                | 2.0   | μA   | $\overline{\text{CS}} = \text{V}_{\text{IH}},$<br>$\text{V}_{\text{I/O}} = \text{V}_{\text{SS}} \text{ to } \text{V}_{\text{CC}}$ |

| Operating power supply current   | I <sub>CC</sub>  | _   | 50 <sup>*3</sup> | 90    | mA   | $\overline{\text{CS}} = \text{V}_{\text{IL}}, \text{ I}_{\text{I/O}} = 0 \text{ mA},$ min. cycle                                  |

| Standby power supply current     | I <sub>SB</sub>  |     | 15               | 25    | mA   | $\overline{\text{CS}} = \text{V}_{\text{IH}}$ , min. cycle                                                                        |

| Standby power supply current (1) | I <sub>SB1</sub> | _   | 0.02             | 2.0   | mA   | $\overline{\text{CS}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V},$                                                                  |

|                                  |                  | _   | 1 *2             | 50 *2 | μA   | $^{-0} V \leq V_{IN} \leq 0.2 V \text{ or} \\ V_{CC} - 0.2 V \leq V_{IN}$                                                         |

| Output low voltage               | V <sub>OL</sub>  | _   | _                | 0.4   | V    | I <sub>OL</sub> = 8 mA                                                                                                            |

| Output high voltage              | V <sub>OH</sub>  | 2.4 | _                | _     | V    | I <sub>OH</sub> = -4.0 mA                                                                                                         |

Notes: 1. Typical limits are at  $V_{CC}$  = 5.0 V, Ta = +25°C and specified loading

2. This characteristic is guaranteed only for L-version.

3. 40 mA typical for 45 ns version.

# **Capacitance** (Ta = $25^{\circ}$ C, f = 1.0 MHz) \*1

| Parameter                | Symbol           | Test conditions | Min | Мах | Unit |

|--------------------------|------------------|-----------------|-----|-----|------|

| Input capacitance        | Cin              | Vin = 0 V       | —   | 6   | pF   |

| Input/output capacitance | C <sub>I/O</sub> | $V_{I/O} = 0 V$ | —   | 9   | pF   |

Note: 1. These parameters are sampled and not 100% tested.

### HM6268 Series

AC Characteristics ( $V_{CC} = 5 V + 10\%$ , Ta = 0 to +70°C, unless otherwise noted)

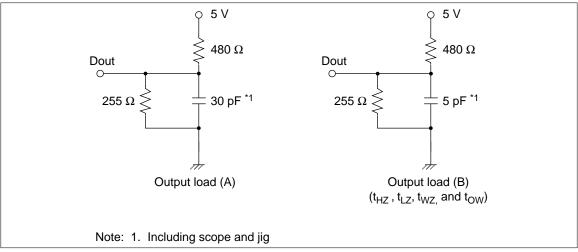

#### AC Test Conditions:

- Input pulse levels:  $V_{SS}$  to 3.0 V

- Input rise and fall times: 5 ns

- Input and output timing reference levels: 1.5 V

- Output load: See figure

#### **Output Load**

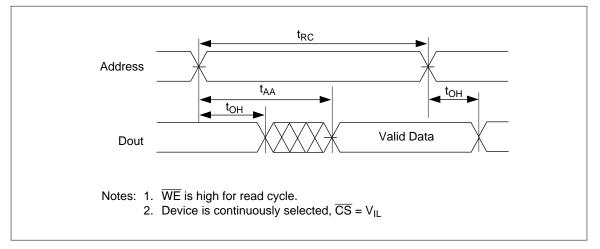

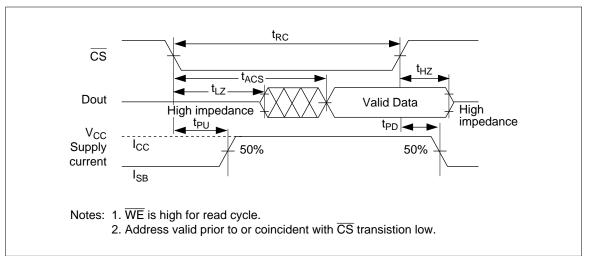

#### **Read Cycle**

|                                      |                    | HM62 | 268-25 | HM62 | 268-35 | HM62 | 268-45 |      |

|--------------------------------------|--------------------|------|--------|------|--------|------|--------|------|

| Parameter                            | Symbol             | Min  | Max    | Min  | Мах    | Min  | Мах    | Unit |

| Read cycle time                      | t <sub>RC</sub>    | 25   | —      | 35   | —      | 45   | —      | ns   |

| Address access time                  | t <sub>AA</sub>    | —    | 25     | _    | 35     | —    | 45     | ns   |

| Chip select access time              | t <sub>ACS</sub>   | —    | 25     | _    | 35     | —    | 45     | ns   |

| Output hold from address change      | t <sub>OH</sub>    | 5    | _      | 5    | _      | 5    | _      | ns   |

| Chip selection to output in low-Z    | t <sub>LZ</sub> *1 | 10   | —      | 10   | —      | 10   | —      | ns   |

| Chip deselection to output in high-Z | t <sub>HZ</sub> *1 | 0    | 15     | 0    | 20     | 0    | 20     | ns   |

| Chip selection to power up time      | t <sub>PU</sub>    | 0    | _      | 0    | _      | 0    | _      | ns   |

| Chip deselection to power down time  | t <sub>PD</sub>    |      | 25     | _    | 25     | _    | 30     | ns   |

Note: 1. Transition is measured +200 mV from steady state voltage with load (B). These parameters are sampled and not 100% tested.

#### Read Timing Waveform (1)

#### Read Timing Waveform (2)

# HM6268 Series

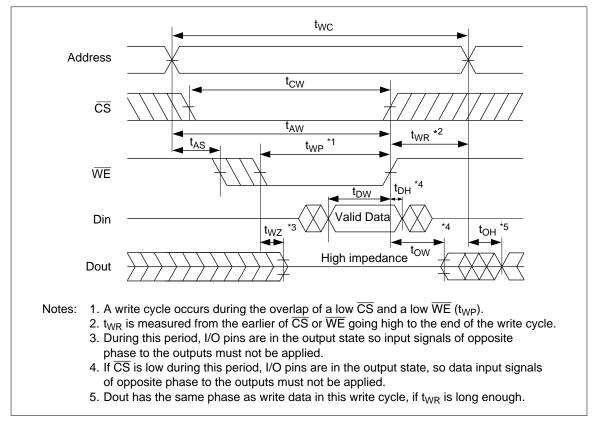

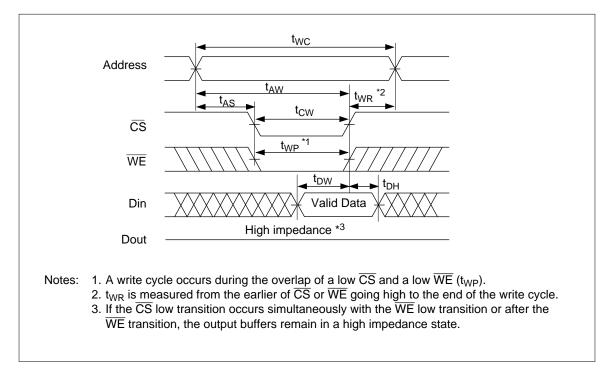

### Write Cycle

|                                   |                    | HM62 | 268-25 | HM62 | 268-35 | HM62 | 268-45 |      |

|-----------------------------------|--------------------|------|--------|------|--------|------|--------|------|

| Parameter                         | Symbol             | Min  | Max    | Min  | Max    | Min  | Мах    | Unit |

| Write cycle time                  | t <sub>WC</sub>    | 25   | _      | 35   | _      | 45   | _      | ns   |

| Chip selection to end of write    | t <sub>CW</sub>    | 20   | —      | 30   | —      | 40   | —      | ns   |

| Address valid to end of write     | t <sub>AW</sub>    | 20   | —      | 30   | —      | 40   | —      | ns   |

| Address setup time                | t <sub>AS</sub>    | 0    | —      | 0    | —      | 0    | —      | ns   |

| Write pulse width                 | t <sub>WP</sub>    | 20   | —      | 30   | —      | 35   | —      | ns   |

| Write recovery time               | t <sub>WR</sub>    | 0    | —      | 0    | —      | 0    | —      | ns   |

| Data valid to end of write        | t <sub>DW</sub>    | 12   | —      | 20   | —      | 20   | —      | ns   |

| Data hold time                    | t <sub>DH</sub>    | 0    | —      | 0    | —      | 0    | —      | ns   |

| Write enabled to output in high-Z | t <sub>WZ</sub> *1 | 0    | 8      | 0    | 10     | 0    | 15     | ns   |

| Output active from end of write   | t <sub>OW</sub> *1 | 0    | _      | 0    | _      | 0    | _      | ns   |

Note: 1. Transition is measured +200 mV from steady state voltage with load (B). These parameters are sampled and not 100% tested.

Write Timing Waveform (1) (WE Controlled)

#### Write Timing Waveform (2) (CS Controlled)

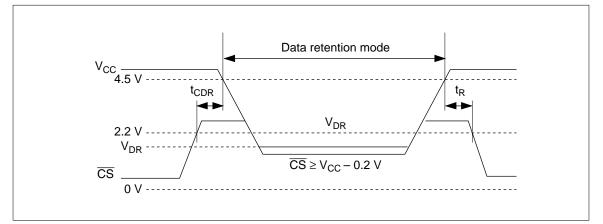

# Low V<sub>CC</sub> Data Retention Characteristics ( $0^{\circ}C \le Ta \le 70^{\circ}C$ )

These characteristics are guaranteed only for L-version.

| Parameter                            | Symbol            | Min                 | Тур | Max              | Unit | Test conditions                                                                       |

|--------------------------------------|-------------------|---------------------|-----|------------------|------|---------------------------------------------------------------------------------------|

| V <sub>CC</sub> for data retention   | V <sub>DR</sub>   | 2.0                 | _   | _                | V    | $\overline{\text{CS}} \ge \text{V}_{\text{CC}} - 0.2 \text{ V},$                      |

| Data retention current               | I <sub>CCDR</sub> | —                   | _   | 30 * 2<br>20 * 3 | μA   | $V_{IN} \ge V_{CC} - 0.2 \text{ V}, \text{ or}$<br>0 V $\le V_{IN} \le 0.2 \text{ V}$ |

| Chip deselect to data retention time | t <sub>CDR</sub>  | 2.0                 | _   |                  | ns   | See retention                                                                         |

| Operation recovery time              | t <sub>R</sub>    | t <sub>RC</sub> * 1 | _   |                  | ns   | -waveform                                                                             |

Notes: 1. Read cycle time

2.  $V_{CC} = 3.0 V$ 3.  $V_{CC} = 2.0 V$

### Low $V_{\mbox{\scriptsize CC}}$ Data Retention Waveform