# LCDC (LCD Timing Controller)

# HITACHI

ADE-207-275(Z) '99.9 Rev. 0.0

#### Description

The HD61830/HD61830B is a dot matrix liquid crystal graphic display controller LSI that stores the display data sent from an 8-bit microcontroller in the external RAM to generate dot matrix liquid crystal driving signals.

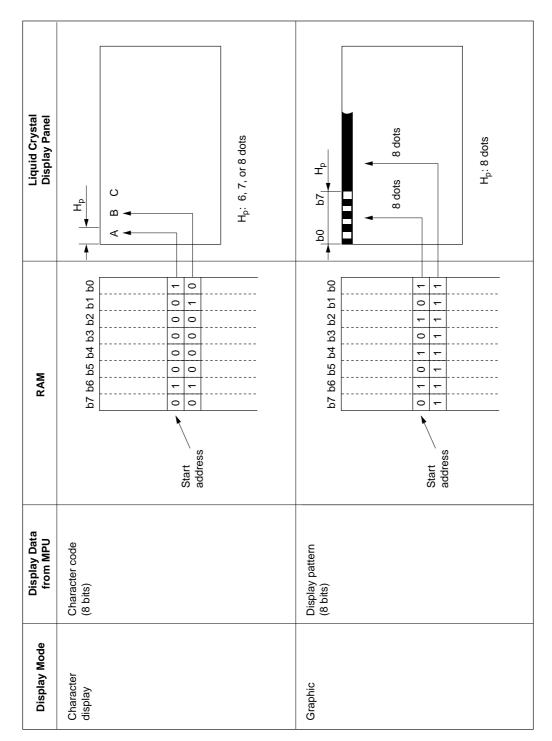

It has a graphic mode in which 1-bit data in the external RAM corresponds to the on/off state of 1 dot on liquid crystal display and a character mode in which characters are displayed by storing character codes in the external RAM and developing them into the dot patterns with the internal character generator ROM. Both modes can be provided for various applications.

The HD61830/HD61830B is produced by the CMOS process. Thus, combined with a CMOS microcontroller it can complete a liquid crystal display device with lower power dissipation.

#### Features

- Dot matrix liquid crystal graphic display controller

- Display control capacity

- Graphic mode: 512k dots (2<sup>16</sup> bytes)

- Character mode: 4096 characters (2<sup>12</sup> characters)

- Internal character generator ROM: 7360 bits

- 160 types of  $5 \times 7$  dot characters

- 32 types of 5 × 11 dot characters Total 192 characters

- Can be extended to 256 characters (4 kbytes max.) with external ROM

- Interfaces to 8-bit MPU

- Display duty cycle (can be selected by a program) Static to 1/128 duty cycle

- Various instruction functions

Scroll, cursor on/off/blink, character blink, bit manipulation

- Display method: Selectable A or B types

- Internal oscillator (with external resistor and capacitor) HD61830

- Operating frequency

- 1.1 MHz HD61830

- 2.4 MHz HD61830B

- Low power dissipation

- Power supply: Single +5 V  $\pm 10\%$

- CMOS process

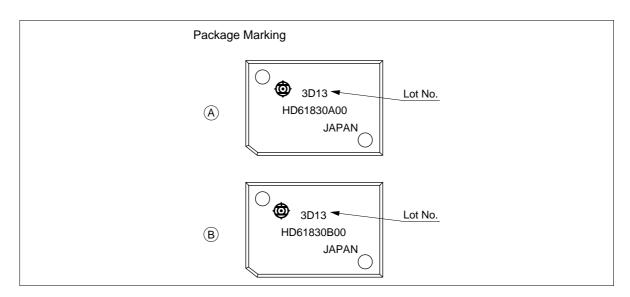

## Differences between Products HD61830 and HD61830B

|                                    | HD61830                            | HD61830B                            |  |

|------------------------------------|------------------------------------|-------------------------------------|--|

| Oscillator                         | Internal or external               | External only                       |  |

| Operating frequency                | 1.1 MHz                            | 2.4 MHz                             |  |

| Pin arrangement<br>and signal name | Pin 6: C<br>Pin 7: R<br>Pin 9: CPO | Pin 6: CE<br>Pin 7: OE<br>Pin 9: NC |  |

| Package marking to see figure      | A                                  | B                                   |  |

# **Ordering Information**

| Туре No.    | Package                    |

|-------------|----------------------------|

| HD61830A00H | 60-pin plastic QFP (FP-60) |

| HD61830B00H |                            |

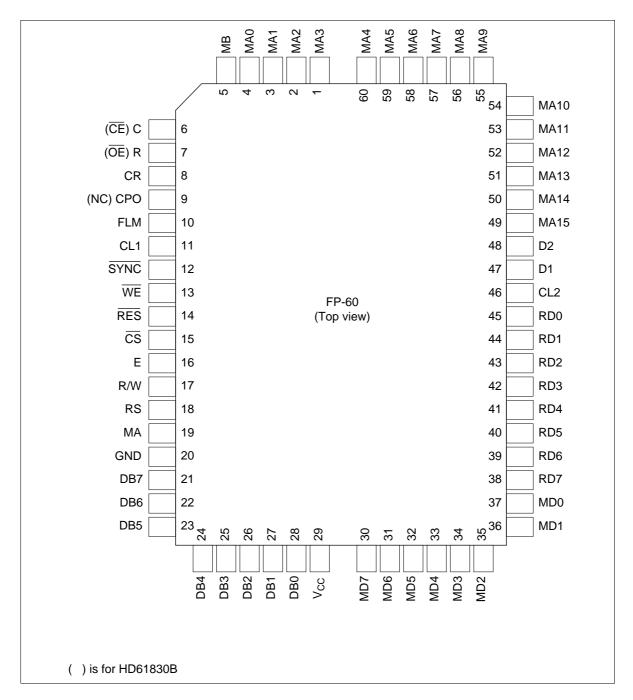

#### **Pin Arrangement**

#### **Terminal Functions**

| Symbol   | Pin Number | I/O  | Function                                                                                                                                                                      |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0–DB7  | 28–21      | I/O  | Data bus: Three-state I/O common terminal<br>Data is transferred to MPU through DB0 to DB7.                                                                                   |

| CS       | 15         | I    | Chip select: Selected state with $\overline{CS} = 0$                                                                                                                          |

| R/W      | 17         | I    | $\begin{array}{l} \text{Read/Write: R/W = 1: MPU \leftarrow HD61830} \\ \text{R/W = 0: MPU \rightarrow HD61830} \end{array}$                                                  |

| RS       | 18         | I    | Register select: RS = 1: Instruction register<br>RS = 0: Data register                                                                                                        |

| E        | 16         | I    | Enable: Data is written at the fall of E<br>Data can be read while E is 1                                                                                                     |

| CR       | 8          | I    | CR oscillator (HD61830), External clock input (HD61830B)                                                                                                                      |

| С        | 6          | _    | CR oscillator to capacitor (HD61830 only)                                                                                                                                     |

| R        | 7          | _    | CR oscillator to resistor (HD61830 only)                                                                                                                                      |

| СРО      | 9          | 0    | Clock signal for HD61830 in slave mode (HD61830 only)                                                                                                                         |

| CE       | 6          | 0    | Chip enable (HD61830B only)<br>$\overline{CE}$ = 0: Chip enables make external RAM in active                                                                                  |

| ŌĒ       | 7          | 0    | $\frac{\text{Output enable (HD61830B only)}}{\text{OE}} = 1: \text{Output enable informs external RAM that HD61830B requires data bus}$                                       |

| NC       | 9          | Open | Unused terminal. Don't connect any wires to this terminal (HD61830B only)                                                                                                     |

| MA0-MA15 | 4–1, 60–49 | 0    | External RAM address output<br>In character mode, the line code for external CG is output through<br>MA12 to MA15 (0: Character 1st line, F: Character 16th line)             |

| MD0-MD7  | 37–30      | I/O  | Display data bus: Three-state I/O common terminal                                                                                                                             |

| RD0-RD7  | 45–38      | I    | ROM data input: Dot data from external character generator is input                                                                                                           |

| WE       | 13         | 0    | Write enable: Write signal for external RAM                                                                                                                                   |

| CL2      | 46         | 0    | Display data shift clock for LCD drivers                                                                                                                                      |

| CL1      | 11         | 0    | Display data latch signal for LCD drivers                                                                                                                                     |

| FLM      | 10         | 0    | Frame signal for display synchronization                                                                                                                                      |

| MA       | 19         | 0    | Signal for converting liquid crystal driving signal into AC, A type                                                                                                           |

| MB       | 5          | 0    | Signal for converting liquid crystal driving signal into AC, B type                                                                                                           |

| D1       | 47         | 0    | Display data serial output                                                                                                                                                    |

| D2       | 48         | _    | D1: For upper half of screen<br>D2: For lower half of screen                                                                                                                  |

| SYNC     | 12         | I/O  | Synchronous signal for parallel operation<br>Three-state I/O common terminal (with pull-up MOS)<br>Master: Synchronous signal is output<br>Slave: Synchronous signal is input |

| RES      | 14         |      | Reset: Reset = 0 results in display off, slave mode and $H_0 = 6$                                                                                                             |

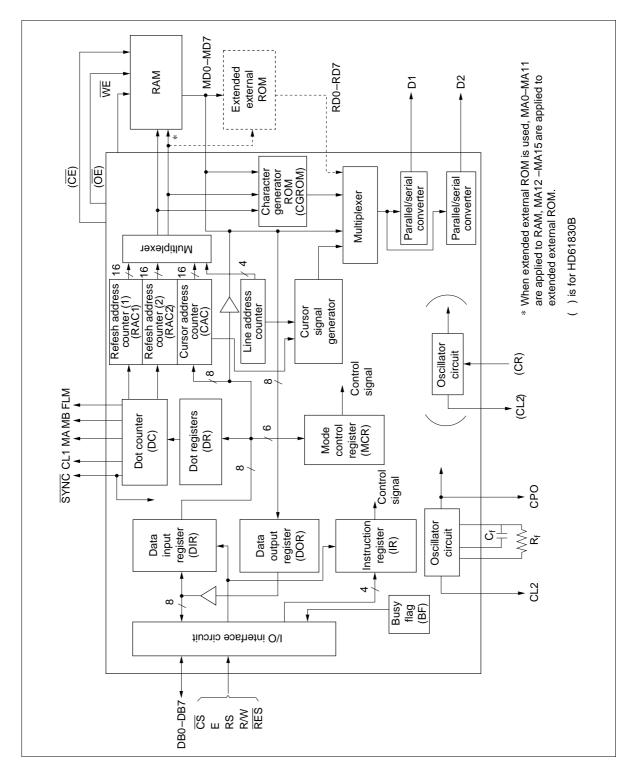

#### **Block Diagram**

#### **Block Functions**

#### Registers

The HD61830/HD61830B has the five types of registers: instruction register (IR), data input register (DIR), data output register (DOR), dot registers (DR), and mode control register (MCR).

The IR is a 4-bit register that stores the instruction codes for specifying MCR, DR, a start address register, a cursor address register, and so on. The lower order 4 bits DB0 to DB3 of data buses are written in it.

The DIR is an 8-bit register used to temporarily store the data written into the external RAM, DR, MCR, and so on.

The DOR is an 8-bit register used to temporarily store the data read from the external RAM. Cursor address information is written into the cursor address counter (CAC) through the DIR. When the memory read instruction is set in the IR (latched at the falling edge of E signal), the data of external RAM is read to DOR by an internal operation. The data is transferred to the MPU by reading the DOR with the next instruction (the contents of DOR are output to the data bus when E is at the high level).

The DR are registers used to store dot information such as character pitches and the number of vertical dots, and so on. The information sent from the MPU is written into the DR via the DIR.

The MCR is a 6-bit register used to store the data which specifies states of display such as display on/off and cursor on/off/blink. The information sent from the MPU is written in it via the DIR.

#### **Busy Flag (BF)**

The busy flag = 1 indicates the HD61830 is performing an internal operation. Instructions cannot be accepted. As shown in Control Instruction, read busy flag, the busy flag is output on DB7 under the conditions of RS = 1, R/W = 1, and E = 1. Make sure the busy flag is 0 before writing the next instruction.

#### **Dot Counters (DC)**

The dot counters are counters that generate liquid crystal display timing according to the contents of DR.

#### **Refresh Address Counters (RAC1/RAC2)**

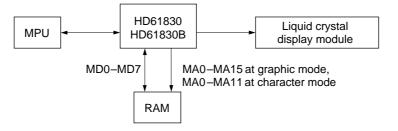

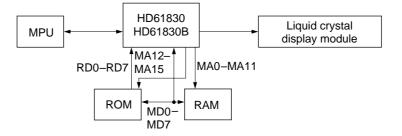

The refresh address counters, RAC1 and RAC2, control the addresses of external RAM, character generator ROM (CGROM), and extended external ROM. The RAC1 is used for the upper half of the screen and the RAC2 for the lower half. In the graphic mode, 16-bit data is output and used as the address signal of external RAM. In the character mode, the high order 4 bits (MA12–MA15) are ignored. The 4 bits of line address counter are output instead and used as the address of extended ROM.

#### **Character Generator ROM**

The character generator ROM has 7360 bits in total and stores 192 types of character data. A character code (8 bits) from the external RAM and a line code (4 bits) from the line address counter are applied to its address signals, and it outputs 5-bit dot data.

The character font is  $5 \times 7$  (160 characters) or  $5 \times 11$  (32 characters). The use of extended ROM allows  $8 \times 16$  (256 characters max.) to be used.

#### **Cursor Address Counter**

The cursor address counter is a 16-bit counter that can be preset by instruction. It holds an address when the data of external RAM is read or written (when display dot data or a character code is read or written). The value of the cursor address counter is automatically increased by 1 after the display data is read or written and after the set/clear bit instruction is executed.

#### **Cursor Signal Generator**

The cursor can be displayed by instruction in character mode. The cursor is automatically generated on the display specified by the cursor address and cursor position.

#### **Parallel/Serial Conversion**

The parallel data sent from the external RAM, character generator ROM, or extended ROM is converted into serial data by two parallel/serial conversion circuits and transferred to the liquid crystal driver circuits for upper screen and lower screen simultaneously.

#### **Display Control Instructions**

Display is controlled by writing data into the instruction register and 13 data registers. The RS signal distinguishes the instruction register from the data registers. 8-bit data is written into the instruction register with RS = 1, and the data register code is specified. After that, the 8-bit data is written in the data register and the specified instruction is executed with RS = 0.

During the execution of the instruction, no new instruction can be accepted. Since the busy flag is set during this, read the busy flag and make sure it is 0 before writing the next instruction.

**1.** Mode Control: (Execution time:  $4 \mu s$ ) Code H'00 (hexadecimal) written into the instruction register specifies the mode control register.

| Register          | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3                                 | DB2 | DB1 | DB0 |  |  |

|-------------------|-----|----|-----|-----|-----|-----|-------------------------------------|-----|-----|-----|--|--|

| Instruction reg.  | 0   | 1  | 0   | 0   | 0   | 0   | 0                                   | 0   | 0   | 0   |  |  |

| Mode control reg. | 0   | 0  | 0   | 0   |     |     | 0     0     0     0       Mode data |     |     |     |  |  |

| DB5            | DB4          | DB3      | DB2    | DB1                       | DB0          | Cursor/blink                | CG          | Graphic/character<br>display |

|----------------|--------------|----------|--------|---------------------------|--------------|-----------------------------|-------------|------------------------------|

| 1/0            | 1/0          | 0        | 0      | 0                         | 0            | Cursor off                  |             | Character display            |

|                |              | 0        | 1      |                           |              | Cursor on                   |             | (Character mode)             |

|                |              | 1        | 0      |                           |              | Cursor off, character blink | Internal CG |                              |

|                |              | 1        | 1      |                           |              | Cursor blink                | -           |                              |

|                |              | 0        | 0      |                           | 1            | Cursor off                  |             |                              |

|                |              | 0        | 1      |                           |              | Cursor on                   | External CG |                              |

|                |              | 1        | 0      |                           |              | Cursor off, character blink | xterna      |                              |

|                |              | 1        | 1      |                           |              | Cursor blink                | Ш           |                              |

|                |              | 0        | 0      | 1                         | 0            |                             |             | Graphic mode                 |

| Display ON/OFF | Master/slave | Blink    | Cursor | Graphic/character<br>mode | Ext./Int. CG |                             |             |                              |

|                |              | <u>.</u> | 0: S   | laster mo                 | de           |                             |             | ·                            |

|                |              |          | 🗕 1: D | isplay O                  | N            |                             |             |                              |

1: Display ON

0: Display OFF

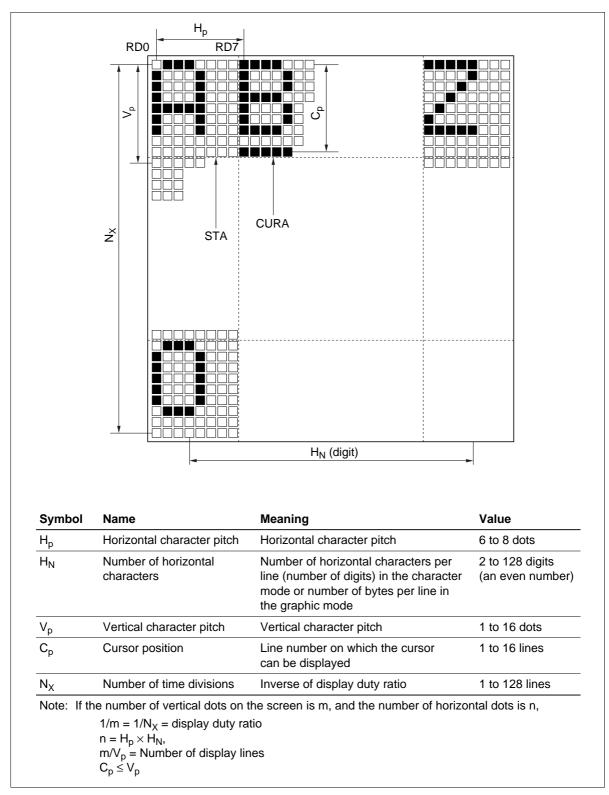

2. Set Character Pitch: (Execution time:  $4 \ \mu s$ )  $V_p$  indicates the number of vertical dots per character. The space between the vertically-displayed characters is included in the determination. This value is meaningful only during character display (in the character mode) and becomes invalid in the graphic mode.

$H_p$  indicates the number of horizontal dots per character in display, including the space between horizontally-displayed characters. In the graphic mode, the  $H_p$  indicates the number of bits of 1-byte display data to be displayed.

There are three  $H_p$  values (Table 1).

| Register             | R/W | RS | DB7 | DB6                 | DB5      | DB4 | DB3 | DB2             | DB1      | DB0  |

|----------------------|-----|----|-----|---------------------|----------|-----|-----|-----------------|----------|------|

| Instruction reg.     | 0   | 1  | 0   | 0                   | 0        | 0   | 0   | 0               | 0        | 1    |

| Character pitch reg. | 0   | 0  |     | (V <sub>p</sub> - 1 | ) binary |     | 0   | (H <sub>p</sub> | – 1) bir | hary |

#### Table 1 H<sub>p</sub> Values

| H <sub>p</sub> | DB2 | DB1 | DB0 | Horizontal Character Pitch |

|----------------|-----|-----|-----|----------------------------|

| 6              | 1   | 0   | 1   | 6                          |

| 7              | 1   | 1   | 0   | 7                          |

| 8              | 1   | 1   | 1   | 8                          |

3. Set Number of Characters: (Execution time:  $4 \mu s$ )  $H_N$  indicates the number of horizontal characters in the character mode or the number of horizontal bytes in the graphic mode. If the total sum of horizontal dots on the screen is taken as n,

$n = H_p \times H_N$

$H_N$  can be set to an even number from 2 to 128 (decimal).

| Register                  | R/W | RS | DB7 | DB6                         | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------------------------|-----|----|-----|-----------------------------|-----|-----|-----|-----|-----|-----|

| Instruction reg.          | 0   | 1  | 0   | 0                           | 0   | 0   | 0   | 0   | 1   | 0   |

| Number-of-characters reg. | 0   | 0  | 0   | (H <sub>N</sub> – 1) binary |     |     |     |     |     |     |

4. Set Number of Time Divisions (Inverse of Display Duty Ratio): (Execution time:  $4 \mu s$ )  $N_x$  indicates the number of time divisions in multiplex display.

$1/N_{\rm X}$  is the display duty ratio.

A value of 1 to 128 (decimal) can be set to  $N_x$ .

| Register                      | R/W | RS | DB7 | DB6                         | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-------------------------------|-----|----|-----|-----------------------------|-----|-----|-----|-----|-----|-----|

| Instruction reg.              | 0   | 1  | 0   | 0                           | 0   | 0   | 0   | 0   | 1   | 1   |

| Number-of-time-divisions reg. | 0   | 0  | 0   | (N <sub>x</sub> – 1) binary |     |     |     |     |     |     |

**5. Set Cursor Position:** (Execution time:  $4 \ \mu$ s)  $C_p$  indicates the position in a character where the cursor is displayed in the character mode. For example, in  $5 \times 7$  dot font, the cursor is displayed under a character by specifying  $C_p = 8$  (decimal). The cursor horizontal length is equal to the horizontal character pitch  $H_p$ . A value of 1 to 16 (decimal) can be set to  $C_p$ . If a smaller value than the vertical character pitch Vp is set ( $C_p \le Vp$ ), and a character overlaps with the cursor, the cursor has higher priority of display (at cursor display on). If  $C_p$  is greater than Vp, no cursor is displayed. The cursor horizontal length is equal to  $H_p$ .

| Register             | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2                         | DB1 | DB0 |  |

|----------------------|-----|----|-----|-----|-----|-----|-----|-----------------------------|-----|-----|--|

| Instruction reg.     | 0   | 1  | 0   | 0   | 0   | 0   | 0   | 1                           | 0   | 0   |  |

| Cursor position reg. | 0   | 0  | 0   | 0   | 0   | 0   |     | (C <sub>p</sub> – 1) binary |     |     |  |

6. Set Display Start Low Order Address: (Execution time:  $4 \ \mu s$ ) Cause display start addresses to be written in the display start address registers. The display start address indicates a RAM address at which the data displayed at the top left end on the screen is stored. In the graphic mode, the start address is composed of high/low order 16 bits. In the character display, it is composed of the lower 4 bits of high order address (DB3–DB0) and 8 bits of low order address. The upper 4 bits of high order address are ignored.

| Register                                       | R/W | RS | DB7 | DB6 | DB5       | DB4     | DB3    | DB2      | DB1 | DB0 |

|------------------------------------------------|-----|----|-----|-----|-----------|---------|--------|----------|-----|-----|

| Instruction reg.                               | 0   | 1  | 0   | 0   | 0         | 0       | 1      | 0        | 0   | 0   |

| Display start address reg.<br>(low order byte) | 0   | 0  |     |     | (Start lo | w order | addres | s) binar | у   |     |

#### Set Display Start High Order Address

| Register                                        | R/W | RS | DB7 | DB6 | DB5       | DB4      | DB3    | DB2      | DB1 | DB0 |

|-------------------------------------------------|-----|----|-----|-----|-----------|----------|--------|----------|-----|-----|

| Instruction reg.                                | 0   | 1  | 0   | 0   | 0         | 0        | 1      | 0        | 0   | 1   |

| Display start address reg.<br>(high order byte) | 0   | 0  |     | (   | Start hig | gh ordei | addres | s) binar | У   |     |

**7.** Set Cursor Address (Low Order) (RAM Write Low Order Address): (Execution time: 4 µs) Cause cursor addresses to be written in the cursor address counters. The cursor address indicates an address for sending or receiving display data and character codes to or from the RAM.

That is, data at the address specified by the cursor address are read/written. In the character mode, the cursor is displayed at the character specified by the cursor address.

A cursor address consists of the low-order address (8 bits) and the high-order address (8 bits). Satisfy the following requirements setting the cursor address (Table 2).

The cursor address counter is a 16-bit up-counter with set and reset functions. When bit N changes from 1 to 0, bit N + 1 is incremented by 1. When setting the low order address, the LSB (bit 1) of the high order address is incremented by 1 if the MSB (bit 8) of the low order address changes from 1 to 0. Therefore, set both the low order address and the high order address as shown in the Table 2.

| Register                                   | R/W | RS | DB7 | DB6 | DB5      | DB4     | DB3      | DB2      | DB1 | DB0 |

|--------------------------------------------|-----|----|-----|-----|----------|---------|----------|----------|-----|-----|

| Instruction reg.                           | 0   | 1  | 0   | 0   | 0        | 0       | 1        | 0        | 1   | 0   |

| Cursor address counter<br>(low order byte) | 0   | 0  |     | ((  | Cursor I | ow orde | r addre: | ss) bina | ry  |     |

| Register                                    | R/W | RS | DB7                                | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---------------------------------------------|-----|----|------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Instruction reg.                            | 0   | 1  | 0                                  | 0   | 0   | 0   | 1   | 0   | 1   | 1   |

| Cursor address counter<br>(high order byte) | 0   | 0  | (Cursor high order address) binary |     |     |     |     |     | ary |     |

## Set Cursor Address (High Order) (RAM Write High Order Address)

#### Table 2Cursor Address Setting

| Condition                                                                              | Requirement                                                                          |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| When you want to rewrite (set ) both the low order address and the high order address. | Set the low order address and then set the high order address.                       |

| When you want to rewrite only the low order address.                                   | Do not fail to set the high order address again after setting the low order address. |

| When you want to rewrite only the high order address.                                  | Set the high order address. You do not have to set the low order address again.      |

8. Write Display Data: (Execution time:  $6 \mu s$ ) After the code \$"0C" is written into the instruction register with RS = 1, 8-bit data with RS = 0 should be written into the data register. This data is transferred to the RAM specified by the cursor address as display data or character code. The cursor address is increased by 1 after this operation.

| Register         | R/W | RS | DB7                                    | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------------------|-----|----|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Instruction reg. | 0   | 1  | 0                                      | 0   | 0   | 0   | 1   | 1   | 0   | 0   |

| RAM              | 0   | 0  | MSB (pattern data, character code) LSB |     |     |     |     |     |     |     |

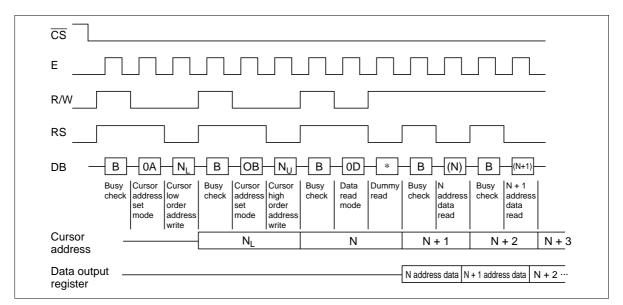

**9. Read Display Data:** (Execution time:  $6 \mu s$ ) Data can be read from the RAM with RS = 0 after writing code \$"0D" into the instruction register. Figure 1 shows the read procedure.

This instruction outputs the contents of data output register on the data bus (DB0 to DB7) and then transfers RAM data specified by the cursor address to the data output register, also increasing the cursor address by 1. After setting the cursor address, correct data is not output at the first read but at the second one. Thus, make one dummy read when reading data after setting the cursor address.

| Register         | R/W | RS | DB7                                    | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|------------------|-----|----|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Instruction reg. | 0   | 1  | 0                                      | 0   | 0   | 0   | 1   | 1   | 0   | 1   |  |

| RAM              | 1   | 0  | MSB (pattern data, character code) LSB |     |     |     |     |     |     |     |  |

Figure 1 Read Procedure

**10.** Clear Bit: (Execution time: 36  $\mu$ s) The clear/set bit instruction sets 1 bit in a byte of display data RAM to 0 or 1, respectively. The position of the bit in a byte is specified by N<sub>B</sub> and RAM address is specified by cursor address. After the execution of the instruction, the cursor address is automatically increased by 1. N<sub>B</sub> is a value from 1 to 8. N<sub>B</sub> = 1 and N<sub>B</sub> = 8 indicates LSB and MSB, respectively.

| Register         | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2             | DB1      | DB0 |

|------------------|-----|----|-----|-----|-----|-----|-----|-----------------|----------|-----|

| Instruction reg. | 0   | 1  | 0   | 0   | 0   | 0   | 1   | 1               | 1        | 0   |

| Bit clear reg.   | 0   | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>B</sub> | – 1) bir | ary |

#### Set Bit

| Register         | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2             | DB1      | DB0  |

|------------------|-----|----|-----|-----|-----|-----|-----|-----------------|----------|------|

| Instruction reg. | 0   | 1  | 0   | 0   | 0   | 0   | 1   | 1               | 1        | 1    |

| Bit set reg.     | 0   | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>в</sub> | – 1) bir | nary |

11. Read Busy Flag: (Execution time:  $0 \ \mu$ s) When the read mode is set with RS = 1, the busy flag is output to DB7. The busy flag is set to 1 during the execution of any of the other instructions. After the execution, it is set to 0. The next instruction can be accepted. No instruction can be accepted when busy flag = 1. Before executing an instruction or writing data, perform a busy flag check to make sure the busy flag is 0. When data is written in the register (RS = 1), no busy flag changes. Thus, no busy flag check is required just after the write operation into the instruction register with RS = 1.

The busy flag can be read without specifying any instruction register.

| Register  | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Busy flag | 1   | 1  | 1/0 |     |     |     | *   |     |     |     |

Figure 2 Display Variables

## **Display Mode**

|        | ligher<br>4 bits | 0010 | 0011     | 0100 | 0101 | 0110     | 0111          | 1010  | 1011          | 1100      | 1101                 | 1110     | 111      |

|--------|------------------|------|----------|------|------|----------|---------------|-------|---------------|-----------|----------------------|----------|----------|

| xxxx00 | 00               |      |          |      |      | ••       | <b>.</b>      |       |               |           | ••••<br>••••<br>•••• | Ċ        |          |

| xxxx00 | 01               |      |          |      |      |          | •             |       |               |           | ć                    |          |          |

| xxxx00 | 10               |      |          |      |      |          | ₽ <b>**</b> • |       | •             | Ņ         | .× <b>i</b>          |          |          |

| xxxx00 | 11               |      | •        |      | :    | <b>.</b> | <u></u>       |       | ŗ             |           |                      |          | <b>.</b> |

| xxxx01 | 00               |      |          |      |      |          |               | •     |               |           |                      |          |          |

| xxxx01 | 01               |      |          |      |      |          |               |       | ••••••<br>••• | •••<br>•• |                      |          |          |

| xxxx01 | 10               |      | <b>.</b> |      | Ņ    | <b>.</b> | Ļ             |       |               |           |                      |          |          |

| xxxx01 | 11               | •    | ſ        |      | IJ   |          | IJ            |       |               | <u>.</u>  | •••••<br>•••         |          |          |

| xxxx10 | 00               | ť.   |          |      | X    | ŀ        | :::           | .1    | •             |           | Ņ                    | •        | ••••     |

| xxxx10 | 01               | )    |          |      | l.i  |          | ••            | ****  |               | ,<br>,    |                      | •• 1     |          |

| xxxx10 | 10               |      |          |      |      |          | •••••••<br>•• |       |               |           | <b>.</b>             |          |          |

| xxxx10 | 11               |      | #<br>;;  | K    |      |          |               |       |               |           |                      | 33       |          |

| xxxx11 | 00               |      |          |      |      |          |               | 1     |               | •••••     | ;<br>,               | <b>.</b> |          |

| xxxx11 | 01               |      |          |      |      | <b>F</b> |               |       |               | ••••      | ••<br>•              |          |          |

| xxxx11 | 10               |      |          |      | •••  | <b>}</b> |               |       |               |           | •••                  |          |          |

| xxxx11 | 11               | ./   | ?        |      |      |          | •             | • • • | ۰.<br>        | ••••      |                      | Ö        |          |

## **Internal Character Generator Patterns and Character Codes**

# Example of Correspondence between External CGROM Address Data and Character Pattern

#### $8\times 8$ Dot Font

| $\square$ |      |              |              |    | A      | 10     |    |        |    | (  | )      |    |        |    |    |    |    | (      | )  |    |        |        | 0 1 |

|-----------|------|--------------|--------------|----|--------|--------|----|--------|----|----|--------|----|--------|----|----|----|----|--------|----|----|--------|--------|-----|

|           | /    |              |              |    | A      | 9      |    |        |    | (  | )      |    |        |    |    |    |    | (      | C  |    |        |        | 0 1 |

|           |      | $\backslash$ |              |    | А      | 8      |    |        |    | (  | )      |    |        |    |    |    |    | (      | )  |    |        |        | 1 1 |

|           |      |              | $\backslash$ |    | Α      | 7      |    |        |    | (  | )      |    |        |    |    |    |    | 1      | 1  |    |        |        | 0 1 |

| A         | 6 A5 | 5 A4         | A3           | A2 | A1     | A0     | 00 | 01     | 02 | 03 | 04     | 05 | 06     | 07 | 00 | 01 | 02 | 03     | 04 | 05 | 06     | 07     |     |

|           |      |              |              | 0  | 0      | 0      | 1  | 1      | 1  | 1  | 0      | 0  | 0      | 0  | 0  | 1  | 1  | 1      | 0  | 0  | 0      | 0      |     |

|           |      |              |              | 0  | 0      | 1      | 1  | 0      | 0  | 0  | 1      | 0  | 0      | 0  | 1  | 0  | 0  | 0      | 1  | 0  | 0      | 0      |     |

|           |      |              |              | 0  | 1      | 0      | 1  | 0      | 0  | 0  | 1      | 0  | 0      | 0  | 1  | 0  | 0  | 0      | 1  | 0  | 0      | 0      |     |

| 0         | 0    | 0            | 0            | 0  | 1      | 1      | 1  | 1      | 1  | 1  | 0      | 0  | 0      | 0  | 1  | 0  | 0  | 0      | 1  | 0  | 0      | 0      |     |

| ľ         | Ŭ    | Ũ            | Ũ            | 1  | 0      | 0      | 1  | 0      | 1  | 0  | 0      | 0  | 0      | 0  | 1  | 0  | 1  | 0      | 1  | 0  | 0      | 0      |     |

|           |      |              |              | 1  | 0      | 1      | 1  | 0      | 0  | 1  | 0      | 0  | 0      | 0  | 1  | 0  | 0  | 1      | 0  | 0  | 0      | 0      |     |

|           |      |              |              | 1  | 1      | 0      | 1  | 0      | 0  | 0  | 1      | 0  | 0      | 0  | 0  | 1  | 1  | 0      | 1  | 0  | 0      | 0      |     |

|           |      |              |              | 1  | 1      | 1      | 0  | 0      | 0  | 0  | 0      | 0  | 0      | 0  | 0  | 0  | 0  | 0      | 0  | 0  | 0      | 0      |     |

|           |      |              |              | 0  | 0      | 0      | 1  | 1      | 1  | 0  | 0      | 0  | 0      | 1  | 0  | 0  | 0  | 0      | 0  | 0  | 0      | 0      |     |

|           |      |              |              | 0  | 0      | 1      | 1  | 0      | 1  | 0  | 0      | 0  | 1      | 0  | 0  | 0  | 0  | 0      | 0  | 0  | 0      | 0      |     |

|           |      |              |              | 0  | 1      | 0      | 1  | 1      | 1  | 0  | 0      | 1  | 0      | 0  | 0  | 1  | 0  | 0      | 0  | 0  | 0      | 1      |     |

| 0         | 0    | 0            | 1            | 0  | 1      | 1      | 0  | 0      | 0  | 0  | 1      | 0  | 0      | 0  | 0  | 0  | 1  | 0      | 0  | 0  | 1      | 0      |     |

|           |      |              |              | 1  | 0<br>0 | 0      | 0  | 0<br>0 | 0  | 1  | 0<br>0 | 0  | 0      | 0  | 0  | 0  | 0  | 1<br>0 | 0  | 1  | 0      | 0<br>0 |     |

|           |      |              |              | 1  | 1      | 1<br>0 | 0  | 1      | 1  | 0  | 0      | 1  | 1<br>0 | 1  | 0  | 0  | 0  | 1      | 1  | 0  | 0<br>0 | 0      |     |

|           |      |              |              | 1  | 1      | 1      | 1  | 0      | 0  | 0  | 0      | 1  | 1      | 1  | 1  | 1  | 1  | 1      | 0  | 0  | 0      | 0      |     |

| $\vdash$  |      |              |              | 0  | 0      | 0      | 1  | 0      |    | 0  | 0      | 1  | 1      | -  | 1  | 1  | 1  | 1      | 0  | 0  | 0      | 0      |     |

| 0         | 0    | 1            | 0            |    | 0      | 0      |    |        |    |    |        |    |        |    |    |    |    |        |    |    |        |        |     |

|           |      |              |              |    |        |        |    |        |    |    |        |    |        |    |    |    |    |        |    |    |        |        |     |

#### $8 \times 16$ Dot Font

| $\overline{}$ |    |    |        |   |   |   |    |    |     |    |    |   |     |    |    |    |     |   |   |     |     |    |    |   |       |

|---------------|----|----|--------|---|---|---|----|----|-----|----|----|---|-----|----|----|----|-----|---|---|-----|-----|----|----|---|-------|

|               |    |    |        |   |   | A |    |    |     |    | (  | ) |     |    |    |    |     |   | 0 | )   |     |    |    | 0 |       |

|               |    |    |        |   |   |   | 10 |    |     |    | (  | ) |     |    |    |    |     |   | C | )   |     |    |    | 0 |       |

|               |    |    |        |   |   |   | 9  |    |     |    | (  | ) |     |    |    |    |     |   | ( | )   |     |    |    | 1 |       |

|               |    |    | $\sim$ |   |   |   | 8  | 00 | 0.4 | 00 | (  | _ | 0.5 | 00 | 07 | 00 | 0.4 |   | 1 | 0.4 | 0.5 | 00 | 07 | 0 | <br>- |

| AI            | Ab | A5 | A4     |   |   |   | _  | 00 | 01  | 02 | 03 |   | 05  |    |    |    | 01  |   |   | 04  |     | 06 |    |   | <br>- |

|               |    |    |        | 0 | 0 | 0 | 0  |    |     |    |    | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 0 | 0 | 0 | 1  |    | 0   | 0  | 0  |   | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 0 | 0 | 1 | 0  |    | 0   | 0  | 0  |   | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 0 | 0 | 1 | 1  |    |     |    |    | 0 | 0   | 0  | 0  |    | 0   | 0 | 0 | 0   | 0   |    | 0  |   |       |

|               |    |    |        | 0 | 1 | 0 | 0  |    | 0   |    | 0  | 0 | 0   | 0  | 0  | 0  |     | 0 | 0 | 0   |     | 0  | 0  |   |       |

|               |    |    |        | 0 | 1 | 0 | 1  |    | 0   | 0  |    | 0 | 0   | 0  | 0  | 0  | 0   |   | 0 |     | 0   | 0  | 0  |   |       |

|               |    |    |        | 0 | 1 | 1 | 0  |    | 0   | 0  | 0  |   | 0   | 0  | 0  | 0  | 0   | 0 |   | 0   | 0   | 0  | 0  |   |       |

| 0             | 0  | 0  | 0      | 0 | 1 | 1 | 1  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   |   | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 0 | 0 | 0  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  |     | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 0 | 0 | 1  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  |    | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 0 | 1 | 0  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 0 | 1 | 1  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 1 | 0 | 0  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 1 | 0 | 1  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 1 | 1 | 0  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 1 | 1 | 1 | 1  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

|               |    |    |        | 0 | 0 | 0 | 0  | 0  | 0   | 0  | 0  | 0 | 0   | 0  | 0  | 0  | 0   | 0 | 0 | 0   | 0   | 0  | 0  |   |       |

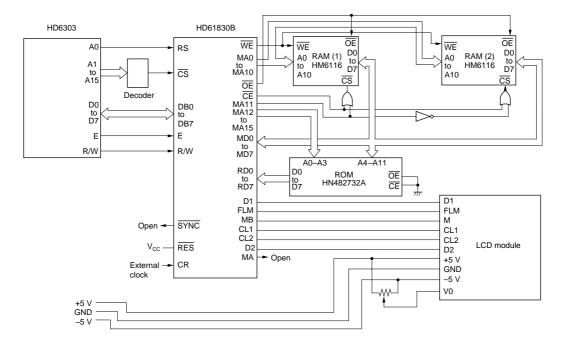

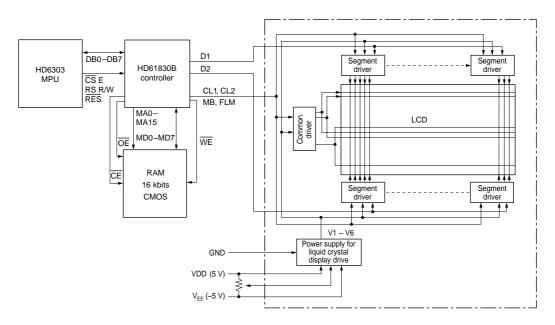

## **Example of Configuration**

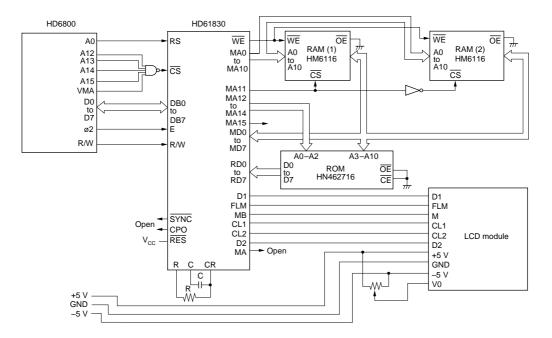

**Graphic Mode or Character Mode (1) (Internal Character Generator)**

**Character Mode (2) (External Character Generator)**

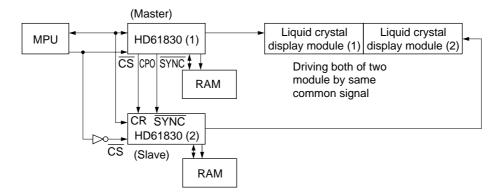

#### Parallel Operation (HD61830)

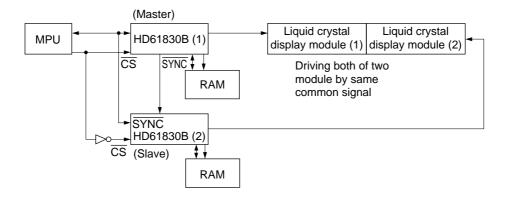

#### Parallel Operation (HD61830B)

## HD61830 Application (Character Mode, External CG, Character Font 8 × 8)

HD61830 Application (Graphic Mode)

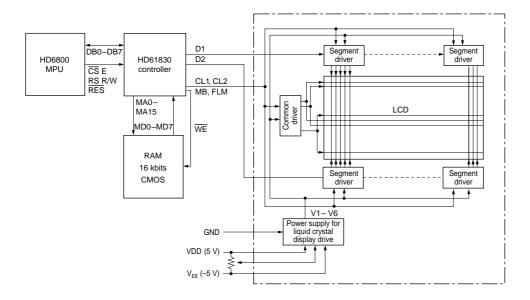

## HD61830B Application (Character Mode, External CG, Character Font 8×8)

HD61830B Application (Graphic Mode)

## HD61830 Absolute Maximum Ratings

| ltem                  | Symbol           | Value                      | Unit | Notes |

|-----------------------|------------------|----------------------------|------|-------|

| Supply voltage        | V <sub>cc</sub>  | -0.3 to +0.7               | V    | 1, 2  |

| Terminal voltage      | VT               | –0.3 to V $_{\rm cc}$ +0.3 | V    | 1, 2  |

| Operating temperature | T <sub>opr</sub> | -20 to +75                 | °C   |       |

| Storage temperature   | T <sub>stg</sub> | -55 to +125                | °C   |       |

Notes: 1. All voltages are referenced to GND = 0 V.

If LSIs are used beyond absolute maximum ratings, they may be permanently destroyed. We strongly recommend that you use the LSIs within electrical characteristic limits for normal operation, because use beyond these conditions will cause malfunction and poor reliability.

# HD61830 Electrical Characteristics (V $_{\rm CC}$ = 5 V ±10%, GND = 0 V, T $_{\rm a}$ = –20 to +75°C)

| Item                                                             | Symbol           | Min            | Тур | Max             | Unit | Test Condition                               | Notes |

|------------------------------------------------------------------|------------------|----------------|-----|-----------------|------|----------------------------------------------|-------|

| Input high voltage (TTL)                                         | VIH              | 2.2            |     | V <sub>cc</sub> | V    |                                              | 1     |

| Input low voltage (TTL)                                          | VIL              | 0              | _   | 0.8             | V    |                                              | 2     |

| Input high voltage                                               | VIHR             | 3.0            |     | V <sub>cc</sub> | V    |                                              | 3     |

| Input high voltage (CMOS)                                        | VIHC             | $0.7 \ V_{cc}$ |     | V <sub>cc</sub> | V    |                                              | 4     |

| Input low voltage (CMOS)                                         | VILC             | 0              | _   | $0.3  V_{cc}$   | V    |                                              | 4     |

| Output high voltage (TTL)                                        | VOH              | 2.4            |     | V <sub>cc</sub> | V    | —I <sub>он</sub> = 0.6 mА                    | 5     |

| Output low voltage (TTL)                                         | VOL              | 0              |     | 0.4             | V    | I <sub>oL</sub> = 1.6 mA                     | 5     |

| Output high voltage (CMOS)                                       | VOHC             | $V_{cc} - 0.4$ |     | V <sub>cc</sub> | V    | −I <sub>OH</sub> = 0.6 mA                    | 6     |

| Output low voltage (CMOS)                                        | VOLC             | 0              |     | 0.4             | V    | I <sub>oL</sub> = 0.6 mA                     | 6     |

| Input leakage current                                            | I <sub>IN</sub>  | -5             |     | 5               | μA   | $VIN = 0 - V_{CC}$                           | 7     |

| Three-state leakage current                                      | I <sub>TSL</sub> | -10            |     | 10              | μA   | $VOUT = 0 - V_{cc}$                          | 8     |

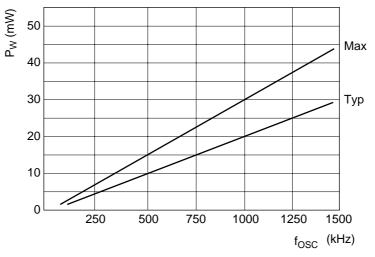

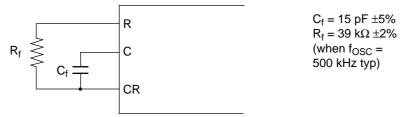

| Power dissipation (1)                                            | P <sub>w</sub> 1 | —              | 10  | 15              | mW   | CR oscillation<br>f <sub>osc</sub> = 500 kHz | 9     |

| Power dissipation (2)                                            | P <sub>w</sub> 2 | —              | 20  | 30              | mW   | External clock<br>f <sub>cp</sub> = 1 MHz    | 9     |

| Internal clock operation<br>(Clock oscillation frequency)        | f <sub>osc</sub> | 400            | 500 | 600             | kHz  | $C_f$ = 15 pF ±5%<br>$R_f$ = 39 kΩ ±2%       | 10    |

| External clock operation<br>(External clock operating frequency) | $f_{cp}$         | 100            | 500 | 1100            | kHz  |                                              | 11    |

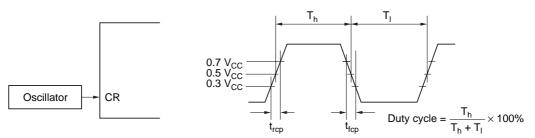

| External clock duty                                              | Duty             | 47.5           | 50  | 52.5            | %    |                                              | 11    |

| External clock rise time                                         | t <sub>rcp</sub> | _              | _   | 0.05            | μs   |                                              | 11    |

| External clock fall time                                         | t <sub>fcp</sub> | _              | _   | 0.05            | μs   |                                              | 11    |

| Pull-up current                                                  | I <sub>PL</sub>  | 2              | 10  | 20              | μA   | VIN = GND                                    | 12    |

Notes: The I/O terminals have the following configuration:

1. Applied to input terminals and I/O common terminals, except terminals SYNC, CR, and RES.

2. Applied to input terminals and I/O common terminals, except terminals SYNC and CR.

3. Applied to terminal RES.

4. Applied to terminals SYNC and CR.

5. Applied to terminals DB0–DB7, WE, MA0–MA15, and MD0–MD7.

6. Applied to terminals SYNC, CP0, FLM, CL1, CL2, D1, D2, MA, and MB.

7. Applied to input terminals.

8. Applied to I/O common terminals. However, the current which flows into the output drive MOS is excluded.

The current which flows into the input and output circuits is excluded. When the input of CMOS is

in the intermediate level, current flows through the input circuit, resulting in the increase of power

supply current. To avoid this, input must be fixed at high or low.

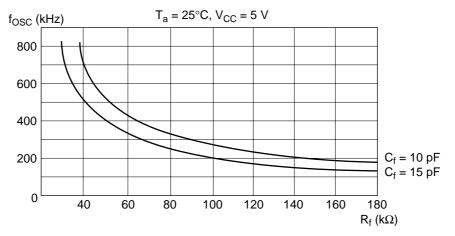

The relationship between the operating frequency and the power dissipation is given below.

10. Applied to the operation of the internal oscillator when oscillation resistor R<sub>f</sub> and oscillation capacity C<sub>f</sub> are used.

The relationship among oscillation frequency,  $R_f$  and  $C_f$  is given below.

11. Applied to external clock operation. Open ROpen COscillator CR Th ThThTh

12. Applied to SYNC, DB0–DB7, and RD0–RD7.

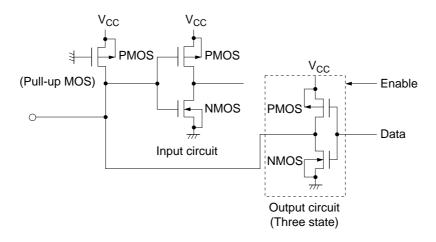

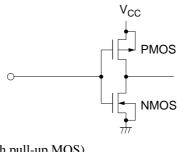

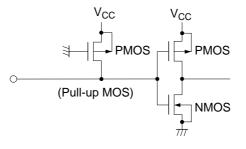

#### **Input Terminal**

Applicable terminal: CS, E, RS, R/W, RES, CR (without pull-up MOS)

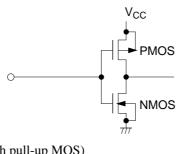

Applicable terminal: RD0-RD7 (with pull-up MOS)

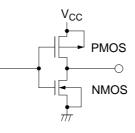

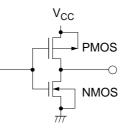

#### **Output Terminal**

Applicable terminal: CL1, CL2, MA, MB, FLM, D1, D2, WE, CPO, MA0-MA15

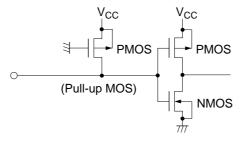

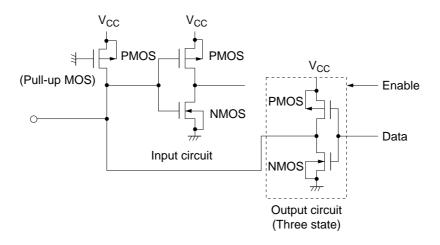

#### I/O Common Terminal

Applicable terminal: DB0–DB7, <u>SYNC</u>, MD0–MD7 (MD0–MD7 have no pull-up MOS)

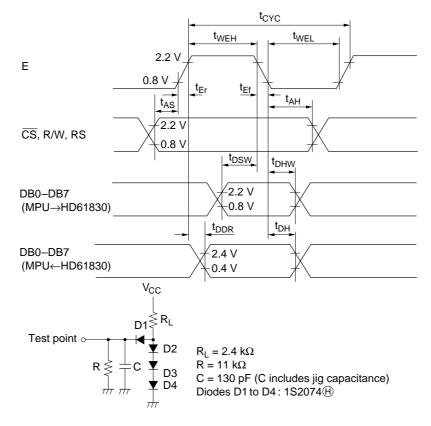

## **Timing Characteristics**

## HD61830 MPU Interface ( $V_{CC} = 5 V \pm 10\%$ , GND = 0 V, $T_a = -20 \text{ to } +75^{\circ}\text{C}$ )

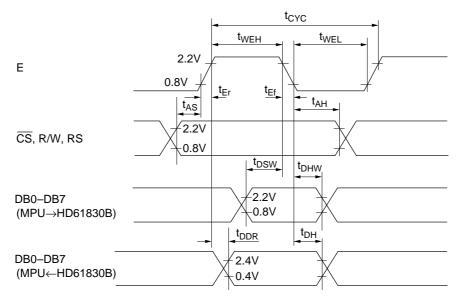

| Item                  |            | Symbol           | Min  | Тур | Max | Unit |

|-----------------------|------------|------------------|------|-----|-----|------|

| Enable cycle time     |            | t <sub>cyc</sub> | 1.0  | _   | _   | μs   |

| Enable pulse width    | High level | t <sub>WEH</sub> | 0.45 | _   | _   | μs   |

|                       | Low level  | t <sub>WEL</sub> | 0.45 | —   | —   | μs   |

| Enable rise time      |            | t <sub>Er</sub>  | _    | —   | 25  | ns   |

| Enable fall time      |            | t <sub>ef</sub>  | —    | —   | 25  | ns   |

| Setup time            |            | t <sub>AS</sub>  | 140  | —   | —   | ns   |

| Data setup time       |            | t <sub>DSW</sub> | 225  | —   | —   | ns   |

| Data delay time       |            | t <sub>DDR</sub> | —    | —   | 225 | ns * |

| Data hold time        |            | t <sub>DHW</sub> | 10   | —   | —   | ns   |

| Address hold time     |            | t <sub>AH</sub>  | 10   | _   | _   | ns   |

| Output data hold time | •          | t <sub>DH</sub>  | 20   | _   | _   | ns   |

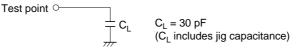

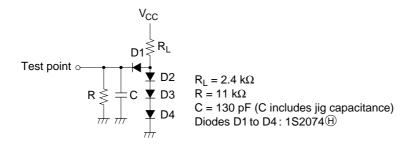

Note: \* The following load circuit is connected for specification:

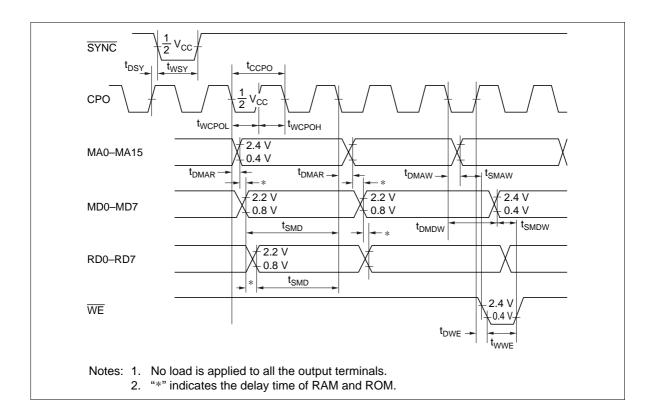

| Item                                    |                   | Symbol             | Min | Тур | Мах | Unit |

|-----------------------------------------|-------------------|--------------------|-----|-----|-----|------|

| SYNC delay time                         |                   | t <sub>DSY</sub>   | _   | —   | 200 | ns   |

| SYNC pulse width                        | Low level         | t <sub>wsy</sub>   | 900 |     | —   | ns   |

| CPO cycle time                          |                   | t <sub>CCPO</sub>  | 900 |     | —   | ns   |

| CPO pulse width                         | High level        | t <sub>wCPOH</sub> | 450 |     | —   | ns   |

|                                         | Low level         | t <sub>WCPOL</sub> | 450 | _   | _   | ns   |

| MA0 to MA15 refresh                     | delay time        | t <sub>DMAR</sub>  |     |     | 200 | ns   |

| MA0 to MA15 write a                     | ddress delay time | t <sub>DMAW</sub>  | _   |     | 200 | ns   |

| MD0 to MD7 write da                     | ta delay time     | t <sub>DMDW</sub>  | _   |     | 200 | ns   |

| MD0 to MD7, RD0 to                      | RD7 setup time    | t <sub>smd</sub>   | 900 | _   | _   | ns   |

| Memory address setu                     | ıp time           | t <sub>smaw</sub>  | 250 | _   | _   | ns   |

| Memory data setup ti                    | me                | t <sub>SMDW</sub>  | 250 | _   | _   | ns   |

| WE delay time                           |                   | t <sub>DWE</sub>   | _   | _   | 200 | ns   |

| $\overline{\text{WE}}$ pulse width (low | level)            | t <sub>wwe</sub>   | 450 | _   | _   | ns   |

## HD61830 External RAM and ROM Interface (V<sub>CC</sub> = 5 V ±10%, GND = 0 V, T<sub>a</sub> = -20 to +75°C)

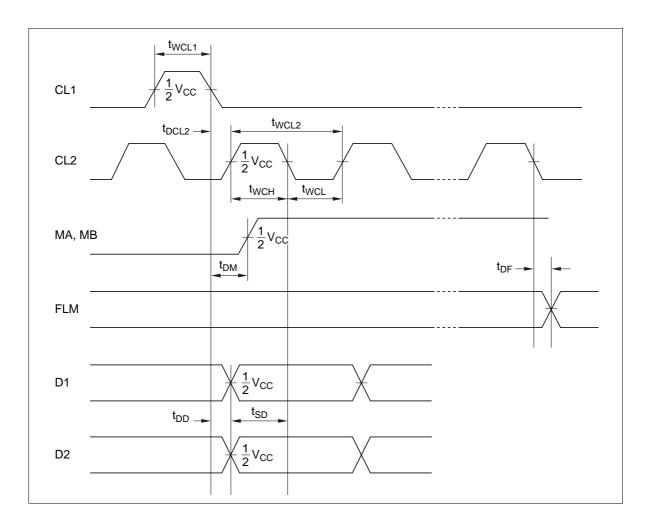

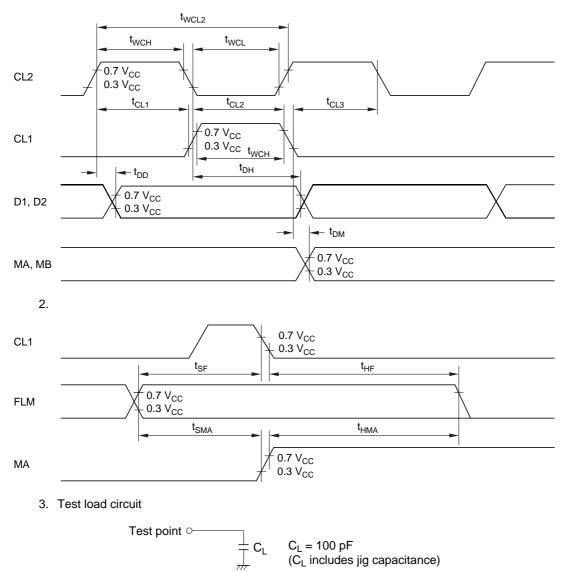

# HD61830 LCD Driver Interface (V $_{\rm CC}$ = 5 V ±10%, GND = 0 V, T $_{\rm a}$ = –20 to +75°C)

| Item                         |            | Symbol            | Min | Тур | Мах | Unit |

|------------------------------|------------|-------------------|-----|-----|-----|------|

| Clock pulse width (high leve | el)        | t <sub>WCL1</sub> | 450 |     | _   | ns   |

| Clock delay time             |            | t <sub>DCL2</sub> | —   |     | 200 | ns   |

| Clock cycle time             |            | t <sub>WCL2</sub> | 900 |     | _   | ns   |

| Clock pulse width            | High level | t <sub>wch</sub>  | 450 |     | —   | ns   |

|                              | Low level  | t <sub>WCL</sub>  | 450 | _   | _   | ns   |

| MA, MB delay time            |            | t <sub>DM</sub>   | _   |     | 300 | ns   |

| FLM delay time               |            | t <sub>DF</sub>   | _   | _   | 300 | ns   |

| Data delay time              |            | t <sub>DD</sub>   | _   | —   | 200 | ns   |

| Data setup time              |            | t <sub>sD</sub>   | 250 |     | _   | ns   |

Note: No load is applied to all the output terminals (MA, MB, FLM, D1, and D2).

## HD61830B Absolute Maximum Ratings

| Item                  | Symbol           | Value                        | Unit | Notes |

|-----------------------|------------------|------------------------------|------|-------|

| Supply voltage        | V <sub>cc</sub>  | -0.3 to +0.7                 | V    | 1, 2  |

| Terminal voltage      | VT               | –0.3 to V <sub>cc</sub> +0.3 | V    | 1, 2  |

| Operating temperature | T <sub>opr</sub> | -20 to +75                   | °C   |       |

| Storage temperature   | $T_{stg}$        | -55 to +125                  | °C   |       |

Notes: 1. All voltage is referred to GND = 0 V.

If LSIs are used beyond absolute maximum ratings, they may be permanently destroyed. We strongly recommend that you use the LSIs within electrical characteristic limits for normal operation, because use beyond these conditions will cause malfunction and poor reliability.

# HD61830B Electrical Characteristics (V<sub>CC</sub> = 5V ±10%, GND = 0V, T<sub>a</sub> = -20 to +75°C)

| Item                        | Symbol           | Min            | Тур | Max             | Unit | Test Condition                              | Notes |

|-----------------------------|------------------|----------------|-----|-----------------|------|---------------------------------------------|-------|

| Input high voltage (TTL)    | VIH              | 2.2            | _   | V <sub>cc</sub> | V    |                                             | 1     |

| Input low voltage (TTL)     | VIL              | 0              | —   | 0.8             | V    |                                             | 2     |

| Input high voltage          | VIHR             | 3.0            | —   | V <sub>cc</sub> | V    |                                             | 3     |

| Input high voltage (CMOS)   | VIHC             | $0.7 V_{cc}$   |     | V <sub>cc</sub> | V    |                                             | 4     |

| Input low voltage (CMOS)    | VILC             | 0              | _   | $0.3  V_{cc}$   | V    |                                             | 4     |

| Output high voltage (TTL)   | VOH              | 2.4            |     | V <sub>cc</sub> | V    | —I <sub>он</sub> = 0.6 mA                   | 5     |

| Output low voltage (TTL)    | VOL              | 0              | _   | 0.4             | V    | I <sub>oL</sub> = 1.6 mA                    | 5     |

| Output high voltage (CMOS)  | VOHC             | $V_{cc} - 0.4$ |     | V <sub>cc</sub> | V    | —I <sub>он</sub> = 0.6 mA                   | 6     |

| Output low voltage (CMOS)   | VOLC             | 0              |     | 0.4             | V    | I <sub>oi</sub> = 0.6 mA                    | 6     |

| Input leakage current       | I <sub>IN</sub>  | -5             | _   | 5               | μΑ   | $VIN = 0 - V_{CC}$                          | 7     |

| Three-state leakage current | I <sub>TSL</sub> | -10            |     | 10              | μΑ   | $VOUT = 0 - V_{cc}$                         | 8     |

| Pull-up current             | I <sub>PL</sub>  | 2              | 10  | 20              | μΑ   | Vin = GND                                   | 9     |

| Power dissipation           | P <sub>w</sub>   | —              | _   | 50              | mW   | External clock<br>f <sub>cp</sub> = 2.4 MHz | 10    |

Notes: 1. Applied to input terminals and I/O common terminals, except terminals SYNC, CR, and RES.

2. Applied to input terminals and I/O common terminals, except terminals SYNC and CR.

- 3. Applied to terminal RES.

- 4. Applied to terminals SYNC and CR.

- 5. Applied to terminals DB0–DB7, WE, MA0–MA15, OE, CE, and MD0–MD7.

- 6. Applied to terminals SYNC, FLM, CL1, CL2, D1, D2, MA, and MB.

- 7. Applied to input terminals.

- 8. Applied to I/O common terminals. However, the current which flows into the output drive MOS is excluded.

- 9. Applied to  $\overline{\text{SYNC}}$ , DB0–DB7, and RD0–RD7.

- 10. The current which flows into the input and output circuits is excluded. When the input of CMOS is in the intermediate level, current flows through the input circuit, resulting in the increase of power supply current. To avoid this, input must be fixed at high or low.

#### Input Terminal

Applicable terminal: CS, E, RS, R/W, RES, CR (without pull-up MOS)

Applicable terminal: RD0–RD7 (with pull-up MOS)

#### **Output Terminal**

Applicable terminal: CL1, CL2, MA, MB, FLM, D1, D2, WE, OE, CE, MA0-MA15

#### **I/O Common Terminal**

Applicable terminal: DB0–DB7, <u>SYNC</u>, MD0–MD7 (MD0–MD7 have no pull-up MOS)

## **Timing Characteristics**

## HD61830B Clock Operation (V<sub>CC</sub> = 5 V ±10%, GND = 0V, T<sub>a</sub> = -20 to +75°C)

| Item                               | Symbol            | Min  | Тур | Max  | Unit | Notes |

|------------------------------------|-------------------|------|-----|------|------|-------|

| External clock operating frequency | f <sub>cp</sub>   | 100  | _   | 2400 | kHz  | 1     |

| External clock duty                | Duty              | 47.5 | 50  | 52.5 | %    | 1     |

| External clock rise time           | t <sub>rcp</sub>  | _    |     | 25.0 | ns   | 1     |

| External clock fall time           | t <sub>fcp</sub>  | _    | _   | 25.0 | ns   | 1     |

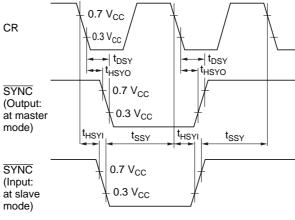

| SYNC output hold time              | t <sub>HSYO</sub> | 30   | _   | _    | ns   | 2, 3  |

| SYNC output delay time             | t <sub>DSY</sub>  |      | _   | 210  | ns   | 2, 3  |

| SYNC input hold time               | t <sub>HSYI</sub> | 10   |     | _    | ns   | 2     |

| SYNC input set-up time             | t <sub>ssy</sub>  | _    | _   | 180  | ns   | 2     |

Notes: 1. Applied to external clock input terminal.

2. Applied to SYNC terminal.

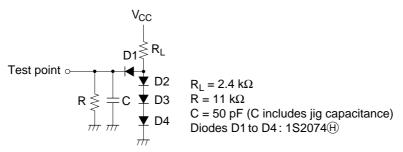

3. Testing load circuit.

## HD61830B MPU Interface ( $V_{CC} = 5V \pm 10\%$ , GND = 0V, $T_a = -20$ to $+75^{\circ}C$ )

| Item                  |            | Symbol           | Min  | Тур | Max | Unit |

|-----------------------|------------|------------------|------|-----|-----|------|

| Enable cycle time     |            | t <sub>CYC</sub> | 1.0  |     | _   | μs   |

| Enable pulse width    | High level | t <sub>wen</sub> | 0.45 | —   | —   | μs   |

|                       | Low level  | t <sub>WEL</sub> | 0.45 |     | —   | μs   |

| Enable rise time      |            | t <sub>Er</sub>  |      | _   | 25  | ns   |

| Enable fall time      |            | t <sub>Ef</sub>  |      | _   | 25  | ns   |

| Setup time            |            | t <sub>AS</sub>  | 140  |     | —   | ns   |

| Data setup time       |            | t <sub>DSW</sub> | 225  | _   | —   | ns   |

| Data delay time       |            | t <sub>DDR</sub> |      | _   | 225 | ns * |

| Data hold time        |            | t <sub>DHW</sub> | 10   | —   | —   | ns   |

| Address hold time     |            | t <sub>AH</sub>  | 10   | _   | _   | ns   |

| Output data hold time |            | t <sub>DH</sub>  | 20   | —   | _   | ns   |

Note: \* The following load circuit is connected for specification:

| Item                              | Symbol            | Min | Тур | Max | Unit | Notes   |

|-----------------------------------|-------------------|-----|-----|-----|------|---------|

| MA0–MA15 delay time               | t <sub>DMA</sub>  | _   |     | 300 | ns   | 1, 2, 3 |

| MA0–MA15 hold time                | t <sub>HMA</sub>  | 40  |     | _   | ns   | 1, 2, 3 |

| CE delay time                     | t <sub>DCE</sub>  | _   | _   | 300 | ns   | 1, 2, 3 |

| CE hold time                      | t <sub>HCE</sub>  | 40  | _   | _   | ns   | 1, 2, 3 |

| OE delay time                     | t <sub>DOE</sub>  | _   | _   | 300 | ns   | 1, 3    |

| OE hold time                      | t <sub>HOE</sub>  | 40  | _   | _   | ns   | 1, 3    |

| MD output delay time              | t <sub>DMD</sub>  | _   | _   | 150 | ns   | 1, 3    |

| MD output hold time               | t <sub>HMDW</sub> | 10  | _   | _   | ns   | 1, 3    |

| WE delay time                     | t <sub>DWE</sub>  | _   |     | 150 | ns   | 1, 3    |

| WE clock pulse width              | t <sub>WWE</sub>  | 150 | _   | _   | ns   | 1, 3    |

| MD output high impedance time (1) | t <sub>ZMDF</sub> | 10  |     | _   | ns   | 1, 3    |

| MD output high impedance time (2) | t <sub>zmdr</sub> | 50  | _   | _   | ns   | 1, 3    |

| RD data set-up time               | t <sub>srd</sub>  | 50  | _   | _   | ns   | 2       |

| RD data hold time                 | t <sub>HRD</sub>  | 40  |     | _   | ns   | 2       |

| MD data set-up time               | t <sub>smD</sub>  | 50  |     | _   | ns   | 2       |

| MD data hold time                 | t <sub>HMD</sub>  | 40  |     | _   | ns   | 2       |

## HD61830B External RAM and ROM Interface (V<sub>CC</sub> = 5V $\pm$ 10%, GND = 0V, T<sub>a</sub> = -20 to +75°C)

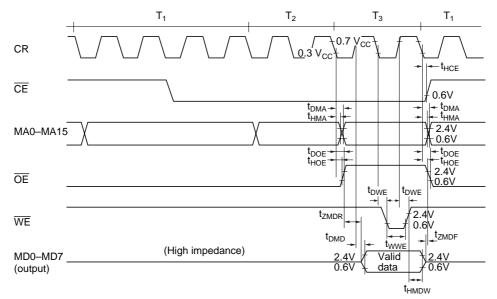

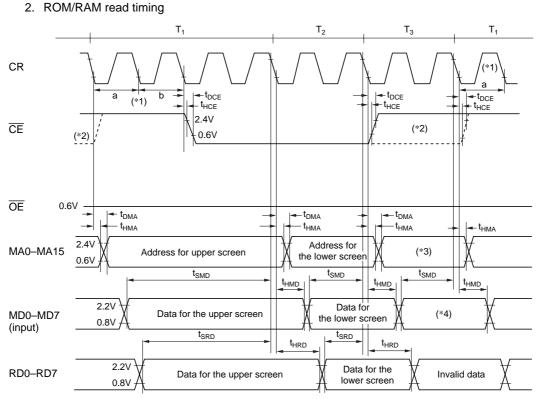

Notes: 1. RAM write timing

T1: Memory data refresh timing for upper screen

T2: Memory data refresh timing for lower screen

T3: Memory read/write timing

- \*1 This figures shows the timing for  $H_p = 8$ . For  $H_p = 7$ , time shown by "b" becomes zero. For  $H_p = 6$ , time shown by "a" and "b" become zero. Therefore, the number of clock pulses during T1 become 4, 3, or 2 in the case of  $H_p = 8$ ,  $H_p = 7$ , or  $H_p = 6$  respectively.

- \*2 The waveform for instructions with memory read is shown with a dash line. In other cases, the waveform shown with a solid line is generated.

- \*3 When an instruction with RAM read/write is executed, the value of cursor address is output. In other cases, invalid data is output.

- \*4 When an instruction with RAM read is executed, HD61830B latches the data at this timing. In other cases, this data is invalid.

- 3. Test load circuit

| Item                          | Symbol            | Min  | Тур | Max | Unit | Notes |

|-------------------------------|-------------------|------|-----|-----|------|-------|

| Clock cycle time              | t <sub>WCL2</sub> | 416  | _   | —   | ns   | 1, 3  |

| Clock pulse width(high level) | t <sub>wch</sub>  | 150  | _   |     | ns   | 1, 3  |

| Clock pulse width(low level)  | t <sub>WCL</sub>  | 150  | _   |     | ns   | 1, 3  |

| Data delay time               | t <sub>DD</sub>   | _    | _   | 50  | ns   | 1, 3  |

| Data hold time                | t <sub>DH</sub>   | 100  | _   | _   | ns   | 1, 3  |

| Clock phase difference (1)    | t <sub>CL1</sub>  | 100  | _   |     | ns   | 1, 3  |

| Clock phase difference (2)    | t <sub>CL2</sub>  | 100  | _   | _   | ns   | 1, 3  |

| Clock phase difference (3)    | t <sub>CL3</sub>  | 100  | _   | _   | ns   | 1, 3  |

| MA, MB delay time             | t <sub>DM</sub>   | -200 | _   | 200 | ns   | 1, 3  |

| FLM set-up time               | t <sub>sF</sub>   | 400  | _   | _   | ns   | 2, 3  |

| FLM hold time                 | t <sub>HF</sub>   | 1000 | _   | _   | ns   | 2, 3  |

| MA set-up time                | t <sub>sma</sub>  | 400  | _   | _   | ns   | 2, 3  |

| MA hold time                  | t <sub>HMA</sub>  | 1000 |     |     | ns   | 2, 3  |

# HD61830B LCD Driver Interface (V<sub>CC</sub> = 5V ±10%, GND = 0V, Ta = -20 to +75°C)

Notes: 1.

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

Hitachi Europe Ltd.

Whitebrook Park Lower Cookham Road

Maidenhead

Electronic Components Group.

Fax: <44> (1628) 778322

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# IITACHI Hitachi. Ltd.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109 URL NorthAmerica http:semiconductor.hitachi.com/ Europe http://www.hitachi-eu.com/hel/ecg http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.has.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKóng) http://www.hitachi.com.hk/eng/bo/grp3/index.htm http://www.hitachi.co.jp/Sicd/indx.htm Japan For further information write to: Hitachi Semiconductor Hitachi Europe GmbH Hitachi Asia Pte. Ltd (America) Inc. Electronic components Group Dornacher Straße 3 16 Collyer Quay #20-00 179 East Tasman Drive, Hitachi Tower San Jose, CA 95134 D-85622 Feldkirchen, Munich Singapore 049318 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Germany Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00 Tel: 535-2100 Fax: 535-1533

Hitachi Asia I td Taipei Branch Office 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180 Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000

Hitachi Asia (Hong Kong) Ltd Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.