FAIRCHILD

SEMICONDUCTOR

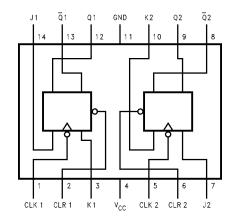

# DM7473 Dual Master-Slave J-K Flip-Flops with Clear and Complementary Outputs

#### **General Description**

This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flops after a complete clock pulse. While the clock is LOW the slave is isolated from the master. On the positive transition of the clock, the data from the J and K inputs is transferred to the master. While the clock is HIGH the J and K inputs are disabled. On the

**Ordering Code:**

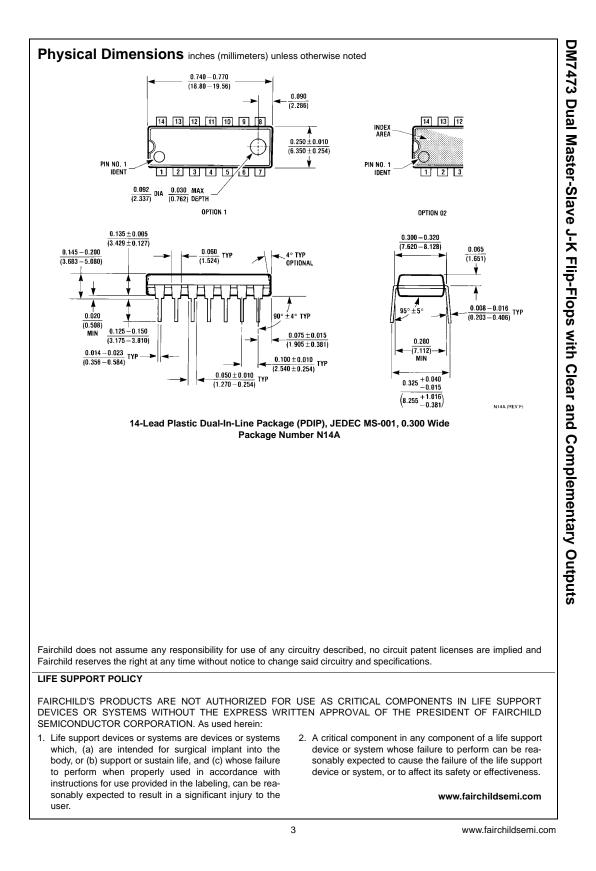

| Order Number | Package Number | Package Description                                                   |

|--------------|----------------|-----------------------------------------------------------------------|

| DM7473N      | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

inputs.

## **Connection Diagram**

|     | Package Description                            |     |   |   |   |   |  |  |  |

|-----|------------------------------------------------|-----|---|---|---|---|--|--|--|

| ו-L | -Line Package (PDIP), JEDEC MS-001, 0.300 Wide |     |   |   |   |   |  |  |  |

| I   | Function Table                                 |     |   |   |   |   |  |  |  |

|     | Inputs Outputs                                 |     |   |   |   |   |  |  |  |

|     | CLR                                            | CLK | J | к | Q | Ø |  |  |  |

|     | L                                              | х   | Х | Х | L | Н |  |  |  |

negative transition of the clock, the data from the master is transferred to the slave. The logic states of the J and K

inputs must not be allowed to change while the clock is

HIGH. Data transfers to the outputs on the falling edge of

the clock pulse. A LOW logic level on the clear input will

reset the outputs regardless of the logic states of the other

|   | L                    | Х | Х | Х | L              | Н                |  |  |

|---|----------------------|---|---|---|----------------|------------------|--|--|

|   | Н                    | л | L | L | Q <sub>0</sub> | $\overline{Q}_0$ |  |  |

|   | Н                    | л | н | L | н              | L                |  |  |

|   | Н                    | л | L | н | L              | н                |  |  |

|   | Н                    | л | н | н | Τος            | ggle             |  |  |

| F | H = HIGH Logic Level |   |   |   |                |                  |  |  |

L = LOW Logic Level

X = Either LOW or HIGH Logic Level

Positive pulse data. the J and K inputs must be held constant while the clock is HIGH. Data is transferred to the outputs on the falling edge of the clock pulse.

$\mathsf{Q}_0$  = The output logic level before the indicated input conditions were established.

Toggle = Each output changes to the complement of its previous level on each HIGH level clock pulse.

© 2000 Fairchild Semiconductor Corporation DS006525

www.fairchildsemi.com

DM7473

## Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 5.5V                              |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol           | Pa                                | rameter    | Min  | Nom | Max  | Units |

|------------------|-----------------------------------|------------|------|-----|------|-------|

| V <sub>CC</sub>  | Supply Voltage                    |            | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>  | HIGH Level Input Voltage          |            | 2    |     |      | V     |

| V <sub>IL</sub>  | LOW Level Input Voltage           |            |      |     | 0.8  | V     |

| I <sub>ОН</sub>  | HIGH Level Output Current         |            |      |     | -0.4 | mA    |

| l <sub>OL</sub>  | LOW Level Output Current          |            |      |     | 16   | mA    |

| f <sub>CLK</sub> | Clock Frequency (Note 3)          |            | 0    |     | 15   | MHz   |

| t <sub>W</sub>   | Pulse Width                       | Clock HIGH | 20   |     |      |       |

|                  | (Note 3)                          | Clock LOW  | 47   |     |      | ns    |

|                  |                                   | Clear LOW  | 25   |     |      |       |

| t <sub>SU</sub>  | Input Setup Time (Note 2)(Note 3) |            | 0↑   |     |      | ns    |

| н                | Input Hold Time (Note 2)(Note 3)  |            | 0↓   |     |      | ns    |

| T <sub>A</sub>   | Free Air Operating Temperature    |            | 0    |     | 70   | °C    |

Note 2: The symbol  $(\uparrow, \downarrow)$  indicates the edge of the clock pulse is used for reference:  $(\uparrow)$  for rising edge,  $(\downarrow)$  for falling edge.

Note 3:  $T_A$  = 25°C and  $V_{CC}$  = 5V.

## **Electrical Characteristics**

| Symbol          | Parameter                                              | Conditions                                   |       | Min | Typ (Note 4) | Max  | Units |  |  |

|-----------------|--------------------------------------------------------|----------------------------------------------|-------|-----|--------------|------|-------|--|--|

| VI              | Input Clamp Voltage                                    | $V_{CC} = Min, I_I = -12 \text{ mA}$         |       |     |              | -1.5 | V     |  |  |

| V <sub>OH</sub> | HIGH Level                                             | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max | 2.4   | 2.4 |              | v    |       |  |  |

|                 | Output Voltage                                         | $V_{IL} = Max, V_{IH} = Min$                 |       | 3.4 |              | v    |       |  |  |

| V <sub>OL</sub> | LOW Level V <sub>CC</sub> = Min, I <sub>OL</sub> = Max |                                              |       | 0.2 | 0.4          | v    |       |  |  |

|                 | Output Voltage                                         | V <sub>IH</sub> = Min, V <sub>IL</sub> = Max |       |     | 0.2          | 0.4  | v     |  |  |

| l <sub>l</sub>  | Input Current @ Max Input Voltage                      | $V_{CC} = Max, V_I = 5.5V$                   |       |     |              | 1    | mA    |  |  |

| IIH             | HIGH Level                                             | V <sub>CC</sub> = Max                        | J, K  |     |              | 40   |       |  |  |

|                 | Input Current                                          | $V_{I} = 2.4V$                               | Clock |     |              | 80   | μΑ    |  |  |

|                 |                                                        |                                              | Clear |     |              | 80   |       |  |  |

| IIL             | LOW Level Input                                        | V <sub>CC</sub> = Max                        | J, K  |     |              | -1.6 |       |  |  |

|                 | Current                                                | $V_I = 0.4V$                                 | Clock |     |              | -3.2 | mA    |  |  |

|                 |                                                        |                                              | Clear |     |              | -3.2 |       |  |  |

| los             | Short Circuit Output Current                           | V <sub>CC</sub> = Max (Note 5)               |       | -18 |              | -55  | mA    |  |  |

| I <sub>CC</sub> | Supply Current                                         | V <sub>CC</sub> = Max, (Note 6)              |       |     | 18           | 34   | mA    |  |  |

Note 4: All typicals are at V<sub>CC</sub> = 5V,  $T_A = 25^{\circ}C$ .

Note 5: Not more than one output should be shorted at a time.

Note 6: With all outputs OPEN, I<sub>CC</sub> is measured with the Q and Q outputs HIGH in turn. At the time of measurement the clock input grounded.

## Switching Characteristics at $V_{CC} = 5V$ and $T_A = 25^{\circ}C$

| Symbol           | Parameter                                       | From (Input)                 | $R_L = 400\Omega$ , | C <sub>L</sub> = 15 pF | Units |

|------------------|-------------------------------------------------|------------------------------|---------------------|------------------------|-------|

|                  | i arameter                                      | To (Output)                  | Min                 | Max                    | Unita |

| f <sub>MAX</sub> | Maximum Clock Frequency                         |                              | 15                  |                        | MHz   |

| t <sub>PHL</sub> | Propagation Delay Time HIGH-to-LOW Level Output | Clear to Q                   |                     | 40                     | ns    |

| t <sub>PLH</sub> | Propagation Delay Time LOW-to-HIGH Level Output | Clear to Q                   |                     | 25                     | ns    |

| t <sub>PHL</sub> | Propagation Delay Time HIGH-to-LOW Level Output | Clock to Q or $\overline{Q}$ |                     | 40                     | ns    |

| t <sub>PLH</sub> | Propagation Delay Time LOW-to-HIGH Level Output | Clock to Q or $\overline{Q}$ |                     | 25                     | ns    |

www.fairchildsemi.com