# **Application Note AN-9042**

## Smart Power Module Tiny-DIP-SPM User's Guide

Written by:

GuHo Jung

SooHyuk Han

BokKeun Song

JongMu Lee

SPM & System Eng Group FAIRCHILD SEMICONDUCTOR

## **Contents**

| 1.        | Introduction                                      | . 4  |

|-----------|---------------------------------------------------|------|

| 1.1.      | . Introduction                                    | 4    |

| 1.2.      | . Tiny DIP SPM Design Concept                     | 4    |

| 2.        | TINY-DIP-SPM Product Guide                        | . 6  |

| 2.1       | Ordering Information                              | 6    |

| 2.2       | Product Line-Up                                   | 6    |

| 2.3       | Applications                                      | 7    |

| 2.4       | Package Structure                                 | 7    |

| 3.        | Outline and Pin Description                       | . 8  |

| 3.1       | Outline Drawings                                  | 8    |

| 3.2       | Description of the input and output pins          | 11   |

| 4.        | Internal Circuit and Features                     | 15   |

| 5.        | Absolute Maximum Ratings                          | 17   |

| 5.1       | Electrical Maximum Ratings                        | . 17 |

| 6.        | Interface Circuit                                 | 19   |

| 6.1       | Input/Output Signal Connection                    | . 19 |

| 6.2       | General Interface Circuit Example                 | . 22 |

| 6.3       | Recommended Wiring of Shunt Resistor              | . 24 |

| 6.4       | Snubber Capacitor                                 | . 24 |

| <b>7.</b> | Function and Protection Circuit                   | 26   |

| 7.1       | SPM Functions versus Control Power Supply Voltage | . 26 |

| 7.2       | Under-Voltage Protection                          | . 27 |

| 8.        | Bootstrap Circuit                                 | 29   |

| 8.1       | Operation of a Bootstrap Circuit                  | . 29 |

| 8.2       | Initial Charging of a Bootstrap Capacitor         | . 29 |

## Tiny-DIP-SPM User's Guide Version 1.0(2007.09.05)

| 8.3         | Selection of a Bootstrap Capacitor                                                | . 31 |

|-------------|-----------------------------------------------------------------------------------|------|

| 8.4         | Selection of a Bootstrap Diode                                                    | . 31 |

| 8.5         | Selection of Series Resistance                                                    | . 31 |

| 8.6         | Charging and Discharging of the Bootstrap Capacitor during PWM-Inverter Operation | . 32 |

| 8.7         | Recommended Boot Strap Operation Circuit and Parameters                           | . 33 |

| <b>9.</b> . | Power Loss and Dissipation                                                        | 34   |

| 9.1         | Power Loss of SPM                                                                 | . 34 |

| 9.2         | Calculation Method for Conduction Loss                                            | . 34 |

| 9.3         | Calculation Method for Switching Loss                                             | . 36 |

| 9.4         | Power Dissipation Design                                                          | . 36 |

| 9.5         | Power Cycle                                                                       | . 37 |

| 10.         | Packaging and Installation Guide                                                  | 39   |

| 10.1        | Heatsink Mounting                                                                 | . 39 |

| 10.2        | P. Handling Precaution                                                            | . 42 |

| 10.3        | Marking Specifications                                                            | . 44 |

| 10.4        | Packaging Specifications                                                          | . 48 |

## 1. Introduction

#### 1.1. Introduction

The terms "energy-saving" and "quiet-running" are becoming very important in the world of variable speed motor drives. For low-power motor control, there are increasing demands for compactness, built-in control, and lower overall-cost. An important consideration, in justifying the use of inverters in these applications, is to optimize the total-cost-performance ratio of the overall drive system. In other words, the systems have to be less noisy, more efficient, smaller and lighter, more advanced in function and more accurate in control with a very low cost.

In order to meet these needs, Fairchild has developed a new series of compact, high-functionality, and high efficiency power semiconductor devices called "Tiny-DIP-SPM (Smart Power Module)". Tiny-DIP-SPM-based inverters are now considered an attractive alternative to conventional discrete-based inverters for low-power motor drives, specifically for appliances such as washing machines, air-conditioners, refrigerators, water pumps etc.

Tiny-DIP-SPM combines optimized circuit protection and drive matched to the FRFET's switching characteristics. System reliability is further enhanced by the integrated under-voltage protection function and short circuit protection function. The high speed built-in HVIC provides an opto-coupler-less FRFET gate driving capability that further reduces the overall size of the inverter system design. Additionally, the incorporated HVIC allows the use of a single-supply drive topology without negative bias.

The objective of this application note is to show the details of TINY-DIP-SPM power circuit design and its application to TINY-DIP-SPM users. This document provides design examples that should enable motor drive design engineers to create efficient optimized designs with shortened design cycles by employing Fairchild TINY-DIP-SPM products.

#### 1.2. Tiny DIP SPM Design Concept

Tiny-DIP-SPM is a tiny smart power module (SPM) based on FRFET technology as a compact inverter solution for small power motor drive applications such as fan motor and water suppliers. It is composed of 6 fast-recovery MOSFET(FRFET), and 3 half-bridge HVICs for FRFET gate driving. Tiny-DIP-SPM provides low electromagnetic interference (EMI) characteristics with optimized switch speed. Moreover, since it employs FRFET as a power switch, it has much better ruggedness and larger safe operation area (SOA) than that of an FRFET-based power module or one-chip solution. The package is optimized for the thermal performance and compactness for the use in the built-in motor application and any other application where the assembly space is concerned. Tiny-DIP-SPM is the most solution for the compact inverter providing the energy efficiency, compactness, and low electromagnetic interference.

September. 2007

Module

## Tiny-DIP-SPM User's Guide Version 1.0(2007.09.05)

The detailed features and integrated functions of Tiny-DIP-SPM are as follows;

- 500V 2.0A ~ 3.0A 3phase FRFET inverter including high voltage integrated circuit(HVIC)

- 3 divided negative dc-link terminals for inverter current sensing applications

- HVIC for gate driving and undervoltage protection

- 3/5V CMOS/TTL compatible, active-high interface

- Optimized for low electromagnetic interference

- Isolation voltage rating of 1500Vrms for 1min

- Surface mounted device package(DIP, SMD, DOUBLE-DIP)

- Moisture sensitive Level(MSL3)

- Extende VB pin for isolation

## 2. TINY-DIP-SPM Product Guide

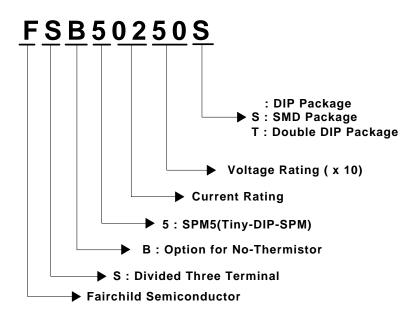

## 2.1 Ordering Information

## 2.2 Product Line-Up

Table 2.1 Lineup of Tiny-DIP-SPM Family

|                          |                   | Current Rating |       |                           |                       |                            |                      |

|--------------------------|-------------------|----------------|-------|---------------------------|-----------------------|----------------------------|----------------------|

| Part<br>Number           | BV <sub>DSS</sub> | Peak           | DC    | R <sub>DS(on)</sub> (typ) | V <sub>SD</sub> (max) | R <sub>th(i-c)</sub> (max) | Isolation<br>Voltage |

| FSB50325                 | 250 V             | 3.0 A          | 1.5 A | 1.4 Ω                     | 1.2 V @ 1 A           | 10.2 °C/W                  | 1500 V               |

| FSB50250                 | 500 V             | 2.0 A          | 1.0 A | 3.3 Ω                     | 1.2 V @ 0.5 A         | 9.3 °C/W                   | 1 min.               |

| FSB50450                 | 500 V             | 3.0 A          | 1.5 A | 1.9 Ω                     | 1.2 V @ 1 A           | 8.9 °C/W                   | 1 1111111.           |

| FSB50325S <sup>(1)</sup> | 250 V             | 3.0 A          | 1.5 A | 1.4 Ω                     | 1.2 V @ 1 A           | 10.2 °C/W                  | 4500 \/              |

| FSB50250S <sup>(1)</sup> | 500 V             | 2.0 A          | 1.0 A | 3.3 Ω                     | 1.2 V @ 0.5 A         | 9.3 °C/W                   | 1500 V               |

| FSB50450S <sup>(1)</sup> | 500 V             | 3.0 A          | 1.5 A | 1.9 Ω                     | 1.2 V @ 1 A           | 8.9 °C/W                   | 1 min.               |

| FSB50325T <sup>(2)</sup> | 500V              | 3.0A           | 1.5A  | 1.4 Ω                     | 1.2 V @ 1 A           | 10.2 °C/W                  |                      |

| FSB50250S <sup>(2)</sup> | 500 V             | 2.0 A          | 1.0 A | 3.3 Ω                     | 1.2 V @ 0.5 A         | 9.3 °C/W                   | 1500 V               |

| FSB50450T <sup>(2)</sup> | 500V              | 3.0 A          | 1.5 A | 1.9 Ω                     | 1.2 V @ 1 A           | 8.9 °C/W                   | 1 min.               |

| FSB50550T <sup>(2)</sup> | 500V              | 3.5A           | 1.8A  | 1.3 Ω                     | 1.2 V @ 1.2 A         | 8.6 °C/W                   |                      |

<sup>(1)</sup> SMP Package

<sup>(2)</sup> Double DIP Package

#### 2.3 Applications

Tiny smart power module based on FRFET technology as a compact inverter solution for small power motor drive applications such as fan motor and water suppliers.

#### 2.4 Package Structure

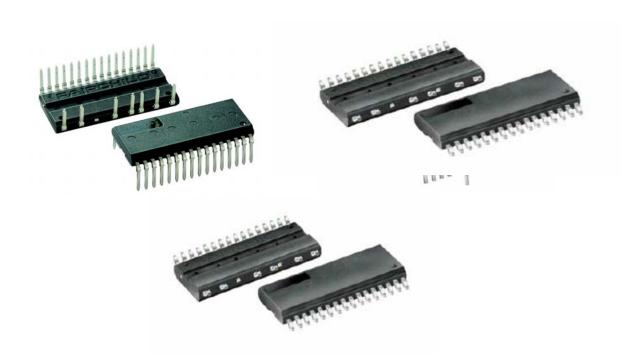

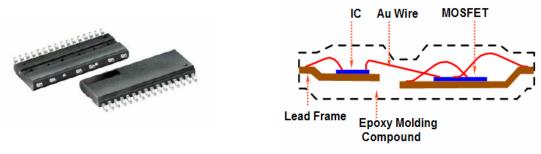

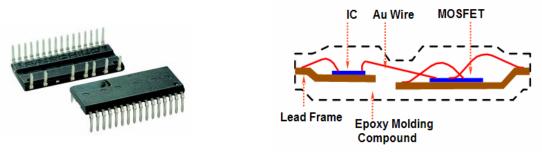

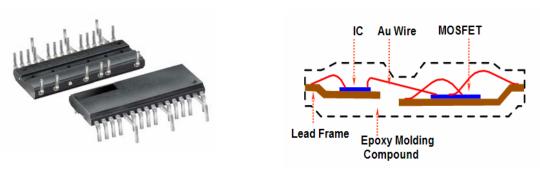

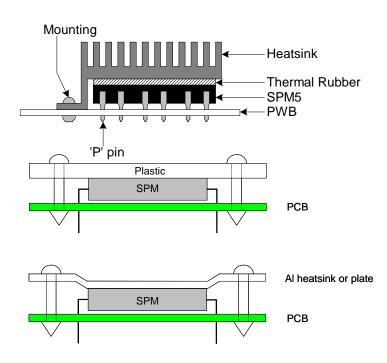

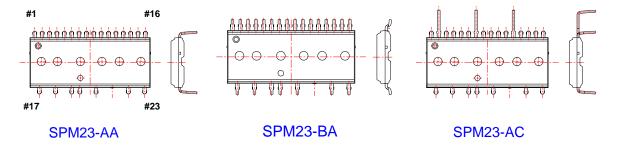

Figure 2.1~2.3 contains a picture and an internal structure illustration of the TINY Mini DIP SPM. The TINY DIP SPM is an ultra-compact power module, which integrates power components, high and low side gate drivers and protection circuitry for AC100 ~ 220V class low power motor drive inverter control into a dual-in-line transfer mold package.

Figure 2.1 Pictures and Cross section of DIP-Package(SPM 23BA).

Figure 2.2 Pictures and Cross section of SMD-Package(SPM 23AA).

Figure 2.3 Pictures and Cross section of Double DIP-Package(SPM 23AC).

17 P

19 N<sub>∪</sub>

$20 N_{V}$

21 V

$22 N_W$

23 W

18

## 3. Outline and Pin Description

## **Outline Drawings**

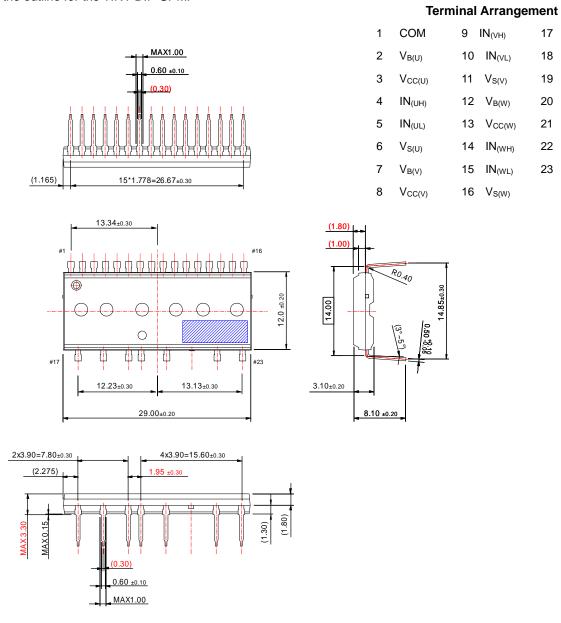

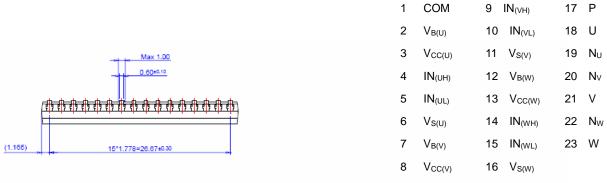

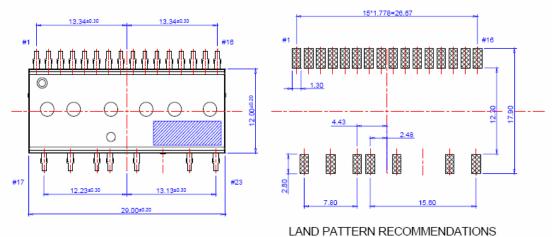

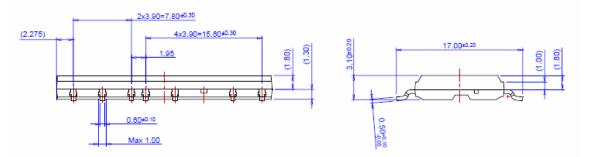

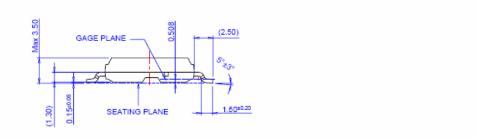

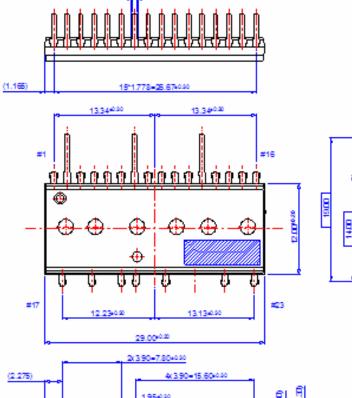

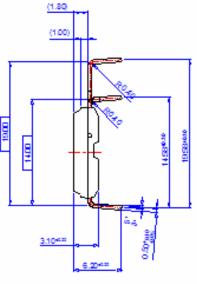

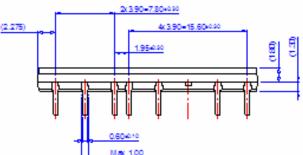

This section includes the outline drawings and dimensions for the Tiny-DIP-SPM. Figure 3.1 ~ 3.3 is the outline for the TINY-DIP-SPM.

Figure 3.1 Outline of the TINY-DIP-SPM(package SPM23AA)

#### **Terminal Arrangement**

Figure 3.2 Outline of the TINY-SMD-SPM(package SPM23BA)

COM

$V_{CC(V)}$

#### **Terminal Arrangement**

9 IN<sub>(VH)</sub>

17 P

16 NC

Figure 3.3 Outline of the TINY-DOUBLE-DIP-SPM(package SPM23AC)

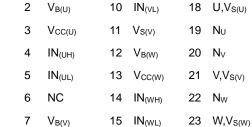

## 3.2 Description of the input and output pins

Table 3.1~3.2 defines the Tiny-DIP-SPM input and output pins. The detailed functional descriptions are as follows :

Table 3.1 Pin description for TINY-DIP-SPM and Tiny-SMD-SPM

| Pin Number | Pin Name           | Pin Description                                         |  |  |

|------------|--------------------|---------------------------------------------------------|--|--|

| 1          | COM                | IC Common Supply Ground                                 |  |  |

| 2          | $V_{B(U)}$         | Bias Voltage for U Phase High Side FRFET Driving        |  |  |

| 3          | $V_{CC(U)}$        | Bias Voltage for U Phase IC and Low Side FRFET Driving  |  |  |

| 4          | IN <sub>(UH)</sub> | Signal Input for U Phase High-side                      |  |  |

| 5          | IN <sub>(UL)</sub> | Signal Input for U Phase Low-side                       |  |  |

| 6          | $V_{S(U)}$         | Bias Voltage Ground for U Phase High Side FRFET Driving |  |  |

| 7          | $V_{B(V)}$         | Bias Voltage for V Phase High Side FRFET Driving        |  |  |

| 8          | $V_{CC(V)}$        | Bias Voltage for V Phase IC and Low Side FRFET Driving  |  |  |

| 9          | IN <sub>(VH)</sub> | Signal Input for V Phase High-side                      |  |  |

| 10         | IN <sub>(VL)</sub> | Signal Input for V Phase Low-side                       |  |  |

| 11         | V <sub>S(V)</sub>  | Bias Voltage Ground for V Phase High Side FRFET Driving |  |  |

| 12         | $V_{B(W)}$         | Bias Voltage for W Phase High Side FRFET Driving        |  |  |

| 13         | V <sub>CC(W)</sub> | Bias Voltage for W Phase IC and Low Side FRFET Driving  |  |  |

| 14         | IN <sub>(WH)</sub> | Signal Input for W Phase Hide-side                      |  |  |

| 15         | IN <sub>(WL)</sub> | Signal Input for W Phase Low-side                       |  |  |

| 16         | $V_{S(W)}$         | Bias Voltage Ground for W Phase High Side FRFET Driving |  |  |

| 17         | Р                  | Positive DC-Link Input                                  |  |  |

| 18         | U                  | Output for U Phase                                      |  |  |

| 19         | N <sub>U</sub>     | Negative DC-Link Input for U Phase                      |  |  |

| 20         | N <sub>V</sub>     | Negative DC-Link Input for V Phase                      |  |  |

| 21         | V                  | Output for V Phase                                      |  |  |

| 22         | N <sub>W</sub>     | Negative DC-Link Input for W Phase                      |  |  |

| 23         | W                  | Output for W Phase                                      |  |  |

Table 3.2 Pin description for TINY-DIP-SPM(Package SPM23AC-DOUBLE DIP)

| Pin Number | Pin Name             | Pin Description                                                      |

|------------|----------------------|----------------------------------------------------------------------|

| 1          | COM                  | IC Common Supply Ground                                              |

| 2          | $V_{B(U)}$           | Bias Voltage for U Phase High Side FRFET Driving                     |

| 3          | V <sub>CC(U)</sub>   | Bias Voltage for U Phase IC and Low Side FRFET Driving               |

| 4          | IN <sub>(UH)</sub>   | Signal Input for U Phase High-side                                   |

| 5          | IN <sub>(UL)</sub>   | Signal Input for U Phase Low-side                                    |

| 6          | NC                   | No Connection                                                        |

| 7          | $V_{B(V)}$           | Bias Voltage for V Phase High Side FRFET Driving                     |

| 8          | V <sub>CC(V)</sub>   | Bias Voltage for V Phase IC and Low Side FRFET Driving               |

| 9          | IN <sub>(VH)</sub>   | Signal Input for V Phase High-side                                   |

| 10         | IN <sub>(VL)</sub>   | Signal Input for V Phase Low-side                                    |

| 11         | NC                   | No Connection                                                        |

| 12         | $V_{B(W)}$           | Bias Voltage for W Phase High Side FRFET Driving                     |

| 13         | V <sub>CC(W)</sub>   | Bias Voltage for W Phase IC and Low Side FRFET Driving               |

| 14         | IN <sub>(WH)</sub>   | Signal Input for W Phase Hide-side                                   |

| 15         | IN <sub>(WL)</sub>   | Signal Input for W Phase Low-side                                    |

| 16         | NC                   | No Connection                                                        |

| 17         | Р                    | Positive DC-Link Input                                               |

| 18         | U, V <sub>S(U)</sub> | Output for U Phase & Bias Voltage Ground for High Side FRFET Driving |

| 19         | N <sub>U</sub>       | Negative DC-Link Input for U Phase                                   |

| 20         | N <sub>V</sub>       | Negative DC-Link Input for V Phase                                   |

| 21         | V, V <sub>S(V)</sub> | Output for U Phase & Bias Voltage Ground for High Side FRFET Driving |

| 22         | N <sub>W</sub>       | Negative DC-Link Input for W Phase                                   |

| 23         | W, V <sub>S(W)</sub> | Output for U Phase & Bias Voltage Ground for High Side FRFET Driving |

# High-Side Bias Voltage Pins for Driving the FRFET / High-Side Bias Voltage Ground Pins for Driving the FRFET

Pin :  $V_{B(U)} - V_{S(U)}$  ,  $V_{B(V)} - V_{S(V)}$  ,  $V_{B(W)} - V_{S(W)}$

- These are drive power supply pins for providing gate drive power to the High-Side FRFETs.

- The virtue of the ability to boot-strap the circuit scheme is that no external power supplies are required for the high-side FRFETs.

- Each boot-strap capacitor is generally charged from the Vcc supply during the ON-state of the corresponding low-side FRFET.

- In order to prevent malfunctions caused by noise and ripple in supply voltage, a good quality (low ESR, low ESL) filter capacitor should be mounted very close to these pins.

#### Low-Side Bias Voltage Pin / High-Side Bias Voltage Pins

$Pin: V_{CC(U),} V_{CC(V),} V_{CC(W)}$

- These are control supply pins for the built-in ICs.

- These three pins should be connected externally.

- In order to prevent malfunctions caused by noise and ripple in the supply voltage, a good quality (low ESR, low ESL) filter capacitor should be mounted very close to these pins.

#### Low-Side Common Supply Ground Pin

Pin: COM

- The Tiny-DIP-SPM common pin connects to the control ground for the internal ICs.

- Important! To avoid noise influences the main power circuit current should not be allowed to flow through this pin.

#### Signal Input Pins

$Pin : IN_{(UL)}, IN_{(VL)}, IN_{(WL)}, IN_{(UH)}, IN_{(VH)}, IN_{(WH)}$

- These are pins to control the operation of the built-in FRFETs .

- They are activated by voltage input signals. These terminals are internally connected to a schmitt trigger circuit composed of 5V-class CMOS.

- The signal logic of these pins is Active-high. That is, the FRFET associated with each of these pins will be turned "ON" when a sufficient logic voltage is applied to these pins.

- The wiring of each input should be as short as possible to protect the Tiny-DIP-SPM against noise influences.

- To prevent signal oscillations, an RC coupling is recommended as illustrated in Figure 8.3 ~ 8.4..

#### Positive DC-Link Pin

Pin:P

• This is the DC-link positive power supply pin of the inverter.

## Tiny-DIP-SPM User's Guide Version 1.0(2007.09.05)

- It is internally connected to the collectors of the high-side FRFETs.

- In order to suppress the surge voltage caused by the DC-link wiring or PCB pattern inductance, connect a smoothing filter capacitor close to this pin. (Typically Metal Film Capacitor are used)

#### Negative DC-Link Pins

$Pin:N_U,\,N_V,\,N_W$

- These are the DC-link negative power supply pins (power ground) of the inverter.

- These pins are connected to the low-side FRFET sources of the each phase.

#### **Inverter Power Output Pin**

Pin: U, V, W

• Inverter output pins for connecting to the inverter load (e. g. motor).

September. 2007

Module

## 4. Internal Circuit and Features

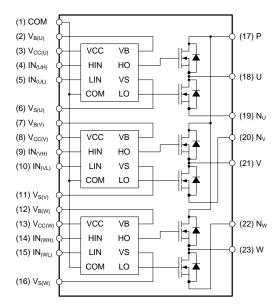

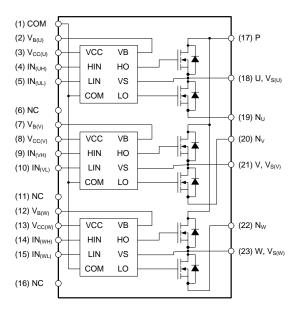

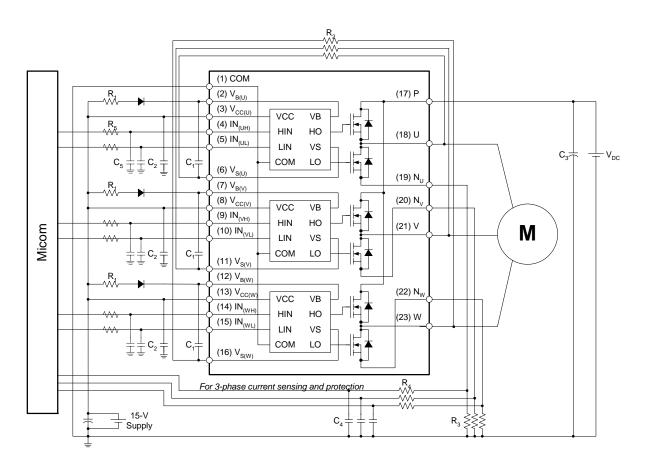

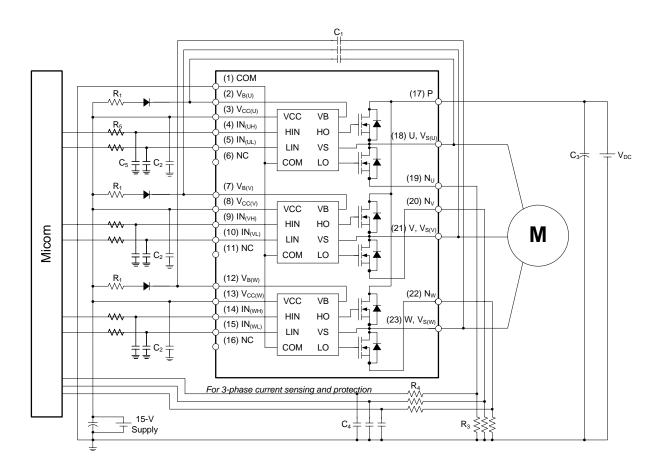

Figure 4.1~4.2 illustrates the internal block diagram of the Tiny-DIP-SPM. It should be noted that the Tiny-DIP-SPM consists of a six fast-recovery MOSFET(FRFET) and three half-bridge HVICs for FRFET gate driving. The detailed features and integrated functions of Tiny-DIP-SPM and the benefits acquired by using it are described as follows.

Figure 4.1 Internal circuit of Tiny-DIP-SPM and Tiny-SMD-SPM.

Figure 4.2 Internal circuit of Tiny-Double-DIP-SPM.

#### Features

- 500V/1A to 1.5A and 250V/1.5A rating in one package size(mechanical layouts are identical).

- Low-loss efficient FRFETs optimized for motor drive applications.

- Compact and low-cost transfer mold package allows inverter design miniaturization.

- High reliability due to fully tested coordination of HVIC and FRFETs.

- 3-phase FRFET inverter bridge including control IC for gate driving and protection.

- High & Low-side : Control circuit under voltage (UV) protection

- (without fault signal output)

- Single-grounded power supply and opto-coupler-less interface due to built-in HVIC.

- FRFET switching characteristics matched to system requirement.

- Low leakage current and high isolation voltage.

- Divided 3-N Power Terminals provide easy and cost-effective phase current sensing.

- Active-high input signal logic, resolves the startup and shutdown sequence constraint between the control supply and control input, this provides fail-safe operation with direct connection between the Tiny-DIP-SPM and a 3.3V CPU or DSP. Additional external sequence logic is not needed.

#### Integrated Functions

- Inverter high-side FRFETs: Gate drive circuit, High-voltage isolated high-speed level shifting,

Control supply under-voltage (UV) protection

- Inverter low-side FRFETs: Gate drive circuit, Control supply circuit under-voltage protection

- Input interface: 3.3V, 5V CMOS/LSTTL compatible, Schmitt trigger input, Active high.

## 5. Absolute Maximum Ratings

## 5.1 Electrical Maximum Ratings

#### **Turn-off Switching**

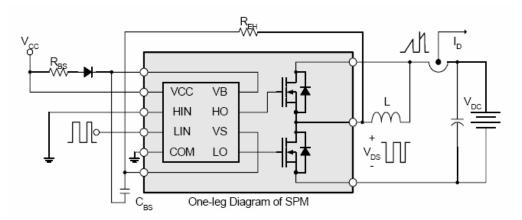

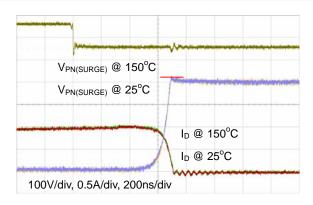

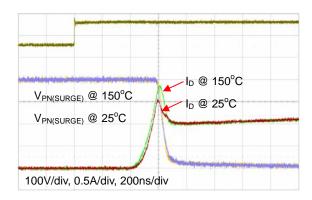

The FRFETs incorporated into the Tiny-DIP-SPM have a 500Volt  $V_{DSS}$  rating. The 450V  $V_{PN(surge)}$  rating is obtained by subtracting the surge voltage (50V or less, generated by the Tiny-DIP-SPM's internal stray inductances) from  $V_{DSS}$ . Moreover, the 400V  $V_{PN}$  rating is obtained by subtracting the surge voltage (50V or less, generated by the stray inductance between the Tiny-SIP-SPM and the DC-link capacitor) from  $V_{PN(Surge)}$ .

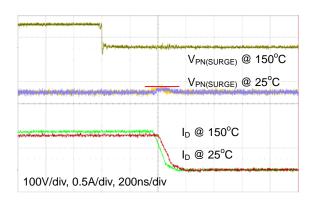

#### **Short-circuit Operation**

In case of short-circuit turn-off, the 400V  $V_{PN(PROT)}$  rating is obtained by subtracting the surge voltage(50V or less, generated by the stray inductance between the Tiny-DIP-SPM and DC-link capacitor)  $V_{PN(Surge)}$ .

| Item                                 | Symbol                 | Condition            | Rating    | Unit |

|--------------------------------------|------------------------|----------------------|-----------|------|

| Supply Voltage                       | V <sub>DC</sub>        | Applied to DC-link   | 400       | V    |

| Supply Voltage (Surge)               | V <sub>PN(Surge)</sub> | Applied between P-N  | 450       | V    |

| Drain-Source Voltage                 | V <sub>DSS</sub>       | Vgs=0V, ID=250uA     | 500       | V    |

| Each FRFET Drain Current, Continuous | I <sub>D80</sub>       | T <sub>C</sub> =25°C | 1.5       | Α    |

| Each FRFET Drain Current, Continuous | I <sub>D25</sub>       | T <sub>C</sub> =80°C | 1.0       | Α    |

| Operating Junction Temperature       | TJ                     |                      | -40 ~ 150 | °C   |

Table. 5.1 Absolute maximum ratings.(FSB50450 Case)

Note) It is recommended that the average junction temperature should be limited to  $T_J \le 150^{\circ}$ C (@  $T_C \le 125^{\circ}$ C) in order to guarantee safe operation.

Figure 5.1 Switching and RBSOA(Single Pulse) Test Circuit (Low-side)

Figure 5.2 Normal current turn-off waveforms @ V<sub>PN</sub>=400V (FSB50450)

Figure 5.3 Normal current turn-on waveforms @ V<sub>PN</sub>=400V (FSB50450)

Figure 5.4 Short-circuit current turn-off waveforms @ V<sub>PN</sub>=350V (FSB50450)

## 6. Interface Circuit

## 6.1 Input/Output Signal Connection

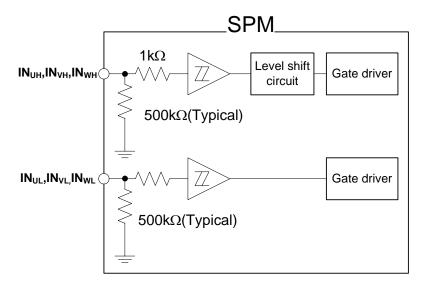

Figure  $6.1 \sim 6.2$  shows the I/O interface circuit between CPU and Tiny-DIP-SPM. Because Tiny-DIP-SPM input logic is high-active and there is built-in pull-down resistor, external pull-down resistor is not needed.

Figure 6.1 Recommended CPU I/O Interface Circuit(Package SPM23AA, SPM23BA)

Figure 6.2 Recommended CPU I/O Interface Circuit(Package SPM23AC)

| ltem                   | Symbol          | Condition                                     | Rating         | Unit |

|------------------------|-----------------|-----------------------------------------------|----------------|------|

| Control Supply Voltage | V <sub>CC</sub> | Applied between                               | 20             | V    |

| Control Supply Voltage |                 | V <sub>CC(U)</sub> – COM                      | 20             | V    |

|                        | V <sub>IN</sub> | Applied between                               |                |      |

| Input Signal Voltage   |                 | $IN_{(UH)}$ , $IN_{(VH)}$ , $IN_{(WH)}$ – COM | -0.3 ~ Vcc+0.3 | V    |

|                        |                 | $IN_{(UL)}$ , $IN_{(VL)}$ , $IN_{(WL)} - COM$ |                |      |

Table 6.1 Maximum ratings of input and F<sub>0</sub> pins

The input output maximum rating voltages are shown in Table 6.1. The RC coupling at each input (parts shown dotted in Figure 6.1~6.2) might change depending on the PWM control scheme used in the application and the wiring impedance of the application's PCB layout.

The Tiny-DIP-SPM family employs active-high input logic. This removes the sequence restriction between the control supply and the input signal during start-up or shutdown operation. Therefore it makes the system fail-safe. In addition, pull-down resistors are built in to each input circuit. Thus, external pull-down resistors are not needed reducing the required external component count. Furthermore, by lowering the turn on and turn off threshold voltage of input signal as shown in Table 6.2, a direct connection to 3.3V-class microprocessor or DSP is possible.

Figure 6.3 Internal structure of signal input terminals.

## Tiny-DIP-SPM User's Guide Version 1.0(2007.09.05)

Table 6.2 Input threshold voltage ratings (at Vcc = 15V, Tj = 25°C)

| Item                       | Symbol               | Condition                                                            | Min. | Тур. | Max. | Unit |

|----------------------------|----------------------|----------------------------------------------------------------------|------|------|------|------|

| Turn on threshold voltage  | V <sub>IN(ON)</sub>  | IN <sub>(UH)</sub> , IN <sub>(VH)</sub> , IN <sub>(VH)</sub> , – COM | 3.0  | -    | -    | V    |

| Turn off threshold voltage | V <sub>IN(OFF)</sub> | $IN_{(UL)}$ , $IN_{(VL)}$ , $IN_{(WL)}$ , $-COM$                     | -    | -    | 0.8  | V    |

As shown in Figure 6.3, the Tiny-DIP-SPM input signal section integrates a  $500k\Omega(typical)$  pull-down resistor. Therefore, when using an external filtering resistor between the CPU output and the Tiny-DIP-SPM input attention should be given to the signal voltage drop at the Tiny-DIP-SPM input terminals to satisfy the turn-on threshold voltage requirement. For instance,  $R_S = 100\Omega$  and  $C_S = 1$ nF are recommend to be applied for the parts shown dotted in figure 6.1 ~ 6.2.

#### 6.2 General Interface Circuit Example

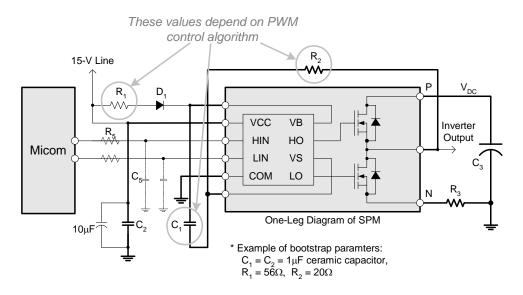

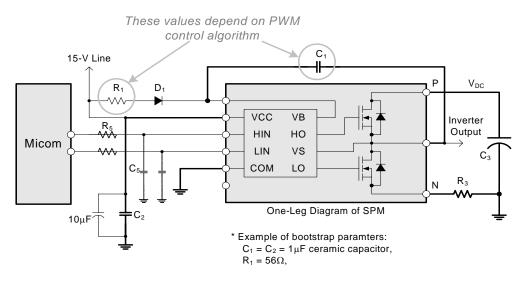

Figure  $6.4 \sim 6.5$  shows a typical application circuit of interface schematic, where control signals are transferred directly from a CPU.

Figure 6.4 Example of application circuit (Package SPM23AA, SPM23BA)

#### Note

- 1. To avoid malfunction, the wiring of each input should be as short as possible. (less than 2-3cm)

- 2. By virtue of integrating an application specific type HVIC inside the Tiny-DIP-SPM, direct coupling to CPU terminals without any opto-coupler or transformer isolation is possible.

- 3. C<sub>SP15</sub> capacitance value approximately 7 times larger than bootstrap capacitor C<sub>BS</sub> is recommended.

- 4. The input signals are Active-high configured. There is a internal 500kΩ pull-down resistor from each input signal line to GND. When employing RC coupling circuits between the CPU and Tiny-DIP-SPM select the RC values such that the input signals will be compatible with the Tiny-DIP-SPM turn-off/turn-on threshold voltages.

- 5 Each capacitor should be mounted as close to the pins of the SPM as possible.

- 6 To prevent surge destruction, the wiring between the smoothing capacitor and the P&N pins should be as short as possible. The use of a high frequency non-inductive capacitor of around 0.1~0.22 uF between the P&N pins is recommended.

- 7. Relays are used in almost all home appliances electrical equipment. These relays should be kept a sufficient distance from the CPU to prevent electromagnetic radiation from impacting the CPU.

- 8. Exessively large inductance due to long wiring patterns between the shunt resistor and Tiny-DIP-SPM will cause large surge voltage that might damage the Tiny-DIP-SPM's internal ICs. Therefore, the wiring between the shunt resistor and Tiny-DIP-SPM should be as short as possible. Additionally,  $C_{SPC15}$  (more than  $1\mu F$ ) should be mounted as close to the pins of the Tiny-DIP-SPM as possible.

- 9. Opto-coupler can be used for electric (galvanic) isolation. When opto-couplers are used, attention should be taken to the signal logic level and opto-coupler delay time.

- 10. RE(H) is recommended to be  $5.6\Omega$  as its minimum. And it should be less than  $20\Omega$ .

Figure 6.5 Example of application circuit(Package SPM23AC)

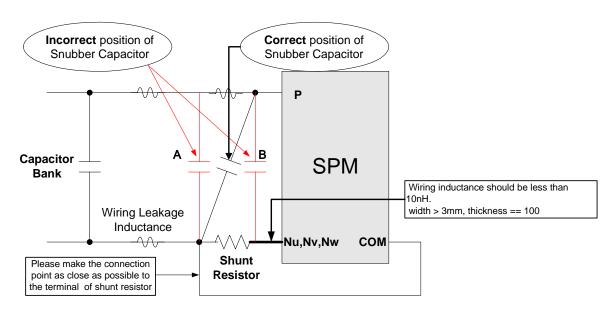

#### 6.3 Recommended Wiring of Shunt Resistor

External current sensing resistors are applied to detect phase current. A longer pattern between the shunt resistor and Tiny-DIP-SPM will cause so large surge that might damage built in IC and current detection components and might distort the sensing signals. To decrease the pattern inductance, the wiring between the shunt resistor and Tiny-DIP-SPM should be as short as possible.

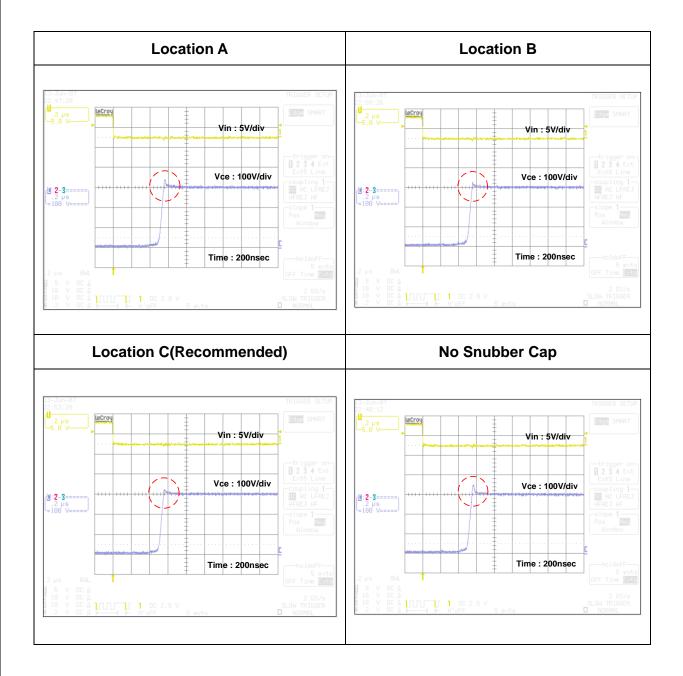

#### 6.4 Snubber Capacitor

As shown in the Figure 6.6, snubber capacitors should be installed in the right location so as to suppress surge voltages effectively. Generally a  $0.1{\sim}0.22\mu F$  snubber is recommended. If the snubber capacitor is installed in the wrong location 'A' as shown in the figure 5.4, the snubber capacitor cannot suppress the surge voltage effectively. If the capacitor is installed in the location 'B', the charging and discharging currents generated by wiring inductance and the snubber capacitor will appear on the shunt resistor. This will impact the current sensing signal (if shunt resistor used). The "B" position surge suppression effect is greater than the location 'A' or 'C'. The 'C' position is a reasonable compromise with better suppression than in location 'A' without impacting the current sensing signal accuracy. For this reason, the location 'C' is generally used.

Figure 6.6 Recommended wiring of Shunt resistor and Snubber Capacitor

Note: IGBT collector-emitter voltage waveform according to Snubber location

## 7. Function and Protection Circuit

## 7.1 SPM Functions versus Control Power Supply Voltage

Control and gate drive power for the Tiny-DIP-SPM is normally provided by a single 15Vdc supply that is connected to the module Vcc and COM terminals. For proper operation this voltage should be regulated to  $15V\pm10\%$  and its current supply should be larger than 160uA for SPM only. Table 7.1 describes the behavior of the SPM for various control supply voltages. The control supply should be well filtered with a low impedance electrolytic capacitor and a high frequency decoupling capacitor connected right at the Tiny-DIP-SPM's pins.

High frequency noise on the supply might cause the internal control IC to malfunction and generate erroneous fault signals. To avoid these problems, the maximum ripple on the supply should be less than  $\pm$  1V/ $\mu$ s. In addition, it may be necessary to connect a 24V/1W zener diode across the control supply to prevent surge destruction under severe conditions.

It is very important that all control circuits and power supplies be referred to module's COM terminal and not to the N power terminal. In general, it is best practice to make the common reference (COM) a ground plane in the PCB layout.

The main control power supply is also connected to the bootstrap circuits that are used to establish the floating supplies for the high side gate drives.

When control supply voltage ( $V_{CC}$  and  $V_{BS}$ ) falls down under UVLO(Under Voltage Lock Out) level, FRFETs will turn OFF while ignoring the input signal.

Table 7.1 Tiny-DIP-SPM: Control Voltage Range versus Function Operations

| Control Voltage Range [V]       | Tiny-DIP-SPM Function Operations                                                             |

|---------------------------------|----------------------------------------------------------------------------------------------|

| 0 ~ 4                           | Control IC does not operate. Under voltage lockout and fault output do not operate.          |

| 0 ~ 4                           | dV/dt noise on the main P-N supply might trigger the FRFETs.                                 |

| 4 ~ 12.5                        | Control IC starts to operate. As the under voltage lockout is set, control input signals are |

| 4 ~ 12.5                        | blocked.                                                                                     |

|                                 | Under voltage lockout is reset. FRFETs will be operated in accordance with the control       |

| 12.5 ~ 13.5                     | gate input. Driving voltage is below the recommended range so Rds(on) and the                |

|                                 | switching loss will be larger than that under normal condition.                              |

| 13.5 ~ 16.5 for V <sub>CC</sub> | Normal operation. This is the recommended operating condition.                               |

| 13.5 ~ 16.5 for V <sub>BS</sub> | Normal operation. This is the recommended operating condition.                               |

| 40.5 00.6                       | FRFETs are still operated. Because driving voltage is above the recommended range,           |

| 16.5 ~ 20 for V <sub>CC</sub>   | FRFETs' switching is faster. It causes increasing system noise. And peak short circuit       |

| 16.5 ~ 20 for V <sub>BS</sub>   | current might be too large for proper operation of the short circuit protection.             |

| Over 20                         | Control circuit in the Tiny-DIP-SPM might be damaged.                                        |

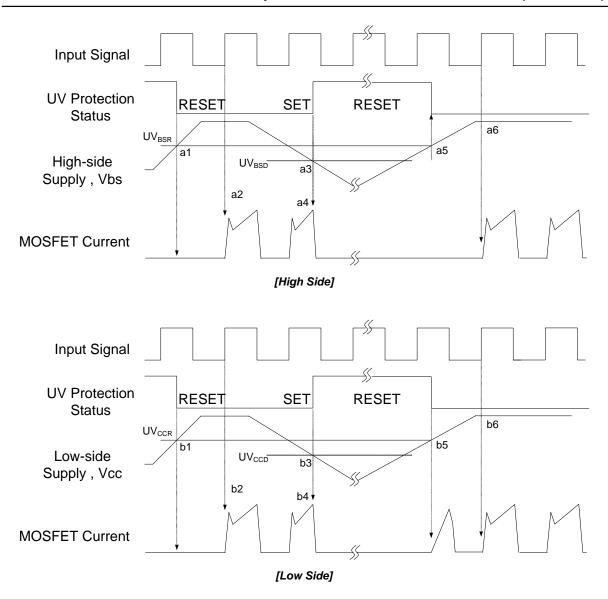

## 7.2 Under-Voltage Protection

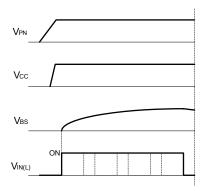

The half bridge HVIC has an under voltage lockout function to protect low side FRFETs from operation with insufficient gate driving voltage. A timing chart for this protection is shown in Figure 7.1

a1 : Control supply voltage rises :

After the voltage rises UV<sub>CCR</sub>, the circuits start to operate when next input is applied.

- a2: Normal operation: FRFET ON and carrying current.

- a3 : Under voltage detection ( U<sub>VCCD</sub>)

- a4: FRFET OFF in spite of control input condition, but there is no fault output signal.

- a5 : Under voltage reset ( UV<sub>CCR</sub>)

- a6: Normal operation: FRFET ON and carrying current

- b1 : Control supply voltage rises:

After the voltage reaches UV<sub>BSR</sub>, the circuits start to operate immediately.

- b2: Normal operation: FRFET ON and carrying current.

- b3: Under voltage detection (UV<sub>BSD</sub>).

- b4: FRFET OFF in spite of control input condition, but there is no fault output signal.

- b5 : Under voltage reset (UV<sub>BSR</sub>)

- b6 : Normal operation: FRFET ON and carrying current

Figure 7.1 Timing chart of under-voltage protection function [High-side, Low-side]

## 8. Bootstrap Circuit

## 8.1 Operation of a Bootstrap Circuit

The  $V_{BS}$  voltage, which is the voltage difference between  $V_{B(U,V,W)}$  and  $V_{S(U,V,W)}$ , provides the supply to the HVICs within the Tiny-DIP-SPM. This supply must be in the range of 13.5~16.5V to ensure that the HVIC can fully drive the high-side FRFET. The Tiny-DIP-SPM includes an under-voltage detection function for the  $V_{BS}$  to ensure that the HVIC does not drive the high-side FRFET, if the  $V_{BS}$  voltage drops below a specified voltage (refer to the datasheet). This function prevents the FRFET from operating in a high dissipation mode.

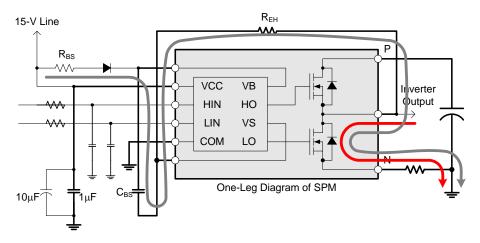

There are a number of ways in which the  $V_{BS}$  floating supply can be generated. One of them is the bootstrap method described here. This method has the advantage of being simple and inexpensive. However, the duty cycle and on-time are limited by the requirement to refresh the charge in the bootstrap capacitor. The bootstrap supply is formed by a combination of an external diode, resistor and capacitor as shown in Figure 8.1. The current flow path of the bootstrap circuit is shown in Figure 8.1. When  $V_S$  is pulled down to ground (either through the low-side or the load), the bootstrap capacitor ( $C_{BS}$ ) is charged through the bootstrap diode ( $D_{BS}$ ) and the resistor ( $R_S$ ) from the  $V_{CC}$  supply.

## 8.2 Initial Charging of a Bootstrap Capacitor

An adequate on-time duration of the low-side FRFET to fully charge the bootstrap capacitor is required for initial bootstrap charging. The initial charging time ( $t_{charge}$ ) can be calculated from the following equation:

$$t_{charge} \ge C_{BS} \times R_S \times \frac{1}{\delta} \times \ln(\frac{V_{CC}}{V_{CC} - V_{BS(min)} - V_f - V_{LS}})$$

(8.1)

$\label{eq:VBS} Vf = \text{Forward voltage drop across the bootstrap diode} \\ V_{BS(min)} = \text{The minimum value of the bootstrap capacitor} \\ V_{LS} = \text{Voltage drop across the low-side FRFET or load} \\ \delta = \text{Duty ratio of PWM}$

(a) Bootstrap circuit operation at turn-on of low-side FRFET

(b) Bootstrap circuit operation at turn-on of low-side freewheeling diode

(c) Timing chart of initial bootstrap charging

Figure 8.1 Bootstrap circuit operation and initial charging(Package SPM23AA, SPM23BA)

#### 8.3 Selection of a Bootstrap Capacitor

The bootstrap capacitance can be calculated by:

$$C_{BS} = \frac{I_{leak} \times \Delta t}{\Delta V} \tag{8.2}$$

Where  $\Delta t = \text{maximum ON pulse width of high-side FRFET}$

$\Delta V$  = the allowable discharge voltage of the  $C_{BS}$ .

$I_{leak}$ = maximum discharge current of the  $C_{BS}$  mainly via the following mechanisms :

Gate charge for turning the high-side FRFET on

Quiescent current to the high-side circuit in the IC

Level-shift charge required by level-shifters in the IC

Leakage current in the bootstrap diode

C<sub>BS</sub> capacitor leakage current (ignored for non-electrolytic capacitors)

Bootstrap diode reverse recovery charge

Practically, 1mA of  $I_{leak}$  is recommended for Mini DIP SPM. By taking consideration of dispersion and reliability, the capacitance is generally selected to be 2~3 times of the calculated one. The  $C_{BS}$  is only charged when the high-side FRFET is off and the  $V_S$  voltage is pulled down to ground. Therefore, the on-time of the low-side FRFET must be sufficient to ensure that the charge drawn from the  $C_{BS}$  capacitor can be fully replenished. Hence, inherently there is a minimum on-time of the low-side FRFET (or off-time of the high-side FRFET).

The bootstrap capacitor should always be placed as close to the pins of the SPM as possible. At least one low ESR capacitor should be used to provide good local de-coupling. For example, a separate ceramic capacitor close to the SPM is essential, if an electrolytic capacitor is used for the bootstrap capacitor. If the bootstrap capacitor is either a ceramic or tantalum type, it should be adequate for local decoupling.

#### 8.4 Selection of a Bootstrap Diode

The bootstrap diode ( $D_{BS}$ ) must block the inverter DC-link voltage, which is seen when the high-side device is switched on. It is important that this diode be an ultra-fast recovery device to minimize the amount of charge that is fed back from the bootstrap capacitor into the  $V_{CC}$  supply. Similarly, the high temperature reverse leakage current would be important if the capacitor has to store a charge for long periods of time.

#### 8.5 Selection of Series Resistance

A resistor ( $R_S$ ) must be added in series with the bootstrap diode to slow down the  $dV_{BS}/dt$ . The value of the series resistor relative to the value of the bootstrap capacitor should be chosen such that the RC time

September. 2007

constant is equal to or greater than 10usec. Note that if the rising  $dV_{BS}/dt$  is slowed down significantly, it could temporarily result in a few missing pulses during the start-up phase due to insufficient  $V_{BS}$  voltage.

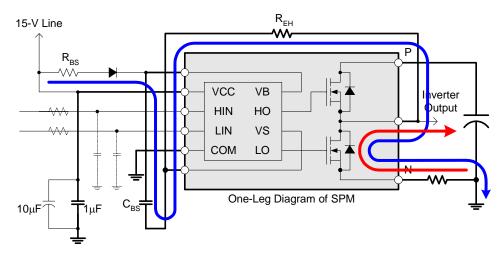

# 8.6 Charging and Discharging of the Bootstrap Capacitor during PWM-Inverter Operation

The bootstrap capacitor ( $C_{BS}$ ) charges through the bootstrap diode ( $D_{BS}$ ) and resistor ( $R_S$ ) from the  $V_{CC}$  supply when the high-side FRFET is off, and the  $V_S$  voltage is pulled down to ground. It discharges when the high-side FRFET is on.

#### **Example 1: Selection of the Initial Charging Time**

An example of the calculation of the minimum value of the initial charging time is given with reference to equation (8.1).

Condition:

$$\begin{split} \text{C}_{\text{BS}} &= 22 \text{uF}, & \text{R}_{\text{S}} &= 20 \Omega, & \text{Duty Ratio of PWM}(\delta) = 0.5 & \text{D}_{\text{BS}} &= 1\text{N}4937 (600\text{V}/1\text{A}) \\ \text{V}_{\text{CC}} &= 16.5\text{V} & \text{V}_{\text{F}} &= 1\text{V}, & \text{V}_{\text{BS (min)}} &= 12.5\text{V}, & \text{V}_{\text{LS}} &= 1\text{V} \\ & & t_{charge} \geq 22 uF \times 20 \Omega \times \frac{1}{0.5} \times \ln(\frac{16.5V}{16.5V - 12.5V - 1V - 1V}) = 1.86 ms \end{split}$$

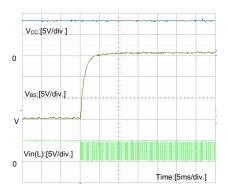

Figure 8.2 shows the result of the experiment obtained in washing machine applications. In order to ensure safety, it is recommended that the charging time must be at least three times longer than the calculated value arrived at by using equation (8.1).

Figure 8.2 Practical initial charging waveforms.

#### **Example 2: The Minimum Value of the Bootstrap Capacitor**

An example of the calculation of the minimum value of the bootstrap capacitor is given with reference to equation (8.2).

Conditions:

∆V=0.1V

$\Delta t$ =66.6us

$I_{leak}$ =1mA

$$C_{BS} \ge \frac{1mA \times 66.6us}{0.1V} = 0.667 \,\mu\text{F}$$

The calculated bootstrap capacitance is  $0.667\mu F$ . By taking consideration of dispersion and reliability, the capacitance is generally selected to be 2-3 times of the calculated one. Therefore,  $1.33\sim 2u F$  of Cbs becomes a proper value. However, this capacitance can be changed according to the switching frequency, sort of the used capacitor(MLCC is recommended) and recommended Vbs voltage of  $13.5\sim 16.5 V$ .

Note that this result is only an example. It is recommended that you design a system by taking consideration of the actual control pattern and lifetime of components.

## 8.7 Recommended Boot Strap Operation Circuit and Parameters

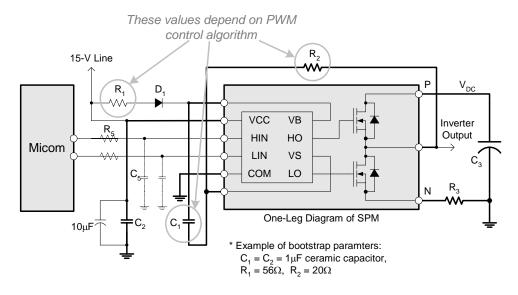

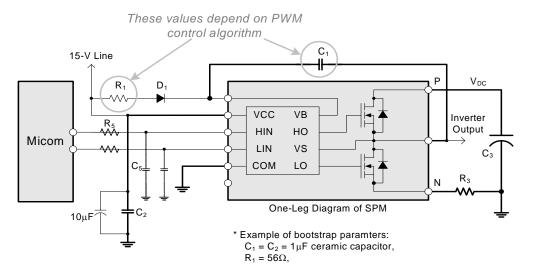

Figure 8.3 ~ 8.4 is the recommended bootstrap operation circuit and parameters.

Note: It would be recommended that the bootstrap diode, D<sub>BS</sub>, has soft and fast recovery characteristics.

Figure 8.3 Recommended Boot Strap Operation Circuit and Parameters for Tiny- DIP-SPM (Package SPM23AA, SPM23BA)

September. 2007

Module

Figure 8.4 Recommended Boot Strap Operation Circuit and Parameters for Tiny- Double-DIP-SPM (Package SPM23AC)

## 9. Power Loss and Dissipation

#### 9.1 Power Loss of SPM

The total power losses in the Tiny DIP SPM are composed of conduction and switching losses in the FRFET and bodydiode. The loss during the turn-off steady state can be ignored because it is very small amount and has little effect on increasing the temperature in the device. The conduction loss depends on the dc electrical characteristics of the device i.e. saturation voltage. Therefore, it is a function of the conduction current and the device's junction temperature. On the other hand the switching loss is determined by the dynamic characteristics like turn-on/off time and over-voltage/current. Hence, in order to obtain the accurate switching loss, we should consider the DC-link voltage of the system, the applied switching frequency and the power circuit layout in addition to the current and temperature.

In this chapter, based on a PWM-inverter system for motor control applications, detailed equations are shown to calculate both losses of the Tiny DIP SPM. They are for the case that 3-phase continuous sinusoidal PWM is adopted. For other cases like 3-phase discontinuous PWMs, please refer to the paper "Minimum-Loss Strategy for three-Phase PWM Rectifier, IEEE Transactions on Industrial Electronics, Vol. 46, No. 3, June, 1999 by Dae-Woong Chung and Seung-Ki Sul".

#### 9.2 Calculation Method for Conduction Loss

The typical forward characteristics are approximated by the following linear equation for the FRFET and the bodydiode, respectively.

$$v_1 = V_1 + R_1 x i$$

$v_D = V_D + R_D x i$  (9.1)

$V_I$  = Threshold voltage of FRFET  $V_D$  = Threshold voltage of bodydiode

$R_I$  = on-state slope resistance of FRFET  $R_D$  = on-state slope resistance of bodydiode

where,  $v_I$  and  $v_D$  are the saturation voltage of FRFET and the saturation voltage of bodydiode, respectively.

Assuming that the switching frequency is high, the output current of the PWM-inverter can be assumed to be sinusoidal. That is,

$$i = I_{\text{peak}} \cos(\theta - \phi) \tag{9.2}$$

Where  $\phi$  is the phase-angle difference between output voltage and current. Using equation (9.1), the conduction loss of one FRFET and bodydiode can be obtained as follows.

$$P_{con.I} = \frac{V_I I_{peak}}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{\frac{\pi}{2} + \phi} \xi \cos(\theta - \phi) d\theta + \frac{R_I I_{peak}}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{2} \xi \cos^2(\theta - \phi) d\theta$$

(9.3)

$$P_{con.D} = \frac{V_D I_{peak}}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{\frac{\pi}{2} + \phi} (1 - \xi) \cos(\theta - \phi) d\theta + \frac{R_D I_{peak}}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{\frac{\pi}{2} + \phi} (1 - \xi) \cos^2(\theta - \phi) d\theta$$

(9.4)

where  $\xi$  is the duty cycle in the given PWM method.

$$\xi = \frac{1 + MI \cos \theta}{2} \tag{9.5}$$

where MI is the modulation index in the PWM method that represents the normalized voltage and is between zero and one. Notice that at full modulation the duty cycle varies from zero to 100%. Under constant frequency conditions the duty cycle can be simplified in terms of the phase angle  $\theta$ .

Finally, the integration of equation (9.3) and (9.4) gives

$$P_{con} = P_{con.I} + P_{con.D}$$

$$= \frac{I_{peak}}{2\pi} (V_I + V_D) + \frac{I_{peak}}{8} (V_I - V_D) MI \cos \phi + \frac{I_{peak}^2}{8} (R_I + R_D) + \frac{I_{peak}^2}{3\pi} (R_I - R_D) MI \cos \phi$$

(9.6)

It should be noted that the total inverter conduction losses are six times the  $P_{con}$  of the FRFET and bodydiode conduction losses.

## 9.3 Calculation Method for Switching Loss

Different devices have different switching characteristics and they also vary according to the handled voltage/current and the operating temperature/frequency. However, the turn-on/off loss energy (Joule) can be experimentally measured indirectly by multiplying the current and voltage and integrating over time, under a given circumstance. Therefore the linear dependency of a switching energy loss on the switched-current is expressed during one switching period as follows.

Switching energy

$$loss = (E_I + E_D) \times |i| [joule]$$

(9.7)

$$E_{L} = E_{LON} + E_{LOFF} \tag{9.8}$$

$$E_D = E_{D,ON} + E_{D,OFF} \tag{9.9}$$

where,  $E_l|i|$  is the switching loss energy of the FRFET and  $E_D|i|$  is for the bodydiode.  $E_l$  and  $E_D$  can be considered a constant.

As mentioned in the above equation (9.2), the output current can be considered a sinusoidal waveform and the switching loss occurs every PWM period in the continuous PWM schemes. Therefore, depending on the switching frequency of  $f_{SW}$ , the switching loss of one device is the following equation (9.10).

$$P_{sw} = \frac{1}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{\frac{\pi}{2} + \phi} (E_I + E_D) \ i \ f_{sw} d\phi$$

$$= \frac{(E_I + E_D) f_{sw} I_{peak}}{2\pi} \int_{-\frac{\pi}{2} + \phi}^{\frac{\pi}{2} + \phi} \cos(\theta - \phi) d\phi = \frac{(E_I + E_D) f_{sw} I_{peak}}{\pi}$$

(9.10)

where  $E_l$  is an unique constant of FRFET related to the switching energy and different FRFET has different  $E_l$  value.  $E_D$  is one for bodydiode. Those should be derived by experimental measurement. From equation (9.10), it should be noted that the switching losses are a linear function of current and directly proportional to the switching frequency.

## 9.4 Power Dissipation Design

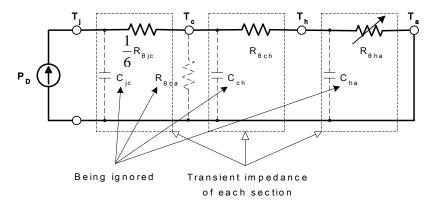

Figure 9.1 shows the thermal equivalent circuit of an SPM mounted on a heat sink. For sustained power dissipation  $P_D$  at the junction, the junction temperature  $T_j$  can be calculated as;

$$T_{i} - T_{a} = P_{D} \left( R_{\theta | c} / 6 + R_{\theta ch} + R_{\theta ha} \right) \tag{9.11}$$

where  $T_a$  is the ambient temperature and  $R_{\theta jc}$ ,  $R_{\theta ch}$ , and  $R_{\theta ha}$  represent the thermal resistance from the junction to the case, case to heat sink, and the heat sink to ambient for each FRFET and bodydiode within the SPM, respectively. The dotted component of  $R_{\theta ca}$  is ignored for the sake of convenience.

From equation (9.11) it is evident that for a limited  $T_{jmax}$  (usually 150°C).  $P_D$  can be increased by reducing  $R_{\theta ha}$ . This means that a more efficient cooling system will increase the power dissipation capability of an SPM. An infinite heat sink will result if  $R_{\theta ch}$  and  $R_{\theta ha}$  are reduced to zero and the case temperature  $T_c$  is locked at the fixed ambient temperature  $T_a$ .

In practical operation, the power loss  $P_D$  is cyclic and therfore the transient RC equivalent circuit shown in Figure 9.1 should be considered. For pulsed power loss, the thermal capacitance effect delays the rise in junction temperature, and thus permits a heavier loading of the SPM. However, in this note, all the thermal capacitances in the dotted boxes in Figure 9.1 are also ignored because we intend to design the SPM with continuous max. power dissipation.

Figure 9.1 Transient thermal equivalent circuit of an SPM with a heat

## 9.5 Power Cycle

A final thermal design consideration is the temperature range of delta  $T_j$ , which works in the actual application. The concern here is what is called the thermal fatigue. As the components of the module heat and cool due to collector power dissipation, there are some mechanical stresses caused by the different expansion coefficients of the various component materials. This differential expansion puts the intermediate layers under bending and shear stress. With the accumulation of these stress cycles the assembly structure can deteriorate causing eventual failure. Studies of this phenomenon involve tests at multiple operating points to create curves that indicate cycling life as a function of the delta  $T_j$  excursion.

These curves are specific to particular temperature, time, and operating ranges, so that a general curve cannot be generated. The curve is representative of the test results for the SPM. All available

# Tiny-DIP-SPM User's Guide Version 1.0(2007.09.05)

information has indicated that thermal fatigue is not an issue when delta T<sub>i</sub> is kept below 30°C.

Repetitive operation of short circuit protection will result a repeated large junction temperature change of the FRFET, and therefore shorten the device life cycle expectancy. The short circuit protection function designed to protect the SPM from non-repetitive short circuit condition. Therefore, it is best practice ti stop operation of the device when there is a fault. For applications involving a large number of power cycles in conjunction with junction temperature excursions greater than 30°C, the application should be reviewed in detail with FAIRCHILD SEMICONDUCTOR application engineers.

September. 2007

Module

# 10. Packaging and Installation Guide

# 10.1 Heatsink Mounting

#### Recommended cooling method of TINY-DIP-SPM

Because TINY-DIP-SPM is the most compact device of all the competitors until around 100W applications and it doesn't have the screw hole, cooling and heat-sink installation are important issues users have to be careful. Temperature rise of power semiconductors is due to the non-ideal effects of switching devices (IGBT, MOSFET and diode, etc). When the switching devices are turned on, we have a forward voltage drop which leads to Power Loss=(Conduction current)\*(Voltage drop) and we have switching losses due to the finite rise and fall time of current and voltage during switching period. These total power losses in the devices make the case temperature rise with the thermal resistance of each package according to the below formula.

#### $T_J$ - $T_c$ = Power loss / Thermal resistance

Therefore, in order to decrease the case temperature and increase the SOA area, we have to minimize the total thermal resistance and power losses. Heat-sink, which is one of the most popular cooling methods of power devices, contributes to decrease the thermal resistance. That is, heat-sink can improve the thermal performance by spreading and cooling the heat. Everything with comparably high thermal conductivity can be heat-sink. For example, even PCB pattern can be heat-sink if it has enough cooling areas. Especially, TINY-DIP-SPM with no stand-off and SMD can benefit from cooling area of the bottom-side of the module on PCB as the distance from the bottom of power modules and PCB is zero. Similarly, thicker pattern of power pins is also useful. Fig.10.1 shows typical test board for TINY-DIP-SPM without cooling area and fig.10.2 shows test board with cooling area at bottom side of the module and thicker power pins. Especially, bare copper area is more preferable in view of cooling.

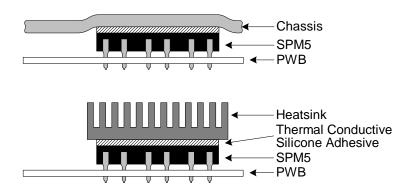

Because TINY-DIP-SPM doesn't have the screw hole, we recommend special heat-sink installation method like fig.10.3. Using the chassis for heat-sink like (a) in fig.10.3 seems to be effective at built-in applications. But in some cases, users can have difficulty in installing the heat-sink on DIP(Dual-in-line) package rather than SIP (Single-in-line) package. In this case, (c) in fig.10.3 can be the probable solution. We can solve the problem by mechanically extending the tail of the heat-sink and fixing the tail on the chassis.

Figure 10.1 Test board of Tiny-DIP-SPM without any cooling area

September. 2007

Module

Figure 10.2 Test board of TINY-DIP-SPM with cooling area of bottom

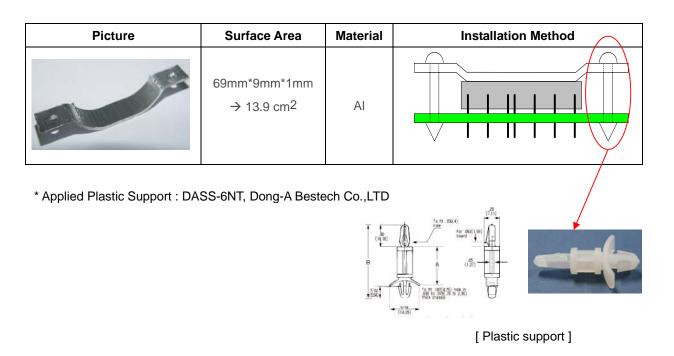

Figure 10.3 Heat-sink installation method of TINY-DIP-SPM

Figure 10.4 Plastic support Installation method using (e) in fig.10.3

Figure 10.5 The used heatsink size for plastic support installation method

# Silicon Grease

Apply silicon grease between the SPM and the heat sink to reduce the contact thermal resistance. Be sure to apply the coating thinly and evenly, do not use too much. A uniform layer of silicon grease (100  $\sim$  200 $\mu$ m thickness) should be applied in this situation.

# 10.2 Handling Precaution

When using semiconductors, the incidence of thermal and/or mechanical stress to the devices due to improper handling may result in significant deterioration of their electrical characteristics and/or reliability.

## **Transportation**

Handle the device and packaging material with care. To avoid damage to the device, do not toss or drop. During transport, ensure that the device is not subjected to mechanical vibration or shock. Avoid getting devices wet. Moisture can also adversely affect the packaging (by nullifying the effect of the antistatic agent). Place the devices in special conductive trays. When handling devices, hold the package and avoid touching the leads, especially the gate terminal. Put package boxes in the correct direction. Putting them upside down, leaning them or giving them uneven stress might cause the electrode terminals to be deformed or the resin case to be damaged. Throwing or dropping the packaging boxes might cause the devices to be damaged. Wetting the packaging boxes might cause the breakdown of devices when operating. Pay attention not to wet them when transporting on a rainy or a snowy day.

#### Storage

- 1) Avoid locations where devices will be exposed to moisture or direct sunlight. (Be especially careful during periods of rain or snow.)

- 2) Do not place the device cartons upside down. Stack the cartons atop one another in an upright position only. : Do not place cartons on their sides.

- 3) The storage area temperature should be maintained within a range of 5°C to 35°C, with humidity kept within the range from 40% to 75%.

- 4) Do not store devices in the presence of harmful (especially corrosive) gases, or in dusty conditions.

- 5) Use storage areas where there is minimal temperature fluctuation. Rapid temperature changes can cause moisture condensation on stored devices, resulting in lead oxidation or corrosion. As a result, lead solderability will be degraded.

- 6) When repacking devices, use antistatic containers. Unused devices should be stored no longer than one month.

- 7) Do not allow external forces or loads to be applied to the devices while they are in storage.

#### **Environment**

- 1) When humidity in the working environment decreases, the human body and other insulators can easily become charged with electrostatic electricity due to friction. Maintain the recommended humidity of 40% to 60% in the work environment. Be aware of the risk of moisture absorption by the products after unpacking from moisture-proof packaging.

- 2) Be sure that all equipment, jigs and tools in the working area are grounded to earth.

- 3) Place a conductive mat over the floor of the work area, or take other appropriate measures, so

September. 2007

that the floor surface is grounded to earth and is protected against electrostatic electricity.

- 4) Cover the workbench surface with a conductive mat, grounded to earth, to disperse electrostatic electricity on the surface through resistive components. Workbench surfaces must not be constructed of low-resistance metallic material that allows rapid static discharge when a charged device touches it directly.

- 5) Ensure that work chairs are protected with an antistatic textile cover and are grounded to the floor surface with a grounding chain.

- 6) Install antistatic mats on storage shelf surfaces.

- 7) For transport and temporary storage of devices, use containers that are made of antistatic materials of materials that dissipate static electricity.

- 8) Make sure cart surfaces that come into contact with device packaging are made of materials that will conduct static electricity, and are grounded to the floor surface with a grounding chain.

- 9) Operators must wear antistatic clothing and conductive shoes (or a leg or heel strap).

- 10) Operators must wear a wrist strap grounded to earth through a resistor of about  $1M\Omega$ .

- 11) If the tweezers you use are likely to touch the device terminals, use an antistatic type and avoid metallic tweezers. If a charged device touches such a low-resistance tool, a rapid discharge can occur. When using vacuum tweezers, attach a conductive chucking pad at the tip and connect it to a dedicated ground used expressly for antistatic purposes.

- 12) When storing device-mounted circuit boards, use a board container or bag that is protected against static charge. Keep them separated from each other, and do not stack them directly on top of one another, to prevent static charge/discharge which occurs due to friction.

- 13) Ensure that articles (such as clip boards) that are brought into static electricity control areas are constructed of antistatic materials as far as possible.

- 14) In cases where the human body comes into direct contact with a device, be sure to wear finger cots or gloves protected against static electricity.

## Electrical Shock

A device undergoing electrical measurement poses the danger of electrical shock. Do not touch the device unless you are sure that the power to the measuring instrument is off.

## Circuit Board Coating

When using devices in equipment requiring high reliability or in extreme environments (where moisture, corrosive gas or dust is present), circuit boards can be coated for protection. However, before doing so, you must carefully examine the possible effects of stress and contamination that may result. There are many and varied types of coating resins whose selection is, in most cases, based on experience. However, because device-mounted circuit boards are used in various ways, factors such as board size, board thickness, and the effects that components have on one another, makes it practically impossible to

September. 2007

predict the thermal and mechanical stresses that semiconductor devices will be subjected to.

# 10.3 Marking Specifications

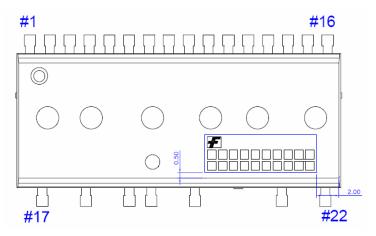

Figure 10.6 show the Tiny-DIP-SPM three package type, that is, SPM23AA, SPM23BA, SPM23AC

Fig. 10.6 Tiny-DIP-SPM of package type

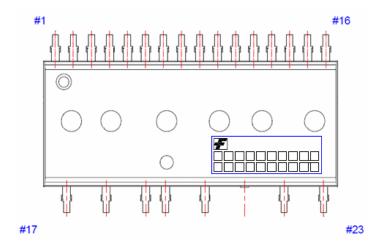

Fig. 10.7 Marking layout of Package SPM23-AA type (bottom side)

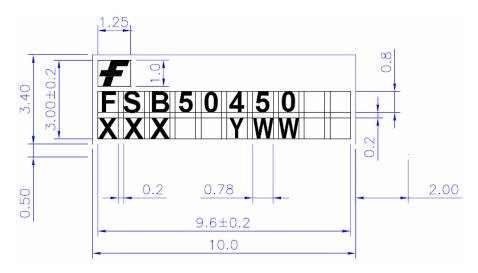

Fig. 10.8 Marking dimension of Package SPM23-AA type

1. F: FAIRCHILD LOGO

2. XXX: Last 3 digits of Lot No.

3. YWW: WORK WEEK CODE ("Y" refers to the below alphabet character table)

4. Hole Side Marking

- CP: FSB50450 (Product Name)

- XXX : Last 3 digits of Lot No.

- YWW : WORK WEEK CODE ("Y" refers to the below alphabet character table)

# Table 10.1 Work Week Code

| Y        | 2000 | 2001 | 2002 | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 |

|----------|------|------|------|------|------|------|------|------|------|------|------|

| Alphabet | Α    | В    | С    | D    | Е    | F    | G    | Н    | J    | K    | Α    |

September. 2007

Module

FAIRCHILD SEMICONDUCTOR - Smart Power

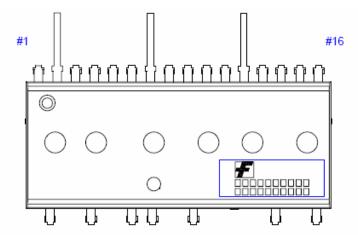

Fig. 10.9 Marking layout of Package SPM23-BA type(bottom side)

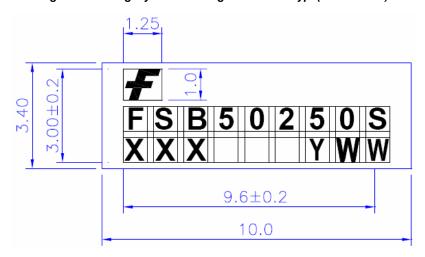

Fig. 10.10 Marking dimension of Package SPM23-BA type

1. F: FAIRCHILD LOGO

2. XXX: Last 3 digits of Lot No.

3. YWW: WORK WEEK CODE ("Y" refers to the below alphabet character table)

4. Hole Side Marking

- CP: FSB50250S (Product Name)

- XXX : Last 3 digits of Lot No.

- YWW : WORK WEEK CODE ("Y" refers to the below alphabet character table)

# Table 10.2 Work Week Code

| Y        | 2000 | 2001 | 2002 | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 |

|----------|------|------|------|------|------|------|------|------|------|------|------|

| Alphabet | Α    | В    | С    | D    | Е    | F    | G    | Н    | J    | K    | Α    |

September. 2007

Module

FAIRCHILD SEMICONDUCTOR - Smart Power

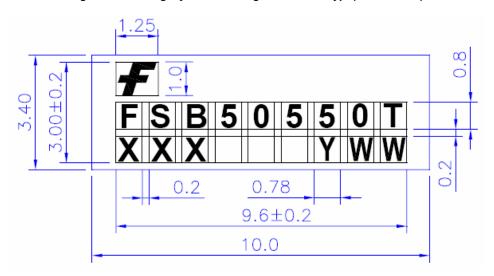

Fig. 10.11 Marking layout of Package SPM23-AC type(bottom side)

Fig. 10.12 Marking dimension of Package SPM23-AC type.

1. F: FAIRCHILD LOGO

2. XXX: Last 3 digits of Lot No.

3. YWW: WORK WEEK CODE ("Y" refers to the below alphabet character table)

4. Hole Side Marking

- CP : FSB50550T (Product Name)

- XXX : Last 3 digits of Lot No.

- YWW : WORK WEEK CODE ("Y" refers to the below alphabet character table)

# Table 10.3 Work Week Code

| Y        | 2000 | 2001 | 2002 | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 |

|----------|------|------|------|------|------|------|------|------|------|------|------|

| Alphabet | Α    | В    | С    | D    | Е    | F    | G    | Н    | J    | K    | Α    |

September. 2007

Module

FAIRCHILD SEMICONDUCTOR - Smart Power

# 10.4 Packaging Specifications

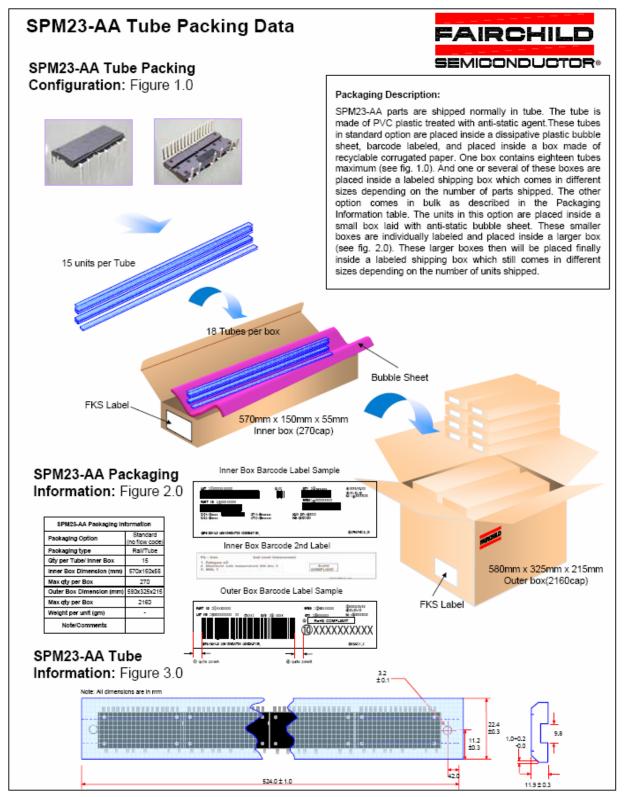

Fig. 10.13 Description of packaging process for SPM23-AA.

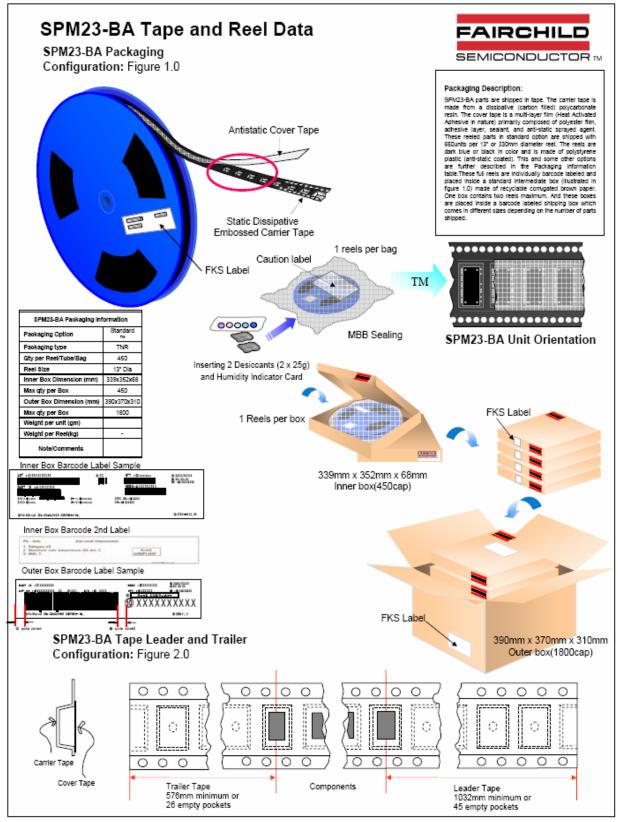

Fig. 10.14 Description of packaging process for SPM23-BA.

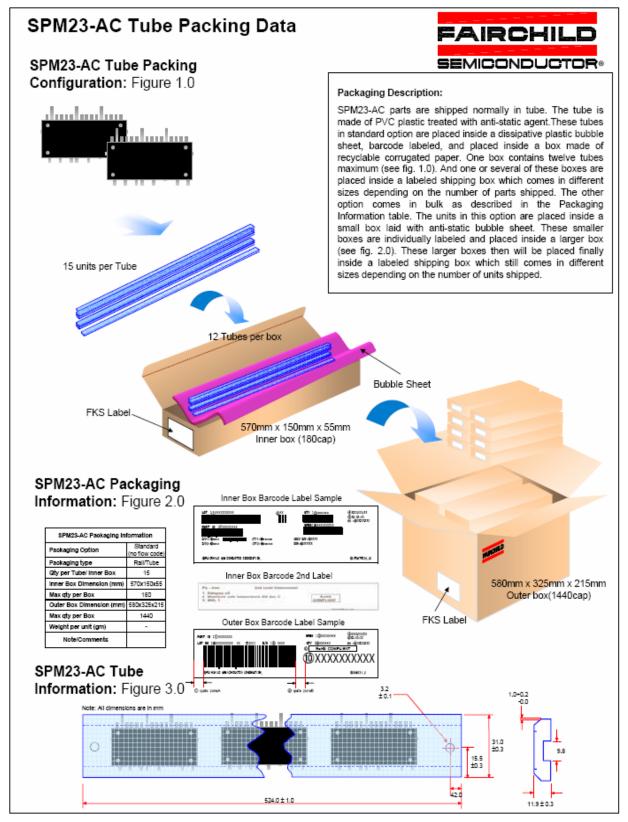

Fig. 10.15 Description of packaging process for SPM23-AC.

# **Notice for Safe Designs**

We are making every effort to improve the quality and reliability of our products. However, there are possibilities that semiconductor products be damaged or malfunctioned. Pay much attention to take safety into consideration and to adopt redundant, fireproof and malfunction-proof designs, so that the breakdown or malfunction of these products would not cause accidents including human life, fire, and social damages.

# **Notes When Using this Specification**

This specification is intended as reference materials when customers use Fairchild semiconductor products. Thus, we disclaim any warranty for exercise or our intellectual property rights and other proprietary rights regarding the product information described in this specification.

We assume absolutely no liability in the event of any damage and any infringement of third party's rights arising from the use of product data, diagrams, tables, and application circuit examples described in this specification.

All data including product data, diagrams, and tables described in this specification are correct as of the day it was issued, and they are subject to change without notice. Always verify the latest information of these products with Fairchild semiconductor and its agents before purchase.

The products listed in this specification are not designed to be used with devices or systems, with would directly endanger human life. Should you intend to use these products for special purposes such as transportation equipment, medical instruments, aerospace machinery, nuclear-reactor controllers, fuel controllers, or submarine repeaters, please contact Fairchild semiconductor and its agents.

Regarding transmission or reproduction of this specification, prior written approval of Fairchild semiconductor is required.

Please contact Fairchild semiconductor and its agents if you have any questions about this specification.

September. 2007

Module