# **Application Note AN-9045**

WLCSP Assembly Guidelines

By Dennis Lang

### INTRODUCTION

Wafer level chip scale packaging (WLCSP) is actually an old packaging technology, likely the oldest finding significant growth today. The technology is valued today for the same reasons it was originally designed; a comparatively small Printed Wiring Board (PWB) footprint with great package parasitic performance and relative ease of assembly. WLCSP assembly performance may require different non-destructive test tools for inspection in production; an optimized board mount process will give the largest process window in volume production ultimately yielding best performance.

### PURPOSE

This application note is intended to provide a recommended starting point for manufacturing process optimization using Fairchild Semiconductor WLCSP components. The suggestions published here have been proven to work under the given conditions, but variances in manufacturing equipment, processes and circuit board design for a specific application may lead to a combination where other process parameters yield superior performance.

### **BOARD MOUNTING**

The solder joint and pad design are the most important factors in creating a reliable assembly. The pad must be designed to the proper dimensions to allow for tolerances in PWB fabrication and pick and place, and also to allow for proper solder fillet formation where applicable.

## **PAD FINISH**

The most frequently encountered pad finish for consumer electronics with tin lead solders was hot air solder leveled, HASL. With lead free, other finishes are preferred. Immersion silver, immersion nickel gold and organic surface protectant, OSP are the board finishes of choice. Each finish has useful properties, and each has its challenges. It is beyond the scope of this paper to debate each system's merits. Not any one finish will be right for all applications, but currently the most commonly seen in large scale consumer electronics is OSP. A high quality OSP like Enthone® Entek® Plus HT is recommended.

### **PWB MATERIAL**

It is recommended that lead free FR-4 is used in PWB construction. Lower quality FR-4 can cause numerous problems with the reflow temperatures seen when using lead free solder. IPC-4101B "Specification for Base Materials for Rigid and Multilayer Printed Boards" contains further information on choosing the correct PWB material for the intended application.

### EXPERIMENTAL PROCEDURE

The study which led to the recommendations here for four of the most critical processing parameters will not be described in detail, but a brief description of the methodology will be presented. Four factors were studied to determine a baseline of recommendations for mounting Fairchild Semiconductor WLCSP with 500µm pitch and 300µm diameter lead free solder bumps. There will not be a suggestion for one type of process. Various customer and industry specifications mean that the WLCSP will be used with many different processes. Using six sigma based techniques, and JMP® software, the interrelated effects of the factors are captured and used for defining the best process based on certain customer requirements.

The four factors are, whether the pad is solder mask defined, SMD, or non-solder mask defined NSMD (also sometimes known as "copper defined"), pad diameter, solder stencil opening and via in pad, or no via in pad. Below each factor will be discussed, and following this, a summary chart of recommendations will be attached in the appendix.

#### SMD/NSMD PADS

SMD pads are exactly what the name says; pads defined by the solder mask on the board. The opening of the solder mask is smaller than the underlying copper area for soldering to the associated bump. A NSMD pad has a solder mask opening larger than the copper pad.

There are many factors influencing whether the PWB designer uses solder mask defined or non solder mask defined pads. Due to external influences the designer may be forced to use one type or the other. Either type can successfully be used with WLCSP packages, but each has characteristics worth noting here.

NSMD pads are perhaps more commonly recommended in the literature. NSMD pads have two key advantages; solder may wet down the side of the copper pad theoretically enhancing the solder joint-PWB bond, and copper etching is a more precise process than solder mask at the board construction level. There are no free lunches however. NSMD pads have less copper on the board, and are thus more prone to damage during rework, and it was found in this study that NSMD pads had higher incidences of voiding and shorting in manufacturing than SMD pads.

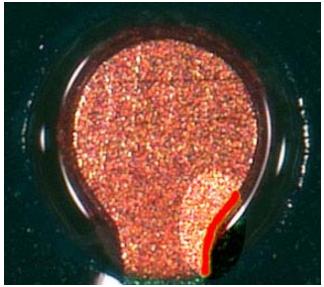

If NSMD pads are chosen, the opening between the pad and solder mask should have at least 50  $\mu$ m clearance. The trace width of interconnections between pads should be no more than 60% the diameter of the pad. The trace should have a fillet radius at the point it meets the pad, this is also known as "tear dropping". This prevents the stress riser that would otherwise occur at the pad/trace intersection.

Figure 1: NSMD Pad with "tear drop" radius highlighted.

SMD pads have copper areas larger than the pad and are defined by the opening in the solder mask. SMD pads have been found to have better void and short performance in reflow than NSMD pads. SMD pads also typically withstand the stresses of rework better than NSMD pads. The main downsides of SMD pads are being defined by the solder mask, which is a typically a less accurate process than the copper layer. Also, SMD pads also have less area for solder to wet to at the bump-PWB interface. However, with lead free solders the long-term failure mechanism (as seen in temperature cycling tests) is typically cracking at the die-bump intermetallic interface, so this may not have an effect on long term reliability.

#### PAD DIAMETER

Pad diameter is also another factor that may be determined by corporate standard for the board designer. If the board designer has the freedom to choose pad diameter, she may find different diameters recommended ranging from 200-300µm. This is due to the long history of WLCSP packages and a multitude of standards which exist regarding Addressed here are pads with the their use. diameters of 250, 275 and 300µm. With lead free solders engineers have found the need to reduce stress at the die-bump interface. A method of more evenly distributing the stress is to reduce the size of the PWB pad to match (or be close to) the diameter of the die under bump metal which the lead free bump is attached to. It has therefore become more common to see a recommendation of 250µm diameter pads for 300µm bumps, which is what Fairchild Semiconductor recommends on its datasheets.

## STENCIL APERTURE

Stencil apertures are defined by the size and shape of the holes cut into the stencil used in screen printing. Fine pitch components work best with 4 mils thick stencils, and that is what was used here for all trials. All openings are square in shape, laser cut into stainless steel and polished. This gives better paste release than round apertures. It was found that a slight overprint of solder would yield superior voiding performance in reflow with most pad types. However, overprinting solder also increases the likelihood of shorting. It is recommended to print at 1:1 or, slightly overprint as recommended in the summary chart depending on what the process engineer is trying to optimize.

## VIA IN PAD

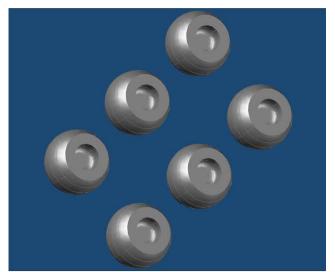

The need for via in pad will be determined by the design. There are many reasons to avoid via in pad if possible, chiefly voiding/inconsistency of solder joints after reflow and the introduction of more failure points in the PWB. If the designer must use via in pad, it is recommended to drill small vias allowing them to be plated solid if possible. With any via in pad PWB the quality of the vendor making the board is more important. Via in pad will create significant voiding in the solder joints. The typical void will be the via diameter to a depth of approximately 1/3 the bump height.

Figure 2: Solid model of voids in bumps created by via in pad board design.

Finite Element Analysis was done to simulate the effects of this void and no increase in stress at the critical die-bump interface was found.

### SOLDER PASTE

The WLCSP is a RoHS compliant and lead free package. Any standard lead free no clean solder paste, made with type 3 or type 4 powder as commonly used in the industry should work with this package. The IPC Solder Products Value Council has recommended that the lead free alloy, 96.5 Sn/3.0Ag/0.5Cu, commonly known as SAC 305, is "...the lead free solder paste alloy of choice for the electronics industry". Type 3 no-clean paste, SAC 305 alloy, was used for the construction of the boards studied to optimize the process.

## **REFLOW PROFILE**

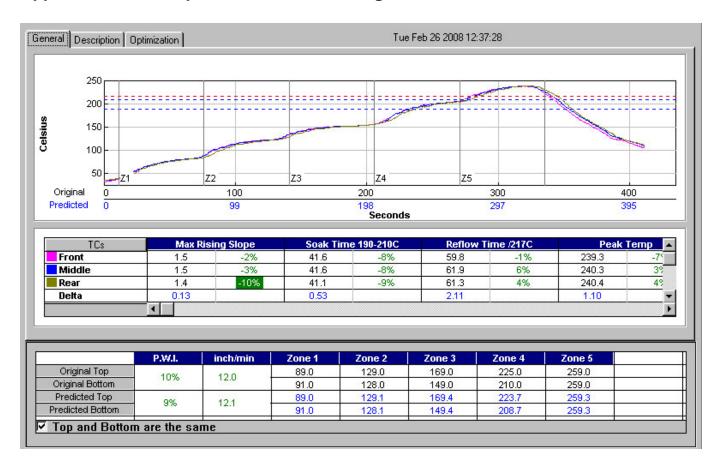

The optimum reflow profile used for every product and oven is different. Even the same brand and model oven in a different facility may require a different profile. The proper ramp and soak rates are determined by the solder paste vendor for their products. Obtaining this information from the paste vendor is highly recommended. If one is using a KIC® profiler, downloading the latest paste library from KIC® will yield ramp rate and soak times at temperature for most commonly used solder pastes. Fairchild WLCSP packages are rated for 260°C peak temperature reflow. Attached in the appendix is a reflow profile example. This profile is provided for reference only; different PWBs, ovens and pastes will change this profile, perhaps dramatically.

### INSPECTION

WLCSP requires different equipment for inspection after reflow than many other surface mount technology components. WLCSP alignment can be inspected in production by

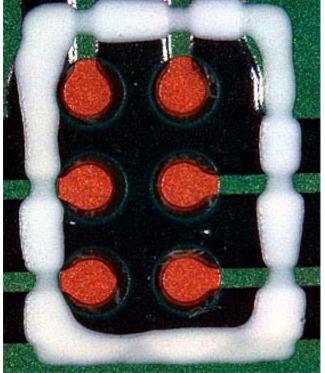

Figure 3: Printed boarder on PWB for visual confirmation of WLCSP alignment.

checking alignment with a boarder printed on the stencil layer of the PWB. Inspection of the solder joints for shorts and voiding is more challenging. There are two methods, side looking cameras using technology to look under the die and allow an operator to inspect the bumps, and more commonly, x-ray. The industry standard for voiding is currently 25% distributed throughout the solder joint.

### REWORK

Due to the high temperatures associated with lead free reflow, it is recommended that this component not be reused if rework becomes necessary. The WLCSP should be removed from the PWB with hot air. After removal, the WLCSP should be discarded. The solder remnants should be removed from the pad with a solder vacuum or solder wick, the pads cleaned and new paste printed with a mini stencil. A WLCSP rework station should be used to align and place the replacement WLCSP, and this machine will typically have a programmable reflow profile using hot air to reflow the solder and make the joint.

# **BOARD LEVEL RELIABILITY**

As part of the standard reliability testing this package was temperature cycled from -10 to 100C. There could be no failures in the sample set at 1000 cycles to pass the test. Extended testing was also successfully completed with various industry standard drop and bend tests as commonly required for portable electronic device. For further information on these studies, contact Fairchild Semiconductor.

### **WORKS CITED**

- Aspandiar, Raiyo, "Voids in Solder Joints," SMTA Northwest Chapter Meeting, September 21, 2005, Intel Corporation

- [2] Bryant, Keith, "Investigating Voids," Circuits Assembly, June 2004

- [3] Englemaier, Werner, "Voids in solder joints-reliability," Global SMT & Package, December 2005

- [4] IPC Solder Products Value Council, "Round Robin Testing and Analysis of Lead Free Solder Pastes with Alloys of Tin, Silver and Copper," 2005

- [5] IPC-A-610-D, "Acceptance of Electronic Assemblies," February 2005

- [6] IPC J-STD-001D, "Requirements for Soldered Electrical and Electronic Assemblies,"

- [7] IPC-SM-7525A, "Stencil Design Guidelines," May 2000

- [8] IPC-7531A "Generic Requirements for Surface Mount Design and Land Pattern Standard," February 2007

- [9] JEDEC, JESD22-B102D, "Solderability," VA, Sept. 2004

- [10]Lang, Dennis, "Determining a Robust WLCSP Mounting Process Using Six Sigma Methodology," IMAPS Device Packaging Conference, March 2008

Applicable FSIDs: FPF1003, FPF1004, FDZ191P, FDZ193P

Appendix 1: Solder Stencil Recommendations Based on Pad Size and Pad Type

Notes: 1. This spec is based on minimizing voiding. 1:1 printing of the pads is a recommendable alternative. 2. The reduced printings on NSMD come from shorting and voiding found with bigger prints.

|              | SMD                     | NSMD |

|--------------|-------------------------|------|

| Pad Diameter | Square Stencil Aperture |      |

| 0.25mm       | 0.3                     | 0.28 |

| 0.275mm      | 0.3                     | 0.28 |

| 0.30mm       | 0.3                     | 0.28 |

## Appendix 2: Reflow profile used for building demonstration boards.