### www.fairchildsemi.com

# **AN-6028** FMS6406 Evaluation Board Application Note

### Summary

The FMS6406 evaluation board provides a flexible base for evaluating the performance of the FMS6406. The board operates from a standard supply voltage of +5V + -5%.

The FMS6406 is a dual-Y/C 5th-order Butterworth low-pass video filter driver optimized for minimum overshoot and flat group delay. The device also contains a summing circuit to generate filtered composite video, an audio trap, and a group-delay compensation circuit.

For a complete description of the FMS6406, please refer to the FMS6406 datasheet at: http://www.fairsbildcami.com/pf/EM/EMS6406.html

http://www.fairchildsemi.com/pf/FM/FMS6406.html

## Applications

- Cable set-top boxes

- Satellite set-top boxes

- Personal Video Recorders (PVR)

- Video On Demand (VOD)

### **Evaluation Kit Contents**

The FMS6406 Evaluation Kit contains the following items:

- AN-6028 FMS6406 Evaluation Board Application Note

- The latest revision of the FMS6406 datasheet, also available at <u>http://www.fairchildsemi.com</u>.

- Fully functional FMS6406 evaluation board

- Female power connector

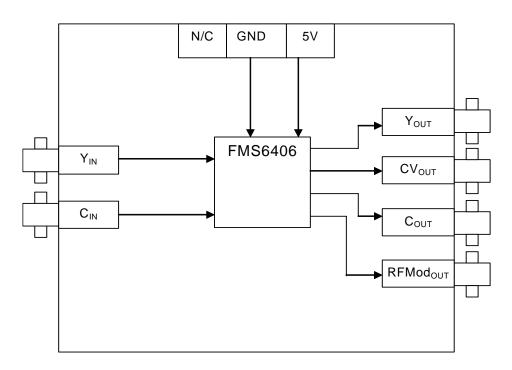

#### Figure 1. FMS6406 Block Diagram

# **Board Setup**

Use the following procedure to verify that the FMS6406 evaluation board is functional. This only verifies functionality. These instructions do not test any parameters outlined in the datasheet. The following test equipment is necessary to test the FMS6406 evaluation board:

- One power supply  $+5V \pm 5\%$ , 250mA

- One high-resolution CRT monitor

- One NTSC or PAL video signal source capable of generating necessary outputs

- One video measurement set (VM700)

- Assorted video cables

Do NOT turn on power supply until all connections are completed.

### **Board Test**

- 1. Set the power supply to 5.0V.

- 2. Connect the power supply to the input voltage terminals of the evaluation board.

- 3. Connect the  $Y_{OUT}$  signal from the signal source to the  $Y_{IN}$  connector on the FMS6406 evaluation board.

- 4. Connect the  $C_{OUT}$  signal from the signal source to the  $C_{IN}$  connector on the FMS6406 evaluation board.

- 5. Connect the  $\mbox{CV}_{\mbox{\scriptsize IN}}$  of the monitor to the  $\mbox{CV}_{\mbox{\scriptsize OUT}}$  connector on the FMS6406 evaluation board.

- 6. Turn on the power supply.

- 7. Verify test pattern that is produced from the generator is the same as the pattern on the monitor screen.

Functional test is complete.

### **Bill of Materials**

| ltem | Quantity | Reference                         | Part        |

|------|----------|-----------------------------------|-------------|

| 1    | 3        | C1,C2,C8                          | 0.1µF       |

| 2    | 4        | C3,C4,C5,C6                       | 220µF       |

| 3    | 1        | C7                                | 0.01µF      |

| 4    | 1        | C10                               | 22µF /25v   |

| 5    | 1        | C11                               | 0.47µF /25v |

| 6    | 1        | D1                                | GREEN       |

| 7    | 1        | D2                                | 1N4004      |

| 8    | 1        | FB1                               | 10µH        |

| 9    | 6        | JP1,JP2,JP3,JP4,JP5,JP6           | JUMPER      |

| 10   | 1        | JP7                               | PWRCON3     |

| 11   | 6        | J1,J2,J3,J4,J5,J6                 | BNC         |

| 12   | 10       | R1,R2,R5,R6,R7,R8,R9,R10, R11,R12 | 75          |

| 13   | 5        | R2,R3,R4,R13,R14                  | 0           |

| 14   | 6        | TP1,TP2,TP3,TP4,TP5,TP6           | TP          |

| 15   | 1        | U1                                | FMS6406     |

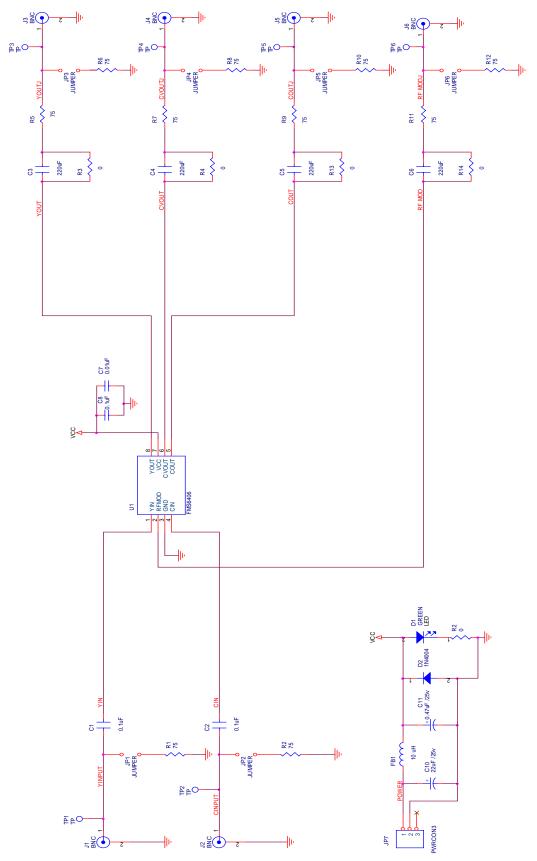

### **Board Schematic**

### **Applications Information**

The FMS6406 is designed to support AC-coupled input and may have AC- or DC- coupled output. Both channels have DC-restore circuitry to clamp the DC input levels during video sync. The Y and C channels use separate feedback clamps. The clamp pulse is derived from the Y channel.

### Luminance (Y) I/O

The typical luma input is driven by either a low-impedance source of  $1V_{pp}$  or the output of a 75 $\Omega$  terminated line driven by the output of a current DAC. In either case, the input must be capacitively coupled to allow the sync-detect and DC-restore circuitry to operate properly. All outputs are capable of driving  $2V_{pp}$ , AC- or DC-coupled, into either a single or dual video load. A single video load consists of a series 75  $\Omega$  impedance-matching resistor connected to a terminated 75  $\Omega$  line, which presents a total of 150  $\Omega$  loading to the part. A dual load would be two in parallel, which would present a total of 75  $\Omega$  to the part. The gain of the Y, C and CV signals is 6dB with  $1V_{pp}$  input levels. Even when two loads are present, the driver produces a full  $2V_{pp}$  signal at its output pin.

#### Chrominance (C) I/O

The chrominance input can be driven in the same manner as the luminance input, but is typically only a  $0.7V_{pp}$  signal. Since the chrominance signal doesn't contain any DC content, the output signal can be AC coupled using a capacitor as small as  $0.1\mu$ F if DC coupling is not desired.

#### Composite Video (CV) Output

The composite video output driver is the same as the other outputs. When driving a dual load, either output functions if the other output connection is inadvertently shorted, providing these loads are AC coupled.

#### Equalizer/Notch (EQ\_NOTCH) Output

This output is designed to drive a 600  $\Omega$  load to  $2V_{pp}$  to meet its primary intention of driving a modulator load.

#### **Layout Considerations**

General layout and supply bypassing play major roles in highfrequency performance and thermal characteristics. The FMS6406 evaluation board is a four-layer board with full power and ground planes. Following this layout configuration provides the optimum performance and thermal characteristics. For best results, follow the rules below as a basis for high-frequency layout:

- Include 1µF and 0.1µF ceramic bypass capacitors.

- Place the  $1\mu$ F capacitor within 0.75 inches of the power pin.

- Place the 0.1µF capacitor within 0.1 inches of the power pin.

- For multi-layer boards, use a large ground plane to help dissipate heat.

- For two-layer boards, use a ground plane that extends beyond the device by at least 0.5 inches.

- Minimize all trace lengths to reduce series inductances.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.