# EN29F002 / EN29F002N 2 Megabit (256K x 8-bit) Flash Memory

#### **FEATURES**

- 5.0V ± 10% for both read/write operation

- Read Access Time

- 45ns, 55ns, 70ns, and 90ns

- Fast Read Access Time

- 70ns with  $C_{load} = 100pF$

- 45ns, 55ns with  $C_{load} = 30pF$

- Sector Architecture:

One 16K byte Boot Sector, Two 8K byte

Parameter Sectors, one 32K byte and

three 64K byte main Sectors

- Boot Block Top/Bottom Programming Architecture

- High performance program/erase speed

- Byte program time: 10µs typical

- Sector erase time: 500ms typical

- Chip erase time: 3.5s typical

- Low Standby Current

- 1µA CMOS standby current-typical

- 1mA TTL standby current

- Low Power Active Current

- 30mA active read current

- 30mA program / erase current

- JEDEC Standard program and erase commands

- JEDEC standard DATA polling and toggle bits feature

- Hardware RESET Pin (n/a for EN29F002N)

- Single Sector and Chip Erase

- Sector Protection / Temporary Sector Unprotect (RESET = V<sub>ID</sub>)

- Sector Unprotect Mode

- Embedded Erase and Program Algorithms

- Erase Suspend / Resume modes: Read and program another sector during Erase Suspend Mode

- 0.4 µm double-metal double-poly triple-well CMOS Flash Technology

- Low Vcc write inhibit ≤ 3.2V

- 100K endurance cycle

- Package Options

- 32-pin PDIP

- 32-pin PLCC

- 32-pin TSOP (Type 1)

- Commercial and Industrial Temperature Ranges

#### **GENERAL DESCRIPTION**

The EN29F002 / EN29F002N is a 2-Megabit, electrically erasable, read/write non-volatile flash memory. Organized into 256K words with 8 bits per word, the 2M of memory is arranged in seven sectors (with top/bottom configuration), including one 16K Byte Boot Sector, two 8K Byte Parameter sectors, and four main sectors (one 32K Byte and three 64K Byte). Any byte can be programmed typically at 10µs. The EN29F002 / EN29F002N features 5.0V voltage read and write operation. The access times are as fast as 45ns to eliminate the need for WAIT states in high-performance microprocessor systems.

The EN29F002 / EN29F002N has separate Output Enable ( $\overline{\text{OE}}$ ), Chip Enable ( $\overline{\text{CE}}$ ), and Write Enable ( $\overline{\text{WE}}$ ) controls which eliminate bus contention issues. This device is designed to allow either single sector or full chip erase operation, where each sector can be individually protected against program/erase operations or temporarily unprotected to erase or program. The device can sustain a minimum of 100K program/erase cycles on each sector.

## **TABLE 1. PIN DESCRIPTION**

| Pin Name                        | Function                           |

|---------------------------------|------------------------------------|

| A0-A17                          | Addresses                          |

| DQ0-DQ7                         | Data Input/Outputs                 |

| CE                              | Chip Enable                        |

| ŌĒ                              | Output Enable                      |

| WE                              | Write Enable                       |

| RESET<br>(n/a for<br>EN29F002N) | Hardware Reset<br>Sector Unprotect |

| Vcc                             | Supply Voltage (5V ± 10%)          |

| Vss                             | Ground                             |

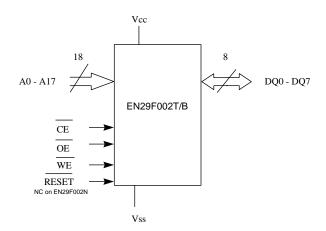

## FIGURE 1. LOGIC DIAGRAM

## **TABLE 2. BLOCK ARCHITECTURE**

## **TOP BOOT BLOCK**

| SECTOR | ADDRESSES       | SIZE (Kbytes) |  |  |  |

|--------|-----------------|---------------|--|--|--|

| 6      | 3C000h - 3FFFFh | 16            |  |  |  |

| 5      | 3A000h - 3BFFFh | 8             |  |  |  |

| 4      | 38000h - 39FFFh | 8             |  |  |  |

| 3      | 30000h - 37FFFh | 32            |  |  |  |

| 2      | 20000h - 2FFFFh | 64            |  |  |  |

| 1      | 10000h - 1FFFFh | 64            |  |  |  |

| 0      | 00000h - 0FFFFh | 64            |  |  |  |

## **BOTTOM BOOT BLOCK**

| ADDRESSES       | SIZE (Kbytes) |

|-----------------|---------------|

| 30000h - 3FFFFh | 64            |

| 20000h - 2FFFFh | 64            |

| 10000h - 1FFFFh | 64            |

| 08000h - 0FFFFh | 32            |

| 06000h - 07FFFh | 8             |

| 04000h - 05FFFh | 8             |

| 00000h - 03FFFh | 16            |

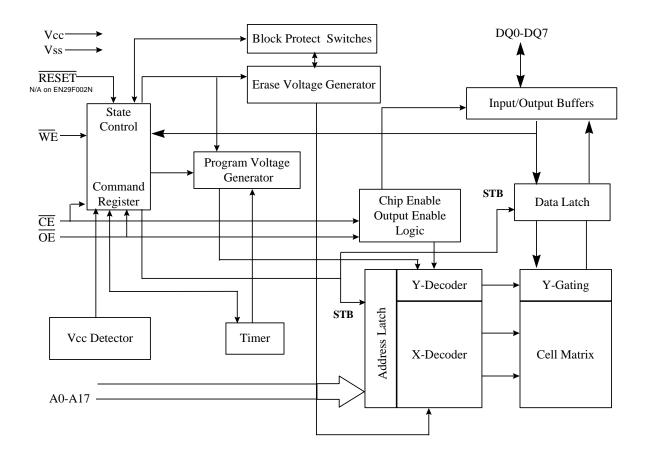

# **BLOCK DIAGRAM**

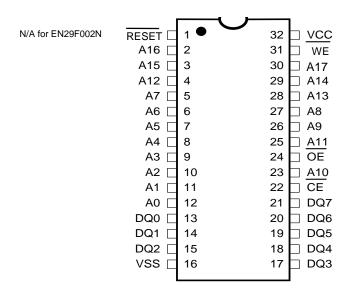

## FIGURE 2. PDIP

## **PDIP Top View**

## FIGURE 3. TSOP

#### TSOP ᄀᅋ 2 3 31 30 4 29 28 DQ7 DQ6 DQ5 A17 WE 27 26 25 24 23 22 21 20 ⊐DQ4 Ycc □ SET □ ⊐ DQ3 RESET A 16 A 15 N/A for EN29F002N □ Yss □ DQ2 EN29F002 12 13 | A0 | A1 | A2 | A3 14 15 19 18 Α4 16 17

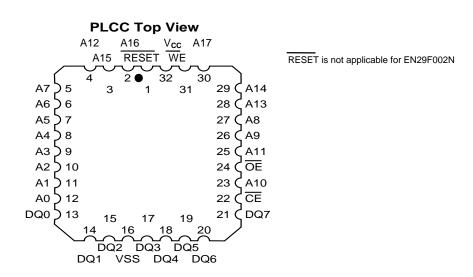

#### FIGURE 4. PLCC

Tel: 408-235-8680

## **TABLE 3. OPERATING MODES**

## **2M FLASH USER MODE TABLE**

|                              | CE | WE | ŌE  | RESET | A9  | A8  | A6 | A1 | A0 | Ax/y | DQ(0-7)            |

|------------------------------|----|----|-----|-------|-----|-----|----|----|----|------|--------------------|

| USER MODE                    |    |    |     |       |     |     |    |    |    |      |                    |

| RESET<br>(n/a for EN29F002N) | Х  | Х  | Х   | L     | Х   | Х   | Х  | Х  | Х  | Х    | HI-Z               |

| STANDBY                      | Н  | X  | X   | Н     | Χ   | Χ   | Χ  | Χ  | Χ  | Χ    | HI-Z               |

| READ                         | L  | Η  | L   | Н     | A9  | A8  | A6 | A1 | A0 | Ax/y | DQ(0-7)            |

| OUTPUT DISABLE               | L  | Н  | Н   | Н     | A9  | A8  | A6 | A1 | A0 | Ax/y | HI-Z               |

| READ<br>MANUFACTURER ID      | L  | Н  | L   | Н     | VID | L/H | L  | L  | L  | Х    | MANUFACTURER<br>ID |

| READ DEVICE ID               | L  | Н  | L   | Н     | VID | L/H | L  | L  | Н  | Χ    | DEVICE ID(T/B)     |

| VERIFY SECTOR<br>PROTECT     | L  | Н  | L   | Н     | VID | Х   | L  | Н  | L  | Х    | CODE               |

| ENABLE SECTOR PROTECT        | L  | L  | VID | Н     | VID | Х   | L  | Х  | Х  | Х    | Х                  |

| SECTOR UNPROTECT             | L  | L  | VID | Н     | VID | Х   | Н  | Н  | L  | Х    | X                  |

| WRITE                        | L  | L  | Н   | Н     | A9  | A8  | A6 | A1 | A0 | Ax/y | DIN(0-7)           |

| TEMPORARY SECTOR UNPROTECT   | Х  | Х  | Х   | VID   | Х   | Х   | Х  | Х  | Х  | X    | X                  |

#### NOTES:

- 1)  $L = V_{IL}, H = V_{IH}, V_{ID} = 11.0V \pm 0.5V$

- 2)  $X = Don't care, either V_{IH} or V_{IL}$

## **TABLE 4. DEVICE IDENTIFICTION**

## **2M FLASH MANUFACTURER/DEVICE ID TABLE**

|                                      | A8 | A6 | A1 | A0 | DQ(7-0)<br>HEX        |

|--------------------------------------|----|----|----|----|-----------------------|

| READ<br>MANUFACTURER ID              | L  | L  | L  | L  | MANUFACTURER ID<br>7F |

| READ<br>MANUFACTURER ID              | Н  | L  | L  | L  | MANUFACTURER ID<br>1C |

| READ DEVICE ID (Top Architecture)    | L  | L  | L  | Н  | DEVICE ID<br>7F       |

| READ DEVICE ID (Top Architecture)    | Н  | L  | L  | Н  | DEVICE ID<br>92       |

| READ DEVICE ID (Bottom Architecture) | L  | L  | L  | Н  | DEVICE ID<br>7F       |

| READ DEVICE ID (Bottom Architecture) | Н  | L  | L  | Н  | DEVICE ID<br>97       |

## **USER MODE DEFINITIONS**

#### **Reset Mode**

EN29F002 features a Reset mode that resets the program and erase operation immediately to read mode. If reset ( $\overline{\text{RESET}} = L$ ) is executed when program or erase operation were in progress, the program or erase which was terminated should be repeated since data will be corrupted. This pin is not available for EN29F002N.

## **Standby Mode**

The EN29F002 / EN29F002N has a CMOS-compatible standby mode which reduces the current to < 1  $\mu$ A (typical). It is placed in CMOS-compatible standby when  $\overline{CE}$  and the  $\overline{RESET}$  pins are at  $V_{CC} \pm 0.5 \text{ V}$  ( $\overline{CE}$  pin only, for EN29F002N). The device also has a TTL-compatible standby mode which reduces the maximum  $V_{CC}$  current to < 1mA. It is placed in TTL-compatible standby when  $\overline{CE}$  and  $\overline{RESET}$  pins are at  $V_{IH}$ . Another method of entering standby mode uses only the  $\overline{RESET}$  pin (n/a for EN29F002N). When  $\overline{RESET}$  pin is at  $V_{SS} \pm 0.3V$ , the device enters CMOS-compatible standby with current typically reduced to < 1  $\mu$ A. When  $\overline{RESET}$  pin is at  $V_{IL}$ , the device enters TTL-compatible standby with current reduced to < 1 mA. When in standby modes, the outputs are in a high-impedance state independent of the  $\overline{OE}$  input.

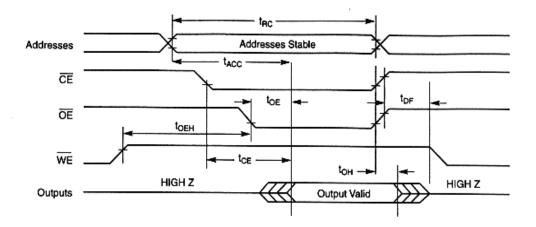

#### **Read Mode**

The EN29F002 / EN29F002N has two control functions which must be satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{CE}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{OE}$ ) is the output control and should be used to gate data to the output pins, provided the device is selected. Read is selected when both  $\overline{CE}$  and  $\overline{OE}$  pins are held at  $V_{IL}$  with the  $\overline{WE}$  pin held at  $V_{IH}$ . Address access time ( $t_{ACC}$ ) is equal to the delay from stable addresses to valid output data. Assuming that addresses are stable, chip enable access time ( $t_{CE}$ ) is equal to the delay from stable  $\overline{CE}$  to valid data at output pins. Data is available at the outputs after output enable access time ( $t_{OE}$ ) from the falling edge of  $\overline{OE}$ , assuming the  $\overline{CE}$  has been LOW and addresses have been stable for at least  $t_{ACC}$  -  $t_{OE}$ .

## **Output Disable Mode**

When the CE or  $\overline{\text{OE}}$  pin is at a logic high level (V<sub>IH</sub>), the output from the EN29F002 / EN29F002N is disabled. The output pins are placed in a high impedance state.

#### **Auto Select Identification Mode**

The manufacturer and device type can be identified by hardware or software operations. This mode allows applications or programming equipment automatically matching the device with its corresponding interface characteristics.

To activate the Auto Select Identification mode, the programming equipment must force 12.0 V  $\pm$  0.5V on address line A9 of the EN29F002T/B. Two identifier bytes can then be sequenced from the device outputs by toggling address lines A0 and A8 from  $V_{IL}$  to  $V_{IH}$ .

The manufacturer and device identification may also be read via the command register. By following the command sequence referenced in the Command Definition Table (Table 5). This method is desirable for in-system identification (using only + 5.0V).

When A0 = A1 = A6 =  $V_{IL}$  and by toggling A8 from  $V_{IL}$  to  $V_{IH}$ , the Manufacturer ID can be read as Eon = 7F, 1C (hex) to identify EON . When A0 =  $V_{IH}$ , A1 = A6 =  $V_{IL}$ , and by toggling A8 from  $V_{IL}$  to  $V_{IH}$ , the

Device Code can be read as 7F, 92 (hex) for EN29F002T or as 7F, 97 (hex) for EN29F002B (See Table 4). All identifiers for manufacturer and device codes possess odd parity with the DQ7 defined as the parity bit.

#### Write Mode

Write is used for device programming and erase through the command register. This mode is selected with  $\overline{CE} = \overline{WE} = L$  and  $\overline{OE} = H$ . The contents of the command register are the inputs to the internal state machine. The command register is a set of latches used to store the commands along with the addresses and data information needed to execute that command. Address latching occurs on the falling edge of  $\overline{WE}$  or  $\overline{CE}$  (whichever occurs later) and data latching occurs on the rising edge of  $\overline{WE}$  or  $\overline{CE}$  (whichever occurs first).

## **Temporary Sector Unprotect Mode**

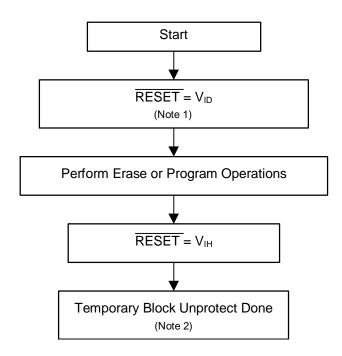

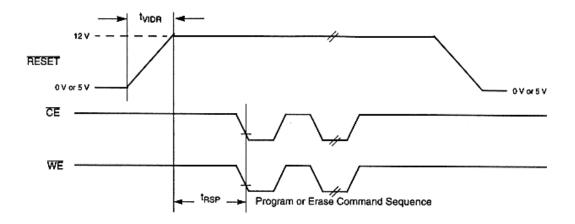

EN29F002 allows protected sectors to be temporarily unprotected for making changes to data stored in a protected sector in system (n/a for EN29F002N). To activate the temporary sector unprotect, the  $\overline{\text{RESET}}$  pin must be set to a high voltage of  $V_{\text{ID}}$  (11V). In this mode, protected sectors can be programmed or erased by selecting the sector addresses. Once the high voltage,  $V_{\text{ID}}$ , is removed from  $\overline{\text{RESET}}$  pin, all previously protected sectors will revert to their protected state.

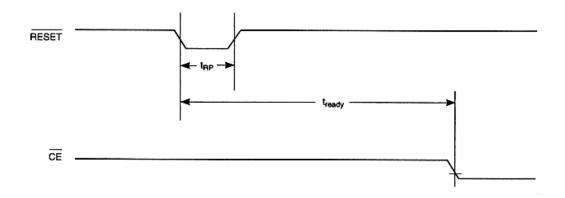

## **RESET Hardware Reset Mode** (not available on EN29F002N)

Resetting the EN29F002 device is performed when the  $\overline{\text{RESET}}$  pin is set to  $V_{IL}$  and kept low for at least 500ns. The internal state machine will be reset to the read mode. Any program/erase operation in progress during hardware reset will be terminated and data may be corrupted. If the  $\overline{\text{RESET}}$  pin is tied to the system reset command, the device will be automatically reset to the read mode and enable the system's microprocessor to read the boot-up firmware from the FLASH memory.

#### **COMMAND DEFINITIONS**

The operations of the EN29F002 are selected by one or more commands written into the command register to perform Read/Reset Memory, Read ID, Read Sector Protection, Program, Sector Erase, Chip Erase, Erase Suspend and Erase Resume. Commands are made up of data sequences written at specific addresses via the command register. The sequences for the specified operation are defined in the Command Table (Table 5). Incorrect addresses, incorrect data values or improper sequences will reset the device to the read mode.

#### Table 5. EN29F002 Command Definitions

| Command<br>Sequence<br>Read/Reset   | Write<br>Cycles<br>Req'd |      | st<br>Cycle | _    | <sup>nd</sup><br>Cycle | _    | Cycle | -        | th<br>Cycle | _    | Cycle | _    | th<br>Cycle |

|-------------------------------------|--------------------------|------|-------------|------|------------------------|------|-------|----------|-------------|------|-------|------|-------------|

|                                     |                          | Addr | Data        | Addr | Data                   | Addr | Data  | Addr     | Data        | Addr | Data  | Addr | Data        |

| Read/Reset                          | 1                        | XXXh | F0h         | RA   | RD                     |      |       |          |             |      |       | -    |             |

| Read/Reset                          | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | F0h   | RA       | RD          |      |       |      |             |

| AutoSelect                          | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | 90h   | 000h/    | 7Fh/        |      |       |      |             |

| Manufacturer ID                     |                          |      |             |      |                        |      |       | 100h     | 1Ch         |      |       |      |             |

| AutoSelect Device ID                | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | 90h   | 001h/    | 7Fh/        |      |       |      |             |

| (Top Boot)                          |                          |      |             |      |                        |      |       | 101h     | 92h         |      |       |      |             |

| AutoSelect Device ID                | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | 90h   | 001h/    | 7Fh/        |      |       |      |             |

| (Bottom Boot)                       |                          |      |             |      |                        |      |       | 101h     | 97h         |      |       |      |             |

| AutoSelect Sector<br>Protect Verify | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | 90h   | SA & 02h | 00h/<br>01h |      |       |      |             |

| Byte Program                        | 4                        | 555h | AAh         | AAAh | 55h                    | 555h | A0h   | PA       | PD          |      |       |      |             |

| Chip Erase                          | 6                        | 555h | AAh         | AAAh | 55h                    | 555h | 80h   | 555h     | AAh         | AAAh | 55h   | 555h | 10h         |

| Sector Erase                        | 6                        | 555h | AAh         | AAAh | 55h                    | 555h | 80h   | 555h     | AAh         | AAAh | 55h   | SA   | 30h         |

| Sector Erase Suspend                | 1                        | xxxh | B0h         |      |                        |      |       |          |             |      |       |      |             |

| Sector Erase Resume                 | 1                        | xxxh | 30h         |      | •                      | •    | •     | •        |             |      | •     |      |             |

#### Notes:

RA = Read Address: address of the memory location to be read. This one is a read cycle.

RD = Read Data: data read from location RA during Read operation. This one is a read cycle.

PA = Program Address: address of the memory location to be programmed

PD = Program Data: data to be programmed at location PA

SA = Sector Address: address of the sector to be erased. Address bits A17-A13 uniquely select any sector.

## **Byte Programming Command**

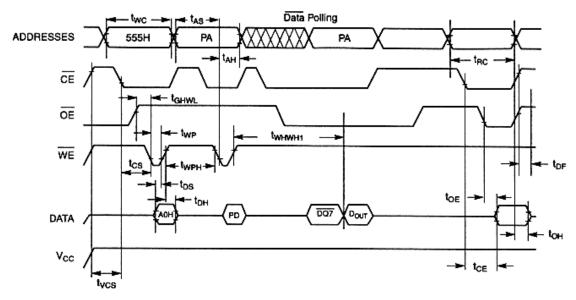

Programming the EN29F002 is performed on a byte-by-byte basis using a four bus-cycle operation (two unlock write cycles followed by the Program Setup command and Program Data Write cycle). When the program command is executed, no additional CPU controls or timings are necessary. The program operation is terminated automatically by an internal timer. Address is latched on the falling edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever is last; data is latched on the rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever is first. The program operation is completed when EN29F002 returns the equivalent data to the programmed location.

Programming status may be checked by sampling data on DQ7 (DATA polling) or on DQ6 (toggle bit). Changing data from 0 to 1 requires an erase operation. When programming time limit is exceeded, DQ5 will produce a logical "1" and a Reset command can return the device to Read mode.

EN29F002 ignores commands written during Byte Programming. If a hardware RESET occurs during Byte Programming, data at the programmed location may get corrupted. Programming is allowed in any sequence and across any sector boundary.

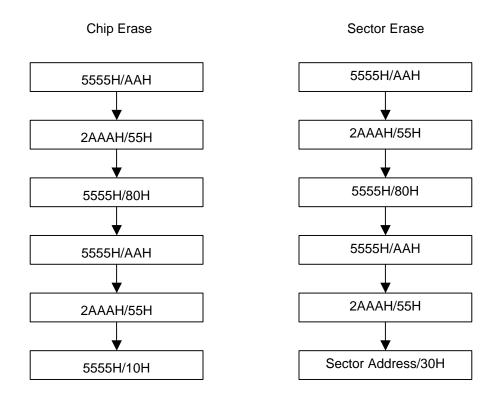

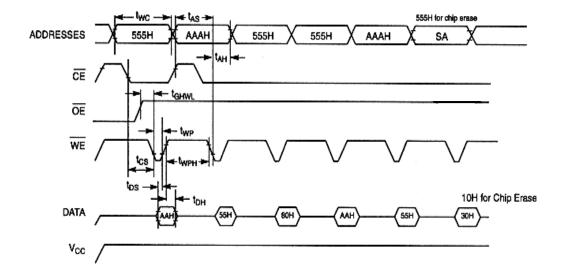

#### **Chip Erase Command**

An auto Chip Erase algorithm is employed when the Chip Erase command sequence is performed. Although the Chip Erase command requires six bus cycles: two unlock write cycles, a setup command, two additional unlock write cycles and the chip erase command, the user does not need to do anything else after that, except check to see if the operation has completed. The Auto Chip Erase algorithm automatically programs and verifies the entire memory array for an all "0" pattern prior to

## EN29F002 / EN29F002N

the erase. Then the EN29F002 will automatically time the erase pulse width, verify the erase, return the sequence count, provide a erase status through DATA POLLING (data on DQ7 is "0" during the operation and "1" when completed, provided the status is not read from a protected sector), and returns to the READ mode after completion of Chip Erase.

#### Sector Erase Command

Sector Erase requires six bus cycles: two unlock write cycles, a setup command, two additional unlock write cycles, and the Sector Erase command. Any sector may be erased by latching any address within the desired sector on the falling edge of WE while the Erase Command (30H) is latched on the rising edge of  $\overline{WE}$ . This device does not support multiple sector erase commands. Sector Erase operation will commence immediately after the first 30h command is written. The first sector erase operation must finish before another sector erase command can be given.

The EN29F002 device automatically programs and verifies all memory locations in the selected sector for an all "0" pattern prior to the erase. Unselected sectors are unaffected by the Sector Erase command. The EN29F002 requires no timing signals during sector erase. Erase is completed when data on DQ7 becomes "1", and the device returns to the READ mode after completion of Sector Erase.

## **Erase Suspend / Resume Command**

Erase suspend allows interruption of sector erase operations to perform data reads from sector not being erased. Erase suspend applies only to Sector Erase operations.

EN29F002 ignores any commands during erase suspend other than the assertion of the RESET pin (n/a for EN29F002N) or Erase Resume commands. Writing erase resume continues erase operations. Addresses are DON'T CARE when writing Erase Suspend or Erase Resume commands.

EN29F002 takes 0.1 - 15 μs to suspend erase operations after receiving Erase Suspend command. Check completion of erase suspend by polling DQ7 and/or DQ6. EN29F002 ignores redundant writes of erase suspend command.

EN29F0002 defaults to erase-suspend-read mode while an erase operation has been suspended. While in erase-suspend-read mode, EN29F002 allows reading data in any sector not undergoing sector erase, which is treated as standard read mode.

Write the Resume command 30h to continue operation of Sector erase. En29F002 ignores redundant writes of the Resume command. En29F002 permits multiple suspend/resume operations during sector erase.

## **Sector Protect and Unprotect**

The hardware sector protection feature disables both program and erase operations in any sector. The hardware sector unprotection feature re-enables both program and erase operation in previously protected sectors.

Sector protection/unprotection must be implemented using programming equipment. The procedure requires a high voltage (V<sub>ID</sub>) on address pin A9 and the control pins. Contact Eon Silicon Devices, Inc. for an additional supplement on this feature.

9

Tel: 408-235-8680

## WRITE OPERATION STATUS

# DQ7 DATA Polling

The EN29F002 provides  $\overline{\text{DATA}}$  Polling on DQ7 to indicate to the host system the status of the embedded operations. The  $\overline{\text{DATA}}$  Polling feature is active during the Byte Programming, Sector Erase, Chip Erase, Erase Suspend. (See Table 6)

When the Byte Programming is in progress, an attempt to read the device will produce the complement of the data last written to DQ7. Upon the completion of the Byte Programming, an attempt to read the device will produce the true data last written to DQ7. For the Byte Programming, DATA polling is valid after the rising edge of the fourth WE or CE pulse in the four-cycle sequence.

When the embedded Erase is in progress, an attempt to read the device will produce a "0" at the DQ7 output. Upon the completion of the embedded Erase, the device will produce the "1" at the DQ7 output during the read. For Chip Erase, the  $\overline{DATA}$  polling is valid after the rising edge of the sixth  $\overline{WE}$  or  $\overline{CE}$  pulse in the six-cycle sequence. For Sector Erase,  $\overline{DATA}$  polling is valid after the last rising edge of the sector erase  $\overline{WE}$  or  $\overline{CE}$  pulse.

DATA Polling must be performed at any address within a sector that is being programmed or erased and not a protected sector. Otherwise, DATA polling may give an inaccurate result if the address used is in a protected sector.

Just prior to the completion of the embedded operations, DQ7 may change asynchronously when the output enable  $(\overline{OE})$  is low. This means that the device is driving status information on DQ7 at one instant of time and valid data at the next instant of time. Depending on when the system samples the DQ7 output, it may read the status of valid data. Even if the device has completed the embedded operations and DQ7 has a valid data, the data output on DQ0-DQ6 may be still invalid. The valid data on DQ0-DQ7 will be read on the subsequent read attempts.

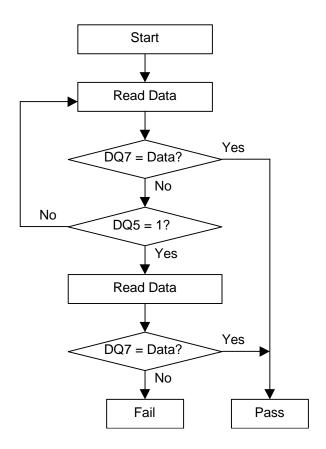

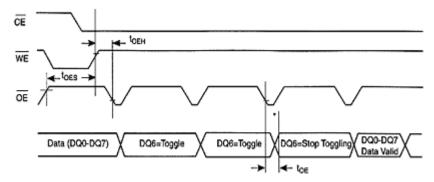

The flowchart for  $\overline{DATA}$  Polling (DQ7) is shown on Flowchart 5. The  $\overline{DATA}$  Polling (DQ7) timing diagram is shown in Figure 8.

## DQ6 Toggle Bit I

The EN29F002 provides a "Toggle Bit" on DQ6 to indicate to the host system the status of the embedded programming and erase operations. (See Table 6)

During an embedded Program or Erase operation, successive attempts to read data from the device at any address (by toggling  $\overline{OE}$  or  $\overline{CE}$ ) will result in DQ6 toggling between "zero" and "one". Once the embedded Program or Erase operation is complete, DQ6 will stop toggling and valid data will be read on the next successive attempts. During Byte Programming, the Toggle Bit is valid after the rising edge of the fourth  $\overline{WE}$  pulse in the four-cycle sequence. For Chip Erase, the Toggle Bit is valid after the last rising edge of the Sector Erase Command (30h)  $\overline{WE}$  pulse.

In Byte Programming, if the sector being written to is protected, DQ6 will toggle for about  $2\mu s$ , then stop toggling without the data in the sector having changed. In Sector Erase or Chip Erase, if all selected sectors are protected, DQ6 will toggle for about 100  $\mu s$ . The chip will then return to the read mode without changing data in all protected sectors.

Toggling either  $\overline{CE}$  or  $\overline{OE}$  will cause DQ6 to toggle.

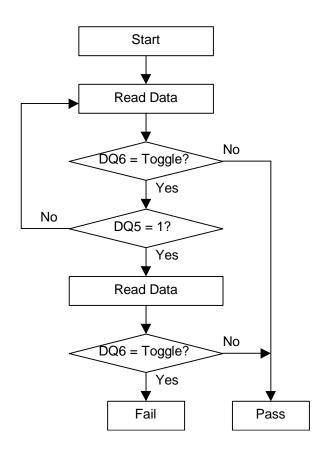

The flowchart for the Toggle Bit (DQ6) is shown in Flowchart 6. The Toggle Bit timing diagram is shown in Figure 9.

#### DQ5

## **Exceeded Timing Limits**

DQ5 will indicate if the program or erase time has exceeded the specified limits (internal pulse count). Under these conditions DQ5 will produce a "1". (The Toggle Bit (DQ6) should also be checked at this time to make sure that the DQ5 is not a "1" due to the device having returned to read mode.) This is a failure condition which indicates that the program or erase cycle was not successfully completed. DATA Polling (DQ7), Toggle Bit (DQ6) and Erase Toggle Bit (DQ2) still function under this condition. Setting the CE to VIH will partially power down the device under those conditions. The  $\overline{OE}$  and  $\overline{WE}$  pins will control the output disable functions as described in Table 3.

The DQ5 failure condition will also appear if the user tries to program a "1" to a location that was previously programmed to a "0". In this case, the device goes into Hang or Error mode out and never completes the Embedded Program Algorithm. Hence, the system never reads valid data on DQ7 and DQ6 never stops toggling. Once the device exceeds the timing limits, DQ5 will indicate a "1". Please note that this is not a device failure condition since the device was used incorrectly. If timing limits are exceeded, reset the device. (See Table 6)

#### DO3

#### **Sector Erase Command Timeout**

This device does not support multiple sector erase commands. DQ3 will go high immediately after the first 30h command (the sixth write cycle). Any extra 30h commands will be ignored (or taken as a resume command if erase suspended).

#### DQ2

## **Erase Toggle Bit II**

In the sector erase operation, DQ2 will toggle with OE or CE when a read is attempted within the sector that is being erased. DQ2 will not toggle if the read address is not within the sector that is selected to be erased. In the chip erase operation, however, DQ2 will toggle with OE or CE regardless of the address given by the user. This is because all sectors are to be erased. (See Table

## Table 6. Status Register Bits

| DQ | Name              | Logic Level             | Definition                                                                                                                                                                              |

|----|-------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                   | '1'                     | Erase Complete or erase sector in Erase suspend                                                                                                                                         |

|    |                   | '0'                     | Erase On-Going                                                                                                                                                                          |

| 7  | DATA<br>POLLING   | DQ7                     | Program Complete or<br>data of non-erase sector<br>during Erase Suspend                                                                                                                 |

|    |                   | <br>DQ7                 | Program On-Going                                                                                                                                                                        |

|    |                   | '-1-0-1-0-1-0-1-'       | Erase or Program On-going                                                                                                                                                               |

|    |                   | DQ6                     | Read during Erase Suspend                                                                                                                                                               |

| 6  | TOGGLE<br>BIT     | '-1-1-1-1-1-1- <b>'</b> | Erase Complete                                                                                                                                                                          |

| 5  | ERROR BIT         | <b>'1'</b>              | Program or Erase Error                                                                                                                                                                  |

|    |                   | '0'                     | Program or Erase On-going                                                                                                                                                               |

| 3  | ERASE<br>TIME BIT | '1'                     | Erase operation start                                                                                                                                                                   |

|    |                   | '0'                     | Erase timeout period on-going                                                                                                                                                           |

|    |                   | '-1-0-1-0-1-0-1-'       | Chip Erase, Erase or Erase suspend on currently addressed sector. (When DQ5=1, Erase Error due to currently addressed sector. Program during Erase Suspend on- going at current address |

| 2  | TOGGLE<br>BIT     | DQ2                     | Erase Suspend read on non Erase Suspend Sector                                                                                                                                          |

#### Notes:

DQ7 DATA Polling: indicates the P/E C status check during Program or Erase, and on completion before checking bits DQ5 for Program or Erase Success.

DQ6 Toggle Bit: remains at constant level when P/E operations are complete or erase suspend is acknowledged. Successive reads output complementary data on DQ6 while programming or Erase operation are on-going.

DQ5 Error Bit: set to "1" if failure in programming or erase

DQ3 Sector Erase Command Timeout Bit: Operation has started. Only possible command is Erase suspend (ES).

DQ2 Toggle Bit: indicates the Erase status and allows identification of the erased sector.

Tel: 408-235-8680 Fax: 408-235-8685

Rev. C, Issue Date: 2001/07/05

## **DATA PROTECTION**

## **Power-up Write Inhibit**

During power-up, the device automatically resets to READ mode and locks out write cycles. Even with  $\overline{CE} = V_{IL}$ ,  $\overline{WE} = V_{IL}$  and  $\overline{OE} = V_{IH}$ , the device will not accept commands on the rising edge of  $\overline{WE}$ .

## Low V<sub>CC</sub> Write Inhibit

During  $V_{CC}$  power-up or power-down, the EN20F002 locks out write cycles to protect against any unintentional writes. If  $V_{CC} < V_{LKO}$ , the command register is disabled and all internal program or erase circuits are disabled. Under this condition, the device will reset to the READ mode. Subsequent writes will be ignored until  $V_{CC} > V_{LKO}$ .

## Write "Noise" Pulse Protection

Noise pulses less than 5ns on  $\overline{OE}$ ,  $\overline{CE}$  or  $\overline{WE}$  will neither initiate a write cycle nor change the command register.

## **Logical Inhibit**

If  $\overline{CE} = V_{IH}$  or  $\overline{WE} = V_{IH}$ , writing is inhibited. To initiate a write cycle,  $\overline{CE}$  and  $\overline{WE}$  must be a logical "zero". If  $\overline{CE}$ ,  $\overline{WE}$ , and  $\overline{OE}$  are all logical zero (not recommended usage), it will be considered a write.

#### **Sector Protection/Unprotection**

When the device is shipped, all sectors are unprotected. Each sector can be separately protected against data changes. Using hardware protection circuitry enabled at user's site with external programming equipment, both program and erase operations may be disabled for any specified sector or combination of sectors.

Verification of write protection for a specific sector can be achieved with an Auto Select ID read command at location 02h where the address bits A17 - A13 select the defined sector (see Table 5). A logical "1" at DQ0 means a protected sector and a logical "0" means an unprotected sector.

The Sector Unprotect disables sector protection in all sectors in one operation to implement code changes. All sectors must be placed in protection mode using the protection algorithm mentioned above before unprotection can be executed.

Additional details on this feature are provided in a supplement, which can be obtained by contacting a representative of Eon Silicon Devices, Inc.

## **EMBEDDED ALGORITHMS**

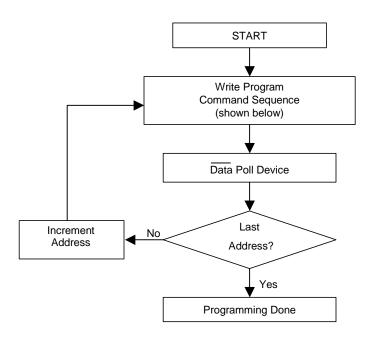

## Flowchart 1. Embedded Program

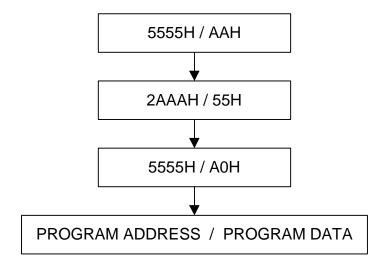

# Flowchart 2. Embedded Program Command Sequence See the Command Definitions section for more information.

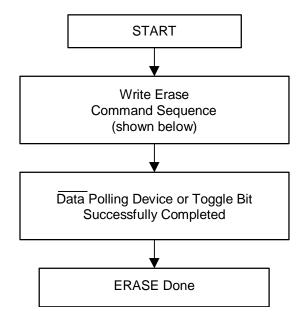

# Flowchart 3. Embedded Erase

# Flowchart 4. Embedded Erase Command Sequence

See the Command Definitions section for more information.

Tel: 408-235-8680 Fax: 408-235-8685

Rev. C, Issue Date: 2001/07/05

# Flowchart 5. DATA Polling Algorithm

Tel: 408-235-8680 Fax: 408-235-8685

Rev. C, Issue Date: 2001/07/05

# Flowchart 6. Toggle Bit Algorithm

# Flowchart 7. Temporary Sector Unprotect Algorithm (Not available for EN29F002N)

#### Notes:

- 1. All protected sectors unprotected.

- 2. All previous protected sectors are protected once again.

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                          |

|----------------------------------------------|

| Plastic Packages –65°C to +125°C             |

| Ambient Temperature                          |

| with Power Applied55°C to +125°C             |

| Voltage with Respect to Ground               |

| V <sub>CC</sub> (Note 1)                     |

| A9, OE# (Note 2) –0.5 V to 11.5 V            |

| All other pins (Note 1)0.5 V to Vcc+0.5V     |

| Output Short Circuit Current (Note 3) 200 mA |

#### Notes:

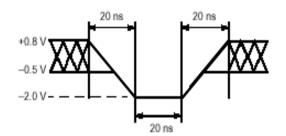

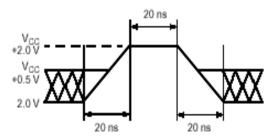

- Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, inputs may undershoot Vss to -1.0V for periods of up to 50 ns and to -2.0 V for periods of up to 20 ns. See Left Figure below. Maximum DC voltage on input and I/O pins is V cc + 0.5 V. During voltage transitions, input and I/O pins may overshoot to Vcc + 2.0 V for periods up to 20 ns. See Right Figure below.

- 2. Minimum DC input voltage on A9 pin is -0.5 V. During voltage transitions, A9 and OE# may undershoot Vss to -1.0V for periods of up to 50 ns and to -2.0 V for periods of up to 20 ns. See Left Figure. Maximum DC input voltage on A9 and OE# is 11.5 V which may overshoot to 12.5 V for periods up to 20 ns.

- 3. No more than one output shorted to ground at a time. Duration of the short circuit should not be greater than one second. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING RANGES**

## Commercial (C) Devices

Ambient Temperature (T A) .....0°C to +70°C

#### Industrial (I) Devices

Ambient Temperature (T A ). . . . . . . -40°C to +85°C

#### **V<sub>CC</sub> Supply Voltages**

Maximum Negative Overshoot Waveform

Maximum Positive Overshoot Waveform

## **Table 7. DC Characteristics**

$(T_a = 0^{\circ}C \text{ to } 70^{\circ}C \text{ or - } 40^{\circ}C \text{ to } 85^{\circ}C; V_{CC} = 5.0V \pm 10\%)$

| Symbol                          | Parameter                                                                               | Test Conditions                                   | Min        | Max       | Uni |

|---------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------|------------|-----------|-----|

|                                 |                                                                                         |                                                   |            | _         | t   |

| ILI                             | Input Leakage Current                                                                   | 0V≤ V <sub>IN</sub> ≤ Vcc                         |            | ±5        | μA  |

| ILO                             | Output Leakage Current                                                                  | 0V≤ V <sub>OUT</sub> ≤ Vcc                        |            | ±5        | μΑ  |

| I <sub>CC1</sub>                | Supply Current (read) TTL Byte                                                          | $CE# = V_{IL}$ ; $OE# = V_{IH}$ ; $f = 6MHz$      |            | 30        | mA  |

| I <sub>CC2</sub>                | Supply Current (Standby) TTL                                                            | CE# = V <sub>IH</sub>                             |            | 1.0       | mA  |

| ICC3                            | Supply Current (Standby) CMOS <sup>(1)</sup>                                            | RESET# = CE# = Vcc ± 0.2V                         |            | 5.0       | μΑ  |

| I <sub>CC4</sub> <sup>(2)</sup> | Supply Current (Program or Erase)                                                       | Byte program, Sector or Chip<br>Erase in progress |            | 30        | mA  |

| V <sub>IL</sub>                 | Input Low Voltage                                                                       |                                                   | -0.5       | 0.8       | V   |

| VIH                             | Input High Voltage                                                                      |                                                   | 2          | Vcc ± 0.5 | V   |

| V <sub>OL</sub>                 | Output Low Voltage                                                                      | I <sub>OL</sub> = 2 mA                            |            | 0.45      | V   |

| Voн                             | Output High Voltage TTL                                                                 | I <sub>OH</sub> = -2.5 mA                         | 2.4        |           | V   |

|                                 | Output High Voltage CMOS                                                                | I <sub>OH</sub> = -100 μA                         | Vcc - 0.4V |           | V   |

| V <sub>ID</sub>                 | A9 Voltage (Electronic Signature)<br>and RESET# Voltage (Temporary<br>Sector Unprotect) |                                                   | 10.5       | 11.5      | V   |

| ILIT                            | A9 and RESET# Current (Electronic Signature)                                            | A9, RESET# = V <sub>ID</sub>                      |            | 100       | μΑ  |

| V <sub>LKO</sub>                | Supply voltage (Erase and Program lock-out)                                             |                                                   | 3.2        | 4.2       | V   |

### Notes:

(1) RESET# pin input buffer is always enabled so that it draws power if not at full CMOS supply voltages

Tel: 408-235-8680 Fax: 408-235-8685

## **Table 8. AC CHARACTERISTICS Read-only Operations Characteristics**

|                   | ameter<br>nbols    |                                                                   |                                                |     |     | Speed           | Option | าร   |    |

|-------------------|--------------------|-------------------------------------------------------------------|------------------------------------------------|-----|-----|-----------------|--------|------|----|

| JEDEC             | Standard           | Description                                                       | Test Setu                                      | р   | -45 | -45 -55 -70 -90 |        | Unit |    |

| t <sub>AVAV</sub> | t <sub>RC</sub>    | Read Cycle Time                                                   |                                                | Min | 45  | 55              | 70     | 90   | ns |

| t <sub>AVQV</sub> | t <sub>ACC</sub>   | Address to Output Delay                                           | $\frac{\overline{CE}}{\overline{OE}} = V_{IL}$ | Max | 45  | 55              | 70     | 90   | ns |

| t <sub>ELQV</sub> | t <sub>CE</sub>    | Chip Enable To Output Delay                                       | OE = VIL                                       | Max | 45  | 55              | 70     | 90   | ns |

| t <sub>GLQV</sub> | t <sub>OE</sub>    | Output Enable to Output Delay                                     |                                                | Max | 25  | 30              | 30     | 35   | ns |

| t <sub>EHQZ</sub> | t <sub>DF</sub>    | Chip Enable to Output High Z                                      |                                                | Max | 10  | 15              | 20     | 20   | ns |

| t <sub>GHQZ</sub> | t <sub>DF</sub>    | Output Enable to Output High Z                                    |                                                | Max | 10  | 15              | 20     | 20   | ns |

| t <sub>AXQX</sub> | t <sub>OH</sub>    | Output Hold Time from Addresses, CE or OE, whichever occurs first |                                                | Min | 0   | 0               | 0      | 0    | ns |

|                   | t <sub>Ready</sub> | RESET Pin Low to Read<br>Mode (n/a for EN29F002N)                 |                                                | Max | 20  | 20              | 20     | 20   | μs |

Notes:

$Vcc = 5.0V \pm 5\%$ For -45,-55

Output Load : 1 TTL gate and 30pF Input Rise and Fall Times: 5ns Input Rise Levels: 0.0 V to 3.0 V

Timing Measurement Reference Level, Input and Output: 1.5 V

For all others:

Vcc = 5.0V ± 10% Output Load: 1 TTL gate and 100 pF Input Rise and Fall Times: 20 ns Input Pulse Levels: 0.45 V to 2.4 V

Timing Measurement Reference Level, Input and Output: 0.8 V and 2.0 V

Tel: 408-235-8680

# Table 9. AC CHARACTERISTICS Write (Erase/Program) Operations

| Parameter Symbols JEDEC Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                 |                         |     |     | Speed | Options |     |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------|-------------------------|-----|-----|-------|---------|-----|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    | Description                     |                         |     | -45 | -55   | -70     | -90 | Unit |

| t <sub>AVAV</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>WC</sub>    | Write Cycle Tim                 | е                       | Min | 45  | 55    | 70      | 90  | ns   |

| t <sub>AVWL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>AS</sub>    | Address Setup                   | Time                    | Min | 0   | 0     | 0       | 0   | ns   |

| t <sub>WLAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>AH</sub>    | Address Hold T                  | ime                     | Min | 35  | 45    | 45      | 45  | ns   |

| t <sub>DVWH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>DS</sub>    | Data Setup Time                 |                         | Min | 20  | 25    | 30      | 45  | ns   |

| t <sub>WHDX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>DH</sub>    | Data Hold Time                  |                         | Min | 0   | 0     | 0       | 0   | ns   |

| Symbol           JEDEC         State           tAVAV         t.W           tAVWL         t.A.           tWLAX         t.A.           tDVWH         t.D.           tWHDX         t.D.           tWHDX         t.D.           tGH         t.D.           tGHWL         t.G.           tWHEH         t.C.           tWHWH         t.W           tWHWH         t.W | t <sub>OES</sub>   | Output Enable S                 | Min                     | 0   | 0   | 0     | 0       | ns  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>OEH</sub>   | Output Enable                   | Read                    | MIn | 0   | 0     | 0       | 0   | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u> </u>           | Hold Time                       | Toggle and DATA Polling | Min | 10  | 10    | 10      | 10  | ns   |

| t <sub>GHWL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>GHWL</sub>  | Read Recovery<br>Write (OE High |                         | Min | 0   | 0     | 0       | 0   | ns   |

| t <sub>ELWL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>CS</sub>    | CE SetupTime                    |                         | Min | 0   | 0     | 0       | 0   | ns   |

| t <sub>WHEH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>CH</sub>    | CE Hold Time                    |                         | Min | 0   | 0     | 0       | 0   | ns   |

| t <sub>WLWH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>WP</sub>    | Write Pulse Wid                 | dth                     | Min | 25  | 30    | 35      | 45  | ns   |

| t <sub>WHDL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>WPH</sub>   | Write Pulse Wid                 | dth High                | Min | 20  | 20    | 20      | 20  | ns   |

| t <sub>WHWH1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>WHWH1</sub> | Programming O                   | peration                | Тур | 7   | 7     | 7       | 7   | μs   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                 |                         | Max | 200 | 200   | 200     | 200 | μs   |

| t <sub>WHWH2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>WHWH2</sub> | Sector Erase O                  | peration                | Тур | 0.3 | 0.3   | 0.3     | 0.3 | S    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                 |                         | Max | 5   | 5     | 5       | 5   | S    |

| t <sub>WHWH3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>WHWH3</sub> | Chip Erase Ope                  | eration                 | Тур | 3   | 3     | 3       | 3   | S    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                 |                         | Max | 35  | 35    | 35      | 35  | s    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>VCS</sub>   | Vcc Setup Time                  |                         | Min | 50  | 50    | 50      | 50  | μs   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>VIDR</sub>  | Rise Time to V <sub>II</sub>    | D                       | Min | 500 | 500   | 500     | 500 | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>RP</sub>    | RESET Pulse (n/a for EN29F0     |                         | Min | 500 | 500   | 500     | 500 | ns   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>RSP</sub>   | RESET Setup                     |                         | Min | 4   | 4     | 4       | 4   | μs   |

Tel: 408-235-8680

# Table 10. AC CHARACTERISTICS Write (Erase/Program) Operations

# Alternate $\overline{\text{CE}}$ Controlled Writes

|                    | nmeter<br>nbols    |                                 |                         |     |     | Speed | Options |                                    |      |

|--------------------|--------------------|---------------------------------|-------------------------|-----|-----|-------|---------|------------------------------------|------|

| JEDEC              | Standard           | Description                     |                         | -   | -45 | -55   | -70     | -90                                | Unit |

| t <sub>AVAV</sub>  | t <sub>WC</sub>    | Write Cycle Tim                 | е                       | Min | 45  | 55    | 70      | 90                                 | ns   |

| t <sub>AVEL</sub>  | t <sub>AS</sub>    | Address Setup                   | Time                    | Min | 0   | 0     | 0       | 0                                  | ns   |

| t <sub>ELAX</sub>  | t <sub>AH</sub>    | Address Hold T                  | ime                     | Min | 35  | 45    | 45      | 45                                 | ns   |

| t <sub>DVEH</sub>  | t <sub>DS</sub>    | Data Setup Time                 |                         | Min | 20  | 25    | 30      | 45                                 | ns   |

| t <sub>EHDX</sub>  | t <sub>DH</sub>    | Data Hold Time                  |                         | Min | 0   | 0     | 0       | 0                                  | ns   |

|                    | t <sub>OES</sub>   | Output Enable S                 | Min                     | 0   | 0   | 0     | 0       | ns                                 |      |

| t <sub>OEH</sub>   | t <sub>OEH</sub>   | Output Enable                   | Read                    | 0   | 0   | 0     | 0       | 0                                  | ns   |

|                    | Hold Time          | Hold Time                       | Toggle and Data Polling | 10  | 10  | 10    | 10      | 10                                 | ns   |

| t <sub>GHEL</sub>  | t <sub>GHEL</sub>  | Read Recovery<br>Write (OE High |                         | Min | 0   | 0     | 0       | 0                                  | ns   |

| t <sub>WLEL</sub>  | t <sub>WS</sub>    | WE SetupTime                    |                         | Min | 0   | 0     | 0       | 0                                  | ns   |

| t <sub>EHWH</sub>  | t <sub>WH</sub>    | WE Hold Time                    |                         | Min | 0   | 0     | 0       | 0                                  | ns   |

| t <sub>ELEH</sub>  | t <sub>CP</sub>    | Write Pulse Wid                 | dth                     | Min | 25  | 30    | 35      | 45                                 | ns   |

| t <sub>EHEL</sub>  | t <sub>CPH</sub>   | Write Pulse Wid                 | th High                 | Min | 20  | 20    | 20      | 20                                 | ns   |

| t <sub>WHWH1</sub> | t <sub>WHWH1</sub> | Programming O                   | peration                | Тур | 7   | 7     | 7       | 7                                  | μs   |

|                    |                    |                                 |                         | Max | 200 | 200   | 200     | 0<br>10<br>0<br>0<br>0<br>45<br>20 | μs   |

| t <sub>WHWH2</sub> | t <sub>WHWH2</sub> | Sector Erase O                  | peration                | Тур | 0.3 | 0.3   | 0.3     | 0.3                                | s    |

|                    |                    |                                 |                         | Max | 5   | 5     | 5       | 5                                  | s    |

| t <sub>WHWH3</sub> | t <sub>WHWH3</sub> | Chip Erase Ope                  | ration                  | Тур | 3   | 3     | 3       | 3                                  | s    |

|                    |                    |                                 |                         | Max | 35  | 35    | 35      | 35                                 | S    |

|                    | t <sub>VCS</sub>   | Vcc Setup Time                  |                         | Min | 50  | 50    | 50      | 50                                 | μs   |

|                    | t <sub>VIDR</sub>  | Rise Time to V <sub>II</sub>    | )                       | Min | 500 | 500   | 500     | 500                                | ns   |

|                    | t <sub>RP</sub>    | RESET Pulse                     |                         | Min | 500 | 500   | 500     | 500                                | ns   |

|                    | t <sub>RSP</sub>   | RESET Setup                     |                         | Min | 4   | 4     | 4       | 4                                  | μs   |

Tel: 408-235-8680

## **Table 11. ERASE AND PROGRAMMING PERFORMANCE**

|                         | Limits |     |        |                                   |

|-------------------------|--------|-----|--------|-----------------------------------|

| Parameter               | Тур    | Max | Unit   | Comments                          |

| Sector Erase Time       | 0.3    | 5   | sec    | Excludes 00H programming prior to |

| Chip Erase Time         | 3      | 35  | sec    | erasure                           |

| Byte Programming Time   | 7      | 200 | μs     | Excludes system level overhead    |

| Chip Programming Time   | 2      | 5   | sec    |                                   |

| Erase/Program Endurance | 100K   |     | cycles | Minimum 100K cycles guaranteed    |

**Table 12. LATCH UP CHARACTERISTICS**

| Parameter Description                                                                              | Min     | Max         |

|----------------------------------------------------------------------------------------------------|---------|-------------|

| Input voltage with respect to Vss on A9 and $\overline{\text{OE}}$ , and $\overline{\text{RESET}}$ | -1.0 V  | 12.0 V      |

| Input voltage with respect to Vss on all other pins                                                | -1.0 V  | Vcc + 1.0 V |

| Vcc Current                                                                                        | -100 mA | 100 mA      |

Note: These are latch up characteristics and the device should never be put under these conditions. Refer to Absolute Maximum ratings for the actual operating limits.

Table 13. 32-PIN PLCC PIN CAPACITANCE @ 25°C, 1.0MHz

| Parameter Symbol | Parameter Description   | Test Setup           | Тур | Max | Unit |

|------------------|-------------------------|----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance       | $V_{IN} = 0$         | 4   | 6   | pF   |

| C <sub>OUT</sub> | Output Capacitance      | V <sub>OUT</sub> = 0 | 8   | 12  | pF   |

| C <sub>IN2</sub> | Control Pin Capacitance | V <sub>IN</sub> = 0  | 8   | 12  | pF   |

Table 14. 32-PIN TSOP PIN CAPACITANCE @ 25°C, 1.0MHz

| Parameter Symbol | Parameter Description   | Test Setup           | Тур | Max | Unit |

|------------------|-------------------------|----------------------|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance       | $V_{IN} = 0$         | 6   | 7.5 | pF   |

| C <sub>OUT</sub> | Output Capacitance      | V <sub>OUT</sub> = 0 | 8.5 | 12  | pF   |

| C <sub>IN2</sub> | Control Pin Capacitance | V <sub>IN</sub> = 0  | 7.5 | 9   | pF   |

Tel: 408-235-8680

## **Table 15. DATA RETENTION**

| Parameter Description               | Test Conditions | Min | Unit  |

|-------------------------------------|-----------------|-----|-------|

| Minimum Pattern Data Retention Time | 150°C           | 10  | Years |

|                                     | 125°C           | 20  | Years |

Tel: 408-235-8680

## **SWITCHING WAVEFORMS**

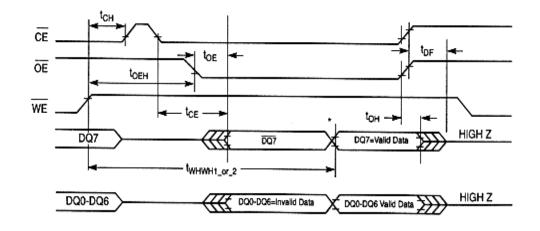

Figure 5. AC Waveforms for READ Operations

Figure 6. AC Waveforms for Chip/Sector Erase Operations

#### Notes:

**1.** SA is the sector address for sector erase.

## **SWITCHING WAVEFORMS (continued)**

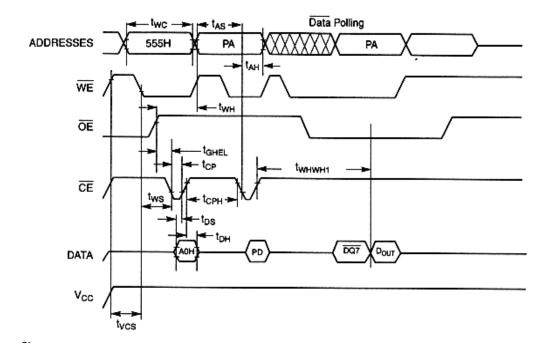

Figure 7. Program Operation Timings

#### Notes:

- 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at byte address.

- 3. /DQ7 is the output of the complement of the data written to the device.

- 4. D<sub>OUT</sub> is the output of data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

Figure 8. AC Waveforms for /DATA Polling During Embedded Algorithm Operations

## Notes:

\*DQ<sub>7</sub> = Valid Data (The device has completed the embedded operation).

Figure 9. AC Waveforms for Toggle Bit During Embedded Algorithm Operations

## Notes:

\*DQ<sub>6</sub> stops toggling (The device has completed the embedded operation).

Figure 10. Temporary Sector Unprotect Timing Diagram

Tel: 408-235-8680 Fax: 408-235-8685

Rev. C, Issue Date: 2001/07/05

# **SWITCHING WAVEFORMS (continued)**

Figure 11. /RESET Timing Diagram

Figure 12. Alternate /CE Controlled Write Operation Timings

#### Notes:

- 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at byte address.

- 3. /DQ7 is the output of the complement of the data written to the device.

- 4. D<sub>OUT</sub> is the output of data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

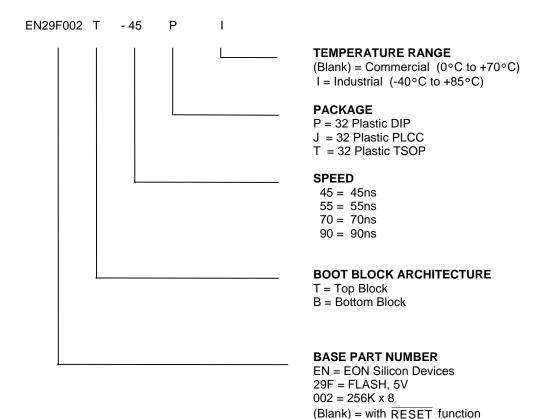

## **ORDERING INFORMATION**

$N = without \overline{RESET}$  function

## **Revisions List**

A:

Preliminary

B (2001.07.03):

Table 7. Icc3 is with RESET# pin at full CMOS levels

Pg. 13 Logical Inhibit section now says that if  $\overline{CE}$ ,  $\overline{WE}$ , and  $\overline{OE}$  are all logical zero (not recommended usage), it will be considered a write.

VID is everywhere changed to be  $V_{ID}$  =11.5 ± 0.5V

C (2001.07.05):

VID is everywhere changed to be  $V_{ID} = 11.0 \pm 0.5 V$

"block" changed to "sector" everywhere appropriate.

Deleted Sector Un/Protect flow charts (we have a supplement for that)

RESET# = VID and not VPP on first page.

LACTHUP >= 200mA line removed from first page

Chip erase and Sector Erase command descriptions modified.

DQ7,DQ5,DQ3 status polling descriptions modified.

Table 7 and Table 12 modified

Absolute Maximum Ratings section added