# \_\_\_EG≥G RETICON

TH Series

Solid State Scanners

## **General Description**

The EG&G Reticon TH series is a family of monolithic self-scanning linear photodiode arrays optimized for application in spectroscopy, specifically HPLC applications. The devices in this series consist of a row of silicon photo diodes. Each photodiode has an associated storage capacitance on which to integrate photo current, and a multiplex switch for periodic readout via an integrated shift register scanning circuit. The part number of each device indicates the number of elements in the array, which vary from 128 to 512. For example, a 256 element array is numbered RL0256THQ011.

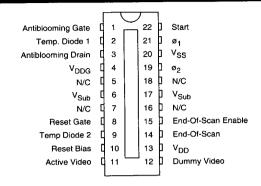

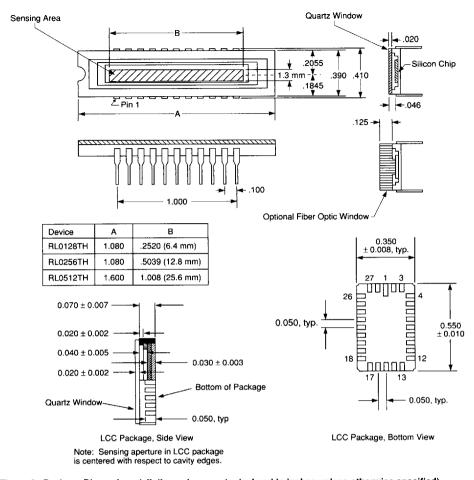

The TH series devices are mounted in ceramic, side-brazed, dual-inline packages that mate with standard 22-pin integrated circuit sockets. The 128-element array is also available in a ceramic LCC package. Pinout configurations are shown in Figure 1. Package dimensions are shown in the outline drawings of Figure 9. Standard TH devices are sealed with a ground and polished quartz window. An optional fiber optic window version is also available for side-brazed packages. The fiber optic window has 6  $\mu m$  diameter fibers and a numerical aperture of 1.

## **Key Features**

- Simultaneous integration of 128, 256, or 512 photodiode elements with 50 µm center-to-center spacing

- Each sensor element has a 26:1 aspect ratio (50 μm x 1.3 mm)

- Extremely low dark current for longer integration times

- Single-supply operation with HCMOS-compatible inputs

- High voltage operation (up to 11V) for increasing dynamic range

- Static shift register design for simplified clocking requirements

- Low output capacitance for low-noise readout

- High saturation charge for wide dynamic range

- · Line Reset/Antiblooming function

- High sensitivity in UV regionHigh UV damage resistance

#### **Sensor Characteristics**

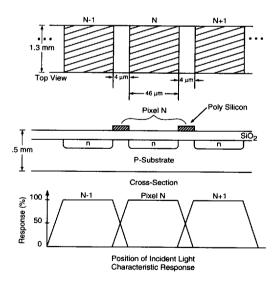

The TH series self-scanning photodiode arrays contain 128, 256, or 512 elements on 50  $\mu m$  centers corresponding to a density of 20 diodes/mm and an overall length of 6.4, 12.8, or 25.6 mm. The height of the sensor elements is 1.3 mm, giving each element a slit-like geometry with 26:1 aspect ratio suitable for coupling to monochromators or spectrographs. The sensor geometry is shown in Figure 3.

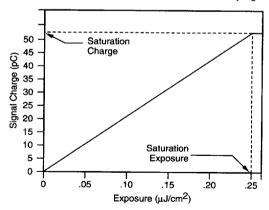

The charge generated by light on the p-type surface between two n-regions will divide between the adjacent diodes to produce the response function shown in Figure 3. Figure 4 shows the typical output charge as a function of exposure at 750 nm wavelength. Exposure in nJ/cm2 is calculated by multiplying the light intensity in  $\mu W/cm^2$  by the integration time in ms. Note that the response is linear with exposure up to a saturation charge of 53 pC at a saturation exposure of .25  $\mu J/cm^2$ .

Figure 1. Pinout Configuration

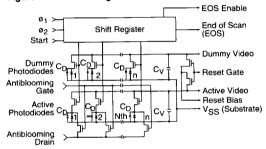

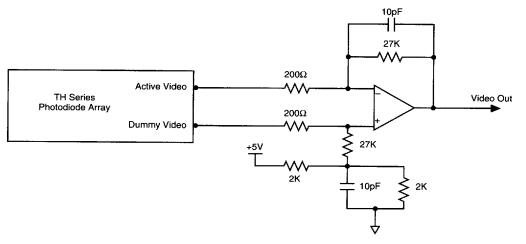

Figure 2. Equivalent Circuit

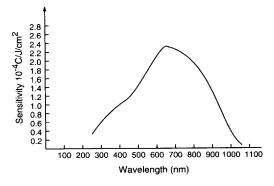

Typical sensitivity as a function of wavelength is shown in Figure 5. Sensitivity is defined as the ratio of saturation charge to saturation exposure and is 2.12 x 10<sup>-4</sup> C/J/cm<sup>2</sup> (at 750 nm).

Peak quantum efficiency is about 75% at 650 nm. Quantum efficiency can be obtained by dividing the sensitivity by the area of a sensor element (6.5 x 10-4 cm2) and multiplying by the energy per photon in eV.

The dark current of a TH series device is typically .14 pA at 25°C and is strongly related to temperature, approximately doubling with every 7°C increase. The dark signal charge equals the dark current multiplied by the integration time. For more information, see Table 2, Electro-Optical Characteristics.

## **Scanning Circuit**

The simplified equivalent circuit of a TH series photodiode array is shown in Figure 2. Each cell consists of an active photodiode and a dummy photodiode. These diodes are connected through MOS multiplex switches to active and dummy video lines. The shift register is driven by complementary

345 POTRERO AVENUE SUNNYVALE, CALIFORNIA 94086-4197 (408) 738-4266 FAX: (408) 738-6979

**■ 3**030738 0004868 554 **■**

299

square wave clocks with periodic start pulses introduced to initiate each scan. The pixel sampling rate is determined by the clock frequency. The integration time is the interval between start pulses. The output signal obtained from each scan of an N-element array is a train of N charge pulses, each proportional to the light exposure on the corresponding photodiode. In addition to the signal charge, switching transients are capacitively coupled to the active video lines by the multiplex switches. Similar transients are introduced into the dummy video lines. Transient noise is reduced and a cleaner signal recovered by reading out the active and dummy video lines differentially.

## **Clock and Voltage Requirements**

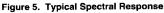

Scanning is achieved by means of an integrated static shift register. The shift register is driven by complementary square wave clocks  $\emptyset 1$  and  $\emptyset _2$ . Table 1 gives rise and fall times and crossover points for these clock waveforms. The clock amplitude should be equal to  $V_{DD} - V_{SS}$ . With  $V_{DD} = 5V$  and  $V_{SS} = 0V$ ; the clock inputs should be HCMOS-compatible. Since each photodiode is read out on a positive transition of  $\emptyset _2$  (see Figure 6), the frequency of the clock signal should be set equal to the desired video data rate.

A start pulse of similar amplitude to the clocks is required to load the shift register and initiate each readout period (each scan of the array). The start pulse is loaded on the falling edge of  $\emptyset_1$ . The start signal is pulsed high for a minimum of 10 ns during one and only one  $\emptyset_2$  clock high cycle. A timing diagram for the start and clock signals is shown in Figure 6. The integration period should be controlled by varying the time between start pulses.

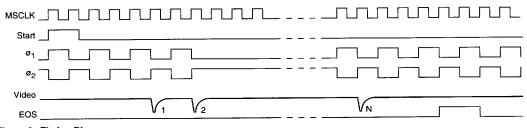

For optimum performance and minimum switching noise, the clocks must be exact complements and their rise and fall times must comply with Table 1. Figure 7 shows a recommended circuit for generating these clocks.

Figure 3. Sensor Geometry and Aperture Response Function

#### **End of Scan**

An EOS output pulse, which is useful primarily for test purposes, is provided two clock cycles after the last photodiode is sampled by the shift register scanning circuit. The timing of the EOS output is shown in Figure 6. The voltage levels on the EOS output will be determined by the  $V_{DD}$  and  $V_{SS}$  voltage levels supplied to the photodiode array. When  $V_{DD}$  is at +5V and  $V_{SS}$  is operated at 0V, the EOS output level will be compatible with the HCMOS family of logic devices. The EOS pulse can be disabled by grounding the end of scan enable input.

## **Amplifier Requirements**

The recommended amplifier for use with TH devices is a simple current amplifier. A current amplifier holds the video line at virtual ground and senses the current pulses flowing into the video line to recharge the diodes through their respective multiplex switches as they are sampled in sequence. These current pulses each contain a charge of up to 53 pC at saturation, and are converted to a train of voltage pulses corresponding to the light intensity on the various diodes. In this mode of operation, the current amplifier must provide a positive bias voltage to the video line, since the photodiode anode (the p-substrate) is biased to 0V (VSS). Figure 8 shows a differential recharge amplifier suitable for use with TH series devices.

The video signal at each photodiode can also be sensed by an external voltage amplifier. When a photodiode is addressed by the digital scanner, its signal charge is shared between the photodiode capacitance and the video line capacitance, causing the video line voltage to vary. This voltage variation can be sensed by an external voltage amplifier. An on-chip reset switch is provided to reset the video line and photodiode after the video line voltage is sensed. Switching transients can be canceled using the dummy video line and reset switches.

#### Line Reset/Antiblooming Control

Under normal operating conditions, TH series devices do not require any blooming control due to their excellent antiblooming characteristics. However, under extremely high

Figure 4. Typical Signal Charge versus Exposure at 750 nm Wavelength

300

contrast conditions, blooming control can be implemented to further enhance antiblooming performance. In this mode of operation, a bias voltage (typically  $V_{DD}$ ) is required on the antiblooming drain. The antiblooming gate is then biased to 1-3V. By adjusting the bias level on the antiblooming gate, any excess charge present on the video line is shunted to the antiblooming drain.

The antiblooming gate can also be used to control the integration time independent of the line scan time (time between start pulses). When the antiblooming gate is held at VDD, all photo diodes are simultaneously reset to the bias voltage on the antiblooming drain. (This should be the same voltage as the video line bias, typically  $V_{\rm DD}/2$ ). Conversely, when the antiblooming gate is held at  $V_{\rm SS}$ , the antiblooming transistor is off and the photo diodes can then integrate photo current. Thus, when an active high pulse is applied to  $V_{\rm ABG}$ , the integration time for diode 'N' then becomes the time interval from the negative-going transition of the antiblooming gate input to the time when diode 'N' is read out through the diode multiplex switch.

## **Dark Signal and Readout Noise**

There are two components of the dark signal from the TH series. These are due to: (1) spatial variations in the switching transients coupled into the video line through the clocks and internal multiplex switches, and (2) the integrated dark current. A portion of the switching transient effect will be spatially random and a portion will have the periodicity of the clocks. The latter portion can be minimized by matching the clock amplitudes and rise and fall times and by good circuit layout to minimize capacitance between clocks and video lines. The peak-to-peak fixed pattern due to all switching transient effects should be less than 1% of the saturated

signal. The dark signal due to dark current is the dark current multiplied by the integration time. It can be arbitrarily reduced by lowering the temperature or by reducing the integration time.

There are three identifiable sources of readout noise: (1) reset noise, (2) shot noise, and (3) amplifier noise. Reset noise is associated with resetting the diode capacitance to a fixed voltage. Its rms. value is given by (kTC)1/2/q where k is Boltzmann's constant, T is the absolute temperature, q is the electronic charge and C is the total capacitance of the photodiode (approximately 10 pF), the video line it connects to, and the capacitance of the external circuitry. At room temperature, kTC noise is approximately 1700 electrons rms. It can be reduced somewhat by cooling. The rms. value of the dark shot noise is the square root of the number of electrons in the dark signal charge. For example, with a room temperature dark current of .14 pA and 10 ms integration time, the RMS dark current shot noise is approximately 94 electrons. Because of the exponential temperature dependence of dark current, shot noise can be reduced dramatically with a moderate amount of cooling. Amplifier noise depends on the amplifier circuit used. In general, the low video output capacitance of the TH series makes it easy to achieve low amplifier noise; values below 2200 electrons are possible.

## **Temperature Diodes**

The TH Series arrays each have 2 on-chip diodes for sensing array temperature. This is usually done by forcing a fixed forward current (normally 10  $\mu\text{A})$  through the diodes and measuring the forward diode voltage drop. For details, please refer to Application Note 130, How to Use Reticon Temperature Diodes.

#### **Evaluation Circuit**

The RC1031 Evaluation Board provides the user with an easy means of evaluating TH series operation (side-brazed packages only). The RC1031 circuit is similar to the circuit shown in Figure 7. The RC1031 has a sample-and-hold video output with a typical dynamic range of 8,000:1. The array can be cooled during evaluation by using a thermal-electric cooler mounted adjacent to the access hole located directly beneath the array. The RC1031 Evaluation Board requires  $\pm 5$  and  $\pm 15V$  supplies and can be adjusted for pixel rates up to 50 kHz.

Figure 6. Timing Diagram

301

**3**030738 0004870 102 🖿

Figure 7. Two-Phase Drive Circuit

Figure 8. Differential Recharge Mode Video Amplifier

302

**3030738 0004871 049**

Table 1. Electrical Characteristics (25°C)

(All voltages measured with respect to V<sub>Sub</sub>)

| Signal                                | Sym                               |      | Min               | Тур                | Max                  | Units |

|---------------------------------------|-----------------------------------|------|-------------------|--------------------|----------------------|-------|

| V <sub>DD</sub>                       | V <sub>DD</sub>                   |      | 4.5               | 5                  | 11                   | V     |

| V <sub>DD</sub> guard                 | V <sub>DDG</sub>                  |      |                   | V <sub>DD</sub>    |                      | V     |

| V <sub>SS</sub>                       | V <sub>SS</sub>                   |      |                   | ō                  |                      | V     |

| Antiblooming drain                    | V <sub>ABD</sub>                  |      |                   | V <sub>DD</sub>    |                      | ٧     |

| Start 1                               | V <sub>SH</sub>                   | High | V <sub>DD</sub> 1 |                    | $V_{DD}$             | ٧     |

|                                       | V <sub>SL</sub>                   | Low  | V <sub>SS</sub>   |                    | V <sub>SS</sub> + .4 | ٧     |

| Clock Ø <sub>1</sub> , Ø <sub>2</sub> | VH1, VH2                          | High | V <sub>DD</sub> 1 | 1                  | V <sub>DD</sub>      | ٧     |

| 1, 2                                  | V <sub>L1</sub> , V <sub>L2</sub> | Low  | V <sub>SS</sub>   |                    | V <sub>SS</sub> + .4 | ٧     |

| Reset gate                            | VHRG                              | High | V <sub>DD</sub> 1 |                    | $V_{DD}$             | ٧     |

| <b>0</b>                              | V <sub>LRG</sub>                  | Low  | V <sub>SS</sub>   |                    | V <sub>SS</sub> + .4 | ٧     |

| Antiblooming gate                     | VHABG                             | High | V <sub>DD</sub> 1 |                    | $V_{DD}$             | ٧     |

| 3 3                                   | VLABG                             | Low  | V <sub>SS</sub>   |                    | V <sub>SS</sub> + .4 | ٧     |

| Video bias                            | VV                                |      | 2                 | V <sub>DD</sub> /2 | V <sub>DD</sub> - 2  | V     |

| Reset drain                           | V <sub>BD</sub>                   |      | 2                 | V <sub>DD</sub> /2 | V <sub>DD</sub> - 2  | V     |

| Clock rate                            | 110                               |      | .001              | 55                 | 1                    | MHz   |

| Start rise time                       | t <sub>rs</sub>                   |      |                   | 10                 | 200                  | ns    |

| Start fall time                       | t <sub>fs</sub>                   |      |                   | 10                 | 200                  | ns    |

| Start pulse width                     | t <sub>pws</sub>                  |      | 10                | i                  |                      | ns    |

| Ø <sub>1</sub> rise time <sup>2</sup> | t <sub>r1</sub>                   |      |                   | 20                 | 100                  | ns    |

| ø <sub>1</sub> fall time <sup>2</sup> | t <sub>f1</sub>                   |      |                   | 20                 | 100                  | ns    |

| ø <sub>2</sub> rise time <sup>2</sup> | t <sub>r2</sub>                   |      |                   | 20                 | 100                  | ns    |

| ø <sub>2</sub> fall time <sup>2</sup> | t <sub>f2</sub>                   |      |                   | 20                 | 100                  | ns    |

| Video delay time                      | tVD                               |      |                   | 20                 |                      | ns    |

| Clock crossings                       | X <sub>1</sub>                    |      | 0                 |                    | 50                   | %     |

| J                                     | X <sub>2</sub>                    |      | 0                 |                    | 50                   | %     |

| Capacitance Ø1, Ø2                    | C <sub>c</sub>                    |      |                   |                    |                      |       |

| at 5V bias                            | "                                 |      |                   |                    |                      |       |

| RL0128TH                              |                                   |      |                   | 60                 |                      | pF    |

| RL0256TH                              |                                   |      | 1                 | 68                 |                      | pF    |

| RL0512TH                              |                                   |      |                   | 80                 |                      | pF    |

| Capacitance, each video               | C <sub>v</sub>                    |      | ]                 | 1                  |                      |       |

| at 2.5V bias                          | •                                 |      |                   |                    | 1                    |       |

| RL0128TH                              |                                   |      |                   | 8                  |                      | рF    |

| RL0256TH                              | 1                                 |      |                   | 12                 |                      | pF    |

| RL0512TH                              |                                   |      |                   | 22                 |                      | pF    |

## Notes:

<sup>1</sup> Can be TTL.

<sup>2</sup> The clock rise and fall times specified are for complementary clocks. The array also can be driven by non-overlapping clocks. There is no restriction on rise and fall time for non-overlapping clocks.

## Table 2. Electro-Optical Characteristics (25°C)

Conditions:

All voltage levels set to typical values shown in Table 1

Light source is 2870°K tungsten filtered with a 750 nm bandpass filter

Video data rate = 80 kHz

| Characteristics                                                                    | Тур                  | Max | Units               |

|------------------------------------------------------------------------------------|----------------------|-----|---------------------|

| Center-to-center spacing                                                           | 50                   |     | μm                  |

| Aperture width                                                                     | 1.3                  |     | mm                  |

| Sensitivity1,2,3                                                                   | 2 x 10 <sup>-4</sup> |     | C/J/cm <sup>2</sup> |

| Nonuniformity of response                                                          |                      |     |                     |

| RL0128TH <sup>2,4,5</sup>                                                          | 5                    | 10  | +%                  |

| RL0256TH <sup>2,4,5</sup>                                                          | 5                    | 10  | ±%                  |

| RL0512TH <sup>2,4,5</sup>                                                          | 5                    | 10  | ±%                  |

| Saturation exposure (E <sub>SAT</sub> ) 1,2,3                                      | .25                  |     | μJ/cm <sup>2</sup>  |

| Saturation charge (QSAT)                                                           | 53                   |     | pC                  |

| Dynamic range                                                                      | 100,000:1            |     |                     |

| (QSAT/QNoise (rms))                                                                | 1 1                  |     |                     |

| (Q <sub>SAT</sub> /Q <sub>Noise (rms)</sub> )<br>Average dark current <sup>6</sup> | .14                  | 0.5 | pΑ                  |

| Spectral response peak                                                             | 650                  |     | nm                  |

| Spectral response range 5,7                                                        | 200-1000             |     | nm                  |

#### Notes:

- Measured at 2.5V video line bias

- Value specified at 750 nm

- Fiber optic faceplate will modify sensitivity as shown in Figure 5

- 4 +% PRNU is defined as [(V<sub>max</sub> V<sub>avg</sub>)/V<sub>avg</sub>] x 100% and -% PRNU is defined as

(V<sub>avg</sub> - V<sub>min</sub>)/V<sub>avg</sub>] x 100%, where V<sub>max</sub> is the output of the pixel closest to saturation level,

V<sub>min</sub> is the output of the pixel closest to dark level,

V<sub>avg</sub> is the numerical average of all the array pixels.

The first and last pixels are not counted in this measurement.

- Measured at an exposure level of E<sub>SAT</sub>/2

- 6 Maximum dark current ≤1.5 x average dark current

- From 250 1000 nm, sensitivity is typically at least 20% of its peak value.

**Table 3. Absolute Maximum Ratings**

|                                                                                         | Min | Max | Units |

|-----------------------------------------------------------------------------------------|-----|-----|-------|

| Voltage applied to any terminal with respect to common Storage of operating temperature | 0   | +15 | ٧     |

| Quartz window                                                                           | -78 | +85 | °C    |

| Fiber optic                                                                             | -40 | +85 | °C    |

Figure 9. Package Dimensions (all dimensions are typical and in inches unless otherwise specified)

## **Ordering Information**

| Part Number                | Evaluation Circuit |  |  |

|----------------------------|--------------------|--|--|

| Quartz Window              |                    |  |  |

| RL0128THQ-011              | RC1031LNN-011      |  |  |

| RL0256THQ-011              | RC1031LNN-011      |  |  |

| RL0512THQ-011              | RC1031LNN-011      |  |  |

| Fiber Optic Window         |                    |  |  |

| RL0128THF-011              | RC1031LNN-011      |  |  |

| RL0256THF-011              | RC1031LNN-011      |  |  |

| RL0512THF-011              | RC1031LNN-011      |  |  |

| Quartz Window, LCC Package |                    |  |  |

| RL0128THQ-111              | none               |  |  |

305