查询CMPWR160供应商

CALIFORNIA MICRO DEVICES

## CMPWR160

## **USB Peripheral Power Management**

#### Features

- 3.3V regulated output up to 500mA

- Quiescent current 35µA (typical)

- Shutdown mode current 7µA (typical)

- 30ms active LOW Power-On Reset (POR) pulse

- Thermal overload protection

- · Foldback current limiting protection

- Reverse-current protection

- 8 pin SOIC power package

#### Applications

- Bus-powered USB peripherals

- Self-powered USB peripherals

- Portable/battery-powered devices

- · Critical power monitoring, hot-insertion devices

The SmartOR<sup>™</sup> CMPWR160 combines a Low Dropout Regulator (LDO) with a Power-On Reset (POR) pulse generator, and is intended for Universal Serial Bus (USB) peripherals. To meet the specification requirements of both USB 1.0 and USB 2.0, the CMPWR160 draws a very low quiescent current (35µA), and delivers up to 500mA of load current at a fixed 3.3V output.

The POR pulse (active LOW) has a typical duration of 30ms after the output has exceeded and stabilized above 2.9V. Thus a new POR pulse is developed each time the regulator power is interrupted and restored, which occurs often on USB buses when cables are connected (or disconnected) by the user. It is not necessary to have a  $V_{\rm CC}$  supply for POR to operate, allowing the CMPWR160 to work in Wired-ORed power systems.

When  $V_{cc}$  is powered down, the device will automatically enter reverse-current protection mode and maintain isolation between  $V_{oUT}$  and  $V_{cc}$ . This is useful for applications that can use power from the USB port in addition to internal batteries or an AC adapter supply (Wired-ORed power systems). In the event of  $V_{cc}$  collapsing below  $V_{oUT}$ , the device will automatically enter shutdown mode and fully isolate the  $V_{cc}$  power source from the output.

A ShutDown input  $(\overline{SD})$  forces the regulator to be powered down on demand. While in shutdown mode the POR circuitry will remain active, making the device suitable for systems which contain backup or alternative power sources.

The CMPWR160 is available in an 8-pin SOIC thermally enhanced package, ideal for applications where space is tight.

| Standard Part Ordering Information |            |                      |                         |            |  |

|------------------------------------|------------|----------------------|-------------------------|------------|--|

| Package                            |            | Ordering Part Number |                         |            |  |

| Pin                                | Style      | Tubes                | Tape & Reel Part Markin |            |  |

| 8                                  | Power SOIC | CMPWR160SA/T         | CMPWR160SA/R            | CMPWR160SA |  |

©2000 California Micro Devices Corp. All rights reserved. SmartOR™ is a trademark of California Micro Devices Corporation.

C1571000

CALIFORNIA MICRO DEVICES

| Absolute Maximum Ratings                  |                                  |      |

|-------------------------------------------|----------------------------------|------|

| Parameter                                 | Rating                           | Unit |

| ESD Protection (HBM)                      | 2000                             | V    |

| V <sub>CC</sub> /V <sub>OUT</sub> Voltage | 6.0, GND –0.5                    | V    |

| SD Logic Input Voltage                    | V <sub>CC</sub> + 0.5, GND -0.5  | V    |

| POR Logic Output Voltage                  | V <sub>OUT</sub> + 0.5, GND –0.5 | V    |

| Temperature: Storage                      | -40 to 150                       |      |

| Operating Ambient                         | 0 to 70                          | °C   |

| Operating Junction                        | 0 to 125                         |      |

| Power Dissipation Note 1                  | Internally Limited               |      |

| Operating Conditions  |            |      |  |

|-----------------------|------------|------|--|

| Parameter             | Range      | Unit |  |

| V <sub>CC</sub>       | 4.2 to 5.5 | V    |  |

| Temperature (Ambient) | 0 to 70    | °C   |  |

| Load Current          | 0 to 500   | mA   |  |

| C <sub>EXT</sub>      | 10 ± 10%   | μF   |  |

|                      | Electrical Operating Characteristics<br>(over operating conditions unless specified otherwise) |                                                                    |       |      |       |      |

|----------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|------|-------|------|

| Symbol               | Parameter                                                                                      | Conditions                                                         | MIN   | ТҮР  | MAX   | UNIT |

| V <sub>OUT</sub>     | Regulator Output Voltage                                                                       | $0mA < I_{LOAD} < 500mA$                                           | 3.135 | 3.30 | 3.465 | V    |

| I <sub>LIM</sub>     | Regulator Current Limit                                                                        |                                                                    | 550   |      |       | mA   |

| I <sub>S/C</sub>     | Short-Circuit Current Limit                                                                    |                                                                    |       | 300  |       | mA   |

| V <sub>R LOAD</sub>  | Load Regulation                                                                                | $V_{CC} = 5V$ , $I_{LOAD} = 5mA$ to 500mA                          |       | 75   |       | mV   |

| V <sub>R LINE</sub>  | Line Regulation                                                                                | $V_{CC} = 4.2V$ to 5.5V, $I_{LOAD} = 5mA$                          |       | 2    |       | mV   |

| V <sub>DO</sub>      | Regulator Dropout Voltage                                                                      | MIN $V_{CC} - V_{OUT}$ for $I_{LOAD} = 500$ mA                     |       | 0.6  | 0.9   | V    |

| l <sub>Q</sub>       | Quiescent Supply Current                                                                       | Regulator Enabled (No Load)                                        |       | 35   | 50    | μA   |

| I <sub>SD</sub>      | Shutdown Supply Current                                                                        | Regulator Disabled                                                 |       | 7    | 10    | μA   |

| I <sub>RCC</sub>     | V <sub>CC</sub> Pin Reverse Leakage                                                            | $V_{OUT} = 3.3 V, V_{CC} = 0 V$                                    |       | 1    | 10    | μA   |

| V <sub>IH SD</sub>   | Shutdown High Detect                                                                           | $V_{CC} = 5V$                                                      |       | 3.0  |       | V    |

| V <sub>IL SD</sub>   | Shutdown Low Detect                                                                            | $V_{CC} = 5V$                                                      |       | 1.0  |       | V    |

| V <sub>POR</sub>     | POR Detect Threshold                                                                           | $4.2V < V_{CC} < 5.5V$                                             | 2.8   | 2.9  | 3.0   | V    |

| T <sub>POR</sub>     | POR Pulse Duration                                                                             |                                                                    | 20    | 30   | 40    | ms   |

| R <sub>POR</sub>     | POR Output Impedance                                                                           | After POR Threshold Detected Sinking to GND/Sourcing from $V_{CC}$ | 0.2   | 0.5  | 2     | kΩ   |

| T <sub>DISABLE</sub> | Shutdown Temperature                                                                           |                                                                    |       | 160  |       | °C   |

| T <sub>HYST</sub>    | Thermal Hysteresis                                                                             |                                                                    |       | 20   |       | °C   |

Note 1: The SOIC package used is thermally enhanced through the use of a fused integral leadframe. The power rating is based on a printed circuit board heat spreading capability equivalent to 2 square inches of copper connected to the GND pins. Typical multi-layer boards using power plane construction will provide this heat spreading ability without the need for additional dedicated copper area. (Please consult with factory for thermal evaluation assistance.)

©2000 California Micro Devices Corp. All rights reserved. SmartOR™ is a trademark of California Micro Devices Corporation.

2

#### **Interface Signals**

$V_{cc}$  is the input power source for the Low Drop Out Regulator, capable of delivering 3.3V/500mA output current even when the input is as low as 4.2V.

Internal loading on this pin is typically 35µA when the regulator is enabled, which reduces to only 7µA whenever the regulator is shutdown ( $\overline{SD}$  taken Low). In the event of V<sub>cc</sub> collapsing below V<sub>out</sub>, the loading at V<sub>cc</sub> will immediately reduce to less than 0.1µA.

If the  $V_{cc}$  pin is within a few inches of the main input filter, a capacitor may not be necessary. Otherwise an input filter capacitor in the range of  $1\mu$ F to  $10\mu$ F will ensure adequate filtering.

**SD** is the regulator shutdown input logic signal which is Active Low. This is a true CMOS input signal referenced to  $V_{cc}$  supply. When the pin is tied High ( $V_{cc}$ ) the regulator operates fully. When the pin is taken to GND, the device enters shutdown mode and the regulator is fully disabled. In this mode all critical POR circuitry remains fully powered consuming less than 7µA (typical).

$V_{out}$  is the regulator output voltage used to power the load. An output capacitor of 10µF is used to provide the necessary phase compensation, thereby preventing oscillation. The capacitor also helps to minimize the peak output disturbance during line or load transients. Whenever  $V_{cc}$  collapses below the output the device immedi-

ately enters reverse protection mode to prevent any current flow back into the regulator pass transistor. Under these conditions  $V_{\text{OUT}}$  will also be used to provide the necessary quiescent current for the internal reference and  $\overrightarrow{\text{POR}}$  circuits. This ensures excellent start-up characteristics for the regulator.

**POR** is the Power-On-Reset output pin (Active Low).

When  $V_{OUT}$  rises above the POR threshold voltage (typically 2.9V), the pin is forced to logic low (GND). The pin remains logic low for 30ms then it is forced logic high (3.3V). If  $V_{OUT}$  falls below the POR threshold voltage during this 30ms interval POR will remain logic low. If it falls below the voltage threshold and then recovers the 30ms time will reset.

If  $V_{\text{OUT}}$  falls below the POR threshold voltage POR is immediately forced to logic low.

The power-on reset circuitry is designed to remain active under all conditions and will produce a valid output even when  $V_{cc}$  is not present. A very low quiescent current (7µA typical) ensures continuous operation of the POR circuit.

**GND** is the negative reference for all voltages. This current that flows in the ground connection is very low  $(35\mu A \text{ typical with the regulator enabled and }7\mu A \text{ typical with the regulator disabled}).$

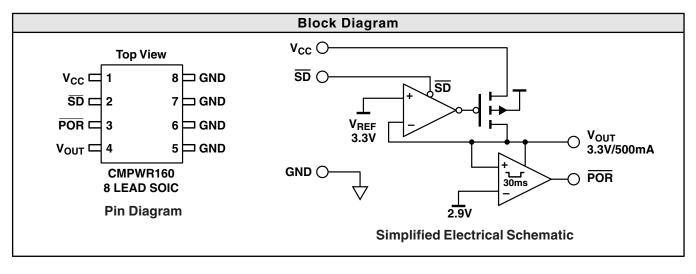

| Pin Functions    |                                                                                                                                                                    |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Description                                                                                                                                                        |  |

| V <sub>CC</sub>  | Positive supply input for regulator. When $V_{CC}$ falls below $V_{OUT}$ the regulator is disabled.                                                                |  |

| SD               | Shutdown control input signal (Active Low) to disable internal voltage regulator and current supply to less than $7\mu A$ .                                        |  |

| POR              | Power-On-Reset output signal is held Low until the output has been stable (>2.9V) for at least 30ms.                                                               |  |

| V <sub>OUT</sub> | Regulator voltage ouput (3.3V) capable of delivering 500mA when device is enabled (SD is High). Whenever the output exceeds 2.9V (TYP) the POR pulse is triggered. |  |

| GND              | Negative reference for all voltages                                                                                                                                |  |

CALIFORNIA MICRO DEVICES

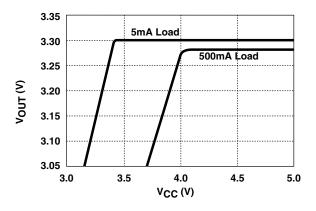

### **Typical DC Characteristics**

Unless stated otherwise, all DC characteristics were measured at room temperature with a nominal  $V_{cc}$  supply voltage of 5V and an output capacitance of  $10\mu$ F. Resistive load conditions were used.

**Line Regulation Characteristics** of the regulator are shown in Figure 1. At maximum rated load conditions (500mA), a 100mV drop in regulation occurs when the line voltage has collapses below 3.8V. For light load conditions (5mA), regulation is maintained for line voltages as low as 3.3V.

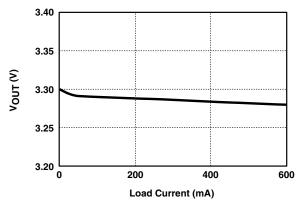

**Load Regulation** performance is shown from zero to maximum rated load in Figure 2. A 10% to 100% change of rated load, results in an output voltage change of less than 10mV. This translates into an effective output impedance of approximately  $0.02\Omega$ .

Figure 2. Load Regulation

100 80 60 40 20 0 0 20 0 20 0 200 400 600 Load Current (mA)

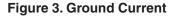

**Ground Current** is shown across the entire range of load conditions in Figure 3. The ground current increases by  $40\mu A$  across the range of load conditions. This increase is due to the current limiting protective circuitry becoming active.

4

#### Typical DC Characteristics continued

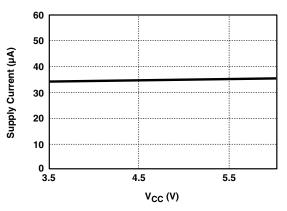

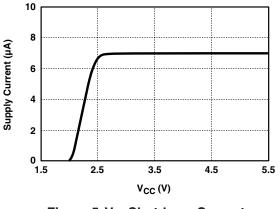

$V_{cc}$  **Operating Current (no load,**  $\overline{SD}$  high) is shown across a range of  $V_{cc}$  supply voltages with the regulator enabled in Figure 4. The graph shows that the operating current is 35µA typical and changes by less than 1µA across this range.

Figure 4. V<sub>cc</sub> Operating Current (no load)

```

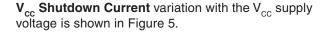

Figure 5. V_{cc} Shutdown Current

```

#### **Typical Transient Characteristics**

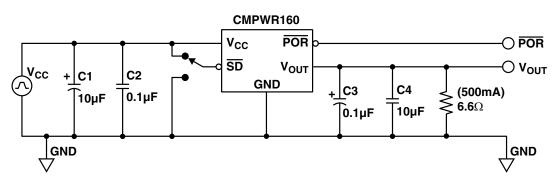

The transient characterization test setup is shown in Figure 6. It was the setup used for the transient tests unless specified otherwise.

A maximum rated load current of 6.6 $\Omega$  (500mA @ 3.3V) was used during characterization along with a nominal V<sub>cc</sub> supply voltage of 5V DC, unless specified otherwise.

The load transient characterization was done by switching between 6.6 and  $660\Omega$  load resistors. This switched the load between 500 and 5mA respectively.

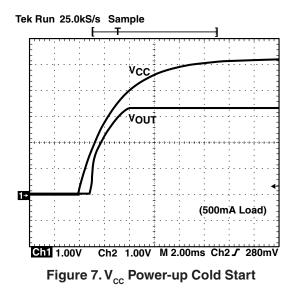

For the V<sub>cc</sub> power-up and power-down characterizations V<sub>cc</sub> supply was ramped between 0 and 5V. Both the rise and fall times for the V<sub>cc</sub> power-up/down pulses were controlled to be 15ms.

In the line transient characterizations the  $V_{cc}$  supply voltage was controlled to step between 4.5 to 5.5V.

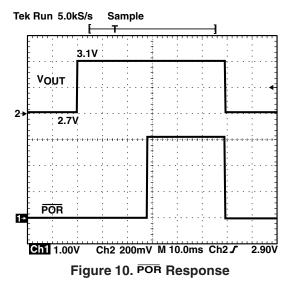

For the POR response characterization V<sub>cc</sub> and SD were tied to ground and the V<sub>OUT</sub> voltage was directly driven between 2.7 and 3.1V. This was done by connecting a function generator directly to the output of the device. These voltage values were picked because it drove V<sub>OUT</sub> directly across the typical POR threshold voltage of 2.9V. V<sub>cc</sub> was tied to ground to show that the POR circuitry will operate even when the V<sub>cc</sub> supply voltage is not present.

The oscilloscope traces show the full bandwidth response at the  $\overline{SD}, \, \overline{POR}, \, V_{_{CC}} \, \text{and} \, V_{_{OUT}} \, \text{pins}$  depending on the characterization.

**Figure 6. Transient Characterization Test Setup**

#### V<sub>cc</sub> power-up Cold Start

6

Figure 7 shows the output response during an initial  $V_{cc}$  power up with  $\overline{SD}$  tied to  $V_{cc}$ . When  $V_{cc}$  reaches a particular threshold, the regulator turns on. The uncharged output capacitor causes maximum inrush current to flow. At this point the device sees the output as a short circuit and the device enters a protective current limiting mode. The output capacitor quickly charges and  $V_{oUT}$  rises. Once this voltage rises to just below  $V_{cc}$  the inrush current stops flowing and the output rises with the input.  $V_{oUT}$  continues to rise with the input until it reaches 3.3V.

#### Typical Transient Characteristics continued

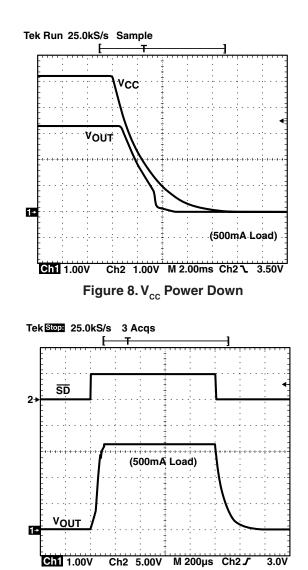

#### V<sub>cc</sub> Power down

Figure 8 shows the output response of the regulator during a complete power down situation under full load conditions with  $\overline{\text{SD}}$  tied to V<sub>cc</sub>.

#### **Shutdown Transient Response**

The transient response of the output voltage to the  $\overline{SD}$  pin is shown in Figure 9. The graph shows that a rising edge on the  $\overline{SD}$  pin enables the regulator and a falling edge disables the regulator.

The rise and fall time for the output voltages are 100µs and 200µs respectively.

### **POR** Response

The transient response of the active low POR pin to V<sub>OUT</sub> is shown in Figure 10. When V<sub>OUT</sub> rises above the POR threshold voltage (typically 2.9V), the pin is forced to logic low (0V). The pin remains at logic low for 30ms then it is forced to logic high (3.3V). If V<sub>OUT</sub> falls below the POR threshold voltage during this 30ms interval POR will remain logic low. If it falls below the voltage threshold and then recovers the 30ms time will reset.

When  $V_{out}$  falls below the  $\overrightarrow{POR}$  threshold voltage  $\overrightarrow{POR}$  is immediately forced to logic low.

$V_{\rm cc}$  is tied to ground to show that the POR circuitry will work without  $V_{\rm cc}$  present.

Figure 9. Shutdown Transient Response

#### Typical Transient Characteristics continued

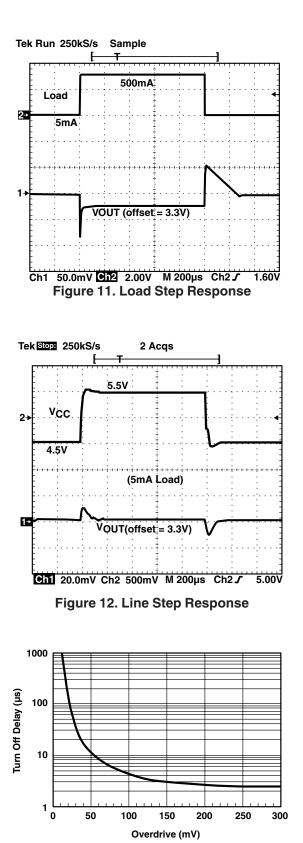

#### Load Step response

Figure 11 shows the output voltage (Ch1) response of the regulator during a step load change between 5mA and 500mA (represented on Ch2). For the 5mA to 500mA transition an initial transient overshoot of 60mV occurs and then the output settles to its final voltage within 20µs. For the 500mA to 5mA transition there is also an initial overshoot of 60mV however it takes approximately 250µs to settle to its final voltage.

The overall DC voltage disturbance on the output is approximately 25mV, which demonstrates the regulator output impedance of  $50m\Omega$ .

V<sub>OUT</sub> offset = 3.3V

#### Line Step Response

Figure 12 shows the output response of the regulator to a  $V_{cc}$  line voltage transient between 4.5V and 5.5V (1Vpp as shown on Ch2). The load condition during this test is 5mA. The output response produces less than 10mV of disturbance on both edges indicating a line rejection of better than 40dB at high frequencies.

$V_{OUT}$  offset = 3.3V

8

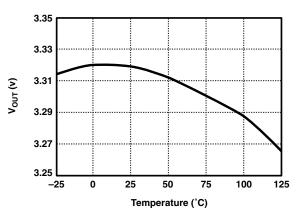

#### Reset response time with overdrive

Figure 13 shows the time it takes for the POR signal to reset when the output voltage is driven below the POR trigger threshold by varying amounts. The amount the voltage is driven below the POR trigger threshold is the overdrive voltage.

Figure 13. Reset Response Time with Overdrive

CALIFORNIA MICRO DEVICES

#### **Typical Thermal Characteristics**

Thermal dissipation of junction heat consists primarily of two paths in series. The first path is the junction to the case ( $\theta_{JC}$ ) thermal resistance which is defined by the package style, and the second path is the case to ambient ( $\theta_{CA}$ ) thermal resistance, which is dependent on board layout.

The overall junction to ambient  $(\boldsymbol{\theta}_{\mathsf{JA}})$  thermal resistance is equal to:

$$\theta_{\rm JA} = \theta_{\rm JC} + \theta_{\rm CA}$$

For a given package style and board layout, the operating junction temperature is a function of junction power dissipation  $P_{JUNC}$ , and the ambient temperature, resulting in the following thermal equation:

$$T_{JUNC} = T_{AMB} + P_{JUNC} (\theta_{JC}) + P_{JUNC} (\theta_{CA})$$

$$= T_{AMB} + P_{JUNC} (\theta_{JA})$$

The CMPWR160SA is housed in a thermally enhanced package where all the GND pins (5 through 8) are integral to the leadframe (fused leadframe). When the device is mounted on a double sided printed circuit board with two square inches of copper allocated for "heat spreading", the resulting  $\theta_{JA}$  is 50°C/W.

Based on a maximum power dissipation of 1.0W (2Vx500mA) with an ambient of 70°C the resulting junction temperature will be:

$$\begin{aligned} \Gamma_{\text{JUNC}} &= T_{\text{AMB}} + P_{\text{JUNC}} \left( \theta_{\text{JA}} \right) \\ &= 70^{\circ}\text{C} + 1.0\text{W} \left( 50^{\circ}\text{C/W} \right) \\ &= 70^{\circ}\text{C} + 50^{\circ}\text{C} = 120^{\circ}\text{C} \end{aligned}$$

All thermal characteristics of the CMPWR160SA were measured using a double sided board with two square inches of copper area connected to the GND pins for "heat spreading".

Measurements showing performance up to junction temperature of 125°C were performed under light load conditions (5mA). This allows the ambient temperature to be representative of the internal junction temperature.

**Note:** The use of multi-layer board construction with power planes will further enhance the thermal performance of the package. In the event of no copper area being dedicated for heat spreading, a multi-layer board construction, using only the minimum size pad layout, will typically provide the CMPWR160SA with an overall  $\theta_{JA}$  of 70°C/W which allows up to 780mW to be safely dissipated.

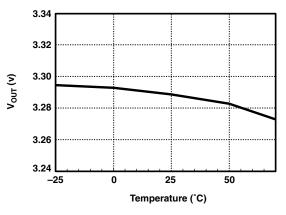

#### **Output Voltage vs. Temperature**

Figure 14 shows the regulator  $V_{OUT}$  performance up to the maximum rated junction temperature. A 125°C variation in junction temperature from -25°C causes an output voltage variation of about 50mV, reflecting a voltage temperature coefficient of approximately ±50ppm/°C.

Figure 14. V<sub>out</sub> Temperature Variation (5mA)

#### Typical Thermal Characteristics continued

#### Output Voltage (Rated) vs. Temperature

Figure 15 shows the regulator steady state performance when fully loaded (500mA) from  $-25^{\circ}$ C up to the rated maximum temperature of 70°C. The output variation at maximum load is approximately 20mV across the shown operating temperature. This translates to a temperature coefficient of approximately ±30ppm/°C.

Figure 15. V<sub>out</sub> Temperature Variation (500mA)

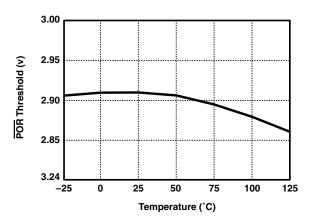

#### **POR** Voltage Threshold Temperature Variation

Figure 16 shows the  $\overrightarrow{POR}$  threshold voltage variation from -25°C up to the maximum rated junction temperature. The overall 150°C change in junction temperature causes less than a 5mV variation in the  $\overrightarrow{POR}$  threshold voltage. This translates to a temperature coefficient of ±6ppm/°C.

The POR pulse duration does not vary with temperature.

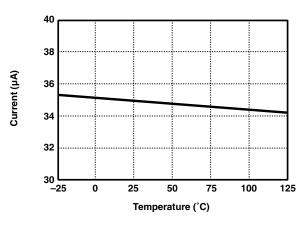

V<sub>CC</sub> Supply Current Temperature Variation

range shown in the plot.

10

Figure 17 shows the  $V_{cc}$  supply current variation with temperature from -25°C to the maximum rated junction temperature with no load on the device. The supply

current changes less than 1µA over the entire 150°C

Figure 16. POR Threshold Temperature Variation

# Figure 17. V<sub>cc</sub> Supply Current vs. Temperature